| First:               |                                        |                            | La                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ıst:                     |           |           |          |         |         |       |          |

|----------------------|----------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|-----------|----------|---------|---------|-------|----------|

| The Please red       | is is a clo<br>ad the ent              | sed bool<br>tire quiz      | La<br>k exam. Yo<br><b>before sta</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ou have 50 rting.        | ) minut   | es, so al | locate y | our tir | ne acc  | ordin | gly.     |

| "The core leadership | e values o<br>o, individu<br>to uphold | f The Unial oppointhese va | r honor conversity of tunity, and throughty."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f Texas at<br>d responsi | bility. E | Each me   | mber of  | the ur  | iversi  | ty is |          |

| Signed: _            |                                        |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |           | No        | vember   | 21, 20  | 800     |       |          |

| (5) Quest            | <b>ion 1.</b> Lis                      | t the thre                 | ee conditio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ns that m                | ust be tr | ue for a  | n RDRI   | F inter | rupt to | occu  | r?       |

|                      |                                        |                            | right-justit<br>f the analo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |           |           | C with a | range   | of 0 to | o +10 | V. What  |

|                      |                                        |                            | a serial poi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                        | _         |           |          |         | -       |       |          |

|                      |                                        |                            | the PS1 of |                          |           |           |          |         | when t  | the A | SCII '5' |

| PS3                  |                                        | 2                          | 3 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          | 6 7       | 8         | 9        | 10      | 11      | 12    | ms       |

Questions 4 and 5 involve the following assembly program involving one 8-bit parameter passed on the stack and one 16-bit local variable, also on the stack.

```

main lds #$4000

movb #100,1,-sp ; pass 8-bit in parameter on stack

jsr sub2

ins

; balance stack, discarding the in parameter

here bra here

in set xxx ; binding of 8-bit input parameter

cnt set yyy ; binding of 16-bit local variable

sub2 leas -2,sp ; allocate 16-bit local variable called cnt

pshx ; save register X

;****body of the subroutine

; .....other stuff.....

ldaa in,sp ; get a copy of in parameter

stx cnt, sp ; store into local variable cnt

; .....other stuff.....

;****end of body

leas 2,sp ; deallocate cnt

; return

```

- (5) Question 4. What value should you use in the **xxx** position to implement the binding of the parameter, **in**?

- (5) Question 5. What value should you use in the yyy position to implement the binding of the local variable, cnt?

- (10) Question 6. Assuming the SCIO has been previously initialized, write a busy-wait subroutine that outputs one 8-bit byte. The parameter is passed call by reference using RegX. ;input: RegX points to data, Output: none SCI\_OutChar

(15) Question 7. This Fifo queue has 8 allocated locations and can hold up to seven 8-bit data values. The picture shows it currently holding three values (shaded). The Fifo and its two pointers are defined in RAM. When the pointers are equal the Fifo is empty.

```

ora

$3900

Address Contents

;allocates 8 holding up to 7 values

Fifo rmb 8

GetPt rmb 2

;points to oldest data

$3900

$00

PutPt rmb 2

;points to place to put next

$3901

$01

This function initializes the Fifo

$02

$3902

Fifo_Init ldx #Fifo

$12

$3903

stx GetPt

$3904

$56

← GetPt

stx PutPt ; Fifo is empty

$3905

$78

$34

$3906

Write an assembly subroutine, Fifo_Get, that implements the Get

$3907

$66

← PutPt

```

operation. A result code is returned in RegA. If RegA=1, then a

byte was successfully removed, and the data is returned in RegB. If RegA=0, no data could be removed from the fifo because it was previously empty at the time of the call.

```

Output: RegA=success, RegB=data removed

;input: none,

Fifo_Get

```

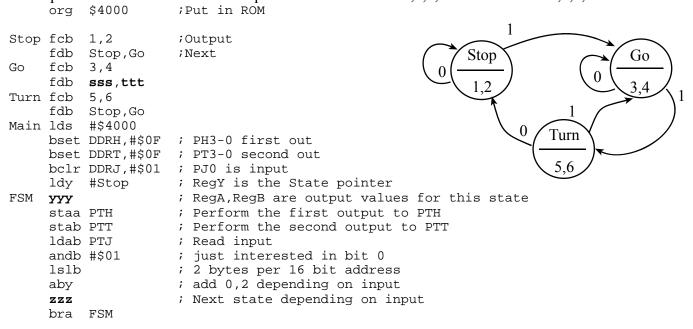

The following 9S12 assembly program implements a one-input four-output finite state machine. The input is on Port J bit 0 and the outputs are on Port H bits 3,2,1,0 and Port T bits 3,2,1,0.

- (5) Question 8. What should you put in the sss, ttt positions?

- (5) Question 9. What instruction (op code and operand) goes in the yyy position?

- (5) Question 10. What instruction (op code and operand) goes in the zzz position?

- (30) Question 11. Assume the PLL is not active, and the E clock is 8 MHz. Write software using output compare 5 interrupts to produce a 1 kHz squarewave on PH0. PH0 is low for 500 µsec, then high for 500 µsec, repeated over and over. Include ALL software for this system: main, initialization, output compare 5 interrupt service routine, the output compare 5 interrupt vector, and reset vector. The main program initializes the stack, initializes PH0, activates output compare 5 interrupts, and then performs a do-nothing loop. The output compare 5 interrupt service routine performs the output to PH0. Global variables are allowed, but not needed.

org \$4000 ; EEPROM main lds #\$4000 ; initialize stack ; initialize PHO, and output compare 5

loop bra loop ; main program does nothing

;output compare 5 interrupt service routine

OC5han

; set the output compare interrupt vector

```

8-bit add RegA=RegA+RegB

des

16-bit decrement RegSP

aba

unsigned add RegX=RegX+RegB

abx

dex

16-bit decrement RegX

unsigned add RegY=RegY+RegB

aby

dey

16-bit decrement RegY

RegY=(Y:D)/RegX, unsigned divide

8-bit add with carry to RegA

ediv

adca

8-bit add with carry to RegB

edivs RegY=(Y:D)/RegX, signed divide

adch

adda

8-bit add to RegA

emacs 16 by 16 signed multiply, 32-bit add

addb

8-bit add to RegB

emaxd 16-bit unsigned maximum in RegD

addd

16-bit add to RegD

emaxm 16-bit unsigned maximum in memory

anda

8-bit logical and to RegA

emind 16-bit unsigned minimum in RegD

eminm 16-bit unsigned minimum in memory

8-bit logical and to RegB

andb

andcc 8-bit logical and to RegCC

RegY:D=RegY*RegD unsigned multiply

emuls RegY:D=RegY*RegD signed multiply

asl/lsl

8-bit left shift Memory

asla/lsla 8-bit left shift RegA

eora

8-bit logical exclusive or to RegA

aslb/lslb 8-bit arith left shift RegB

8-bit logical exclusive or to RegB

eorb

16-bit look up and interpolation

asld/lsld 16-bit left shift RegD

etbl

8-bit arith right shift Memory

exchange register contents

exg X,Y

exa

8-bit arith right shift to RegA

fdiv

unsigned fract div, X=(65536*D)/X

asra

asrb

8-bit arith right shift to RegB

ibeq

increment and branch if result=0

ibeq Y,loop

branch if carry clear

increment and branch if result≠0

ibne A,loop

bcc

ibne

bclr

bit clear in memory

bclr PTT, #$01

idiv

16-bit unsigned div, X=D/X, D=remainder

branch if carry set

16-bit signed divide, X=D/X, D= remainder

bcs

idivs

branch if result is zero (Z=1)

8-bit increment memory

inc

bea

branch if signed ≥

8-bit increment RegA

bge

inca

enter background debug mode

8-bit increment RegB

bgnd

incb

hat.

branch if signed >

ins

16-bit increment RegSP

branch if unsigned >

16-bit increment RegX

bhi

branch\ if\ unsigned \geq

16-bit increment RegY

bhs

iny

8-bit and with RegA, sets CCR

jump always

bita

ami

bitb 8-bit and with RegB, sets CCR

jump to subroutine

ble

branch if signed ≤

lbcc

long branch if carry clear

blo

branch if unsigned <

lbcs

long branch if carry set

bls

branch if unsigned ≤

lbeq

long branch if result is zero

branch if signed <

long branch if signed ≥

blt.

lbge

branch if result is negative (N=1)

long branch if signed >

bmi

lbat.

branch if result is nonzero (Z=0)

long branch if unsigned >

lbhi

long branch if unsigned ≥

bpl

branch if result is positive (N=0)

1 bhs

bra

branch always

1ble

long branch if signed ≤

brclr branch if bits are clear

brclr PTT, #$01, loop

lblo

long branch if unsigned <

branch never

lbls

long branch if unsigned ≤

brn

brset branch if bits are set

brset PTT, #$01, loop

lblt

long branch if signed <

bset bit set clear in memory

bset PTT, #$04

lbmi

long branch if result is negative

long branch if result is nonzero

bsr

branch to subroutine

1bne

branch if overflow clear

lbpl

long branch if result is positive

bvc

bvs

branch if overflow set

lbra

long branch always

subroutine in expanded memory

long branch never

1 hrn

call

cha

8-bit compare RegA with RegB

long branch if overflow clear

clc

clear carry bit, C=0

lbvs

long branch if overflow set

clear I=0, enable interrupts

8-bit load memory into RegA

ldaa

cli

8-bit memory clear

8-bit load memory into RegB

clr

ldab

RegA clear

ldd

16-bit load memory into RegD

clra

RegB clear

lds

16-bit load memory into RegSP

clrb

clear overflow bit, V=0

16-bit load memory into RegX

ldx

clv

8-bit compare RegA with memory

ldv

16-bit load memory into RegY

cmpa

8-bit compare RegB with memory

16-bit load effective addr to SP

cmph

leas

leas 2.sp

8-bit logical complement to memory

16-bit load effective addr to X

leax 2.x

com

8-bit logical complement to RegA

coma

leav

16-bit load effective addr to Y

leay 2,y

8-bit logical complement to RegB

8-bit logical right shift memory

lsr

comb

cpd

16-bit compare RegD with memory

lsra

8-bit logical right shift RegA

16-bit compare RegX with memory

lsrb

8-bit logical right shift RegB

срх

16-bit compare RegY with memory

16-bit logical right shift RegD

lsrd

сру

8-bit decimal adjust accumulator

8-bit unsigned maximum in RegA

daa

maxa

decrement and branch if result=0

dbea

dbeq Y,loop

maxm

8-bit unsigned maximum in memory

decrement and branch if result≠0

determine the membership grade

dbne

dbne A, loop

mem

8-bit decrement memory

8-bit unsigned minimum in RegA

mina

deca

8-bit decrement RegA

minm

8-bit unsigned minimum in memory

decb 8-bit decrement RegB

8-bit move memory to memory

movb #100.PTT

```

| movw               | 16-bit move memo                                                         | ory to memory   | movw #13,5 | CIBD | wai                                           | wait for inte                           | errupt          |                            |  |  |  |

|--------------------|--------------------------------------------------------------------------|-----------------|------------|------|-----------------------------------------------|-----------------------------------------|-----------------|----------------------------|--|--|--|

| mul                | RegD=RegA*RegB                                                           |                 |            |      | wav weighted Fuzzy logic average              |                                         |                 |                            |  |  |  |

| neg                | 8-bit 2's compleme                                                       |                 |            |      | xgdx                                          | exchange R                              | egD with RegX   |                            |  |  |  |

| nega               | 8-bit 2's compleme                                                       | ent negate RegA | Λ          |      | xgdy                                          | exchange R                              | egD with RegY   |                            |  |  |  |

| negb               | 8-bit 2's compleme                                                       |                 | 3          |      |                                               |                                         |                 |                            |  |  |  |

| oraa               | 8-bit logical or to                                                      | •               |            |      | Exan                                          | nple                                    | Mode            | Effective Address          |  |  |  |

| orab               | 8-bit logical or to                                                      |                 |            |      |                                               | a #u                                    | immediate       | No EA                      |  |  |  |

| orcc               | 8-bit logical or to                                                      | -               |            |      | ldaa                                          |                                         |                 |                            |  |  |  |

| psha               | push 8-bit RegA o                                                        |                 |            |      |                                               |                                         | direct          | EA is 8-bit address        |  |  |  |

| pshb               | push 8-bit RegB o                                                        |                 |            |      | ldaa                                          |                                         | extended        | EA is a 16-bit address     |  |  |  |

| pshc<br>pshd       | push 8-bit RegCC<br>push 16-bit RegD                                     |                 |            |      |                                               | a m,r                                   | 5-bit index     | EA=r+m (-16 to 15)         |  |  |  |

| psha               | push 16-bit RegX                                                         |                 |            |      | ldaa                                          | a v,+r                                  | pre-incr        | r=r+v, EA=r (1 to 8)       |  |  |  |

| pshy               | push 16-bit RegY                                                         |                 |            |      | ldaa                                          | a v,-r                                  | pre-dec         | r=r-v, EA=r (1 to 8)       |  |  |  |

| pula               | pop 8 bits off stack                                                     |                 |            |      |                                               | a v,r+                                  | post-inc        | EA=r, r=r+v (1 to 8)       |  |  |  |

| pulb               | pop 8 bits off stack                                                     |                 |            |      |                                               |                                         |                 |                            |  |  |  |

| pulc               | pop 8 bits off stacl                                                     | -               |            |      |                                               | a v,r-                                  | post-dec        | EA=r, r=r-v (1 to 8)       |  |  |  |

| puld               | pop 16 bits off sta                                                      | ck into RegD    |            |      |                                               | a A,r                                   | Reg A offset    | EA=r+A, zero padded        |  |  |  |

| pulx               | pop 16 bits off sta                                                      | ck into RegX    |            |      | ldaa                                          | a B,r                                   | Reg B offset    | EA=r+B, zero padded        |  |  |  |

| puly               | pop 16 bits off sta                                                      | _               |            |      | ldaa                                          | a D,r                                   | Reg D offset    | EA=r+D                     |  |  |  |

| rev                | Fuzzy logic rule e                                                       |                 |            |      | ldaa                                          | a q,r                                   | 9-bit index     | EA=r+q                     |  |  |  |

| revw               | weighted Fuzzy ru                                                        |                 |            |      |                                               | a W,r                                   | 16-bit index    | EA=r+W                     |  |  |  |

| rol                | 8-bit roll shift left                                                    | -               |            |      |                                               |                                         |                 |                            |  |  |  |

| rola               | 8-bit roll shift left                                                    | -               |            |      | ldaa                                          |                                         | D indirect      | $EA = \{r + D\}$           |  |  |  |

| rolb               | 8-bit roll shift left<br>8-bit roll shift righ                           | -               |            |      | ldaa                                          | a [W,r]                                 | indirect        | $EA=\{r+W\}$               |  |  |  |

| ror<br>rora        | 8-bit roll shift righ                                                    | •               |            |      | Free                                          | scale 6812                              | addressing mod  | des r is X, Y, SP, or PC   |  |  |  |

| rorb               | 8-bit roll shift righ                                                    |                 |            |      |                                               |                                         |                 |                            |  |  |  |

| rtc                | return sub in expan                                                      |                 |            |      | Pceu                                          | do op                                   | Mea             | ninα                       |  |  |  |

| rti                | return from interru                                                      |                 |            |      |                                               | ио ор                                   |                 | ere to put subsequent code |  |  |  |

| rts                | return from subrou                                                       | 1               |            |      | org                                           | _                                       |                 |                            |  |  |  |

| sba                | 8-bit subtract Reg.                                                      | A-RegB          |            |      |                                               | qu set                                  |                 | ne a constant symbol       |  |  |  |

| sbca               | 8-bit sub with carr                                                      | y from RegA     |            |      | dc.                                           | b db fck                                | .byte Allo      | cate byte(s) with values   |  |  |  |

| sbcb               | 8-bit sub with carr                                                      | y from RegB     |            |      | fcc                                           |                                         | Crea            | ite an ASCII string        |  |  |  |

| sec                | set carry bit, C=1                                                       |                 |            |      | dc.                                           | w dw fdb                                | .word Allo      | cate word(s) with values   |  |  |  |

| sei                | set I=1, disable int                                                     | •               |            |      |                                               | l dl .lc                                |                 | cate 32-bit with values    |  |  |  |

| sev                | set overflow bit, V                                                      |                 | B B        |      |                                               |                                         | -               |                            |  |  |  |

| sex                | sign extend 8-bit to                                                     | -               | sex B,D    |      | ds ds.b rmb .blkb Allocate bytes without init |                                         |                 |                            |  |  |  |

| stab               | aa 8-bit store memory from RegA ds.w .blkw Allocate word(s) without init |                 |            |      |                                               |                                         |                 |                            |  |  |  |

| stab               | 16-bit store memor                                                       | _               |            |      |                                               |                                         |                 |                            |  |  |  |

| sts                | 16-bit store memo                                                        |                 |            |      | Vecto                                         | r Inte                                  | errupt Source   | Arm                        |  |  |  |

| stx                | 16-bit store memo                                                        | -               |            |      | \$FFF                                         | E Res                                   | set             | None                       |  |  |  |

| sty                | 16-bit store memo                                                        |                 |            |      | \$FFF                                         |                                         | ın              | None                       |  |  |  |

| suba               | 8-bit sub from Reg                                                       |                 |            |      | \$FFF                                         |                                         |                 | None                       |  |  |  |

| subb               | 8-bit sub from Reg                                                       | gВ              |            |      |                                               |                                         |                 |                            |  |  |  |

| subd               | 16-bit sub from Re                                                       | egD             |            |      | \$FFF                                         |                                         | al time interru |                            |  |  |  |

| swi                | software interrupt,                                                      | trap            |            |      | \$FFE                                         |                                         | ner channel 0   | TIE.C0I                    |  |  |  |

| tab                | transfer A to B                                                          |                 |            |      | \$FFE                                         |                                         | ner channel 1   | TIE.C1I                    |  |  |  |

| tap                | transfer A to CC                                                         |                 |            |      | \$FFE                                         | A Tin                                   | ner channel 2   | TIE.C2I                    |  |  |  |

| tba                | transfer B to A                                                          |                 | bee 37 3   |      | \$FFE                                         | 8 Tin                                   | ner channel 3   | TIE.C3I                    |  |  |  |

| tbeq               | test and branch if i<br>8-bit look up and i                              |                 | beq Y,loop |      | \$FFE                                         |                                         | ner channel 4   | TIE.C4I                    |  |  |  |

| tbl<br>tbne        | test and branch if                                                       | 1               | bne A,loop |      | \$FFE                                         |                                         | ner channel 5   | TIE.C5I                    |  |  |  |

| tfr                | transfer register to                                                     |                 | fr X,Y     |      | \$FFE                                         |                                         | ner channel 6   |                            |  |  |  |

| tpa                | transfer CC to A                                                         |                 | 41/1       |      |                                               |                                         |                 | TIE.C6I                    |  |  |  |

| trap               | illegal instruction                                                      | interrupt       |            |      | \$FFE                                         |                                         | ner channel 7   | TIE.C7I                    |  |  |  |

| trap               |                                                                          |                 |            |      |                                               | \$FFDE <b>Timer overflow</b> TSCR2.TOI  |                 |                            |  |  |  |

| tst                | - 5 1                                                                    |                 |            |      |                                               | \$FFD6 <b>SCIO TDRE, RDRF</b> SCIOCR2.T |                 |                            |  |  |  |

| tsta               | 8-bit compare Reg                                                        |                 |            |      | \$FFD                                         | 4 <b>SC</b>                             | II TDRE, RD     | RF SCI1CR2.TIE,RIE         |  |  |  |

| tstb               | 8-bit compare Reg                                                        | B with zero     |            |      | \$FFC                                         |                                         | y Wakeup J      | PIEJ.[7,6,1,0]             |  |  |  |

| tsx                | transfer S to X                                                          |                 |            |      | \$FFC                                         |                                         | y Wakeup H      | PIEH.[7:0]                 |  |  |  |

| tsy                | transfer S to Y                                                          |                 |            |      | \$FF81                                        |                                         | y Wakeup P      | PIEP.[7:0]                 |  |  |  |

| txs                | transfer X to S                                                          |                 |            |      |                                               |                                         | _               | 1121.[7.0]                 |  |  |  |

| tys<br>Addres      | transfer Y to S                                                          | 6               | 5          | 4    | nter<br>3                                     | rupt Vectoi<br>2                        |                 | Bit 0 Name                 |  |  |  |

| \$0040             | s Bit 7 IOS7                                                             | IOS6            | IOS5       | IOS4 | IOS3                                          | IOS2                                    | I<br>IOS1       | IOS0 TIOS                  |  |  |  |

| φυυ <del>1</del> υ | 1057                                                                     | 1030            | 1000       | 1004 | 1000                                          | 1032                                    | 1001            | 1050                       |  |  |  |

| \$0044-5 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TCNT      |

|----------|--------|---------|-------|---------|--------|-------|-------|-------|-----------|

| \$0046   | TEN    | TSWAI   | TSFRZ | TFFCA   | 0      | 0     | 0     | 0     | TSCR1     |

| \$004C   | C7I    | C6I     | C5I   | C4I     | C3I    | C2I   | C1I   | COI   | TIE       |

| \$004D   | TOI    | 0       | PUPT  | RDPT    | TCRE   | PR2   | PR1   | PR0   | TSCR2     |

| \$004E   | C7F    | C6F     | C5F   | C4F     | C3F    | C2F   | C1F   | C0F   | TFLG1     |

| \$004F   | TOF    | 0       | 0     | 0       | 0      | 0     | 0     | 0     | TFLG2     |

| \$0050-1 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC0       |

| \$0052-3 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC1       |

| \$0054-5 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC2       |

| \$0056-7 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC3       |

| \$0058-9 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC4       |

| \$005A-B | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC5       |

| \$005C-D | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC6       |

| \$005E-F | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | TC7       |

| \$0082   | ADPU   | AFFC    | ASWAI | ETRIGLE | ETRIGP | ETRIG | ASCIE | ASCIF | ATD0CTL2  |

| \$0083   | 0      | S8C     | S4C   | S2C     | S1C    | FIFO  | FRZ1  | FRZ0  | ATD0CTL3  |

| \$0084   | SRES8  | SMP1    | SMP0  | PRS4    | PRS3   | PRS2  | PRS1  | PRS0  | ATD0CTL4  |

| \$0085   | DJM    | DSGN    | SCAN  | MULT    | 0      | CC    | СВ    | CA    | ATD0CTL5  |

| \$0086   | SCF    | 0       | ETORF | FIFOR   | 0      | CC2   | CC1   | CC0   | ATD0STAT0 |

| \$008B   | CCF7   | CCF6    | CCF5  | CCF4    | CCF3   | CCF2  | CCF1  | CCF0  | ATD0STAT1 |

| \$008D   | Bit 7  | 6       | 5     | 4       | 3      | 2     | 1     | Bit 0 | ATD0DIEN  |

| \$008F   | PAD07  | PAD06   | PAD05 | PAD04   | PAD03  | PAD02 | PAD01 | PAD00 | PORTAD0   |

| \$0090-1 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR0   |

| \$0092-3 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR1   |

| \$0094-5 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR2   |

| \$0096-7 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR3   |

| \$0098-9 | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR4   |

| \$009A-B | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR5   |

| \$009C-D | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR6   |

| \$009E-F | Bit 15 | 14      | 13    | 12      | 11     | 10    |       | Bit 0 | ATD0DR7   |

| \$00C9   | 0      | 0       | 0     | SBR12   | SBR11  | SBR10 |       | SBR0  | SCI0BD    |

| \$00CA   | LOOPS  | SCISWAI | RSRC  | M       | WAKE   | ILT   | PE    | PT    | SCI0CR1   |

| \$00CB   | TIE    | TCIE    | RIE   | ILIE    | TE     | RE    | RWU   | SBK   | SCI0CR2   |

| \$00CC   | TDRE   | TC      | RDRF  | IDLE    | OR     | NF    | FE    | PF    | SCI0SR1   |

| \$00CD   | 0      | 0       | 0     | 0       | 0      | BRK13 | TXDIR | RAF   | SCI0SR2   |

| \$00CF   | R7/T7  | R6/T6   | R5/T5 | R4/T4   | R3/T3  | R2/T2 | R1/T1 | R0/T0 | SCI0DRL   |

| \$00D0-1 | 0      | 0       | 0     | SBR12   | SBR11  | SBR10 |       | SBR0  | SCI1BD    |

| \$00D2   | LOOPS  | SCISWAI | RSRC  | M       | WAKE   | ILT   | PE    | PT    | SCI1CR1   |

| \$00D3   | TIE    | TCIE    | RIE   | ILIE    | TE     | RE    | RWU   | SBK   | SCI1CR2   |

| \$00D4   | TDRE   | TC      | RDRF  | IDLE    | OR     | NF    | FE    | PF    | SCI1SR1   |

| \$00D5   | 0      | 0       | 0     | 0       | 0      | BRK13 | TXDIR | RAF   | SCI1SR2   |

| \$00D7   | R7/T7  | R6/T6   | R5/T5 | R4/T4   | R3/T3  | R2/T2 | R1/T1 | R0/T0 | SCI1DRL   |

| \$0240   | PT7    | PT6     | PT5   | PT4     | PT3    | PT2   | PT1   | PT0   | PTT       |

| \$0242   | DDRT7  | DDRT6   | DDRT5 | DDRT4   | DDRT3  | DDRT2 | DDRT1 | DDRT0 | DDRT      |

| \$0248   | PS7    | PS6     | PS5   | PS4     | PS3    | PS2   | PS1   | PS0   | PTS       |

| \$024A   | DDRS7  | DDRS6   | DDRS5 | DDRS4   | DDRS3  | DDRS2 | DDRS1 | DDRS0 | DDRS      |

| \$0250   | PM7    | PM6     | PM5   | PM4     | PM3    | PM2   | PM1   | PM0   | PTM       |

| \$0252   | DDRM7  | DDRM6   | DDRM5 | DDRM4   | DDRM3  | DDRM2 | DDRM1 | DDRM0 | DDRM      |

| \$0258   | PP7    | PP6     | PP5   | PP4     | PP3    | PP2   | PP1   | PP0   | PTP       |

| \$025A   | DDRP7  | DDRP6   | DDRP5 | DDRP4   | DDRP3  | DDRP2 | DDRP1 | DDRP0 | DDRP      |

| \$0260   | PH7    | PH6     | PH5   | PH4     | PH3    | PH2   | PH1   | PH0   | PTH       |

| \$0262   | DDRH7  | DDRH6   | DDRH5 | DDRH4   | DDRH3  | DDRH2 | DDRH1 | DDRH0 | DDRH      |

| \$0268   | PJ7    | PJ6     | 0     | 0       | 0      | 0     | PJ1   | PJ0   | PTJ       |

| \$026A   | DDRJ7  | DDRJ6   | 0     | 0       | 0      | 0     | DDRJ1 | DDRJ0 | DDRJ      |

TSCR1 is the first 8-bit timer control register

bit 7 TEN, 1 allows the timer to function normally, 0 means disable timer including TCNT

TSCR2 is the second 8-bit timer control register

bits 2,1,0 are PR2, PR1, PR0, which select the rate, let  $\bf n$  be the 3-bit number formed by PR2, PR1, PR0 without PLL **TCNT** is  $8 \rm MHz/2^n$ , with PLL **TCNT** is  $24 \rm MHz/2^n$ ,  $\bf n$  ranges from 0 to 7

**TIOS** is the 8-bit output compare select register, one bit for each channel (1 = output compare, 0 = input capture)**TIE** is the 8-bit output compare arm register, one bit for each channel (1 = armed, 0 = disarmed)