| EE445L Spring 2018 | Final | EID: | Page 1 of 7 |

|--------------------|-------|------|-------------|

|--------------------|-------|------|-------------|

Jonathan W. Valvano

First:\_\_\_\_\_ Last:\_\_\_\_\_

This is the closed book section. Calculator is allowed (no laptops, phones, devices with wireless communication). You must put your answers in the boxes. Do not write on the back of the page. When you are done, you turn in the closed-book part and can start the open book part.

(4) Question 1. Why do we use PWM to adjust power to the motor? Choose the one best answer.

- A) Provides for reduced latency

- B) Provides high precision

- C) Provides low precision

- D) Provides good CMRR

E) Provides high input impedance

- F) Creates a low amount of EM radiation

- G) Low amount of back EMF

(6) Question 2. Consider the lab 10 system used to control motor speed. Choose the one best answer from the following A-F for both parts a) and b).

A) Reduces controller error

B) Reduces controller response time

C) Reduces cost

D) Reduces sensor noise

E) Faster for software to execute

F) Requires less memory

(3) Part a) In what way is a PI controller better than just an I controller?

(3) Part b) In what way is a PI controller better than just a P controller?

(2) Question 3. In 8 words or less, why does the motor not spin at all if the duty cycle is nonzero, but very small (e.g., 1%)?

(4) **Question 4.** Why do we use an active filter (with op amp) rather than a passive filter (with just R and C)? Choose the one best answer.

A) Central limit theorem

B) Nyquist theorem

C) Shannon channel capacity

D) Lower input impedance

E) Lower output impedance

F) Lower cost

(4) Question 5. What is the purpose of the resistance bridge when interfacing the thermistor to the microcontroller like Lab 9? Select all that apply.

A) Converts resistance to voltage

- B) Handles the offset needed because the resistance varied from  $R_{min}$  to  $R_{max}$

- C) Nonlinear correction, so the output is more linear with temperature than resistance alone

D) Allows the use of a voltage reference, so the signals are low noise

(5) Question 6. You are debugging an implementation of a software FIFO queue with functions Put and Get. You are wondering if a call to Put has occurred at any point inside Get. I.e., you are looking to detect the following sequence A) Get starts, B) an interrupt occurs, C) Put starts, D) Put finishes, E) return from interrupt, and F) Get finishes. You must use a logic analyzer to solve this problem. Part a) How do you modify the Get and Put software in order to be able to use the logic analyzer for

EID:

debugging? Do not worry about initializing GPIO inputs or outputs you wish to add.

**Part b)** Show the logic analyzer signals if this scenario were to occur?

Part c) How do you configure the trigger on the logic analyzer to capture this scenario?

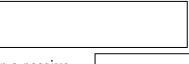

(5) Question 7. The output from PB2 contains a clock signal transmitted across a long wire to an external device. We will model the long wire as a 100- $\Omega$  resistor and a 10-nF capacitor. What is the fastest clock speed (*f*=1/*T*) that can be safely used in this interface? Show your work. Draw the clock signal at the device if the speed is two times faster than your answer (approximate shape is ok). Draw the clock signal at the device if the speed is two times slower than your answer (approximate shape is ok).

| EE445L Spring 2018 | Final | EID: | Page 3 of 7 |

|--------------------|-------|------|-------------|

|--------------------|-------|------|-------------|

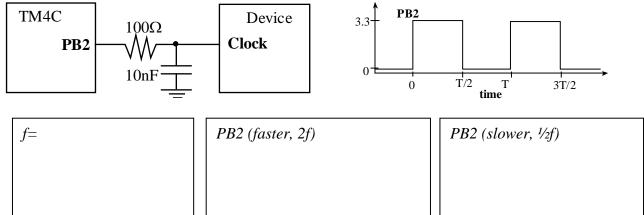

(5) Question 8. Consider a real-time data acquisition system with a 10-bit ADC sampled at  $f_s$ . The following data were collected at the input of the ADC. The desired signal exists in the 0 to 100 kHz range, and the rest of what you see in this spectrum is noise. Yes, it needs an analog filter. However, if you were to sample this signal exactly like this, what is the slowest sampling rate  $f_s$  allowed that will prevent aliasing? Show your work. In particular, calculate the ADC resolution in  $dB_{FS}$  and draw it as a horizontal line on this graph.

(5) Question 9. This FIFO queue implementation with shared globals Size, GetI, PutI has a critical section on the read modify write access to Size. It can store up to 16 elements.

| <pre>int Fifo_Put(int32_t data){</pre>       | int Fifo_Get(int32_t *datapt){               |

|----------------------------------------------|----------------------------------------------|

| if(Size==16) return 0; // full               | if(Size == 0) return 0; // empty             |

| <pre>FIFO[PutI] = data; // save</pre>        | <pre>*datapt = FIFO[GetI]; // retrieve</pre> |

| <pre>PutI = (PutI+1)&amp;0x0F; // next</pre> | GetI = (GetI+1)&0x0F; // next place to get   |

| Size++;                                      | Size;                                        |

| return 1;                                    | return 1;                                    |

| }                                            | }                                            |

To remove the critical section someone changed the implementation of **Size** to be static.

```

int Fifo_Get(int32_t *datapt){

int Fifo Put(int32 t data){

static uint32_t Size;

static uint32 t Size;

if(Size==16) return 0; // full

if(Size == 0) return 0; // empty

FIFO[PutI] = data;

// save

*datapt = FIF0[GetI];

// retrieve data

PutI = (PutI+1) \& 0x0F;

// next

GetI = (GetI+1) \& 0x0F;

// next place to get

Size++;

Size--;

return 1;

return 1;

```

(3) Part a) Does this new system still have a critical section?

Circle: "has a critical section" or "no critical sections"

(2) Part b) Does this change create any other bugs?

Circle: "yes, adds a bug" or "no, system ok"

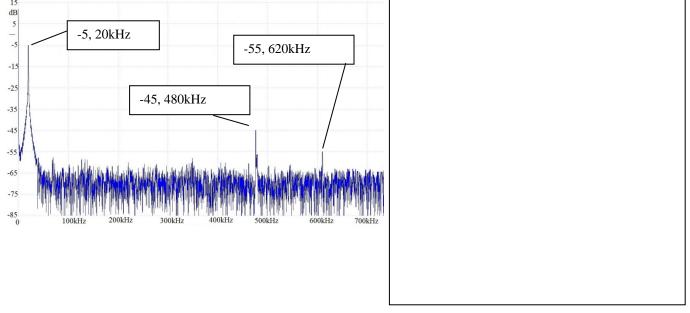

(5) Question 10. Consider a flip flop that stores data into itself on the falling edge of its *Clock* input. The hold time is 100 ns and the setup time is 200 ns. *Which timing signal can you specify (data available or data required)? Complete the timing diagram to scale showing either data available or data required.* Show the transfer of one bit (not the entire frame).

(10) Question 11. Consider a battery with voltage  $V_{bat}$  (in volts). The battery has *S* storage (in mA-hr). The regulator has a power efficiency of *E*, creating a 3.3V supply for the system. To save power, the system runs x% of the time at  $I_{run}$  (in mA) and sleeps (100-x)% at  $I_{sleep}$  (in mA). The units of x are percent (0 to 100). Derive three equations needed to determine how long will this battery run the system?

Derive an equation for  $I_{sys}$ , the average current of the system at the output of the regulator

Derive an equation relating voltage (3.3V) and current ( $I_{sys}$ ) at the output of the regulator compared to voltage ( $V_{bat}$ ) and current ( $I_{bat}$ ) at the battery

Derive an equation relating system operation time T, S and Ibat

(5) **Question 12**. In what manner does being ethical in the engineering world optimize profit? Give your answer in 16 words or less.

| EE445L Spring 2018 | Final | EID: | Page 5 of 7 |

|--------------------|-------|------|-------------|

|                    |       |      |             |

First:

Jonathan W. Valvano

\_\_\_\_\_ Last:\_\_\_\_

Open book, open notes, calculator (no laptops, phones, devices with screens larger than a TI-89 calculator, devices with wireless communication). You must put your answers in these boxes. Please don't turn in any extra sheets or write on the back of the pages.

(15) Problem 13. You are given an input analog signal connected to the microcontroller. Assume the ADC has been initialized, and you have access to the ADC\_In function that returns a new 12-bit sample. uint16\_t ADC\_In(void); // returns 0 to 4095

The signals of interest are 0 to 100 Hz. Design a software system that measures the input in volts and calculates the derivative in V/s. The bus clock is 80 MHz.

(8) Part a) Show the global variables, and initialization function (configure periodic interrupts, arm and enable). Specify the appropriate priority for this real-time task. You do not write ADC\_Init().

(8) Part b) Show the interrupt service routine that runs in the background, sampling the ADC, calculating the derivative, and passing the results to the foreground. You do not write ADC\_In().

| EE445L Spring 2018 | Final | EID: | Page 6 of 7 |

|--------------------|-------|------|-------------|

|--------------------|-------|------|-------------|

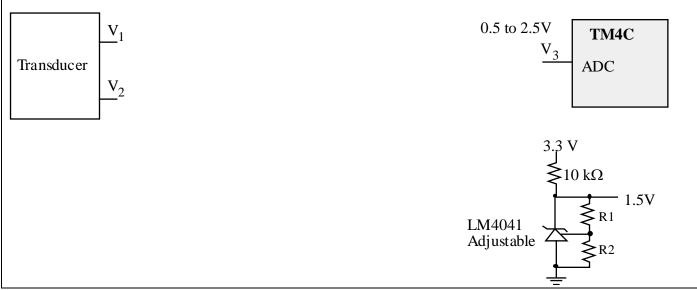

(10) Question 14. Design an analog amplifier with an input impedance larger than 10 M $\Omega$ . There are two inputs V<sub>1</sub> and V<sub>2</sub>, and the input signal is defined as V<sub>1</sub> - V<sub>2</sub>. Design the circuit such that the output V<sub>3</sub> ranges from 0.5 to 2.5V. The input voltages are constrained to -0.025V < (V<sub>1</sub> - V<sub>2</sub>) < 0.025V. No analog filter is required in this question. The only available power supply voltage is 3.3V. Assume R1 and R2 are already chosen to achieve a reference of 1.5V.

(5) Question 15. Design an anti-aliasing filter. The signals of interest are 0 to 100 Hz, and the sampling rate is 1000 Hz. Show the design steps, and specify resistor/capacitor values. Use standard values for the resistors and capacitors. We can multiply a number in the following table by powers of 10 to select a standard value. For example, if we need a 2.5 k $\Omega$  resistor, the closest number is 24, or 2.4 k $\Omega$ . For example if we need a 123nF capacitor, the closest number is 12, or 120 nF.

| 10 | 11 | 12 | 13 | 15 | 16 | 18 | 20 | 22 | 24 | 27 | 30 |

|----|----|----|----|----|----|----|----|----|----|----|----|

| 33 | 36 | 39 | 43 | 47 | 51 | 56 | 62 | 68 | 75 | 82 | 91 |

(10) Question 16. The goal of the problem is to design a system to measure the phase between two sin waves,  $V_1$  and  $V_2$ . Both waves vary from -2 to +2 V around a DC value of 0 V and have a frequency of 100 Hz (period is 10ms). The phase lag from the first signal to the second signal will be limited to 0 to +90 degrees (PB6 always leads PB7). Assume the bus clock is 80 MHz. Calculate the phase as a fixed point number with resolution 0.1 degree. Store the measurement in the global **Phase**.

uint32\_t Phase; int Done;

**Part a)** You are given the hardware and asked to design the software that uses input capture interrupts. Show the ritual that initializes the system. The main program calls this initialization, enables interrupts, and then performs other unrelated tasks. You may call any software function defined in the book.

**Part b)** Show the interrupt service routine that measures phase. Signal the semaphore **Done** when new data is available