Jonathan W. Valvano First: Last: <u>Solution</u> November 20, 2015, 10:00-10:50am. Open book, open notes, calculator (no laptops, phones, devices with screens larger than a TI-89 calculator, devices with wireless communication). You have 50 minutes, so please allocate your time accordingly. *Please read the entire quiz before starting*.

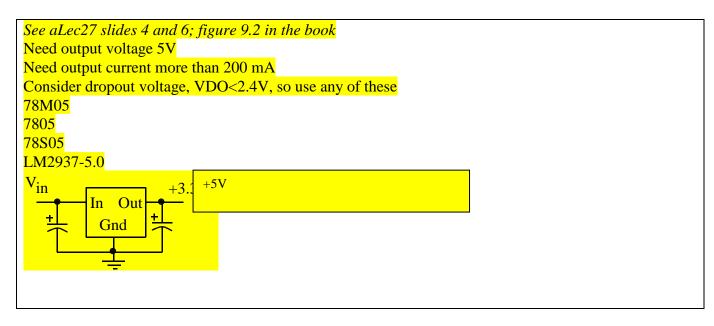

(10) Question 1. Design a circuit that takes a 8.4V NiMH battery and produces a 5V power supply for an embedded system. In sleep mode the system needs 0.5 mA of current, and in active mode the system requires 200 mA of current. Show all part numbers, but do not worry about exact values for the resistors, capacitors and inductors. It runs in sleep mode 99% of the time and runs in active mode 1% of the time.

(5) Question 2. Consider a quantitative data acquisition system that measures voltage versus time. The input voltage range is 0 to 2.5 V. The ADC is 14 bits. The microcontroller crystal is 48 MHz. The bus clock is 48 MHz. The ADC is clocked such that the maximum sampling rate is 125 kHz. A periodic timer triggers an interrupt at 1 kHz (every 1 ms), and the timer ISR starts the ADC, waits for the ADC to complete, and stores the result into an array. The array can hold 1024 samples. Hardware averaging is selected so each sample is the average of four ADC conversions. The array fills up in 1024ms. Once the array is full the timer interrupt is disarmed, and a DFT (FFT) is performed on the data. What is the frequency resolution represented in these digital samples? Show your work.

**Resolution is range over precision;**  $\Delta f = f_s/N = 1000$ Hz/1024 = 0.98Hz On the DFT the frequency range is  $-\frac{1}{2} f_s$  to  $+\frac{1}{2} f_s$  with N points (15) Question 3. The goal is to transmit data from left to right using SSI. The microcontroller on the left is master and the one on the right is the slave. When the left microcontroller wishes to transmit 8 bits of data, it calls this function

```

void SSI_Out(uint8_t data){

while((SSI0_SR_R&0x0000002)==0){};

SSI0_DR_R = data; }

```

| TM4C123 |                                         |            | TM4C123                                      |

|---------|-----------------------------------------|------------|----------------------------------------------|

| SSI0    | PA5/SSI0Tx<br>PA4/SSI0Rx<br>PA3/SSI0Fss | $\uparrow$ | PA4/SSI0Rx<br>PA5/SSI0Tx SSI0<br>PA3/SSI0Fss |

|         | PA2/SSI0Clk                             |            | PA2/SSI0Clk                                  |

|         | GND                                     |            | GND                                          |

**Part a)** Assume the master (one on the left) has **SPH**=0, **SPO** =1, and **DSS**=7 in the **SSIO\_CRO\_R** register. What are the correct configurations for **SPH**, **SPO**, and **DSS** in the slave (one on the right)?

**Part b)** The master will be calling  $SSI_Out$  inside a periodic ISR, so we have to assure the time to complete the ISR is short and bounded. Assume the SSI is idle and the master calls  $SSI_Out N$  times in order to transmit N bytes to the slave. What is the maximum value that N can be so that the master is guaranteed that the busy-wait loop in  $SSI_Out$  never spins? Assume the software is faster (bus clock at 80 MHz) than the SSI hardware (SSI clock at 1 MHz). Justify your answer.

Hardware FIFO queue can hold 8 frames, so ISR can output 8 times without stalling

**Part c**) Which pins in the hardware interface can be disconnected and still have the interface function as described? If no pin can be removed, specify none. If multiple pins could be removed, list them all.

(15) Question 4. This software increments the counter on the falling edge of PC4. Edit the following two functions so the counter is incremented on the **rising edge** of **PC6** instead of the falling edge of PC4. Change the priority to level 1. Cross out parts of the code you wish to delete and insert necessary additions.

```

volatile uint32_t Counter = 0;

void EdgeCounter Init(void){

SYSCTL_RCGCGPIO_R |= 0 \times 04;

Counter = 0;

GPIO_PORTC_DIR_R &= ~<del>0x10</del>; 0x40;

GPIO PORTC DEN R = \frac{0 \times 10}{0 \times 40}; \frac{0 \times 40}{0 \times 40};

GPIO_PORTC_IS_R &= ~<del>0x10;</del> 0x40;

GPIO_PORTC_IBE_R &= ~0 \times 10; 0 \times 40;

GPIO PORTC IEV R \&= ~0x10; = 0x40; // rising

GPIO_PORTC_IM_R = \frac{0 \times 10}{0 \times 40}; \frac{0 \times 40}{0 \times 40};

NVIC PRIO R=(NVIC PRIO R&0xFF00FFF)

NVIC ENO R = 4;

EnableInterrupts();

}

void GPIOPortC Handler(void){

GPIO_PORTC_ICR_R = \frac{0 \times 10}{0 \times 40};

Counter = Counter + 1;

}

```

$V_{in} \xrightarrow{InF} \stackrel{R}{\leqslant} \stackrel{R}{\underset{lk}{R}}$

*V*<sub>out</sub>

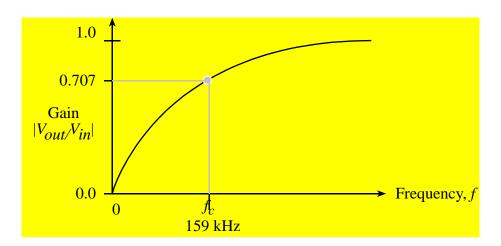

(15) Question 5. Consider the following circuit with a 1-nF capacitor and a 1-k $\Omega$  resistor. (5) Part a) Derive a relationship for the gain  $(V_{out}/V_{in})$  as a function of frequency, *f*. Show your work.

$Z_{c} = 1/(j2\pi fC). Z_{r} = R. \text{ Ohms Law } V_{out}/V_{in} = Z_{r}/(Z_{r} + Z_{c})$   $V_{out}/V_{in} = R/(R + 1/(j2\pi fC)) = (j2\pi f R C)/(1 + j2\pi f R C)$   $||V_{out}/V_{in}| = (2\pi f R C)/\text{sqrt}(1 + (2\pi f R C)^{2}) = (f/f_{c})/\text{sqrt}(1 + (f/f_{c})^{2})$ where  $f_{c} = 1/(2\pi R C) = 159 \text{ kHz}$

(5) Part b) Draw a rough plot of the gain versus frequency for the circuit. Include three points, f=0, f at the point where is gain is sqrt(2)/2=0.707 and at very large f.

(5) Part c) Assume  $V_{in}$  is limited between 0 and 1 V. Can we connect  $V_{out}$  to the ADC input of the TM4C123 microcontroller? If yes, justify your answer. If no, explain why not. No, the HPF will shift the signal to  $-\frac{1}{2}$  to  $+\frac{1}{2}$  V (10) Question 6. Write the C code to implement the following equation using fixed-point math Y = sqrt(0.3)\*X

Floating point is not allowed. The sqrt(0.3)  $\approx 0.5477225575051661134569697828008$ . X and Y are 16-bit signed integers stored in global variables. Make it as accurate as possible without causing overflow during an intermediate calculation.

```

// choose 54772 so intermediate calculation does not overflow

// -32768*54722 and +32767*54722 both fit into a 32-bit register

// reduces by a factor of 0.54, so the result will fit into 16-bit Y

Y = (54772*X)/100000;

```

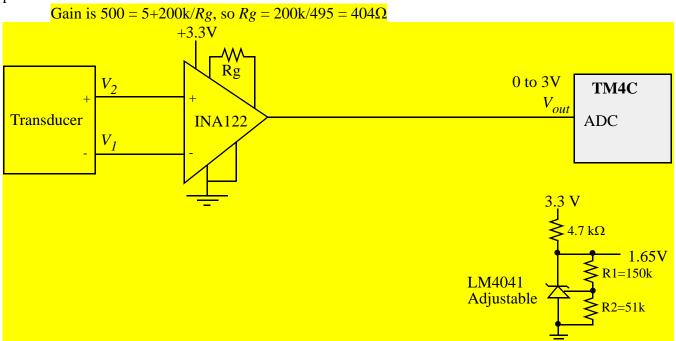

(15) Question 7. Design an analog circuit that implements  $V_{out} = 500*V_2 - 500*V_1$ . The information in the signal is encoded as the difference between  $V_2$  and  $V_1$ . The output,  $V_{out}$ , is connected to the microcontroller ADC. You may assume the inputs are bounded such that  $V_{out}$  will be between 0 and 3V. R1 and R2 are already chosen such that the analog reference is 1.65V. You may use any chips shown in the book or presented in class. Show your work and label all chip numbers and resistor values. You do not have to show pin numbers.