# **CMOS processing**

# With help from David Szmyd, Silicon Labs

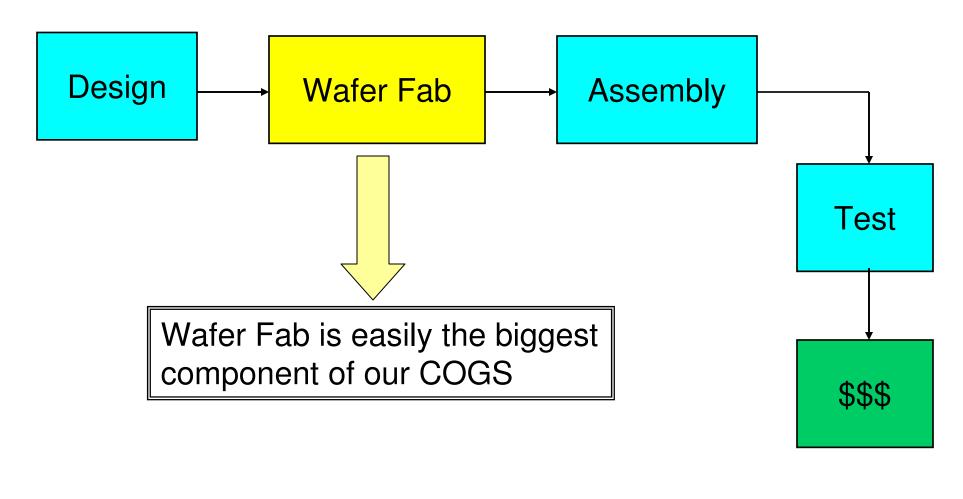

## **Where Does Wafer Fab Fit into Product Flow?**

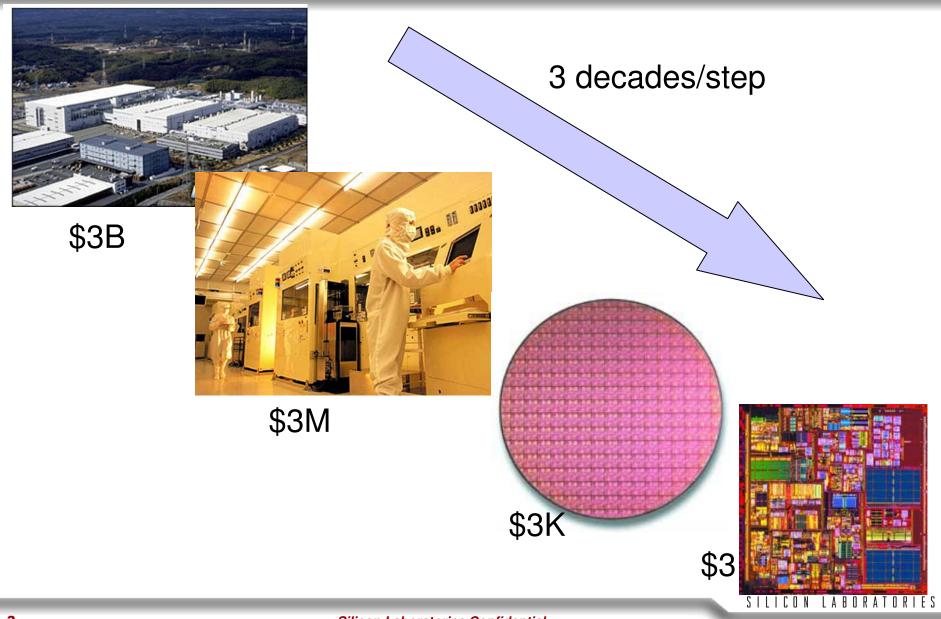

## What is a Wafer Fab?

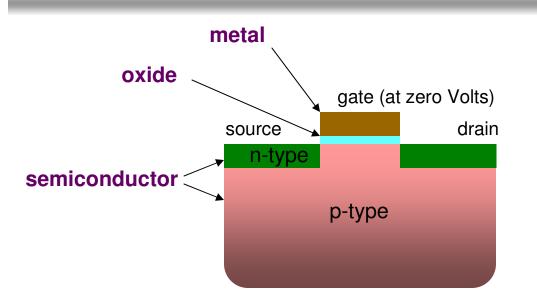

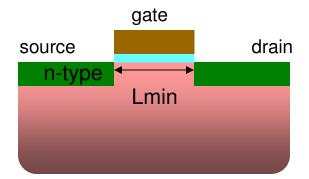

## **MOS Transistor Cross Section**

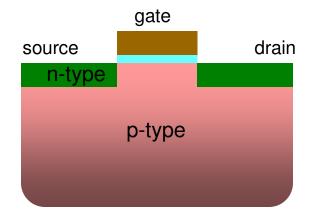

Electrons in source cannot flow to the drain because p-type region is a barrier. Transistor is OFF.

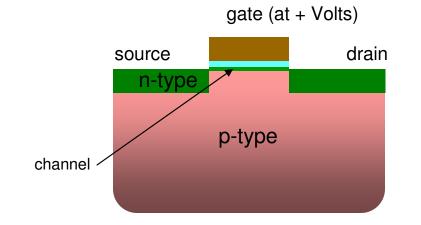

Apply positive voltage to gate. Attracts electrons to oxide, forming n-type channel. Now, electrons have a continuous path from source to drain. Transistor is ON.

Silicon Laboratories Confidential

# **CMOS: Complementary MOS**

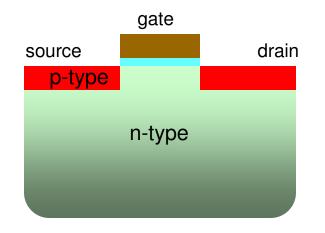

#### NMOS: S, D and channel are n-type

#### PMOS: S, D and channel are p-type

- Can combine NMOS and PMOS so that when one is on, the other is off.

- No current flows because one device is always off. Saves power!!

- Exception: Current flows only when devices are switching.

- Devices are complementary  $\rightarrow$  CMOS.

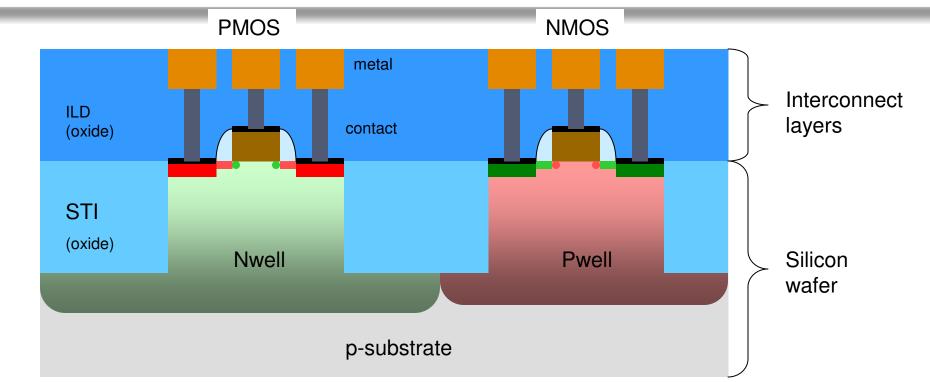

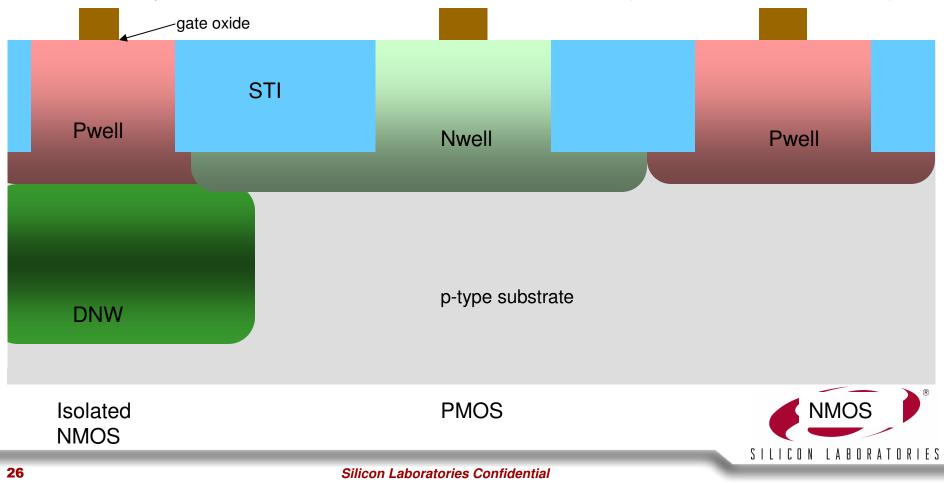

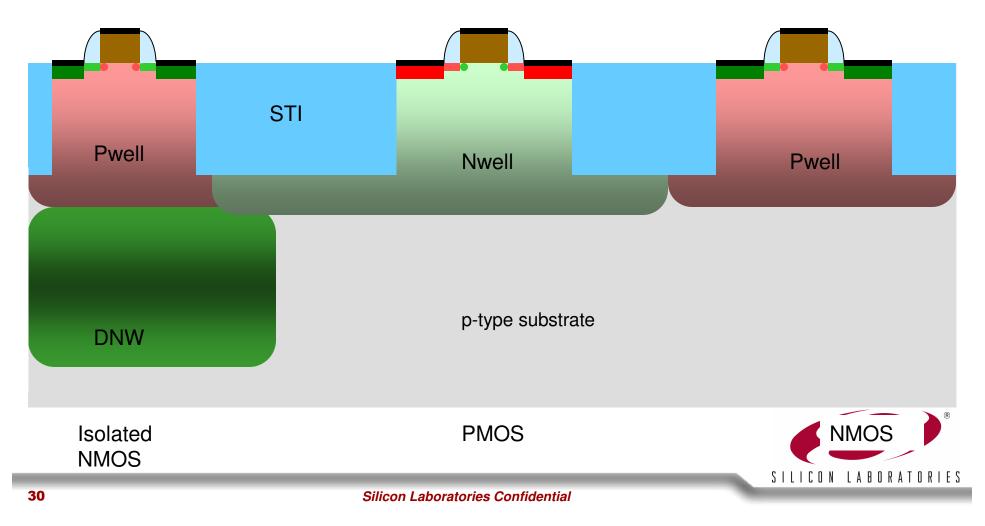

# **CMOS Integration**

- Devices are built into a common p-type substrate (wafer).

- Shallow Trench Isolation (STI) provides electrical isolation between devices.

- Metal and contacts provide access to the device terminals S, D, G.

- Multiple levels of metal lines are routed to interconnect the devices  $\rightarrow$  form a circuit on a chip.

- Capacitors, resistors and inductors can also be integrated.

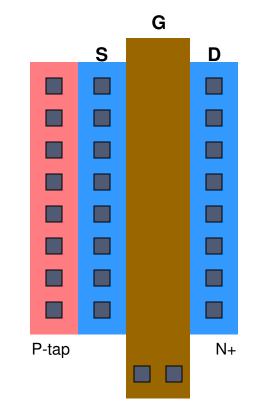

# **Transistor Layout**

NMOS with separate well tap poly crossing G STI edge. Gate oxide weakest S D here. cross section - -P-tap N+ contacts to poly must be field oxide over field oxide

NMOS with well tap shorted to source by the silicide

Silicon Laboratories Confidential

# **Technology Nodes**

Technology defined by minimum allowed gate length.

Shorter gates  $\rightarrow$  faster transistors (100 GHz) and denser circuits. Each node increases density by ~2x.  $0.5\mu m \rightarrow 0.35\mu m \rightarrow 0.25\mu m \rightarrow 0.18\mu m \rightarrow 0.13\mu m$

• At finer nodes, all features shrink: contact size, metal width, oxide thickness, etc.

• In 0.13um, gate oxide thickness is only 20A (about a dozen SiO<sub>2</sub> molecules).

| Part  | Function | Tech   | Contact | M1 L/S      | # metals | # masks | Size                 |

|-------|----------|--------|---------|-------------|----------|---------|----------------------|

| chip1 | example1 | 0.5µm  | 0.5µm   | 0.6/0.6µm   | 3        | 16      | 4.62 mm <sup>2</sup> |

| chip2 | Example2 | 0.35µm | 0.4µm   | 0.5/0.45µm  | 4        | 21      | 6.07 mm <sup>2</sup> |

| chip3 | Example3 | 0.35µm | 0.4µm   | 0.5/0.45µm  | 4        | 30      | 8.95 mm <sup>2</sup> |

| chip4 | Example4 | 0.25µm | 0.3µm   | 0.32/0.32µm | 4        | 23      | 5.5 mm <sup>2</sup>  |

| chip5 | Example5 | 0.18µm | 0.22µm  | 0.23/0.23µm | 5        | 23      | 6.51 mm <sup>2</sup> |

| chip6 | Example6 | 0.13µm | 0.16µm  | 0.16/0.18µm | 8        | 37      | 2.93 mm <sup>2</sup> |

# **Wafer Fabrication**

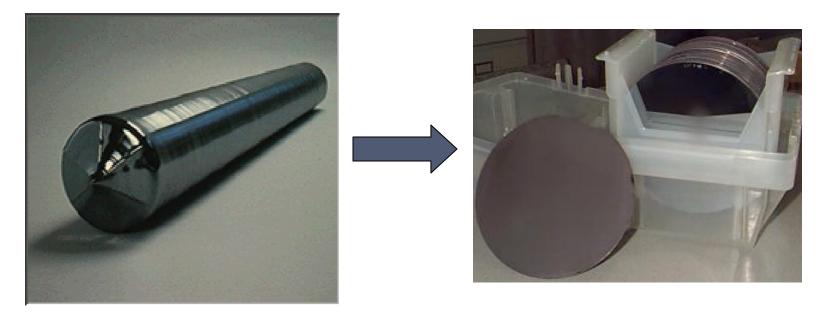

- Armed with photomasks and starting substrates, the foundry can now fabricate the wafers.

- Starting substrates are cut and polished from huge single crystals of silicon. Not done by the foundries.

# **Basic Process Steps**

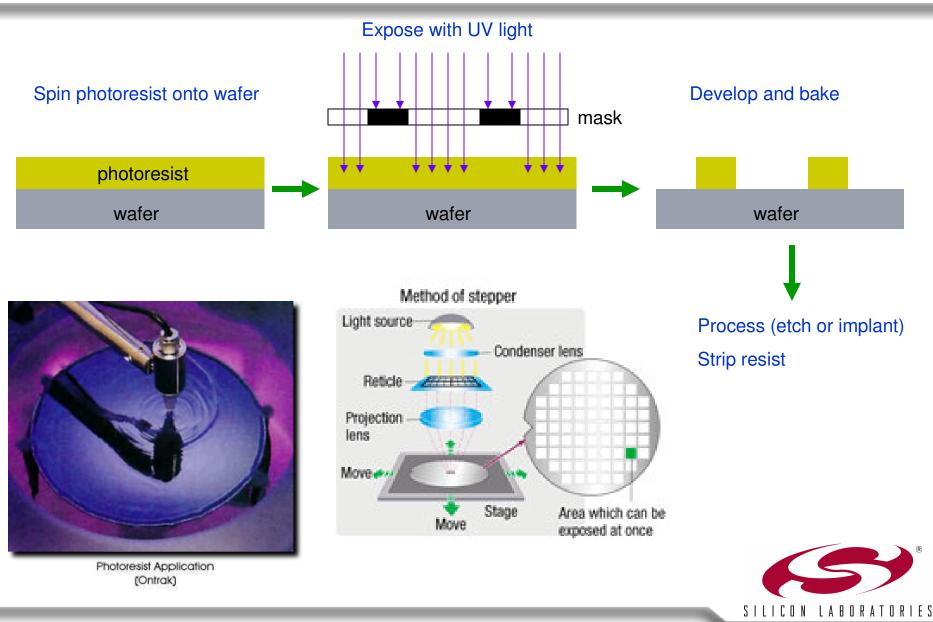

- Photolithography transfer mask pattern to wafer

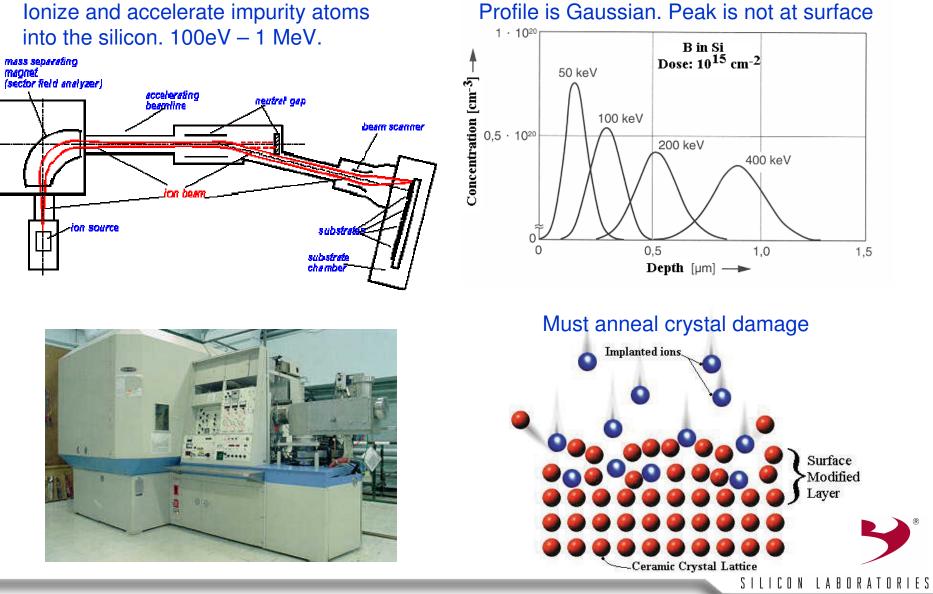

- Implant shoot impurities into the silicon

- Diffusion anneal implant damage, grow oxide

- Deposition deposit layers (oxides, metals, etc.)

- Etch remove unwanted material

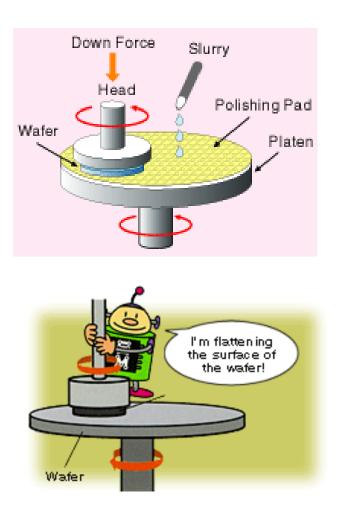

- CMP chemo-mechanical polishing. Removes unwanted material by polishing, leaving the wafer flat.

# **Photolithography**

Silicon Laboratories Confidential

# **Ion Implantation**

Silicon Laboratories Confidential

# **Deposition**

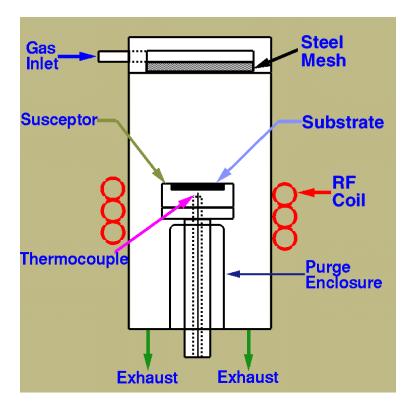

#### **Chemical Vapor Deposition**

- React source gases inside chamber.

- RF plasma (usually)

- Reduced pressure

- Used for oxides and polysilicon, epitaxy.

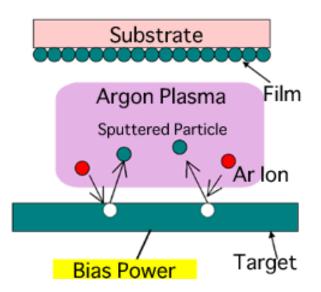

#### Sputter material from a target onto the wafer

- RF plasma + magnetron.

- Argon ions physically dislodge target atoms.

- Good for depositing metals.

- Can add O<sub>2</sub> for reactive sputtering.

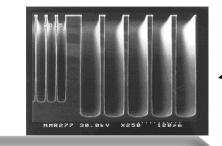

# Etch

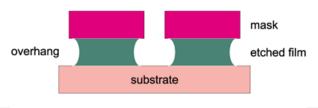

#### Wet Etch

- Dip wafers boat in HF acid to remove oxide

- Isotropic

ISOTROPIC ETCHING

#### Etching Region

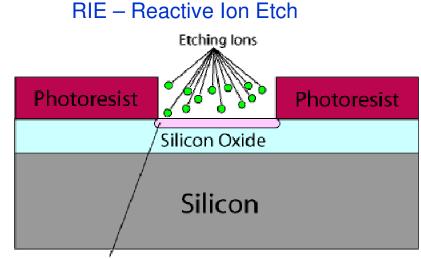

- Use reactive ions like Cl<sup>-</sup> or F<sup>-</sup> to etch material.

- Single wafer tool.

- Want high selectivity.

- Usually want high anisotropy.

Silicon Laboratories Confidential

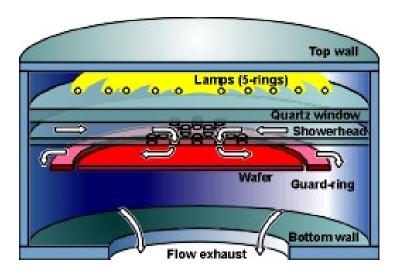

# **Diffusion**

#### Furnace

- Used for long anneal or alloy

- Grow gate oxide

- Batch mode

#### **RTP-** Rapid Thermal Process

- Heat wafer extremely fast with IR lamps. Soak time of a few seconds.

- Used for impurity activation. Impurities have no time to move.

- Uniform

- Can grow films

- Single wafer tool

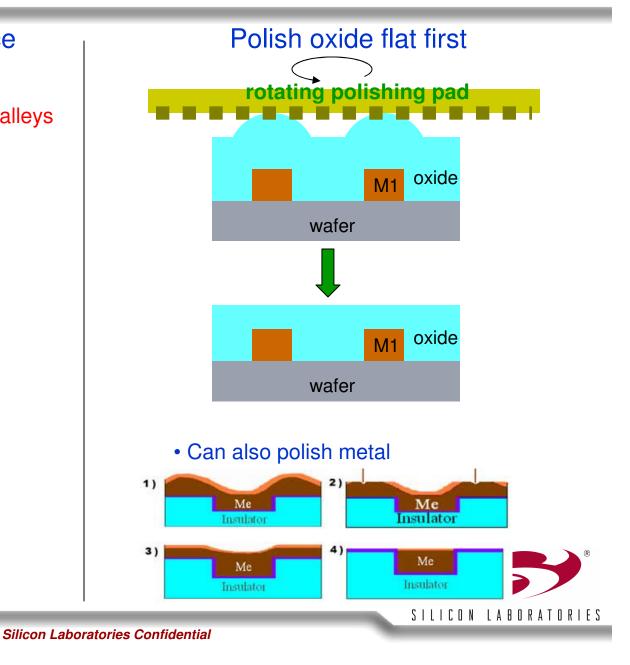

# **CMP: Chemo-Mechanical Polishing**

# Nonplanar wafer surface hard to etch away metal in valleys

- Lowers yields.

- Limits number of interconnect layers to 2 or 3.

- Limits spacing between lines.

## **CMP Tools**

#### **CMP** Tool

• Dirty - kept apart from other tools

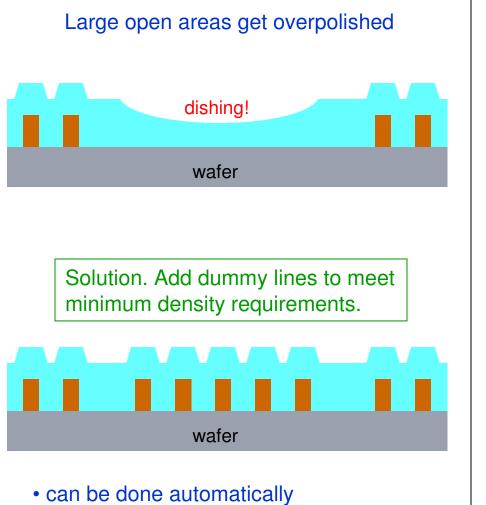

# **CMP Density Limitation** $\rightarrow$ **DFM**

• increases parasitic capacitance

#### Wide metal lines get overpolished

# **Process Flow**

- Integrate all the previous process steps top make realize a fully processed wafer with an array of functional die.

- 0.13um process with Cu interconnect.

- Two halves

- Frontend: from bare wafer to transistors with S/D/G electrodes.

- Backend: interconnect layers (metals and vias) for wiring the devices.

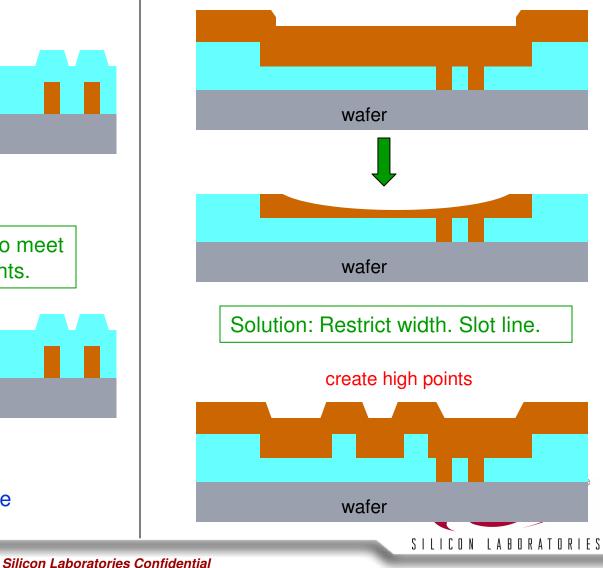

# **Starting Wafer**

Starting Oxide

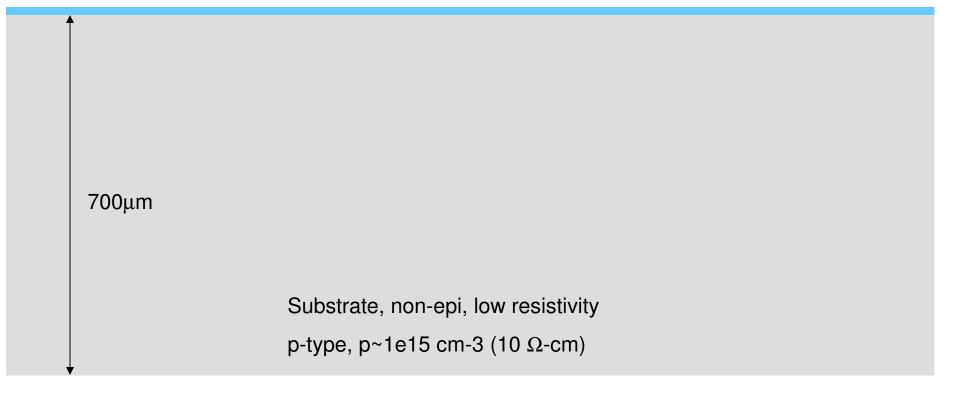

## **Etch Global Alignment Marks**

Silicon Laboratories Confidential

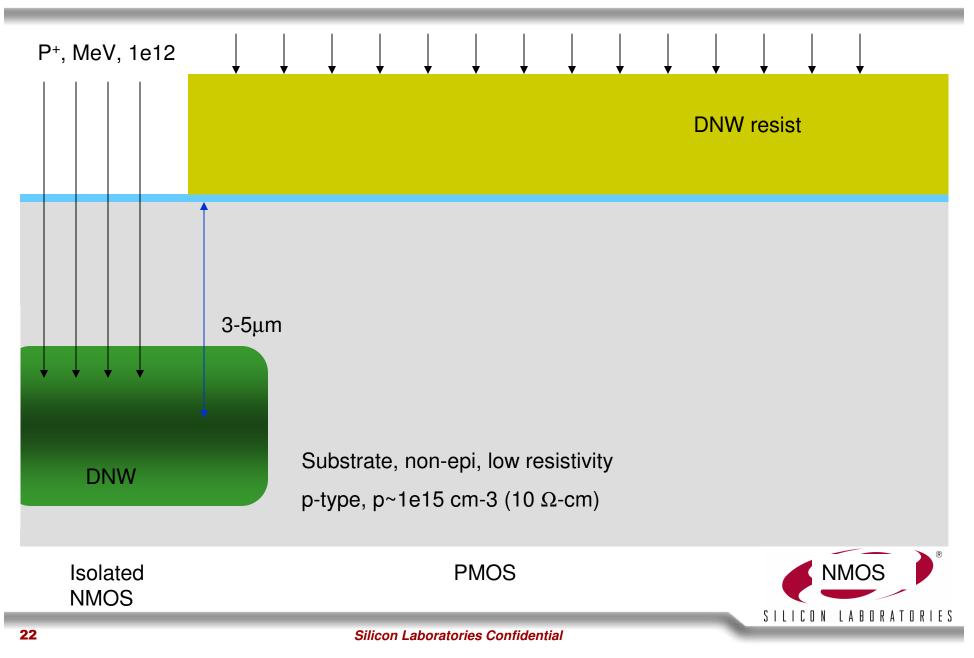

## **DNW** Mask: Deep Nwell $\rightarrow$ Isolation

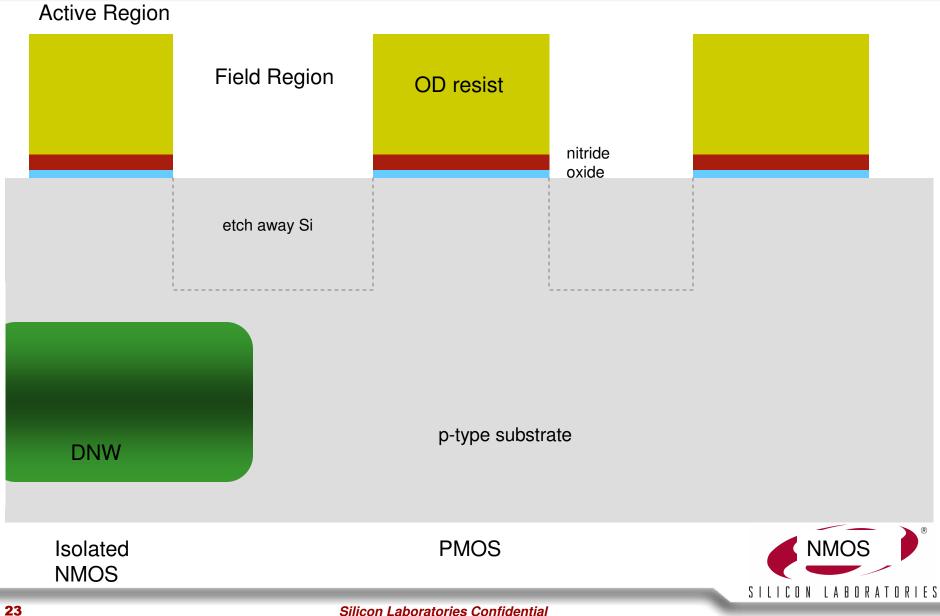

# **OD** Mask/Etch: Oxide Definition $\rightarrow$ Field Oxide

Silicon Laboratories Confidential

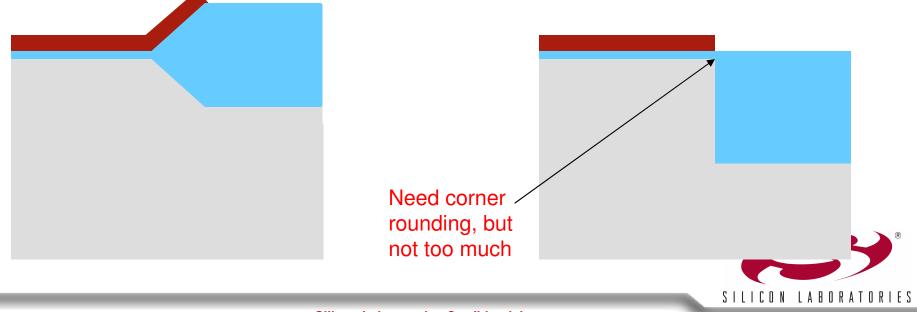

# **Field Oxide: STI or LOCOS**

#### LOCOS

(Local Oxidation of Silicon)

- High temperature oxidation

- Bird's beak  $\rightarrow$  edge ill-defined

- Coarse pitch. No narrow field oxide

- Partially Recessed. Non-planar

- Old, 0.35um and higher

### NEW: STI

(Shallow Trench Isolation)

- Si etch, Oxide overfill, <u>CMP</u> back

- Flat, planar

- Low temperature

- Fine pitch

- New, 0.25um and lower

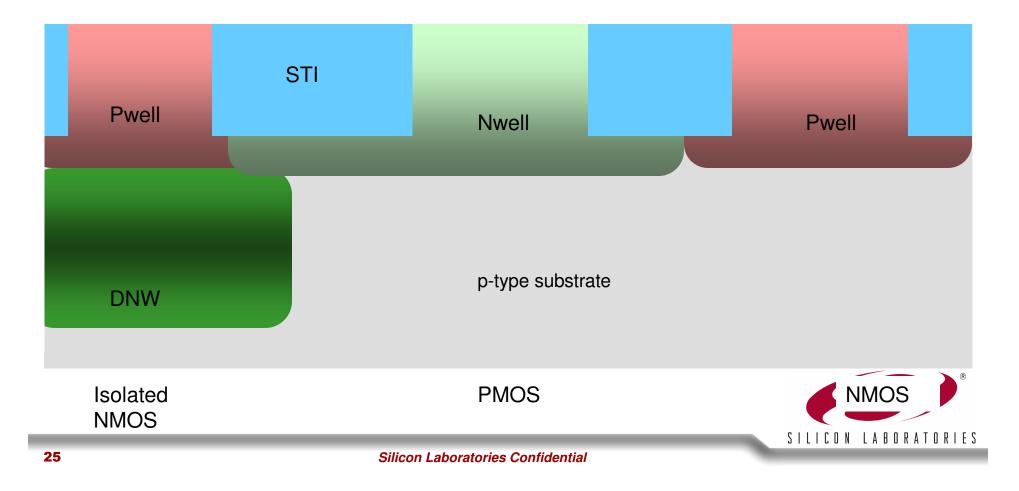

## **PW and NW Masks: Nwell and Pwell Formation**

- 2-3 implants/mask, B/In for Pwell, As/P for Nwell

- If process has dual Vdd, then core and I/O have separate wells

- Also, Vt adjust implants for LV and HV flavors of core transistors

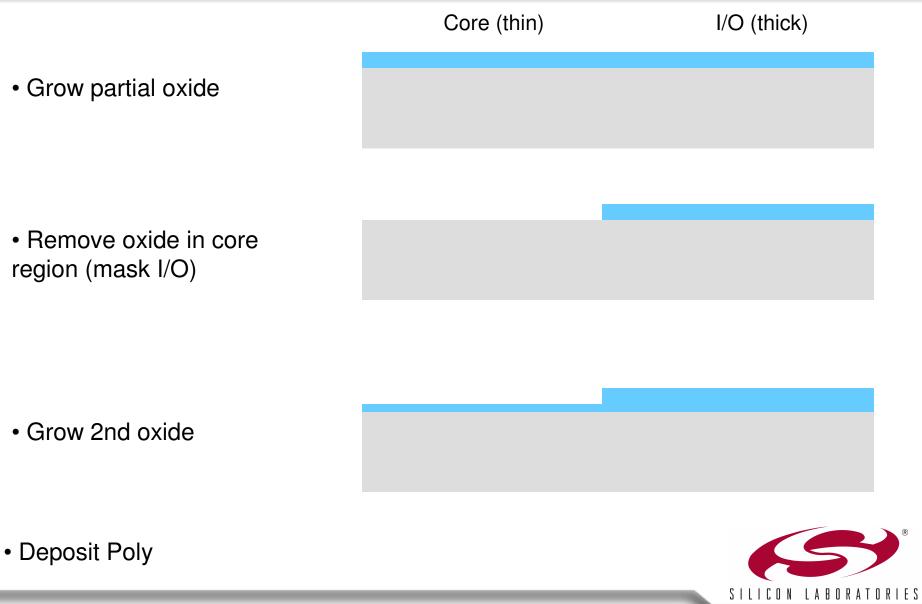

# **Gate Oxide and Poly**

- Grow gate oxide (could be dual oxide)

- Deposit Polysilicon (gate material)

- Etch Poly. Width is the transistor L. Control is critical (CD = Critical Dimension)

# **Dual Gate Oxide: Core and I/O Transistors**

Silicon Laboratories Confidential

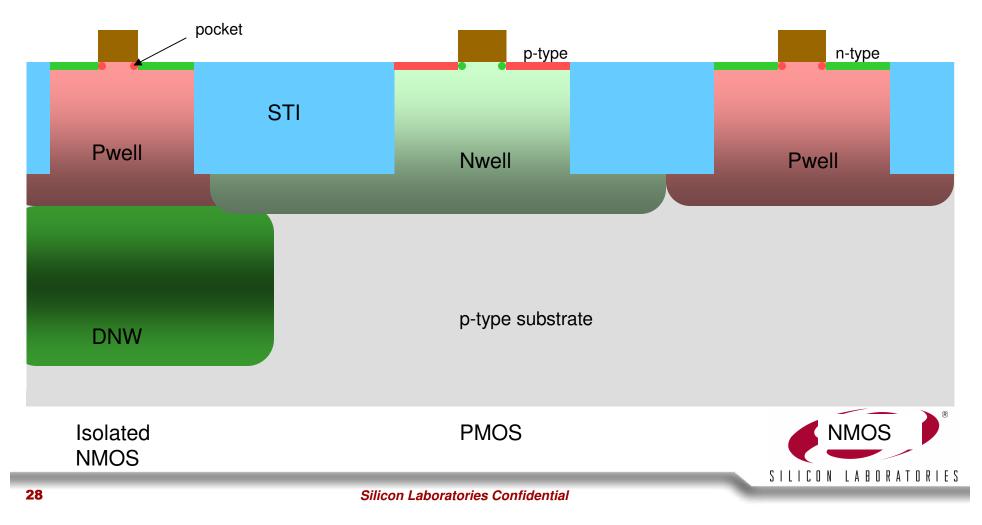

# **LDD and Pocket Implants**

- Self-aligned to gate poly.

- Pocket: extra well doping to prevent Vt rolloff. Angled to get under gat poly.

- LDD: Lightly-Doped Drain. Reduces electric field and hot-carriers at drain.

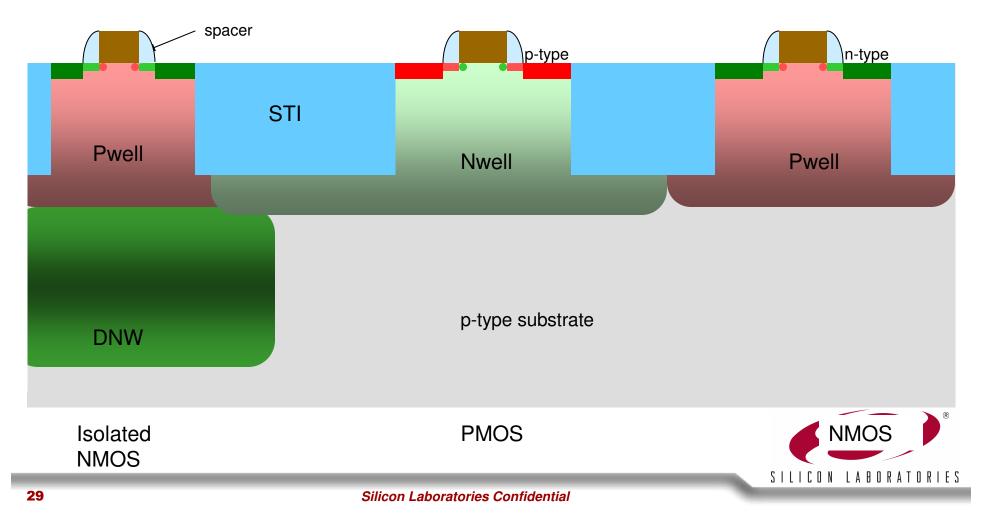

# **Spacer and Extrinsic Drain**

- Spacer protects LDD. About 0.1um 0.2um wide.

- Spacer: TEOS only or nitride/oxide bilayer stack.

- Heavy extrinsic implants for low Rseries. Also dopes the poly.

# **Silicide Formation**

- Self-aligned to diffusion regions and poly.

- TiSi (0.25um and above), CoSi (0.18um to 90nm), NiSi (65nm)

- Deposit  $\rightarrow$  React  $\rightarrow$  Strip  $\rightarrow$  Convert to low resistance phase

## **Prevent Silicide with RPO Layer**

- Before sputtering silicide metal, deposit oxide.

- Remove oxide where silicide is needed. Block oxide etch with RPO mask for resistors.

| before strip      |            | after conversion |                      |  |  |

|-------------------|------------|------------------|----------------------|--|--|

|                   |            |                  |                      |  |  |

| resistor top view |            |                  |                      |  |  |

|                   | < ₩ →<br>L |                  |                      |  |  |

|                   |            |                  | (S) <sup>®</sup>     |  |  |

|                   |            |                  | SILICON LABORATORIES |  |  |

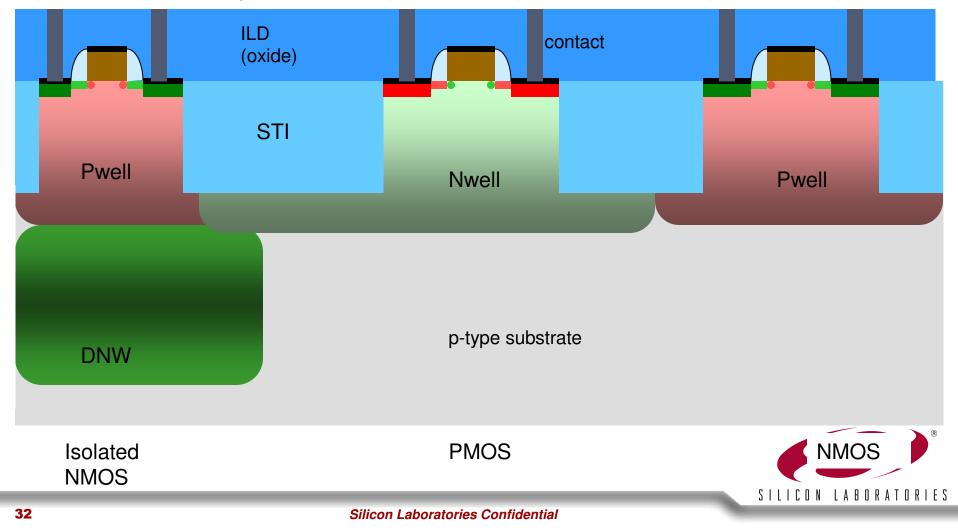

# **Contact Formation**

- Deposit ILD oxide and CMP flat

- Usually W-plug

- Etch hole  $\rightarrow$  Deposit W  $\rightarrow$  CMP flat

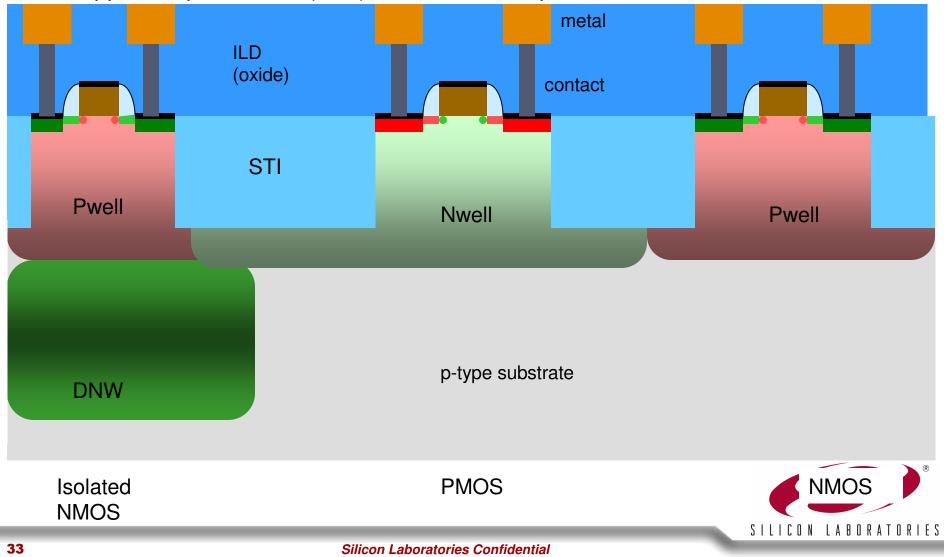

# **Metal1**

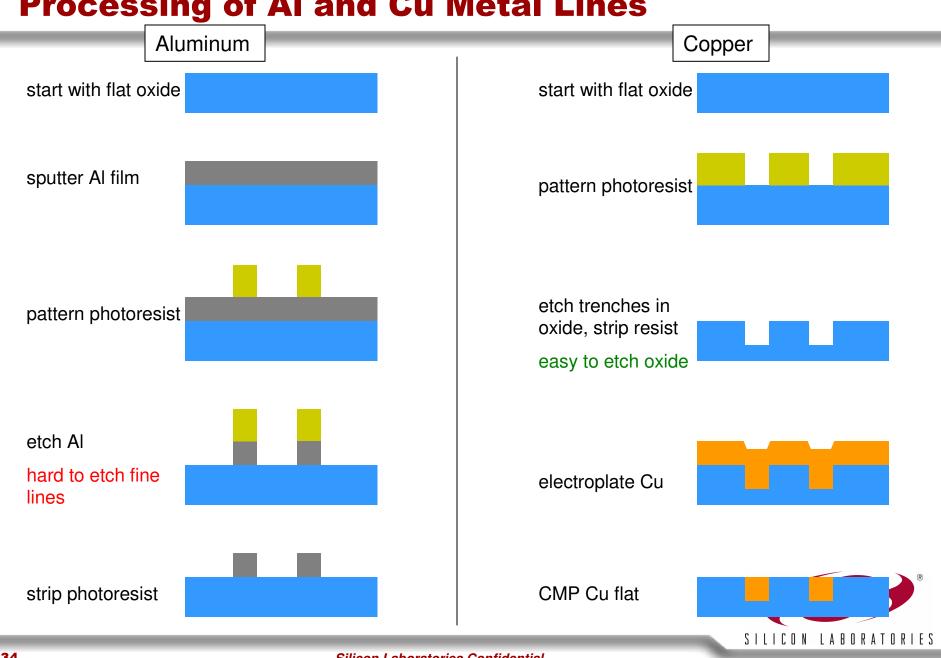

- Aluminum: Deposit metal, mask and etch.

- Copper: Deposit oxide (IMD), etch trench, deposit metal, CMP flat

## **Processing of AI and Cu Metal Lines**

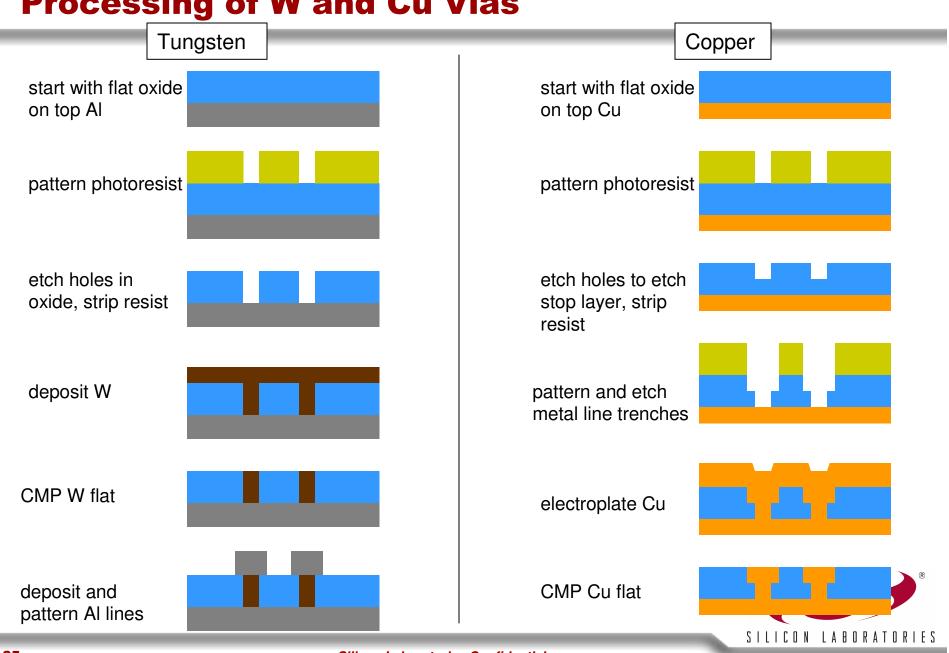

## **Processing of W and Cu Vias**

Silicon Laboratories Confidential

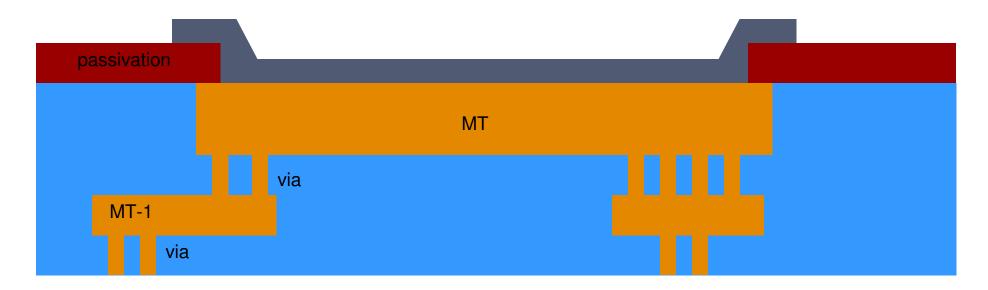

# **Passivation and bondpads**

- Repeat metal and via processing steps to complete interconnect.

- Deposit passivation (nitride) and etch.

- For Cu, deposit Al wirebond layer and etch.

- For P49, route Al layer to bump (redistribution of bondpads)

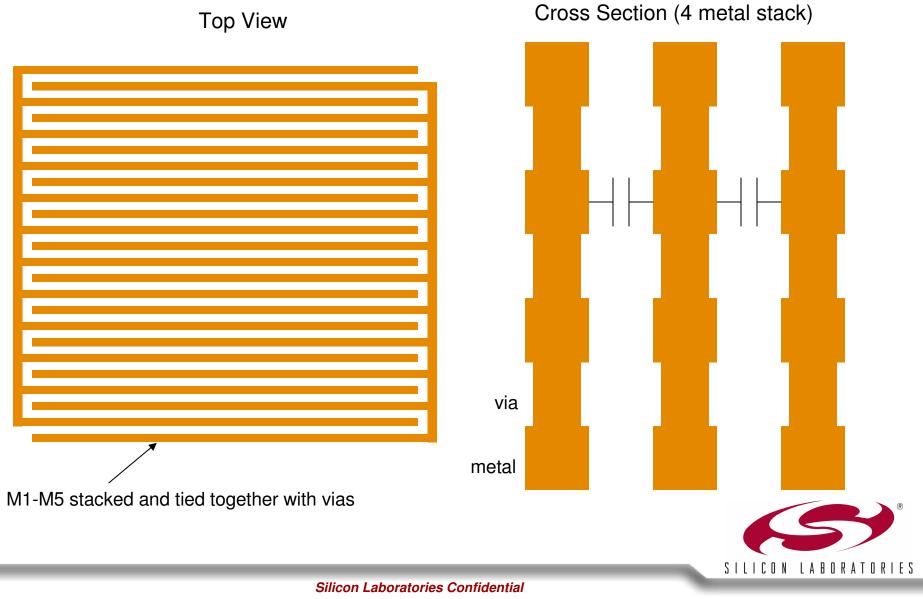

# **Metal Finger Capacitors**

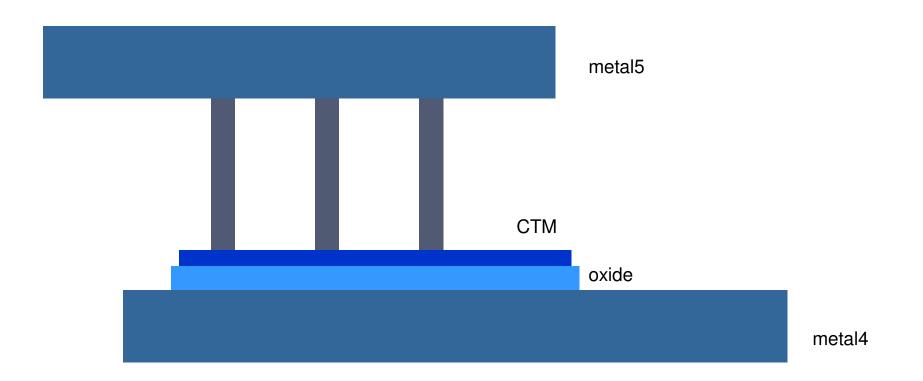

# **MIM Capacitor**

- Above MIMcap uses existing metal for bottom plate. This style found in 0.18um and higher. Requires one mask for CTM

- For 0.13um process, cannot use copper as a bottom plate. Instead, separate CBM layer is added. Two masks required.