**Department of ECE**

Laboratory for Computer Architecture

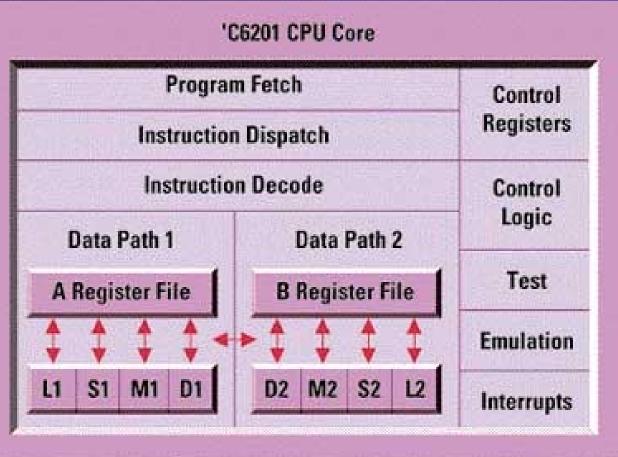

#### **VLIW Processors**

- Very Long Instruction Word

- Single Instruction specifies more than one concurrent operation

- > Instruction width is quite large taking many bits to encode multiple operations

- > Rely on software to pack the collection of operations (Compaction)

- > In code with limited instruction parallelism, most of the instruction is wasted with no operations

- TI's TMS320C6x series, Analog Device's TigerSHARC\* and Lucent+Motorola's StarCore

#### VLIW Processors (continued...)

Laboratory for Computer Architecture

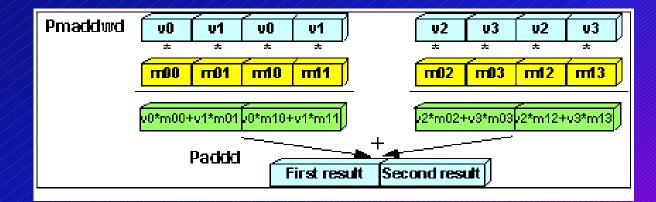

#### **SIMD Processors**

- Single Instruction Multiple Data

- Exploit data parallelism as opposed to instruction parallelism in VLIW processors

- A technique that has been added to generalpurpose processors for DSP and multimedia processing

> Intel's MMX, Sun's VIS, Motorola's AltiVec

#### **SIMD Processors** (continued...)

| Packed |     |      |         |         |       |     |    |    |    |    |    |    |   |   |  |

|--------|-----|------|---------|---------|-------|-----|----|----|----|----|----|----|---|---|--|

| 63     | 56  | 55   | 48      | 47      | 48    | 39  | 32 | 31 | 24 | 23 | 16 | 15 | 8 | 7 |  |

|        |     |      |         |         |       |     |    |    |    |    |    |    |   |   |  |

| Packed | WØ  | eds  | (4 x 16 | i bits) | 1     |     |    |    |    |    |    |    |   |   |  |

| 63     |     |      | 48      | 47      |       |     | 32 | 31 |    |    | 16 | 15 |   |   |  |

|        |     |      |         |         |       |     |    |    |    |    |    |    |   |   |  |

| Packed | đe  | ubla | e ward: | s (2 x  | 32 bi | ts) |    |    |    |    |    |    |   |   |  |

| 63     |     |      |         |         |       |     | 32 | 31 |    |    |    |    |   |   |  |

|        |     |      |         |         |       |     |    |    |    |    |    |    |   |   |  |

| Quadwo | und | (64  | bits)   |         |       |     |    |    |    |    |    |    |   |   |  |

| 63     |     |      |         |         |       |     |    |    |    |    |    |    |   |   |  |

|        |     |      |         |         |       |     |    |    |    |    |    |    |   |   |  |

**Department of ECE**

Laboratory for Computer Architecture

## **Motivation/What's the deal?**

- Over 90% of future workloads are expected to be multimedia oriented

- Multimedia applications have good instruction and data parallelism -> VLIW and SIMD are a good bet

- Very few existing literature on evaluation of such applications

- Have to benchmark important kernels and complete applications

# Frequently asked Q & A !!

- What is it that is being evaluated?

- Evaluate a VLIW representative and a SIMD representative -> C6x and Pentium II (MMX)

- What are the benchmarks that will be used?

- DSP and multimedia kernels and applications (more details in a later slide)

- What are the tools that will used?

- For the C6x -> C6x compiler, Stand-alone simulator, and the simulator & debugger

- For the Pentium II -> VTune and Performance Counters

## Frequently asked Q & A !! (continued...)

- What would be final conclusion? Something like the C6x is better than Pentium II or vice versa!

- > C6x is meant for low cost embedded solutions while the Pentium II is a general-purpose processor for PC/desktop use

- **‡** Comparison would be between apples and oranges

- **‡** Either processor is not a replacement for the other

- ‡ Which is why the title is "SIMD and VLIW" and not "SIMD vs VLIW"!

- > The goal is to evaluate two techniques using one representative processor for each

# Frequently asked Q & A !! (continued...)

- Are these two techniques not orthogonal?

- > Yes, they are and both can be implemented in a single processor -> ADI's TigerSHARC is something like that

- > We might see more processors like that in the future, but for now the idea is to use the state-ofthe-art processors using one of these techniques

- > Therefore, this is not a comparison between a DSP and a general-purpose processor in the strict sense, but surely some insight can be gained into high-performance DSPs versus high-purpose general-purpose processors

## **Benchmarks**

#### • Kernels

- > Dot-product, matrix-vector products

- > **FIR and IIR filters**

- > **FFT and DCT**

- Applications

- > Speech compression algorithms (G.721, 722, 723..)

- > Image Processing applications (JPEG, GIF, blurring..)

- > **3D graphics**

- > Video processing (MPEG, H.261, 263..)

## Methodology

- Use relevant C code and respective compilers and evaluate metrics of interest (execution time, number of instructions..)

- But MMX instructions are not generated by compilers in general -> try CodeWarrior

- Resort to libraries where ever applicable (this means optimized assembly)

## References

- [1] R. Bhargava, L. John, B. Evans and R. Radhakrishnan, "Evaluating MMX Technology Using DSP and Multimedia Applications", *Proceedings of IEEE Micro-31*, Dec 1998.

- [2] P. Ranganathan, S. Adve and N. Jouppi, "Performance of Image and Video Processing with General-Purpose Processors and Media ISA Extensions", *To appear in Proceedings of International Symposium on Computer Architecture-26*, 1999.

- [3] C. Lee, M. Potkonjak and W.H. Mangione-Smith,

"MediaBench: A Tool for Evaluating and Synthesizing Multimedia and Communications Systems", *Proceedings of IEEE Micro-30*, Dec 1997.

Research in Laboratory for Computer Architecture!