Copyright

by

Kyungtae Han

2006

The Dissertation Committee for Kyungtae Han certifies that this is the approved version of the following dissertation:

# Automating transformations from floatingpoint to fixed-point for implementing digital signal processing algorithms

| Committee:                 |

|----------------------------|

| Brian L. Evans, Supervisor |

| Ross Baldick               |

| Margarida F. Jacome        |

| Earl E. Swartzlander, Jr.  |

| Robert A. van de Geijn     |

# Automating transformations from floatingpoint to fixed-point for implementing digital signal processing algorithms

by

Kyungtae Han, B.S., M.S.

## DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm August~2006}$

Dedicated to my wife Jinyoung, my mother Sunmin, and my father Changseob.

## Acknowledgments

On completing this dissertation I give my special thanks to my parents. They have devoted themselves to backing me up since the beginning of my life. I would then like to thank my wife for her support as I completed this dissertation. And to Obed I express my great joy to have him in my life.

I would like to thank my advisor, Dr. Brian L. Evans, for his support and guidance in academic, financial, and everyday issues. He helped and supported me in getting in, getting through, and getting out of UT Austin. Without him, this dissertation could not have been completed. He has my deepest respect professionally and personally.

I would like to thank my committee members, Dr. Ross Baldick, Dr. Margarida F. Jacome, Dr. Earl E. Swartzlander, Jr. and Dr. Robert A. van de Geijn (in alphabetical order). I am honored to have them serve on my committee. Dr. Baldick teaches an optimization course, which influenced me as I derived the formulation used in this dissertation. Dr. Swartzlander influenced my approach to low-power consumption and the hardware modeling of arithmetic units in this dissertation. Software design methods from Dr. van de Geijn and Dr. Jacome had a profound impact on my development of automated transformation software.

I would like to thank Dr. Wonyong Sung at Seoul National University

and Dr. Iksu Eo at the Electronics and Telecommunications Research Institute

(ETRI). My initiation into research came about by my taking Dr. Sung's VLSI

class, and my work in algorithm development began under the tutelage of

Dr. Eo.

I would like to thank the researchers at Intel, Inc., where I did my

internship. Besides giving me a great learning experience, my internship gave

me the opportunity to undertake a project and give presentations. I would

like to express thanks to my mentor, Mr. Keith R. Tinsley, who guided me to

a successful project completion. In all, my experience at Intel accelerated the

completion of this dissertation.

I would like to thank Dr. Greg Rohling. His comments on multiob-

jective evolutionary algorithm have been helpful to multiobjective wordlength

optimization in this dissertation.

I would like to thank my groupmates in Embedded Signal Processing

Laboratory (ESPL) and the Wireless Networking and Communications Group

(WNCG). I learned much from our many valuable discussions.

Last but not least, I would like to thank God for blessing me with the

completion of this dissertation.

KYUNGTAE HAN

The University of Texas at Austin

August 2006

vi

Automating transformations from floatingpoint to fixed-point for implementing digital signal processing algorithms

Publication No.

Kyungtae Han, Ph.D. The University of Texas at Austin, 2006

Supervisor: Brian L. Evans

Many digital signal processing and communication algorithms are first simulated using floating-point arithmetic and later transformed into fixed-point arithmetic to reduce implementation complexity. This transformation process may take more than 50% of the design time for complex designs. In addition, wordlengths in fixed-point designs may be altered at later stages in the design cycle. Different choices of wordlengths lead to different tradeoffs between signal quality and implementation complexity.

In this dissertation, I propose two methods for characterizing the tradeoffs between signal quality and implementation complexity during the transformation of digital system designs to fixed-point arithmetic and variables. The first method, a gradient-based search for single-objective optimization with sensitivity information, scales linearly with the number of variables, but

vii

can become trapped in local optima. Based on wordlength design case studies for a wireless communication demodulator, adding sensitivity information reduces the search time by a factor of four and yields a design with 30% lower implementation costs.

The second method, a genetic algorithm for multi-objective optimization, provides a Pareto optimal front that evolves towards the optimal tradeoff curve for signal quality vs. implementation complexity. This second method can be used to fully characterize the design space.

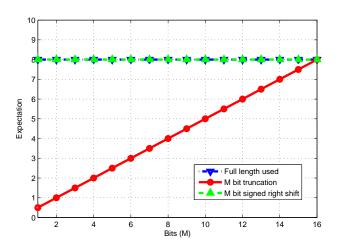

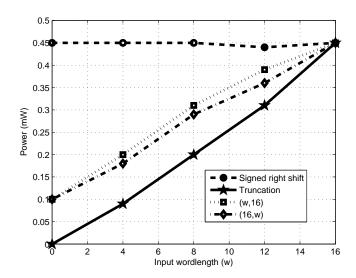

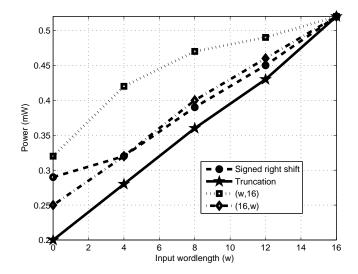

I propose to use wordlength reduction methods of signed right shift and truncation to reduce power consumption in a given hardware architecture. For each method, I derive the expected values of the number of gates that switch during multiplication of the inputs. I apply the signed right shift method and the truncation method to a 16-bit radix-4 modified Booth multiplier and a 16-bit Wallace multiplier. The truncation method with 8-bit operands reduces the power consumption by 56% in the Wallace multiplier and 31% in the Booth multiplier. The signed right shift method shows a 25% power reduction in the Booth multiplier, but no power reduction in the Wallace multiplier.

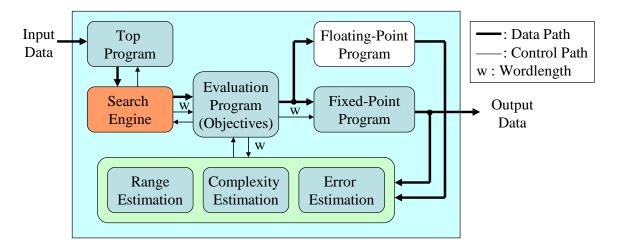

Finally, this dissertation describes a method to automate design assistance for transformation from floating-point to fixed-point data types. Floating-point programs are converted to fixed-point programs by a code generator. Then, the proposed wordlength search algorithms offer designers the freedom to determine data wordlengths to optimize the tradeoffs between signal quality and implementation complexity.

# **Table of Contents**

| Ackno   | wledg | ments                                 | $\mathbf{v}$ |

|---------|-------|---------------------------------------|--------------|

| Abstra  | act   |                                       | vii          |

| List of | Table | es                                    | xiii         |

| List of | Figu  | res                                   | xiv          |

| Chapt   | er 1. | Introduction                          | 1            |

| 1.1     | Motiv | vation of This Study                  | . 1          |

| 1.2     | Thesi | s Statement                           | . 5          |

| 1.3     | Contr | ributions                             | . 5          |

| 1.4     | Outli | ne of Dissertation                    | . 6          |

| 1.5     | Notat | tion                                  | . 8          |

| 1.6     | Acror | nyms                                  | . 8          |

| Chapt   | er 2. | Background                            | 11           |

| 2.1     | Fixed | l-Point Data Format                   | . 11         |

| 2.2     | Relat | ed Work                               | . 12         |

| 2.3     | Optin | num Wordlength                        | . 15         |

|         | 2.3.1 | Formulation of Optimum Wordlength     | . 15         |

|         | 2.3.2 | Finding Optimum Wordlength            | . 16         |

| 2.4     | Revie | ew of Simulation-Based Search Methods | . 17         |

|         | 2.4.1 | Complete Search                       | . 17         |

|         | 2.4.2 | Exhaustive Search                     | . 18         |

|         | 2.4.3 | Sequential Search                     | . 20         |

|         | 2.4.4 | Preplanned Search                     |              |

|         | 2.4.5 | Case Study                            | . 24         |

|         | 2.4.6 | Comparison                            | . 28         |

| 2.5   | tic Algorithms | 31                                                                   |    |

|-------|----------------|----------------------------------------------------------------------|----|

|       | 2.5.1          | Multi-Objective Evolutionary Optimization                            | 32 |

|       | 2.5.2          | Pareto Rank                                                          | 33 |

|       | 2.5.3          | Wordlength Optimization with Multi-Objective Evolutionary Algorithms | 34 |

| 2.6   | Sumn           | nary                                                                 | 36 |

| Chapt | er 3.          | Wordlength Optimization for Hardware Implementation                  | 38 |

| 3.1   | Intro          | duction                                                              | 38 |

| 3.2   | Sensit         | tivity Measurements                                                  | 38 |

|       | 3.2.1          | Complexity Measure (CM)                                              | 39 |

|       | 3.2.2          | Distortion Measure (DM)                                              | 40 |

|       | 3.2.3          | Complexity-and-Distortion Measure (CDM)                              | 41 |

| 3.3   | Case           | Study                                                                | 42 |

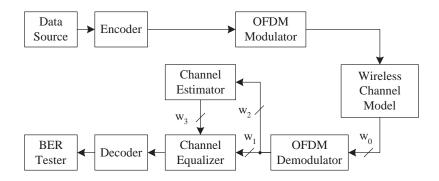

|       | 3.3.1          | Orthogonal Frequency Division Multiplexing Demodulator Design        | 42 |

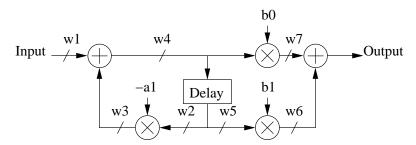

|       | 3.3.2          | Infinite Impulse Response Filter                                     | 46 |

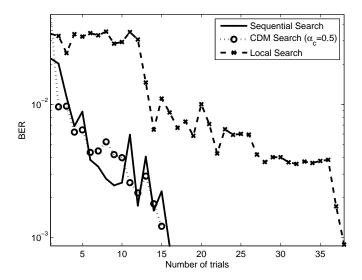

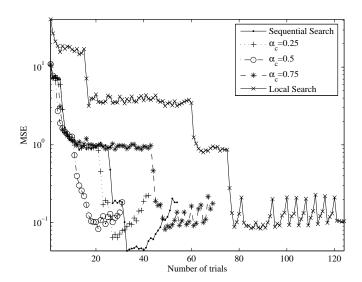

| 3.4   | Resul          | ts of Sensitivity Measurements                                       | 46 |

|       | 3.4.1          | Number of Iterations                                                 | 48 |

|       | 3.4.2          | Hardware Complexity                                                  | 51 |

|       | 3.4.3          | Discussion                                                           | 52 |

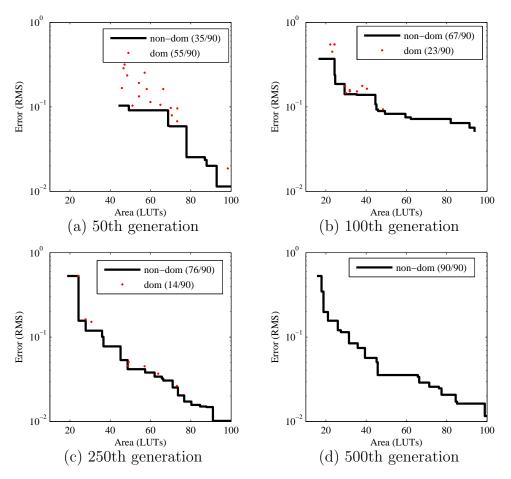

| 3.5   | Resul          | ts of Genetic and Evolutionary Algorithms                            | 53 |

| 3.6   | Comp           | parison                                                              | 56 |

| 3.7   | Sumn           | nary                                                                 | 61 |

| Chapt | er 4.          | Wordlength Reduction for Lowering Power Consumption                  | 63 |

| 4.1   | Intro          | duction                                                              | 63 |

| 4.2   | Word           | length Reduction                                                     | 64 |

| 4.3   | Power          | r Consumption                                                        | 65 |

|       | 4.3.1          | Power Analysis                                                       | 65 |

|       | 4.3.2          | Software Power Minimization                                          | 67 |

|       | 433            | Minimizing Wordlength for Low Power                                  | 68 |

|            | 4.3.4   | Power Reduction via Wordlength Reduction                 | 69  |

|------------|---------|----------------------------------------------------------|-----|

| 4.4        | Expe    | ctation of Switching                                     | 70  |

|            | 4.4.1   | L-Bit Input                                              | 71  |

|            | 4.4.2   | N-Bit Truncated Data in $L$ -Bit Input                   | 72  |

|            | 4.4.3   | Signed Right Shift                                       | 72  |

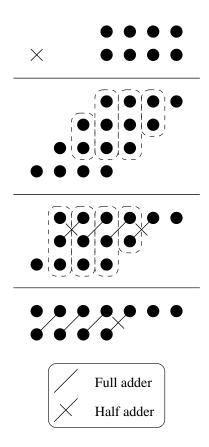

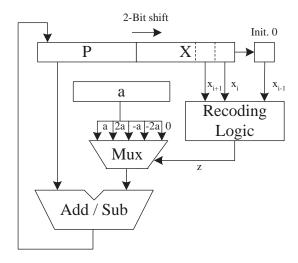

| 4.5        | Multi   | plier                                                    | 76  |

|            | 4.5.1   | Wallace Multiplier                                       | 76  |

|            | 4.5.2   | Radix-4 Modified Booth Multiplier                        | 76  |

| 4.6        | Simul   | ation Results                                            | 78  |

| 4.7        | Sumn    | nary                                                     | 82  |

| Chapt      | er 5.   | Automating Transformation to Fixed Point in Soft-        |     |

| F 1        | T., 4., | ware                                                     | 83  |

| 5.1        |         | duction                                                  | 83  |

| 5.2        |         | ed Work                                                  | 84  |

|            | 5.2.1   | Fixed-Point Simulation Environment                       | 84  |

| <b>F</b> 0 |         | Wordlength Optimization                                  | 85  |

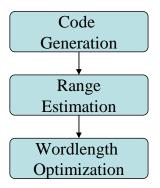

| 5.3        |         | mating Transformation from Floating Point to Fixed Point | 86  |

|            | 5.3.1   | Code Generation                                          | 87  |

|            | 5.3.2   | Range Estimation                                         | 89  |

|            | 5.3.3   | Optimum Wordlength Search                                | 90  |

| 5.4        |         | Study                                                    | 90  |

| 5.5        | Sumn    | nary                                                     | 97  |

| Chapt      | er 6.   | Conclusion                                               | 99  |

| 6.1        | Sumn    | nary                                                     | 99  |

| 6.2        | Futur   | e Work                                                   | 102 |

|            | 6.2.1   | Advanced Wordlength Search Algorithms                    | 102 |

|            | 6.2.2   | Further Analysis on Search Algorithms                    | 104 |

|            | 6.2.3   | Low Power Consumption                                    | 105 |

|            | 6.2.4   | Electronic Design Automation Software                    | 106 |

|            | 6.2.5   | Optimum DSP Algorithms                                   | 107 |

|            | 6.2.6   | Area Model                                               | 108 |

| Bibliography | 109 |

|--------------|-----|

| Vita         | 126 |

## List of Tables

| 1.1 | Research on floating-point to fixed-point transformation                                                         | 3   |

|-----|------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Notation used in this dissertation                                                                               | 8   |

| 2.1 | Fixed-point conversion approaches for integer wordlength (IWL) and for fractional wordlength (FWL) determination | 13  |

| 2.2 | Optimum Wordlength Search Methods                                                                                | 15  |

| 2.3 | Sequence of the sequential search for CDMA demodulator                                                           | 29  |

| 2.4 | Comparison of complete, exhaustive, sequential, and preplanned search                                            | 30  |

| 2.5 | Advantages/disadvantages of wordlength search algorithms in this chapter                                         | 37  |

| 3.1 | Simulation results of several search methods                                                                     | 46  |

| 3.2 | Simulation results in IIR filter of several search methods                                                       | 48  |

| 3.3 | Simulation results in noise cancellation with Wiener filter                                                      | 52  |

| 4.1 | Expectation of switching in $L$ bit input                                                                        | 75  |

| 4.2 | Radix-4 Booth's recoding                                                                                         | 79  |

| 6.1 | Advantages/disadvantages of wordlength search algorithms                                                         | 100 |

# List of Figures

| 2.1  | The possible wordlength combinations from searching the entire space in a complete search                                                                           | 18 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | The direction of Exhaustive Search                                                                                                                                  | 20 |

| 2.3  | The direction of the sequential search                                                                                                                              | 22 |

| 2.4  | The direction of the preplanned search                                                                                                                              | 24 |

| 2.5  | Analog and digital demodulators in CDMA receiver and performance measurement position                                                                               | 25 |

| 2.6  | A digital demodulator block                                                                                                                                         | 26 |

| 2.7  | Result of the independent one-variable simulations on a CDMA demodulator                                                                                            | 27 |

| 2.8  | Genetic and Evolutionary Algorithms                                                                                                                                 | 32 |

| 2.9  | Pareto front in two objectives                                                                                                                                      | 34 |

| 3.1  | Wordlength model for a fixed-broadband wireless access demodulator                                                                                                  | 43 |

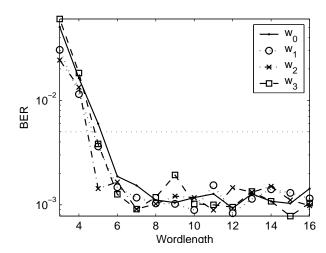

| 3.2  | Wordlength effect for the demodulator                                                                                                                               | 45 |

| 3.3  | First-order direct form-II IIR filter                                                                                                                               | 47 |

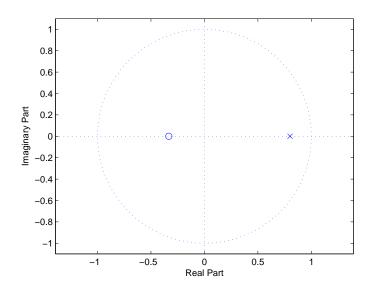

| 3.4  | Pole/zero plot for the IIR filter                                                                                                                                   | 47 |

| 3.5  | Number of iterations for optimum wordlength with various search algorithms in OFDM demodulator wordlength design                                                    | 49 |

| 3.6  | Number of iterations for optimum wordlength in IIR filter with various search algorithms                                                                            | 50 |

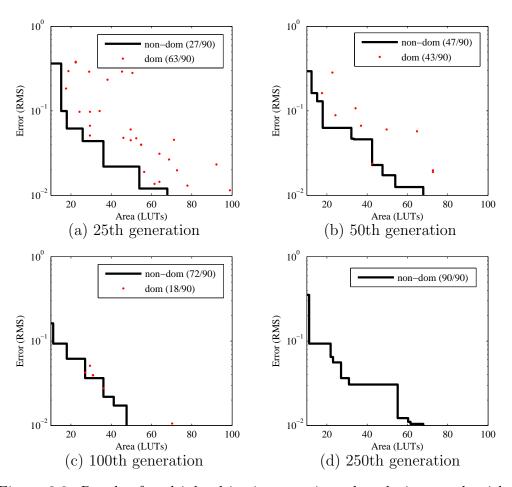

| 3.7  | Results of multiple objective genetic and evolutionary algorithms in the IIR filter case study with seven wordlength variables                                      | 55 |

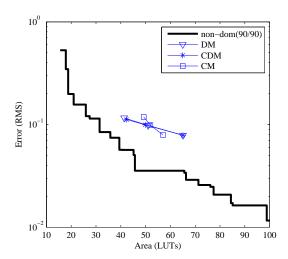

| 3.8  | Result of multiple objective genetic and evolutionary algorithms in the IIR filter case study with three wordlength variables                                       | 57 |

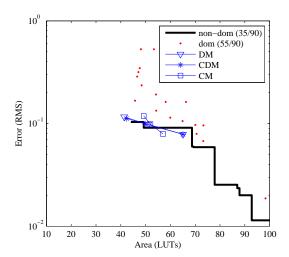

| 3.9  | Overlap genetic evolutionary algorithm results in 50th generation with gradient-based search results for the IIR filter case study with seven wordlength variables  | 58 |

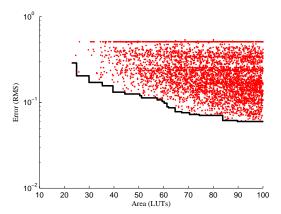

| 3.10 | Overlap genetic evolutionary algorithm results in 500th generation with gradient-based search results for the IIR filter case study with seven wordlength variables | 59 |

|      |                                                                                                                                                                     |    |

| 3.11 | Result of random search algorithm in the IIR filter study with seven wordlength variables    |

|------|----------------------------------------------------------------------------------------------|

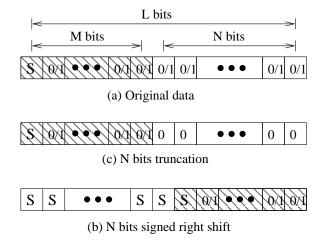

| 4.1  | Example of 8-bit data wordlength reduction                                                   |

| 4.2  | Bit operation in effective bits, $M. S$ is a signed bit                                      |

| 4.3  | Expectation of number of switching bits in inputs                                            |

| 4.4  | Dadda dot diagram for a 4-bit Wallace multiplier                                             |

| 4.5  | A Radix-4 multiplier based on Booth's recoding                                               |

| 4.6  | Dynamic power consumption in 16-bit $\times$ 16-bit Wallace multiplier (1MHz)                |

| 4.7  | Dynamic power consumption in 16-bit $\times$ 16-bit Radix-4 modified Booth multiplier (1MHz) |

| 5.1  | Three phases in automating transformation from floating point to fixed point                 |

| 5.2  | Conversion to fixed point by a code generator                                                |

| 5.3  | Automated transformation environment                                                         |

| 5.4  | Example of MAC floating-point program                                                        |

| 5.5  | Automatically converted fixed-point code for MAC                                             |

| 5.6  | Generated MAC cost function                                                                  |

| 5.7  | Generated MAC objective function                                                             |

| 5.8  | Generated MAC top file                                                                       |

| 5.9  | Main batch file for code generation                                                          |

## Chapter 1

## Introduction

## 1.1 Motivation of This Study

Digital signal processing algorithms are typically simulated in floating-point environments for refinement and validation. After validation, the algorithms can be implemented in floating-point hardware or transformed to run on fixed-point hardware. Implementation on floating-point hardware offers the direct use of floating-point programs without conversion. However, when compared to implementation on floating-point hardware, implementation on fixed-point hardware offers lower economic cost, lower power consumption, and faster speed, but with a tradeoff in signal quality. In addition, off-line transformation from floating-point programs to fixed-point programs must be performed.

Fixed-point transformation requires data-type conversion from floating point to fixed point. A fixed-point data type represents a limited range of data compared to that of a floating-point data type. During fixed-point transformation, proper ranges to prevent overflow and underflow at each variable are estimated. Based on range-estimation information, wordlengths in the fixed-point data types can be modified to reduce hardware complexity or

power consumption. Modification can be either manual by trial-and-error or automated by computer methods.

Floating-point to fixed-point transformation, including data-type conversion and wordlength optimization, which is mostly wordlength reduction, is time-consuming and can sometimes account for up to 50% of the total design effort [1]. Hence, many studies have been performed on fixed-point transformation methods, as shown in Table 1.1.

Many fixed-point environments have been developed to simulate fixed-point signal processing systems. Fixed-point simulation environments support fixed-point arithmetic and range estimation by analytical and/or statistical approaches [1–4]. Analytical estimation extracts data flow in a system and calculates the data ranges. Analytical estimation often produces conservative results. Statistical approaches, which monitor data ranges in variables through simulation, need much longer running times to collect signal statistics by simulation.

Wordlength optimization methods that determine bit widths of fixed-point variables with tradeoffs in signal quality and hardware complexity have been developed based on wordlength search methods [2, 10-13, 15]. Sung and Kum use a statistical approach for range estimation with the Signal Processing Worksystem (SPW) [5] for fixed-point simulation [2]. Fixed-point simulation environments for C++ have been developed in [3]. This environment provides range estimation class (fSig) and fixed-point data type and arithmetic class (gFix). Kum  $et\ al.\ [4]$  developed a program for converting a floating-point C

Table 1.1: Research on floating-point to fixed-point transformation. (SPW: Signal Processing Worksystem, HDS: Hardware Design System, FRIDGE: Fixed-point Programming Design Environment, MATCH: Matlab Compiler for Heterogeneous Computing Systems, MILP: Mixed Integer Linear Programming, CDM: Complexity-and-Distortion Measure)

| Paper        | Fixed- | point Conversion | W     | ordlength Optin | nization   |

|--------------|--------|------------------|-------|-----------------|------------|

|              | Range  | Environment      | Error | Search          | Search     |

|              | Est.   |                  | Est.  | Method          | Objective  |

| Sung [2]     | S      | SPW HDS [5]      | S     | Min+a           | Cost       |

| Kim [3]      | S      | fSig/gFix        | ı     | -               | -          |

| Kum [4]      | S      | Autoscaler       | ı     | -               | Shift      |

| Keding [1]   | A      | FRIDGE           | -     | -               | -          |

| Cmar [6]     | A/S    | -                | S     | -               | -          |

| Yama. [7]    | -      | -                | A/S   | -               | -          |

| Nayak [8]    | A      | MATCH [9]        | ı     | -               | -          |

| Han [10]     | -      | -                | S     | Seq./Preplan    | Error      |

| Cantin [11]  | -      | -                | S     | Max - 1         | Cost       |

| Const. [12]  | -      | -                | Α     | MILP/Heur.      | -          |

| Shi [13]     | -      | -                | A/S   | Mosek [14]      | Cost       |

| Han [15, 16] | -      | -                | S     | Seq./CDM        | Error/Cost |

| Proposed     | S      | MATLAB fi [17]   | S     | Genetic         | Error/Cost |

<sup>\*</sup> A: Analytical, S: Statistical, -: Not available

program to an integer C program with scaling optimization (AUTOSCALER) that minimizes the number of shifts in scaling operations. Keding et al. [1] proposed a fixed-point conversion tool using annotation and interpolation techniques that are employed in a commercial tool, CoCentric Fixed-point Designer [18]. Nayak et al. [8] implemented a forward and backward propagation algorithm that is used for the MATCH project [9] for analytical range estimation.

Signal quality in systems according to wordlength is estimated by an-

alytical or statistical approaches. Analytical approaches, which model and calculate propagated errors through fixed-point data types, could find solutions faster than statistical approaches for simple systems. However, modeling propagated errors in a closed form is sometimes difficult in complex systems. Statistical approaches measure propagated errors by simulation. Statistical approaches can be used for any system, but require long running times to measure errors.

Any consideration of all states of all possible wordlength combinations is generally impractical except for trivial systems. Wordlength optimization problems can be solved by optimization algorithms with search methods. Since statistical approaches require a long simulation time, accelerating the running time is one of the research topics in wordlength optimization.

Sung and Kum [2] proposed a wordlength search algorithm that first determined the minimum bound of the wordlength and then tried to determine the cost-optimal solution. Han et al. [10] proposed a sequential search algorithm utilizing error information based on the search algorithm from [2]. Cantin et al. [11] proposed the Max-1 algorithm, which starts with the maximum wordlength. In addition, Cantin et al. [11] provide a useful survey of search algorithms for wordlength determination, and compare wordlength search algorithms. Constantinides et al. [12] and Shi [13] employed mixed integer linear programming (MILP) and Mosek [14], respectively, to solve wordlength optimization problems. In [15,16], sequential search algorithms utilizing error and cost information were proposed.

This dissertation, which focuses mainly on wordlength search algorithms in fixed-point transformations, proposes a fast search algorithm utilizing gradient information. Genetic and evolutionary algorithms are employed to search a Pareto optimal set in multiple-objective wordlength optimization.

The dissertation also shows how to reduce power consumption with optimized wordlength for hardware multipliers. Finally, the dissertation presents a fully automated floating-point to fixed-point transformation environment supporting the proposed algorithms.

#### 1.2 Thesis Statement

This dissertation defends the following idea:

Wordlength search algorithms utilizing genetic and evolutionary algorithms can be used to automate floating-point to fixed-point transformations, in which data wordlengths can be determined to optimize the signal quality vs. implementation complexity tradeoffs. Alternately, wordlength search algorithms utilizing gradient information can provide faster ways to find data wordlengths but can get caught in local optima.

#### 1.3 Contributions

The research presented in this dissertation is focused on developing a fixed-point transformation framework that includes wordlength optimization. The primary contributions of this dissertation are the following:

- Development of wordlength optimization algorithms with search methods for multiple objectives as well as a single objective. I have developed fast search algorithms for a single objective utilizing gradient information to find data wordlength. I have also developed search algorithms for multiple objectives employing genetic and evolutionary algorithms to optimize the signal quality vs. implementation complexity tradeoffs. Thus, the Pareto optimal set can be searched through this algorithm.

- Development of low-power signal processing methods for embedded hardware and software. I propose wordlength reduction techniques to reduce power consumption, and I mathematically derive an expected value of switching activity in wordlength reduction techniques. The reduction in dynamic power consumption on FPGAs is estimated.

- Development of an automated floating-point to fixed-point transformation environment. I propose a transformation structure for this environment and develop transformation software, including a code generator and wordlength searchers. This software can automatically transform any floating-point program of digital signal processing to a fixed-point program. The software for this automatic transformation is available at <a href="http://www.ece.utexas.edu/~bevans/projects/wordlength/">http://www.ece.utexas.edu/~bevans/projects/wordlength/</a>

## 1.4 Outline of Dissertation

The dissertation is organized as follows.

Chapter 2 gives an overview of previous research on wordlength optimization and provides a mathematical definition of optimum wordlength. The chapter reviews simulation-based search algorithms and genetic and evolutionary algorithms and uses a case study to illustrate how to search wordlengths.

The proposed wordlength search algorithms utilizing gradient information are presented in Chapter 3. The proposed algorithms have been tested on an Orthogonal Frequency Division Multiplexing (OFDM) demodulator design and an Infinite Impulse Response (IIR) filter design. Case studies providing performance results of the proposed algorithms are discussed in terms of running time and hardware complexity. The results of multi-objective genetic and evolutionary algorithms are compared.

Shorter wordlengths in data can reduce power consumption in digital signal processing systems even though the hardware architecture is fixed. Chapter 4 presents two proposed methods for reducing power consumption by decreasing switching activity and derives mathematically the expected switching values at inputs. Chapter 4 also demonstrates and compares dynamic power reduction in FPGAs employing the methods.

Chapter 5 describes a proposed environment for a completely automating floating-point to fixed-point transformation. The wordlength optimization structure of the environment is presented. Chapter 5 illustrates the automating transformation with a case study.

Chapter 6 concludes the dissertation by highlighting the major contri-

Table 1.2: Notation used in this dissertation

|                                           | ole 1.2: Notation used in this dissertation     |

|-------------------------------------------|-------------------------------------------------|

| Notation                                  | Meaning                                         |

| $\alpha_c$                                | complexity weighting factor                     |

| $\alpha_d$                                | distortion weighting factor                     |

| c                                         | cost function                                   |

| $c_n(\mathbf{w})$                         | normalized complexity function                  |

| d                                         | sum of distance; L1 norm                        |

| dw                                        | distance between minimum and optimum wordlength |

| $d_n(\mathbf{w})$                         | normalized distortion function                  |

| $\int f$                                  | objective function                              |

| $\nabla$                                  | gradient of function                            |

| p                                         | performance function                            |

| s                                         | integer step size                               |

| $\mathbf{w} = [w_1,, w_n]$                | wordlength vector                               |

| w                                         | Wordlength                                      |

| $\overline{w}$                            | upper bound in $w$                              |

| $\underline{w}$                           | lower bound in $w$                              |

| $w^k$                                     | wordlength in $k$ th iteration                  |

| ξ                                         | integer update direction                        |

| $\frac{w}{w^k}$ $\xi$ $C_{req}$ $D_{req}$ | complexity constant                             |

| $D_{req}$                                 | required distortion                             |

| $I^n$                                     | n-dimensional integer space                     |

| $P_{req}$                                 | required performance                            |

butions from the research and discussing directions for future work.

## 1.5 Notation

The notation used in this dissertation is listed in Table 1.2.

## 1.6 Acronyms

ADC : analog-to-digital converter

BER : bit error rate

CM : complexity measure

CDM : complexity-and-distortion measure

CDMA : code division multiplex access

CMOS : complementary metal oxide semiconductor

CS : complete search

DSP : digital signal processing

DM : distortion measure

ES : exhaustive search

FER : frame error rate

FFT : fast Fourier transform

FPGA : field programmable gate array

FRIDGE: fixed-point programming design environment

FWL : fraction wordlength

GEA : genetic and evolutionary algorithm

HDS : hardware design system

IC : integrated circuit

IIR : infinite impulse response

IWL : integer wordlength

LPF : lowpass filter

LS : least significant

MAC : multiply and accumulate

MATCH: Matlab compiler for heterogeneous computing systems

MILP : mixed integer linear programming

MOEA : multi-objective evolutionary algorithm

MS : most significant

MSE : mean square error

OFDM : orthogonal frequency division multiplexing

PS : preplanned search

SNR : signal-to-noise ratio

SPW : signal processing worksystem

SRS : signed right shift

SS : sequential search

TI : Texas Instruments

WL : wordlength

## Chapter 2

## Background

## 2.1 Fixed-Point Data Format

When designers model at a high level, floating-point numbers are useful for modeling arithmetic operations. Floating-point numbers can handle a very large range of values, and they are easily scaled. In hardware, floating-point data types are typically converted or built as fixed-point data types to reduce the amount of hardware needed to implement the functionality. To model the behavior of fixed-point arithmetic hardware, designers need bit-accurate fixed-point data types.

Fixed-point data consists of an integer part and a fractional part. The number of bits assigned to the integer representation is called the integer wordlength (IWL), and the number of bits assigned to the fraction is the fractional wordlength (FWL) [19]. Fixed-point wordlength (WL) corresponds to the following equation:

$$WL = IWL + FWL \tag{2.1}$$

The wordlength must be greater than 0. Given IWL and FWL, fixed-point data represent a value in the range R with the quantization step  $\Delta$  as follows:

$$\begin{pmatrix} -2^{IWL} \le R < 2^{IWL} & \text{for signed} \\ 0 \le R < 2^{IWL} & \text{for unsigned} \end{pmatrix}$$

(2.2)

and

$$\Delta = 2^{-FWL}. (2.3)$$

IWL and FWL are determined to prevent unwanted overflow and underflow. IWL can be determined by the following relation:

$$IWL \ge \lceil \log_2 R \rceil. \tag{2.4}$$

Here,  $\lceil x \rceil$  is the smallest integer that is greater than or equal to x. The range R can be estimated by monitoring the maximum and minimum value or mean and the standard deviation of a signal [3, 20]. FWL can be determined by wordlength optimization or trade-offs in the design parameters during fixed-point conversion.

## 2.2 Related Work

During the floating-point-to-fixed-point conversion process, fixed-point wordlengths composed of the IWL and the FWL are determined by different approaches, as shown in Table 2.1. Some published approaches for floating-point-to-fixed-point conversion use an analytical approach for range and error estimation [8,12,13,21,22], and others use a statistical approach [3,6,13,23]. An analytical approach has a range and error model for integer wordlength and fractional wordlength design. Some use a worst-case error model for range estimation [8,21], and some use forward and backward propagation for IWL design [22]. The advantages of analytical techniques are that they do not

Table 2.1: Fixed-point conversion approaches for integer wordlength (IWL) and for fractional wordlength (FWL) determination.

(a) Analytical Approach

| Range Model for IWL  | Error Model for FWL      |

|----------------------|--------------------------|

| Wadekar 1998 [21]    | Constantinides 2003 [12] |

| Stephenson 2000 [22] | Shi 2004 [13]            |

| Nayak 2001 [8]       |                          |

(b) Statistical Approach

| Range Statistic for IWL | Error Statistic for FWL |

|-------------------------|-------------------------|

| Cmar 1999 [6]           | Cmar 1999 [6]           |

| Kim 1998 [3]            | Kum 2001 [23]           |

|                         | Shi 2004 [13]           |

require simulation stimulus and can be faster. However, they tend to produce more conservative wordlength results.

Statistical approaches have been used for IWL and FWL determination. Some use range monitoring for IWL estimation [3, 6], and some use error monitoring for FWL [6, 13, 23]. The work in [13] also uses an error model that has coefficients obtained through simulation. The advantage of statistical techniques is that they do not require a range or error model. However, they often need long simulation times and tend to be less accurate in determining wordlengths.

After obtaining models or statistics of range and error by analytical or statistical approaches, respectively, search algorithms can find an optimal wordlength. Some published methods search for optimal wordlength without sensitivity information [2, 24], whereas others do use sensitivity information [11, 24, 25], as shown in Table 2.2. "Exhaustive Search" [2] and "Branch-and-Bound" procedure [24] can find an optimum wordlength without any sensitivity information. However, non-sensitivity methods have an unrealistic search space as the number of wordlengths increases.

Some use sensitivity information to search for an optimum wordlength. The "Local Search" [24] and the "Evolutive Search" in [11] use cost-sensitivity information. The advantage of cost-sensitivity methods is that they can find an optimum wordlength in terms of cost. The "Sequential Search" and the "Preplanned Search" in [25] and the "Max-1 Search" in [11] use error-sensitivity information. The advantage of employing error-sensitivity methods is that they find the optimal wordlength in terms of error faster than cost-sensitivity methods. However, neither type of sensitivity method always reaches a globally optimal wordlength.

Cantin et al. provide a useful survey of search algorithms for wordlength determination. In this work, search algorithms are compared, and the Preplanned Search shows the smallest number of iterations to find a solution. However, the heuristic procedures do not necessarily capture the optimum solution to the wordlength determination problem, because of nonconvexity in the constraint space [12]. Thus, consideration is given to the distance between a globally optimal wordlength and a locally optimal wordlength.

Table 2.2: Optimum Wordlength Search Methods

| Cost Sensitivity                                    | Error Sensitivity      | Non-Sensitivity       |

|-----------------------------------------------------|------------------------|-----------------------|

| Local Search [24]                                   | Sequential Search [25] | Exhaustive Search [2] |

| Evolutive Search [26]                               | Max-1 Search [11]      | Branch and Bound [24] |

|                                                     | Preplanned Search [25] |                       |

| Complexity-and-Distortion Measure Search - proposed |                        |                       |

## 2.3 Optimum Wordlength

#### 2.3.1 Formulation of Optimum Wordlength

The wordlength is an integer value, and a set of n wordlengths in a system is defined to be a wordlength vector, that is,  $\mathbf{w} \in \mathbb{I}^n$  such as  $\{w_1, w_2, \dots, w_n\}$ . I assume that the objective function f is defined by the sum of every wordlength implementation cost function c as

$$f(\mathbf{w}) = \sum_{k=1}^{n} c_k(w_k) \tag{2.5}$$

where  $c_k$  has real value so that  $c_k : \mathbb{I} \to \mathbb{R}$ . The quantized performance function p indicates propagated precision or quantized error and is constrained as follows:

$$p(\mathbf{w}) \ge P_{req} \tag{2.6}$$

where p has real value so that  $p: \mathbb{I} \to \mathbb{R}$  and  $P_{req}$  is a constant for a required performance. I also consider the lower bound wordlength  $\underline{w}$  and upper bound wordlength  $\overline{w}$  as constraints for each wordlength variable:

$$\underline{w}_k \le w_k \le \overline{w}_k \text{ for } \forall k = 1, \cdots, n$$

(2.7)

The complete wordlength optimization problem can then be stated as

$$\begin{cases}

\min_{\mathbf{w} \in \mathbf{I}^n} f(\mathbf{w}) \\

\text{subject to } p(\mathbf{w}) \ge P_{req}, \underline{\mathbf{w}} \le \mathbf{w} \le \overline{\mathbf{w}}

\end{cases}$$

(2.8)

The goal of the wordlength optimization is hence to search for the optimizer  $\mathbf{w}^*$  that minimizes the objective function  $f(\mathbf{w})$  in (2.8).

#### 2.3.2 Finding Optimum Wordlength

One of the algorithms for searching the "optimum" wordlength starts with an initial feasible solution  $\mathbf{w}^{(0)}$  and performs an update via

$$\mathbf{w}^{(h+1)} = \mathbf{w}^{(h)} + s \, \xi^{(h)} \tag{2.9}$$

Here, h is an iteration index, s is the integer step size, and  $\xi$  is an integer update direction. A sound initial guess, a well-chosen step size, and a well-chosen update direction can reduce the number of iterations to find optimum wordlengths.

Optimum wordlengths can be found by solving equations when the performance function p is expressed in analytical form. If there is no analytical form to express the performance, then simulation-based search methods can be used to search for optimum wordlengths by measuring the performance function. Typical approaches involve assigning wordlength vector  $\mathbf{w}^{(0)}$  to a lower bound, an upper bound, or a vector between the lower and upper bounds. Step size can be fixed or adapted. The update direction is adapted according to the search algorithms in Section 2.4.

During iteration, the stopping criteria are dependent on the search algorithm. The algorithm that starts from the lower bound stops when the performance P reaches the required performance  $P_{req}$ . The algorithm that starts from the upper bound stops when P falls below  $P_{req}$ . Other algorithms stop when the performance P or cost c converges within a neighborhood.

## 2.4 Review of Simulation-Based Search Methods

Optimum wordlengths can be found by solving equations when the performance function P is expressed in analytical form. If there is no analytical form to express the performance, then simulation-based search methods can be used to search for optimum wordlengths by measuring the performance at the system output.

## 2.4.1 Complete Search

A complete search (CS) tests every possible combination of wordlengths between the lower bound and upper bound and measures the performance of each combination by simulation. Then optimum wordlengths can be selected from the simulation results.

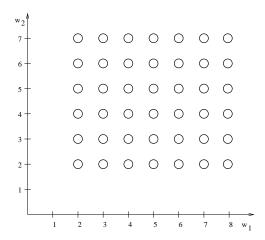

For example, assuming that the number of independent variables to find optimum word-length is two, and the lower bound and upper bound are  $\{2,2\}$  and  $\{8,7\}$ , respectively, the possible wordlength combinations are shown in Fig. 2.1. The number of trial tests or trials is 42. The optimum wordlength can be selected from the given simulation results after simulation is completed.

Figure 2.1: The possible wordlength combinations from searching the entire space in a complete search ( $\underline{\mathbf{w}} = \{2, 2\}; \mathbf{w} = \{8, 7\}; \text{ trials} = 42$ ).

The total number of tests in N wordlength variables is

$$E_{CS}^{N} = \prod_{k=1}^{N} (\overline{w}_k - \underline{w}_k + 1).$$

(2.10)

A complete search is guaranteed to find a global optimum point, but computational time and the number of tests increase exponentially as the number of wordlength variables increases.

#### 2.4.2 Exhaustive Search

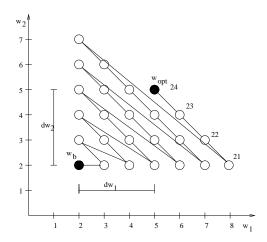

Sung and Kum [2] search for the first feasible solution. They search for a wordlength with the minimum wordlength as the initial guess and increment the wordlength by one until the propagated error meets the minimum error. For example, assuming that we are trying to find the optimum wordlength for two variables, the minimum wordlengths are  $\{2,2\}$ , and all wordlength costs

are similar, the search path is shown in Fig. 2.2. An optimized point  $\{5,5\}$  is given for a comparison between search methods. The minimum number of trials is 24.

I have generalized the total number of experiments of the Exhaustive Search in N dimensions with the sum of the distance. The sum of the distance, d, is defined as

$$d = dw_1 + dw_2 + \dots + dw_N. (2.11)$$

where  $dw_i$  is the distance between the minimum wordlength and the optimum wordlength in the  $i_{th}$  dimension. The expected number of experiments of the Exhaustive Search is calculated by using the summation of combination-with-replacement in [27] as

$$E_{ES}^{N}(d) = \sum_{r=0}^{d-1} C^{R}(N,r)$$

$$= C^{R}(N+1,d-1)$$

$$= {N+d-1 \choose d-1}$$

$$= {(N+d-1)! \over {\{(N+d-1)-(d-1)\}!(d-1)!}}$$

$$= {(d+N-1)\cdots(d+2)(d+1)d \over N!}.$$

(2.12)

The trials may be bounded as

$$E_{ES}^{N}(d) \le E_{ES}^{N,d} < E_{ES}^{N}(d+1).$$

(2.13)

The number of experiments is always less than that of the Complete Search if at least two feasible solutions exist. However, the Exhaustive Search method does not always guarantee that it will find the global optimum.

Figure 2.2: The direction of Exhaustive Search ( $\underline{\mathbf{w}} = \{2, 2\}$ ; optimum point  $= \{5, 5\}$ ; distance, d, in (2.11) is 6; trials = 24).

#### 2.4.3 Sequential Search

The basic notion of the Sequential Search is that each trial eliminates a portion of the region being searched [25]. This procedure is also called a "Min+1 Search" in [11] or "Local Search" in [24]. The Sequential Search method decides where the most promising areas are located, and continues in the most favorable region after each set of experiments [28]. The Sequential Search algorithm can be summarized by the following four steps:

- 1. For the independent variables, select a set of values that satisfies the desired system performance during the one-variable simulations.

- 2. Evaluate the system performance.

- 3. Choose feasible locations at which system performance is evaluated.

4. If the system performance of one point is better than at others, then move to the better point, and repeat the search, until the point has been located within the desired accuracy.

A base point is the minimum wordlength as an initial wordlength  $\mathbf{w}^{(0)}$  in (2.9). In Step 3, the direction of search,  $\xi$  in (2.9) is chosen in accordance with the maximum derivative of their performance

$$\xi_{j} = \begin{cases} \{1, 0, 0, \dots, 0\} & \text{if } m_{j} = \nabla \frac{p}{w_{1}} \\ \{0, 1, 0, \dots, 0\} & \text{if } m_{j} = \nabla \frac{p}{w_{2}} \\ \dots \\ \{0, 0, 1, \dots, 0\} & \text{if } m_{j} = \nabla \frac{p}{w_{N}} \end{cases}$$

$$(2.14)$$

and

$$m_j = \max(\nabla \frac{p}{w_1}, \nabla \frac{p}{w_2}, \cdots, \nabla \frac{p}{w_N})$$

(2.15)

where  $\nabla$  is the gradient operator.

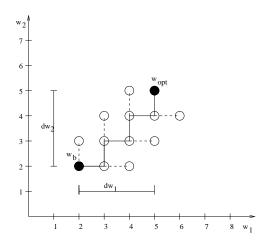

In Fig.2.3, starting from the wordlength base point  $\{2,2\}$ , I measure the performance of  $\{2,3\}$  and  $\{3,2\}$  from the direction of the sequential search in Step 3. If the performance of  $\{3,2\}$  is better than that of  $\{2,3\}$ , then a new wordlength vector moves into  $\{3,2\}$ . Simulations are repeated until the desired performance is obtained.

I have generalized the trials of the sequential search in N dimensions as

$$E_{SS}^{N} = N \cdot (dw_1 + dw_2 + \dots + dw_N). \tag{2.16}$$

In this example, the number of trials in (2.16) is 12, as illustrated in Fig.2.3. The number of trials is reduced by using sensitivity information; however, an optimum wordlength can be a local optima.

Figure 2.3: The direction of the sequential search ( $\underline{\mathbf{w}} = \{2, 2\}$ ; optimum point  $= \{5, 5\}$ ; distance d in (2.11) is 6; trials = 12)

A local search [24] uses sensitivity information with the above procedure, but it uses cost sensitivity instead of performance sensitivity.

#### 2.4.4 Preplanned Search

A preplanned search [25] is one in which all the experiments are completely scheduled in advance. The directions are obtained from the sensitivity of performance of an independent variable. The optimum point is found by employing the steepest descent among local neighboring points.

The preplanned search algorithm in N dimensions is summarized by the following steps:

1. For the independent variables, select a set of values for the independent variables that satisfies the desired performance during the one-variable simulations.

- 2. Make a performance sensitivity list from the one-variable simulations.

- 3. Make a test schedule with the sensitivity list to follow the higher sensitivity points from the base point.

- 4. Evaluate the performance at those points.

- 5. Move to the points, until the point has been located within the desired accuracy.

In step 3, the direction of preplanned search is chosen in accordance with the maximum derivative of an independent performance

$$\xi_{j} = \begin{cases} \{1, 0, 0, \cdots, 0\} & \text{if } m_{j} = \nabla \frac{p_{1}}{w_{1}} \\ \{0, 1, 0, \cdots, 0\} & \text{if } m_{j} = \nabla \frac{p_{2}}{w_{2}} \\ \dots \\ \{0, 0, 1, \cdots, 0\} & \text{if } m_{j} = \nabla \frac{p_{N}}{w_{N}} \end{cases}$$

$$(2.17)$$

where

$$m_j = \max(\nabla \frac{p_1}{w_1}, \nabla \frac{p_2}{w_2}, \cdots, \nabla \frac{p_N}{w_N})$$

(2.18)

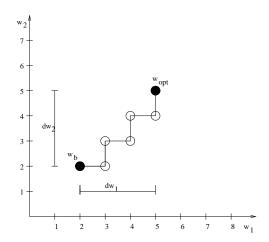

In Fig. 2.4, starting from the base point  $\{2,2\}$ , the preplanned search makes a list of the directions of the steepest ascent by comparing the gradients of the independent performances in one dimension from the one-variable simulations. If the gradient, which is calculated from the one-variable simulations at a  $w_1$  of 2 bits, is larger than that at a  $w_2$  for 2 bits, then the next feasible location is  $\{3,2\}$ . Then, if the gradient at a  $w_1$  of 3 is smaller than that at a  $w_2$  of 2, the next feasible location is  $\{3,3\}$ . The simulation path would be  $\{2,2\}$ ,  $\{3,2\}$ ,  $\{3,3\}$ , etc. After scheduling the feasible points, the performance

Figure 2.4: The direction of the preplanned search ( $\underline{\mathbf{w}} = \{2, 2\}$ ; optimum point  $= \{5, 5\}$ ; distance d in (2.11) is 6; trials = 6)

of these points are evaluated until the value of the performance meets the desired accuracy.

I generalized the trials of the preplanned search in N dimensions as

$$E_{PS}^{N} = dw_1 + dw_2 + \dots + dw_N. \tag{2.19}$$

In this example, the number of trials in (2.19) is 6, as illustrated in Fig. 2.4. The number of trials is the least among the search methods reported so far. However, finding the global optimum wordlength is not guaranteed.

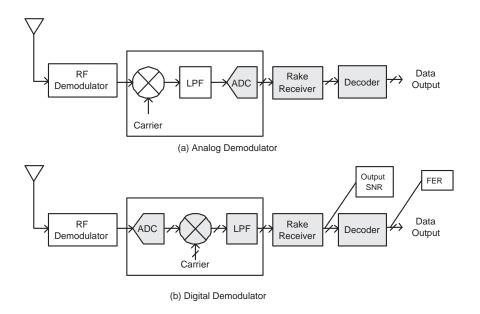

#### 2.4.5 Case Study

Typical demodulators are implemented with an analog block in front of an analog-to-digital converter (ADC) block, as shown in Fig. 2.5(a). As the speed of the ADC increases in communication systems [29], the analog parts are replaced with digital parts. As shown in Fig. 2.5(b), I replaced the analog

Figure 2.5: Analog and digital demodulators in CDMA receiver and performance measurement position.

demodulator with a digital demodulator.

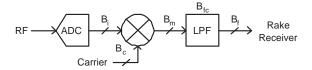

The demodulator converts modulated signals into baseband signals. In the digital demodulator block of Fig. 2.6, the sampled data values output by the ADC are multiplied by a carrier signal to shift the spectrum down to the baseband. The out-of-band signal is removed by the lowpass filter (LPF). The variables in the digital demodulator are given below [10, 30]:

- $B_i$ : input wordlength

- $B_c$ : carrier wordlength

- $B_m$ : multiplier output wordlength

- $B_f$ : filter output wordlength

Figure 2.6: A digital demodulator block.

# • $B_{fc}$ : filter coefficient wordlength.

Because direct measurement of frame error rate (FER), which is a general measurement to evaluate CDMA systems requires at least 10<sup>5</sup> frames during the simulation [31], the output SNR is used for performance measurement instead of FER. The required output SNR in this system is over 0.8 dB, whereas FER is under 0.03 [10].

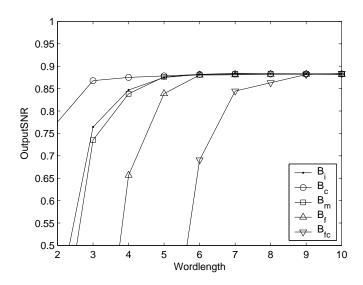

For the initial point, the minimum wordlength is selected by the independent one-variable simulations in which one variable changes while other variables maintain high precision. To satisfy the output SNR of 0.8 dB, the minimum wordlength of  $\{B_i, B_c, B_m, B_f, B_{fc}\}$  is  $\{4, 3, 4, 5, 7\}$ , which is acquired from the one-variable simulations shown as Fig. 2.7. For a simplified example, I assume that the cost-per-bit is one. In the exhaustive search, the next points are searched:  $\{5, 3, 4, 5, 7\}$ ,  $\{4, 4, 4, 5, 7\}$ ,  $\{4, 3, 4, 5, 8\}$ ,  $\{5, 4, 4, 5, 7\}$ , etc. The search is continued until the communications performance meets the specified desired requirement. In the sequential search, the next point is one of the following:  $\{5, 3, 4, 5, 7\}$ ,  $\{4, 4, 4, 5, 7\}$ ,  $\{4, 3, 5, 5, 7\}$ ,  $\{4, 3, 4, 6, 7\}$ , and  $\{4, 3, 4, 5, 8\}$ . The next point would have the largest communication performance among them. From Table

Figure 2.7: Result of the independent one-variable simulations on a CDMA demodulator.

2.3,  $\{4,3,4,6,7\}$  is the next location because it has the largest communication performance. The simulation moves the current point to the new point and continues to search until the performance exceeds the specified desired requirement, which is an output SNR of 0.8dB in this case. The final point is  $\{5,3,6,6,7\}$ , as shown in Table 2.3. From (2.11), the distance between the base and the optimum point is 4. From (2.16), the number of trials for the sequential search to find an optimum wordlength is 20.

In the preplanned search, the search path is estimated from the sensitivity of each one-variable simulation shown in Fig. 2.7. Starting from the minimum wordlength or base point,  $\{4, 3, 4, 5, 7\}$ , the first expected point is  $\{4, 3, 4, 6, 7\}$  because, from Fig. 2.7,  $B_f$  has the greatest derivative among each wordlength at the base point.

The sequence of the preplanned search points is  $\{4, 3, 4, 5, 7\}$ ,  $\{4, 3, 4, 6, 7\}$ ,  $\{4, 3, 4, 6, 8\}$ ,  $\{4, 3, 5, 6, 8\}$ ,  $\{4, 4, 5, 6, 8\}$ , etc. Simulations move the current point to the next point until the performance exceeds the specified desired requirement. From (2.11), the optimum point is  $\{5, 4, 5, 6, 8\}$  and distance is 5. From (2.19), the number of trials of the preplanned search to find an optimum wordlength is 5.

#### 2.4.6 Comparison

The four search methods are compared according to the trials from (2.10), (2.12), (2.16), and (2.19), as shown in Table 2.4. For each method, the number of trials is calculated in addition to the one-variable simulation, which all of the search methods use. The complete search needs 283920 trials to find the optimum wordlength from (2.10) with  $\overline{w}_k = \{16, 16, 16, 16, 16\}$  and  $\underline{w}_k = \{4, 3, 4, 5, 7\}$ , assuming that the maximum wordlength is 16 bits. If the computer simulation to calculate the frame error rate per trial in the CDMA system takes about 10 minutes, the complete search to find an optimum wordlength would require 5 years, which is an unrealistic design time.

By using (2.12), the exhaustive search needs 56 trials, by using (2.12), which is fewer than the complete search. The exhaustive search is, however, inefficient in finding the optimum wordlength when the wordlength variables for optimization are numerous and the distance between the base and optimum point is longer.

The sequential search and preplanned search requires 20 and 5 tri-

Table 2.3: Sequence of the sequential search for CDMA demodulator (Traffic Channel Rate Set 1 in Additive White Gaussian Noise, Input SNR = -17.3 dB, Eb/Nt= 3.8, Rate= 9600 bps, Desired performance: Output SNR> 0.8dB, FER< 0.03)

| Step | $\{B_i, B_c, B_m, B_f, B_{fc}\}$ | Output SNR | FER   | Result |

|------|----------------------------------|------------|-------|--------|

| 1, 2 | ${4, 3, 4, 5, 7}$                | 0.711      | 0.038 | Fail   |

| 3    | $\{5, 3, 4, 5, 7\}$              | 0.735      | -     | -      |

| 3    | $\{4, 4, 4, 5, 7\}$              | 0.694      | -     | -      |

| 3    | ${4, 3, 5, 5, 7}$                | 0.712      | -     | -      |

| 3    | $\{4, 3, 4, 6, 7\}$              | 0.759      | -     | Max    |

| 3    | ${4, 3, 4, 5, 8}$                | 0.704      | ı     | -      |

| 4    | ${4, 3, 4, 6, 7}$                | 0.759      | 0.035 | Fail   |

| 3    | $\{5, 3, 4, 6, 7\}$              | 0.763      | -     | -      |

| 3    | $\{4, 4, 4, 6, 7\}$              | 0.722      | -     | -      |

| 3    | ${4, 3, 5, 6, 7}$                | 0.773      | -     | Max    |

| 3    | $\{4, 3, 4, 7, 7\}$              | 0.751      | -     | -      |

| 3    | ${4, 3, 4, 6, 8}$                | 0.749      | -     | -      |

| 4    | ${4, 3, 5, 6, 7}$                | 0.773      | 0.034 | Fail   |

| :    | i:                               | :          | ÷     | ÷      |

| 3    | {6, 3, 5, 6, 7}                  | 0.798      | _     | -      |

| 3    | $\{5, 4, 5, 6, 7\}$              | 0.802      | -     | -      |

| 3    | $\{5, 3, 6, 6, 7\}$              | 0.805      | -     | Max    |

| 3    | $\{5, 3, 5, 7, 7\}$              | 0.803      | -     | -      |

| 3    | $\{5, 3, 5, 6, 8\}$              | 0.798      |       |        |

| 4    | $\{5, 3, 6, 6, 7\}$              | 0.805      | 0.029 | Pass   |

Table 2.4: Comparison of complete, exhaustive, sequential and preplanned search (N = 5,  $\overline{w}_k = \{16, 16, 16, 16, 16\}$ ,  $\underline{w}_k = \{4, 3, 4, 5, 7\}$ , and the term d is defined in (2.11)).

| Search     | Distance (d) | Equation for Number of Experiments from                  | Trials |

|------------|--------------|----------------------------------------------------------|--------|

|            |              | (2.10), (2.12), (2.16), (2.19)                           |        |

| Complete   | -            | $\prod_{k=1}^{N} (\overline{w}_k - \underline{w}_k + 1)$ | 283920 |

| Exhaustive | 4            | $(d+4)(d+3)\cdots(d)/5!$                                 | 56     |

| Sequential | 4            | $5 \cdot d$                                              | 20     |

| Preplanned | 5            | d                                                        | 5      |

als, respectively, which are fewer than for the other search methods. Among the search methods, the preplanned search has the smallest number of experiments, but its distance according to (2.11) is greater than that for the sequential search. By implication, therefore, the wordlength of the sequential search method is closer to a global optimum with respect to hardware cost.

Techniques based on the gradient projection method encounter a loss of direction problem when they employ the sequential search and preplanned search. This problem can be solved by adapting the step size.

The sequential search and the preplanned search reduce the trials by rates of 64% and 91%, respectively, when compared to the exhaustive search for wordlength optimization in the CDMA demodulator design. However, the preplanned search seldom converges to the same optimum point, and the distance is longer than that of the other search methods.

### 2.5 Genetic Algorithms

In 1975, Holland introduced an optimization procedure that mimics the process observed in natural evolution [32] and is known as the genetic algorithm, or GA [33–35]. This technique of optimization is similar to its associated algorithms such as simulated annealing [36], evolutionary strategies [37], and evolutionary programming [38, 39], which are classified as guided random techniques. Because of its simple implementation procedure, the GA can be used as an optimization tool for designing AI-hybrid systems for real-world applications [40–45].

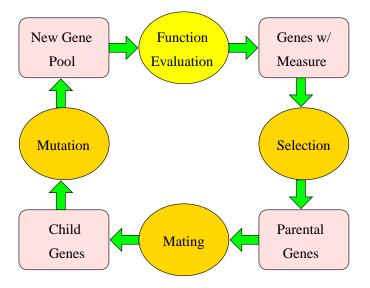

Genetic and evolutionary algorithms [35] provide optimization techniques that mimic the three major components of natural evolution and selective breeding: selection, exchange of genetic material during reproduction (or mating), and random mutations as shown in Fig. 2.8 [46].

By their definition, genetic algorithms lend themselves to discussion in terms of a biological paradigm. For example, an instance of a system is referred to as an individual. An individual contains a genotypic description, which is the list of attributes (or decision variables) to be optimized. A group of individuals make up a population. Selection is mimicked by comparing the performances of individuals in a population and determining which individuals get to mate. An individual with more desirable features for fitness is given a higher probability of mating. Mating is performed by combining some attributes from one parent and the remaining attributes from the other parent. The attributes of the resulting individual can then be mutated using

Figure 2.8: Genetic and Evolutionary Algorithms [46]

any method desired, including normal and uniform distributions. Mutation provides a natural resistance to the optimization process converging on a local minimum or maximum and allows the introduction of new genetic material into the gene pool.

#### 2.5.1 Multi-Objective Evolutionary Optimization

Most problems in nature have several objectives (normally conflicting with each other) that need to be achieved at the same time. These problems, called "multi-objective" optimization problems, were originally studied in the context of economics [47]. Because of the conflicting nature of their objectives, multi-objective optimization problems do not normally have a single solution, and, in fact, they even require the definition of a new notion of "optimum." The most commonly adopted notion of optimality in multi-objective

optimization is that originally proposed by Edgeworth [48] and later generalized by Pareto [49]. Such a notion is called *Edgeworth-Pareto optimality* or, more commonly, *Pareto optimality*.

**Definition 2.5.1 (Definition of Pareto Optimality).** A vector of decision variables  $\mathbf{x}^* \in \mathcal{F}$  is *Pareto optimal* if there does not exist another  $\mathbf{x} \in \mathcal{F}$  such that  $f_i(\mathbf{x}) \leq f_i(\mathbf{x}^*)$  for all i = 1, ..., k and  $f_j(\mathbf{x}) < f_j(\mathbf{x}^*)$  for at least one j. Here,  $\mathcal{F}$  denotes the feasible region of the problem (i.e., where the constraints are satisfied).

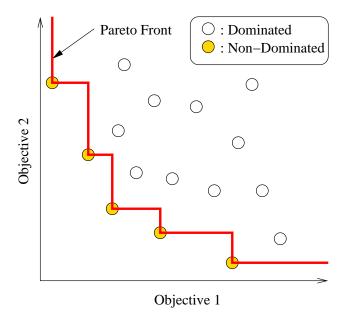

In words, this definition says that  $\mathbf{x}^*$  is Pareto optimal if there exists no feasible vector of decision variables  $\mathbf{x} \in \mathcal{F}$  that would decrease some criterion without causing a simultaneous increase in at least one other criterion. Unfortunately, this concept almost always gives not a single solution, but rather a set of solutions, called the *Pareto optimal set*. The vectors  $\mathbf{x}^*$  corresponding to the solutions included in the Pareto optimal set are called *non-dominated*. The plot of the objective functions whose non-dominated vectors are in the Pareto optimal set is called the *Pareto front*, as shown in Fig. 2.9.

#### 2.5.2 Pareto Rank

A fitness value of a chromosome is required in GA operations. However, it is difficult to combine the objectives both in linear and/or nonlinear fashion to reflect the fitness of the chromosome. Therefore, a Pareto multi-objective ranking approach [50] is adopted. Consider an individual  $x_i$  at generation t

Figure 2.9: Pareto front in two objectives

that is dominated by  $p_i^{(t)}$  individuals in the current population. Its current position in the individuals' rank can be given by

$$rank(x_i, t) = 1 + p_i^{(t)}$$

(2.20)

All non-dominated individuals are assigned Rank 1. Fitness is assigned to each chromosome according to its rank in the population.

# 2.5.3 Wordlength Optimization with Multi-Objective Evolutionary Algorithms

When implementing a digital filter in hardware, filter coefficients have to be represented with finite wordlength. Several methods have been proposed to effectively design finite impulse response (FIR) filters with linear programming [51–53]. Xu and Daley [54] show that GA is superior to integer

programming techniques in filter design.

Being powerful optimization tools, the genetic and evolutionary algorithms have explored a large number of applications [55] in signal processing, such as adaptive IIR filtering [56], nonlinear model selection, time-delay estimation, active noise control, and speech processing.

Genetic algorithms have been used in filter design [54,57–61]. The initial use of a genetic algorithm for filter design was reported in [57]. Genetic algorithms have been used to design multiplierless filters [62–64] or filters represented with cannoical signed-digits (CSD) [65–68].

Genetic algorithms have been applied to wordlength design in digital signal processing. Wordlengths in digital signal processing are analogous to genes, and each set of wordlengths is analogous to a chromosome. The GA is used to determine wordlength in filter coefficients [61] and to optimize the wordlength of input data and coefficients in a FFT processor [69] with a single objective.

Some papers have employed multiple objectives for wordlength optimization. Leban and Tasic [60] used mean square error, delay, and area as objectives. Signal-to-noise ratio and power are used as objectives by Sulaiman and Arslan [70]. These works employed a weighted sum as a fitness function. As in the case of the weighted sums methods, the relative importance of objectives should be specified using weights (quantitatively). Furthermore, a simple weighted-sum technique only finds a single solution of the many possible opti-

mal solutions in the objective space. Thus, the single solution does not provide the ability to understand the various trade-offs that are possible in objective space [46].

In this dissertation, Pareto ranking approaches [46] are used for multiple objective evolutionary algorithms to optimize wordlength, and the results are shown in Section 3.5.

## 2.6 Summary

This chapter briefly explains fixed-point wordlength optimization and several search algorithms. Table 2.5 summarizes the advantages and disadvantages of the algorithms mentioned in this chapter. As shown in Table 2.5 the complete method and the genetic method have more advantages compared to the other methods. However, the complete search method is impractical. The sequential and the preplanned methods show less iteration than the other methods. However, these methods cannot handle multiple objectives. The next chapter proposes a modified sequential search algorithm that can handle multiple objectives.

Table 2.5: Advantages/disadvantages of wordlength search algorithms in this chapter

| Advantages                  | Disadvantages |   |   |              |                              |                 |       |     |              |      |      |              |   |

|-----------------------------|---------------|---|---|--------------|------------------------------|-----------------|-------|-----|--------------|------|------|--------------|---|

| 1. Global optima            |               |   |   |              |                              | 1. Local optima |       |     |              |      |      |              |   |

| 2. Pareto rank              | king          |   |   |              | 2. Weights in objectives     |                 |       |     |              |      |      |              |   |

| 3. Handle multi-objectives  |               |   |   |              | 3. Single objective          |                 |       |     |              |      |      |              |   |

| 4. Amenable to parallelism  |               |   |   |              | 4. Limited parallelism       |                 |       |     |              |      |      |              |   |

| 5. Low algorithm complexity |               |   |   |              | 5. High algorithm complexity |                 |       |     |              |      |      |              |   |

| 6. Fewer iterations         |               |   |   |              | 6. More iterations           |                 |       |     |              |      |      |              |   |

|                             |               |   |   |              |                              | Imp             | racti | cal |              |      |      |              |   |

| Methods                     | 1             | 2 | 3 | 4            | 5                            | 6               | 1     | 2   | 3            | 4    | 5    | 6            | 7 |

|                             | Advantages    |   |   |              |                              |                 |       | Ι   | )isac        | lvan | tage | S            |   |

| Complete                    | $\mathbf{V}$  |   |   | $\mathbf{V}$ | $\mathbf{V}$                 |                 |       |     | $\mathbf{V}$ |      |      | $\mathbf{V}$ | 7 |

| Methods          | 1          | 2 | 3 | 4 | 5 | 6             | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|------------------|------------|---|---|---|---|---------------|---|---|---|---|---|---|---|

|                  | Advantages |   |   |   |   | Disadvantages |   |   |   |   |   |   |   |

| Complete         | Y          |   |   | Y | Y |               |   |   | Y |   |   | Y | Y |

| Exhaustive       |            |   |   |   | Y |               | Y |   | Y | Y |   | Y |   |

| Sequential       |            |   |   |   | Y | Y             | Y |   | Y | Y |   |   |   |

| Preplanned       |            |   |   |   | Y | Y             | Y |   | Y | Y |   |   |   |

| Genetic/weighted |            |   | Y | Y |   |               |   | Y |   |   | Y | Y |   |

# Chapter 3

# Wordlength Optimization for Hardware Implementation

#### 3.1 Introduction

As described in Section 2.4, there are many search algorithms used in wordlength optimization. Gradient-based search algorithms utilize gradient information of wordlength to find better solutions. The gradient information can be obtained from sensitivity measurements of complexity or distortion according to the wordlength set. In this chapter, I propose a complexity-and-distortion measurement method that utilizes all sensitivity information simultaneously. Case studies in wordlength design in OFDM demodulators and IIR filters demonstrate the proposed algorithms. Simulation results from multi-objective genetic algorithms are also shown and compared.

# 3.2 Sensitivity Measurements

The sensitivity information or gradient information used to update directions in (2.9) can help reduce the search space dramatically. The sensitivity information can be obtained by measuring hardware complexity and distortion or propagated quantized precision loss. The complexity measure is used for

the hardware cost function in [24]. The distortion measure in [25] utilizes the sensitivity information of a propagated quantization error. The complexity-and-distortion measure in [15] combines the two measures to update the search direction.

#### 3.2.1 Complexity Measure (CM)

The complexity measure method considers the hardware complexity function as the cost function in (2.5) and uses the sensitivity information of the complexity as the direction to search for the optimum wordlengths. The local search in [24] uses the complexity measure.

The complexity measure method updates wordlengths from the direction of the lowest sensitive complexity until a system meets a required performance, such as  $P_{req}$  in (2.6). The complexity measure method searches the wordlengths that minimize hardware complexity; however, it demands a large number of iterations since it does not use any distortion sensitivity information that can speed up the search for the optimum wordlengths. For example, in a system composed of adders and multipliers, the complexity sensitivity of a multiplier is larger than that of an adder. The complexity measure method increases the wordlength in the adder with the priority during an increase procedure even if the wordlength in the multiplier affects the propagated quantized performance more. It would waste computer simulation time if the complexity sensitivity of an adder is much smaller than that of a multiplier.

#### 3.2.2 Distortion Measure (DM)

The distortion measure method considers the distortion function as the objective function in (2.5) and uses the sensitivity information of the distortion for the direction to search for the optimum wordlengths. The sequential search method uses the distortion measure. This method assumes that every cost or complexity function will be the same or equal to 1 and selects wordlengths with the update direction according to the distortion sensitivity information.

The complexity objective function is replaced with the distortion objective function  $d(\mathbf{w})$  as

$$f_d(\mathbf{w}) = d(\mathbf{w}) \tag{3.1}$$

and the complexity minimization problem is changed into a distortion minimizing problem by

$$\begin{cases}

\min_{\mathbf{w} \in \mathbf{I}^n} f_d(\mathbf{w}) \\

\text{subject to } d(\mathbf{w}) \le D_{req}, c(\mathbf{w}) \le C_{req}, \underline{w} \le \mathbf{w} \le \overline{w}

\end{cases}$$

(3.2)

where  $D_{req}$  is the required distortion, and  $C_{req}$  is a complexity constant.

The sensitivity information is also calculated by the gradient of the distortion function. For the steepest descent direction, the update direction is

$$\xi_{\mathbf{DM}} = -\nabla f_d(\mathbf{w}) \tag{3.3}$$

For the distortion, Fiore and Lee [71] computed an error variance, and Han *et al.* [25] measured an output SNR.