| <b>P</b> I | rotection<br>HPROT    |                        | litional inf           | ormation ab             | out a bus acc     | cess |

|------------|-----------------------|------------------------|------------------------|-------------------------|-------------------|------|

|            | HPROT[3]<br>cacheable | HPROT[2]<br>bufferable | HPROT[1]<br>privileged | HPROT[0]<br>data/opcode | Description       | _    |

|            | -                     | -                      | -                      | 0                       | Opcode fetch      | _    |

|            | -                     | -                      | -                      | 1                       | Data access       | _    |

|            | -                     | -                      | 0                      | -                       | User access       | _    |

|            | -                     | -                      | 1                      | -                       | Privileged access | _    |

|            | -                     | 0                      | -                      | -                       | Not bufferable    | _    |

|            | -                     | 1                      | -                      | -                       | Bufferable        | _    |

|            | 0                     | -                      | -                      | -                       | Not cacheable     | _    |

|            | 1                     | -                      | -                      | -                       | Cacheable         | _    |

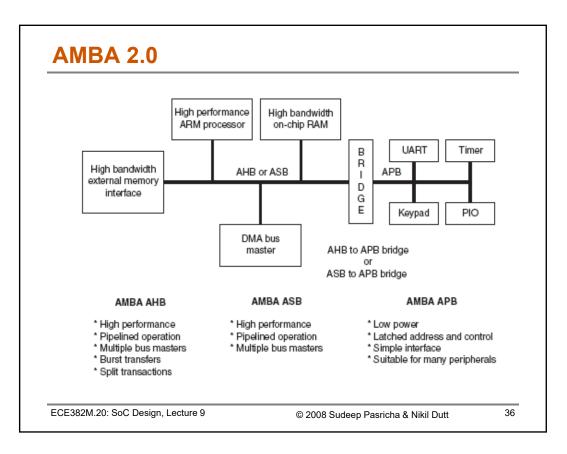

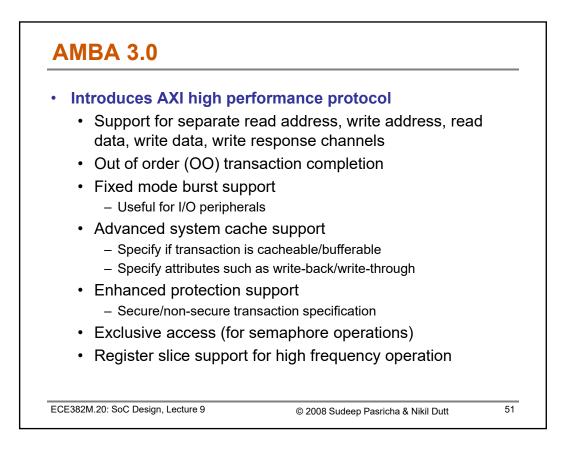

| AMBA 3.0 AXI                                                                                                                                                                            | AMBA 2.0 AHB                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

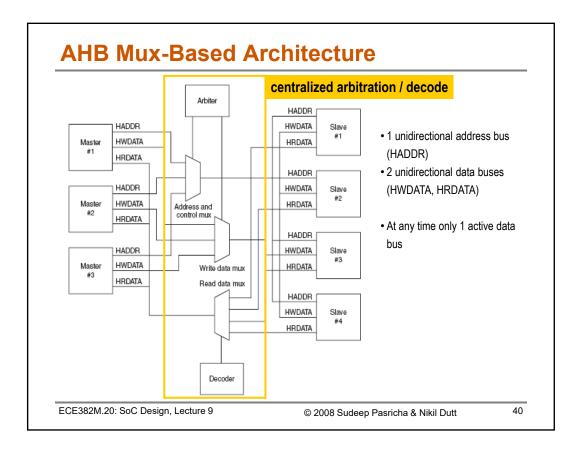

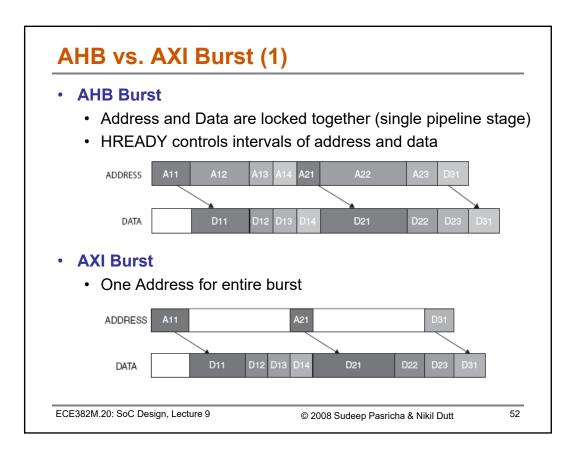

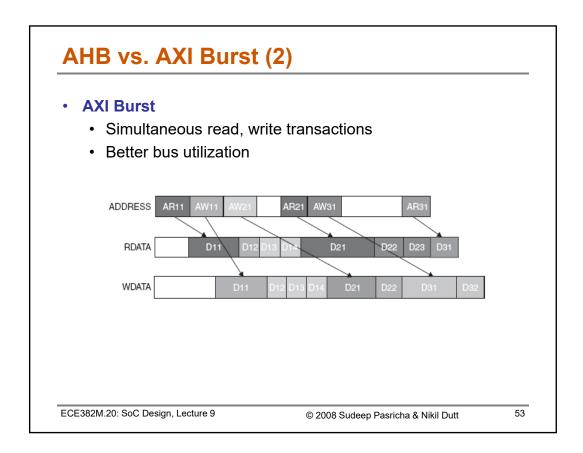

| Channel-based specification, with five<br>separate channels for read address,<br>read data, write address, write data,<br>and write response enabling flexibility in<br>implementation. | Explicit bus-based specification, with<br>single shared address bus and separate<br>read and write data buses. |

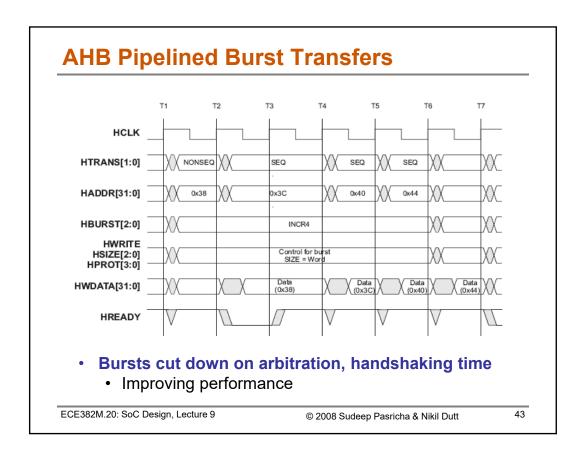

| Burst mode requires transmitting address<br>of only first data item on the bus.                                                                                                         | Requires transmitting address of every<br>data item transmitted on the bus.                                    |

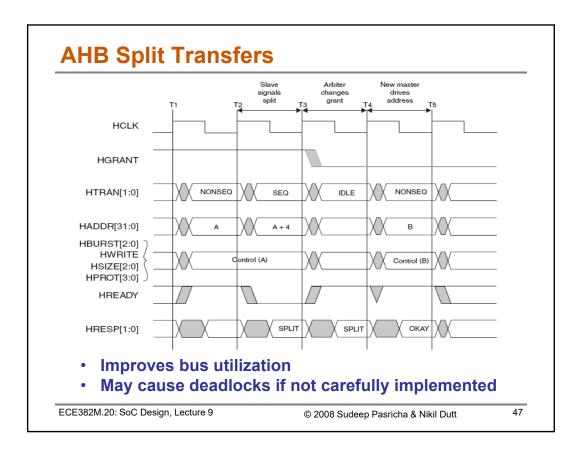

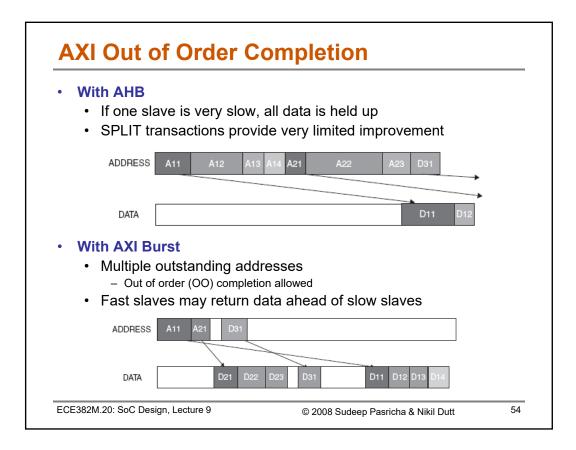

| OO transaction completion provides<br>native support for multiple, outstanding<br>transactions.                                                                                         | Simpler SPLIT transaction scheme<br>provides limited and rudimentary<br>outstanding transaction completion.    |

| Fixed burst mode for memory mapped I/O peripherals.                                                                                                                                     | No fixed burst mode.                                                                                           |

| Exclusive data access (semaphore operation) support.                                                                                                                                    | No exclusive access support.                                                                                   |

| Advanced security and cache hint support.                                                                                                                                               | Simple protection and cache hint support.                                                                      |

| Register slice support for timing isolation.                                                                                                                                            | No inherent support for timing isolation                                                                       |

| Native low-power clock control interface.                                                                                                                                               | No low-power interface.                                                                                        |

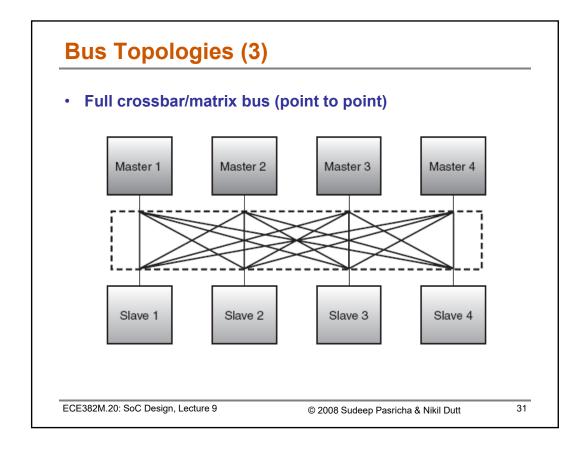

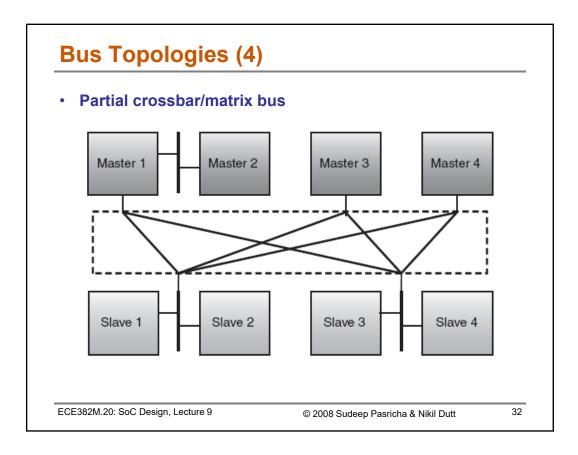

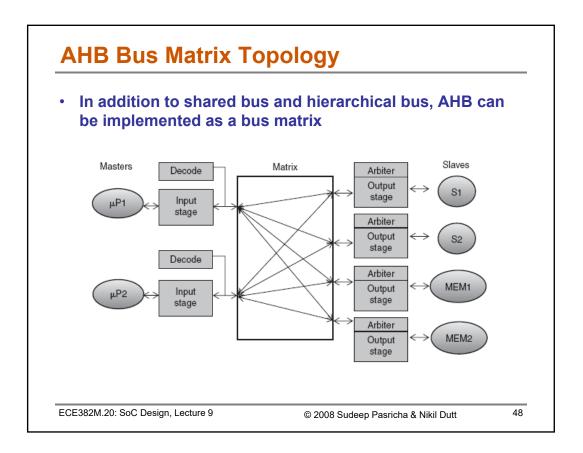

| Default bus matrix topology support.                                                                                                                                                    | Default hierarchical bus topology support.                                                                     |