# Communication Systems Design in Practice

Jacob Kornerup, Ph.D.

LabVIEW R&D

National Instruments

#### A Word About National Instruments

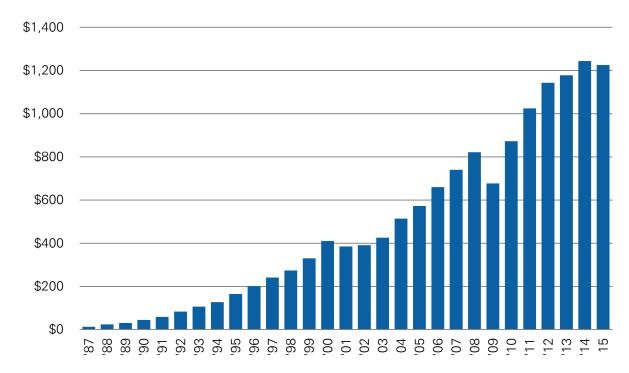

- Annual Revenue: \$1.23 billion

- Global Operations: Approximately 6,870 employees; operations in more than 40 countries

- Broad Customer Base: More than 35,000 companies served annually

- Diversity: No industry >15% of revenue

## **Graphical System Design**

A Platform-Based Approach for Measurement and Control

## Tough Real-Time Challenges

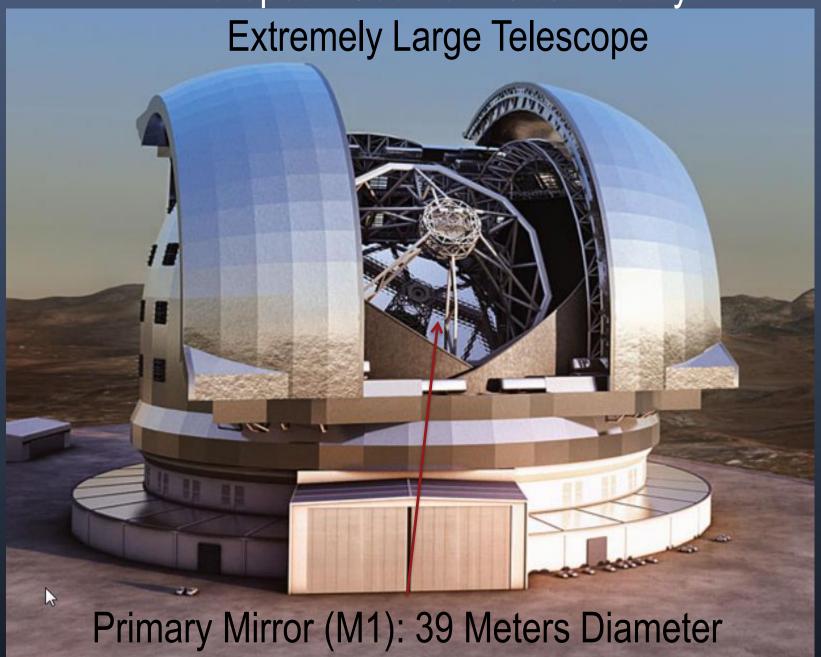

Large Telescope Mirror Control

Tokomak Plasma Control

Wind Turbine Sound Source Characterization

**CERN Hadron Collider**

**Early Cancer Detection**

Structural Health Monitoring

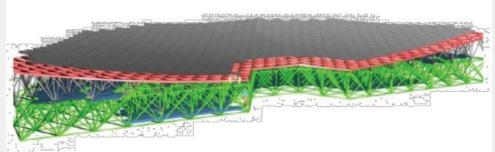

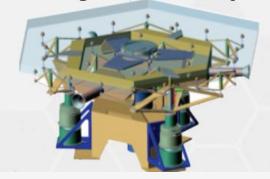

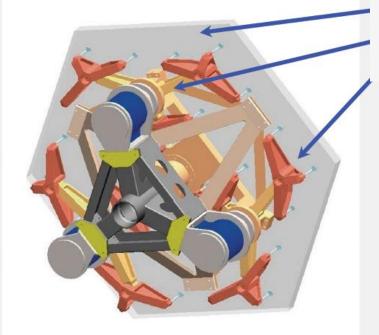

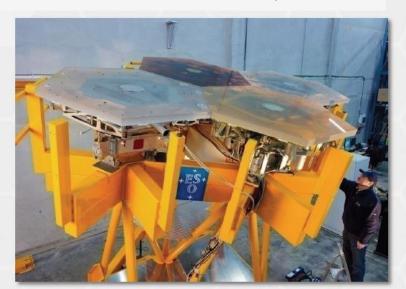

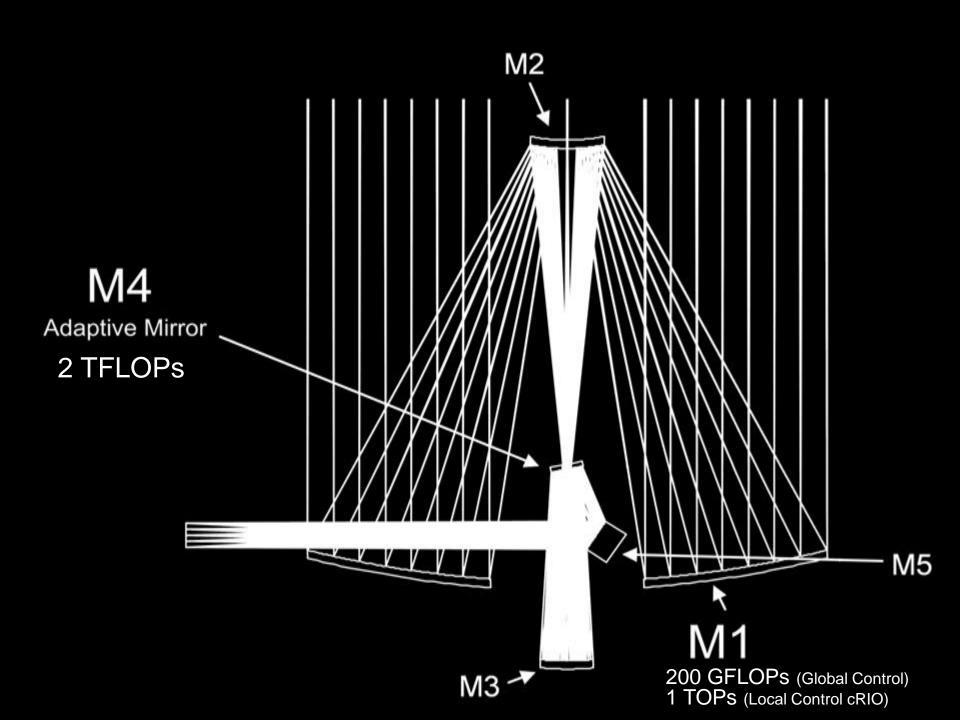

## European Southern Observatory

#### The Primary Mirror (M1)

- 6 Edge Sensors (4788 total)

- 3 Actuators (2394 total)

- 2.4K x 4.8K Matrix calculation / 1 ms

# Perspective

Pope Election 2005

## Perspective

Pope Election 2013

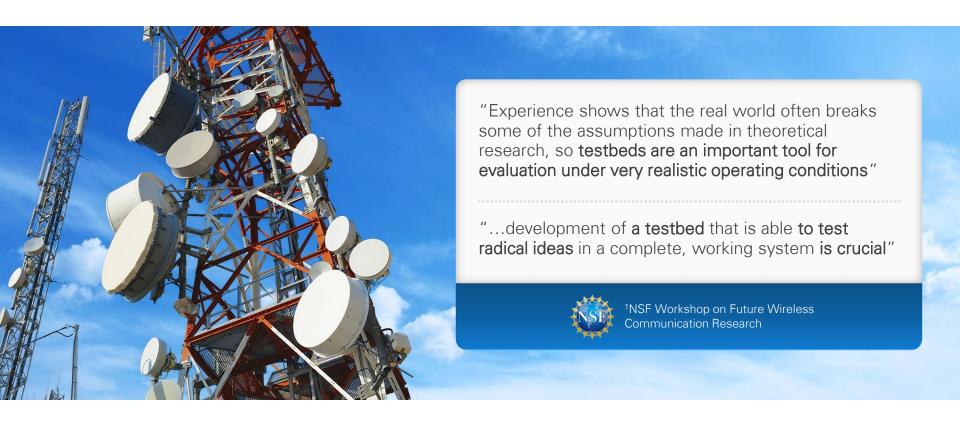

#### The Need for 5G

Explosion of wireless data and connected devices

50 BILLION

DEVICES CONNECTED BY 2020

#### Prototyping Is Critical for Algorithm Research

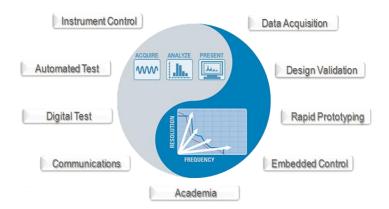

#### The National Instruments Vision

"To do for test and measurement what the spreadsheet did for financial analysis."

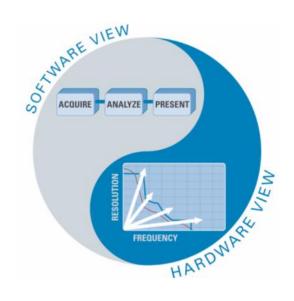

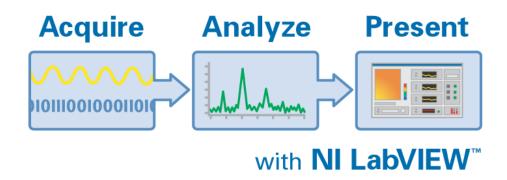

## Virtual Instrumentation

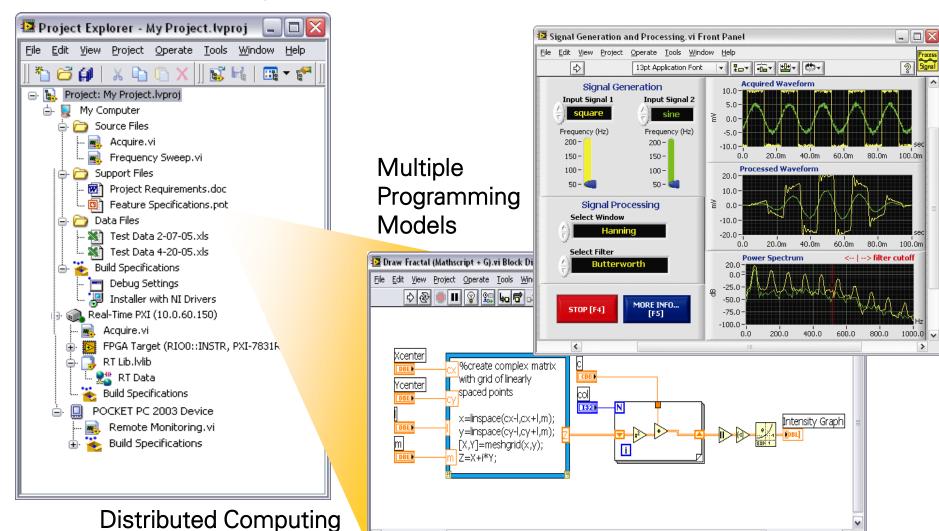

## High-Level Design Models

**Graphical System Design Platform**

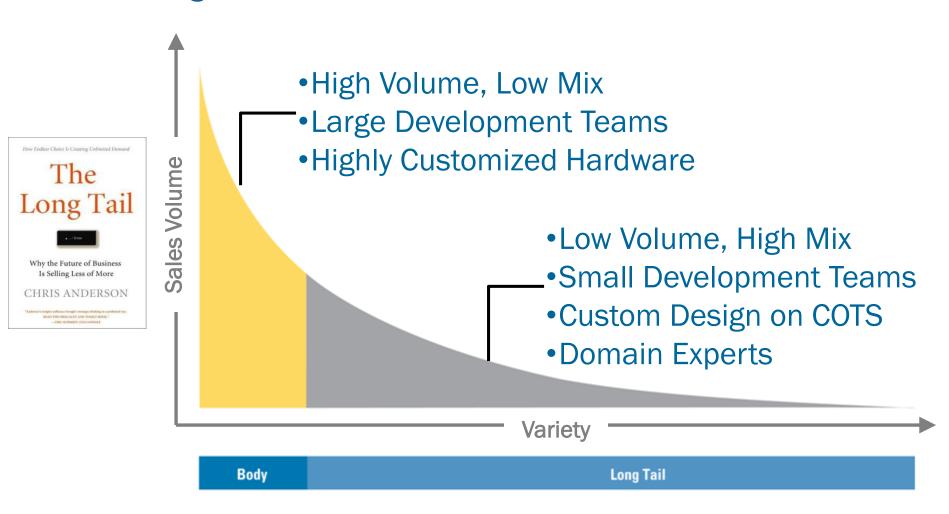

## The Long Tail

[ "The Long Tail," Chris Anderson Wired, 2004]

# NI Vision *Evolved*. Graphical System Design

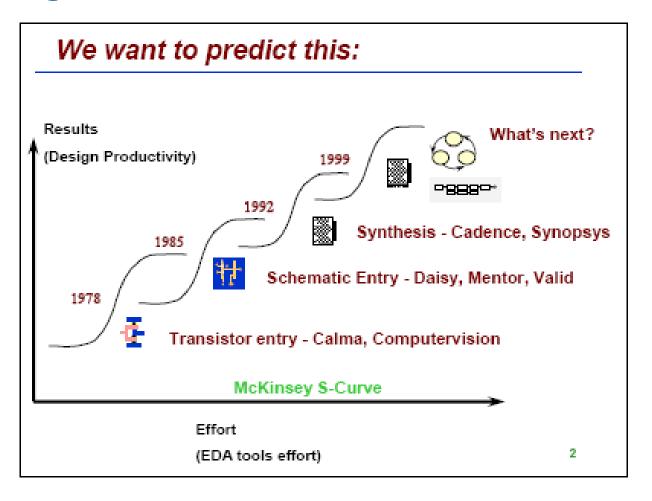

# Design discontinuities in EDA tools

[1] Kurt Keutzer, UC Berkeley EECS 244 class

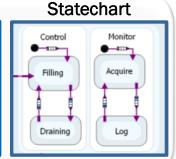

## Platform Based Design & Models of Computation

- Constructs for application domain experts

- Structured implementation with the right levels of abstraction

- Separation of concerns between functionality and architecture

- Evolve designs on hardware "generations"

- Design flow that supports analysis, simulation, verification and synthesis

[1] E.A. Lee, "Embedded Software", Revised from UCB ERL Memorandum M01/26, November 1, 2001,

[2] E.A. Lee and S. Neuendorffer, "Concurrent Models of Computation for Embedded Software," Memorandum No. UCB/ERL M04/26, July 22, 2004

[3] Alberto Sangiovanni-Vincentelli, "Quo Vadis, SLD? Reasoning About the Trends and Challenges of System Level Design", Proceedings of the IEEE, Vol. 95, No. 3, March 2007.

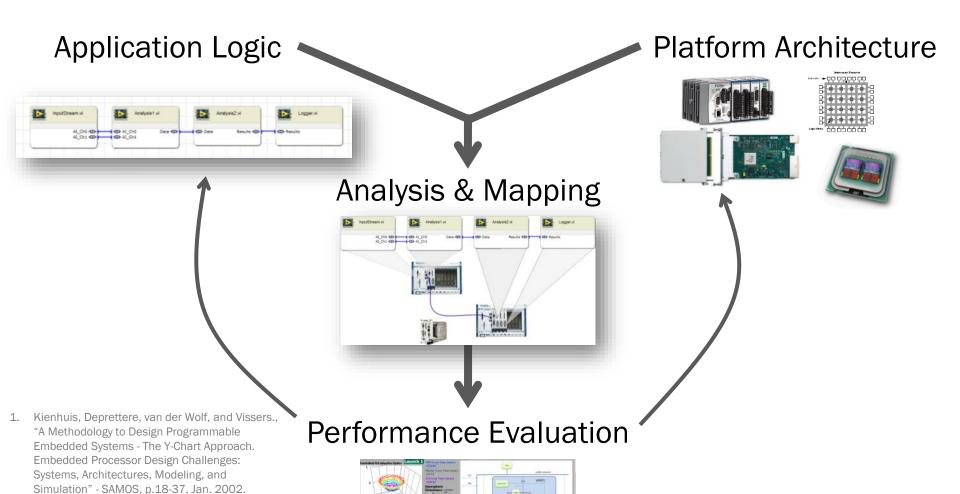

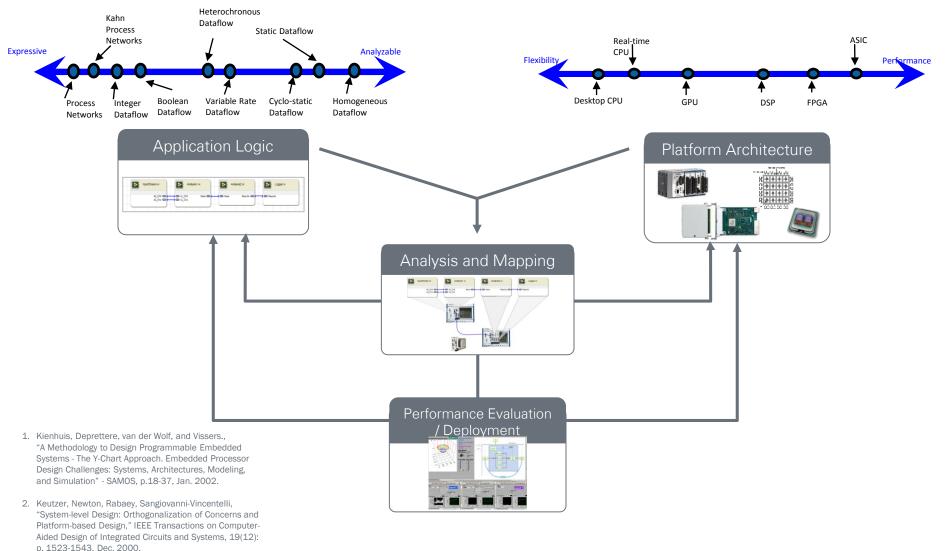

#### The Y-Chart System Design Methodology

Keutzer, Newton, Rabaey, Sangiovanni-Vincentelli, "System-level Design: Orthogonalization of Concerns and Platformbased Design," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 19(12): p. 1523-1543, Dec. 2000.

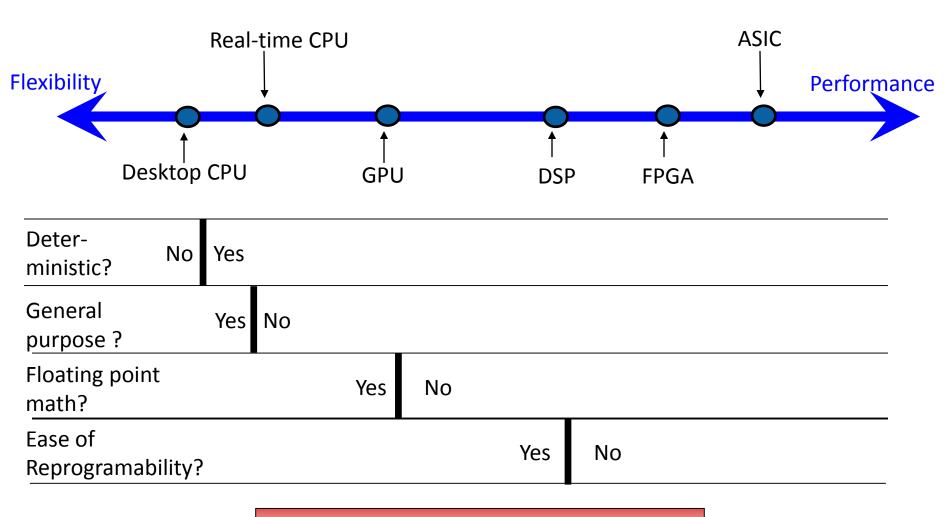

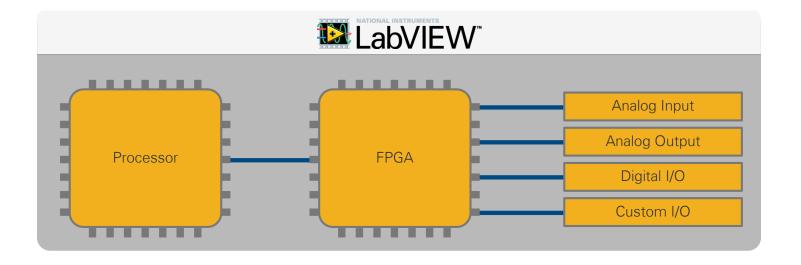

#### Platform Dimensions

- Distributed

- Heterogeneous computing platforms

- Real-time OS, FPGA, Desktop OS, GPU

- Communication schemes

- Real-time

- · 10

- Timing

## Application Dimensions

- Algorithm development

- IO characterization

- Timing characteristics

- Real-time constraints

- Models of Computation integration

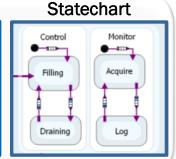

- State management

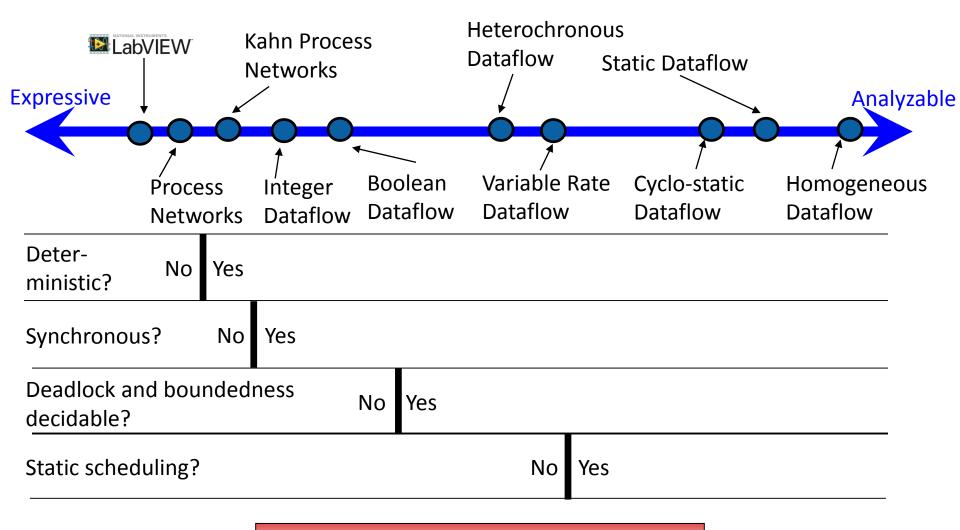

# Dataflow MoCs for Streaming Applications

Key trade-off: Analyzability vs. Expressibility

## Platform Architectures

Key trade-off: Flexibility vs. Performance

#### The Y-Chart System Design Methodology

## High-Level Design Models

**Graphical System Design Platform**

#### LabVIEW Today

# Realizing Our Vision for Instrumentation Graphical System Design

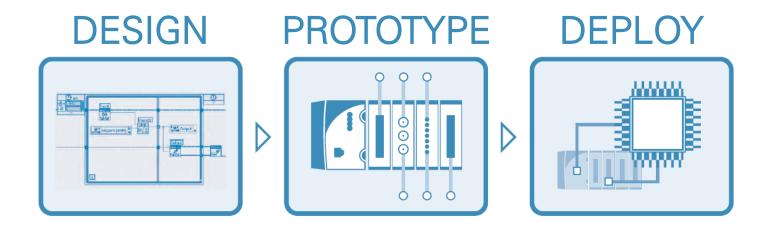

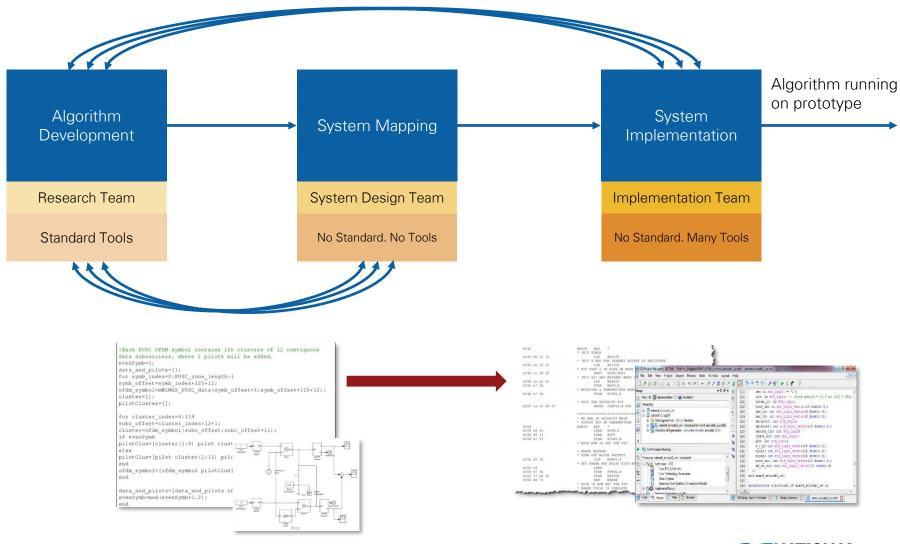

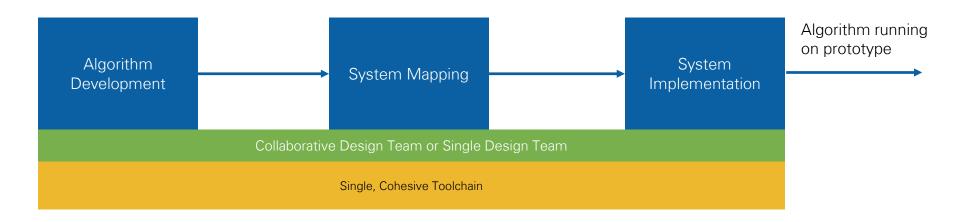

#### Classical Design Flow

## Platform Enabled Design Flow

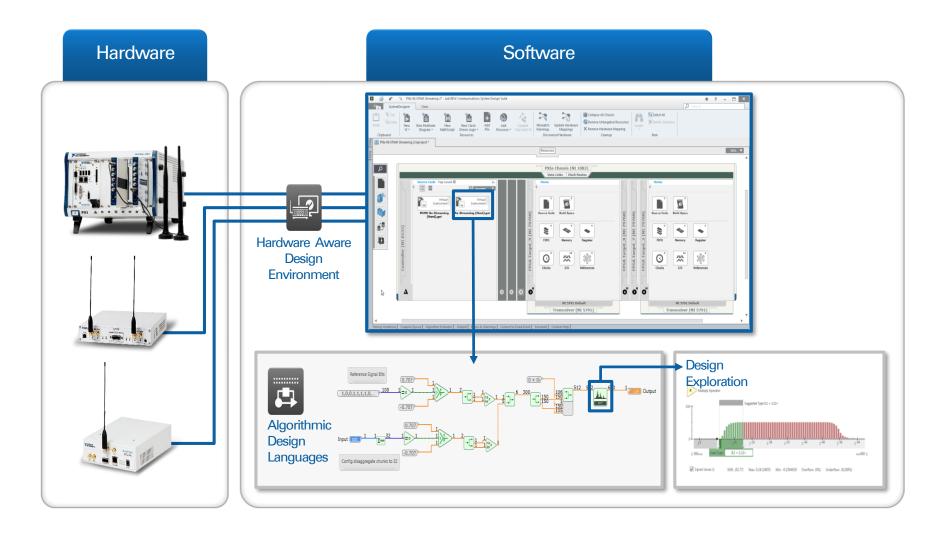

## LabVIEW Communications System Design Suite

The Next Generation Platform for Software Defined Radio

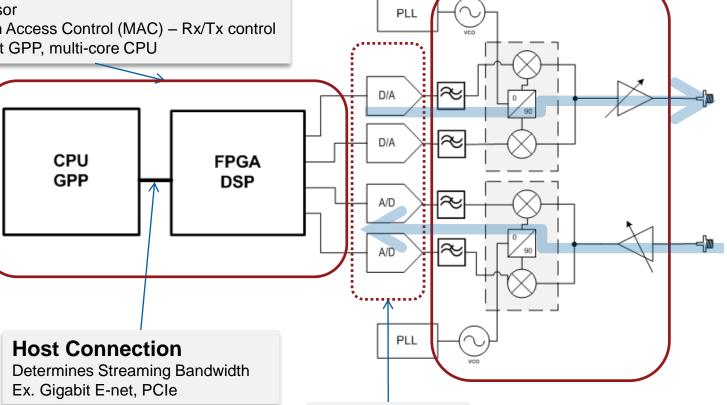

#### **Software Defined Radio Architecture**

#### **RF Front End** General Purpose RF

**Dual LOs** Contiguous Frequency Range

**Multi-Processor Subsystem** Real-time signal processor

Physical Layer (PHY) ex FPGA, DSP

Host processor

Medium Access Control (MAC) - Rx/Tx control

ex. Host GPP, multi-core CPU

**Baseband Converters**

## Design Tool Wish List

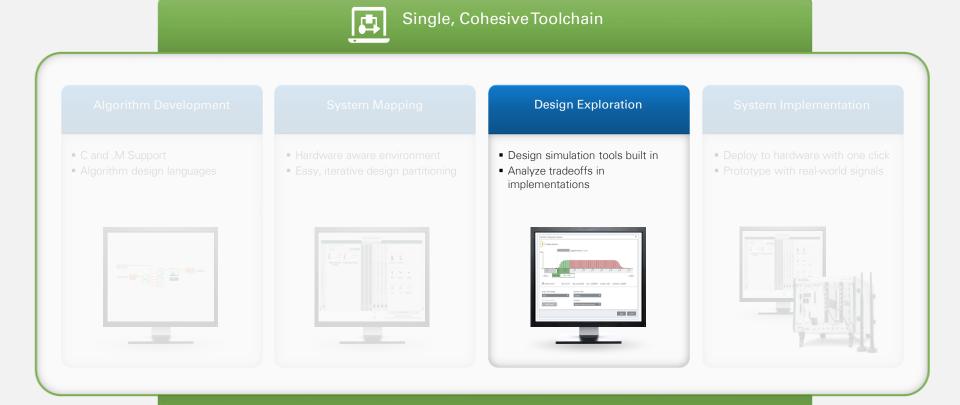

#### Single, Cohesive Toolchain

#### **Algorithm Development**

- C and .M Support

- Algorithm design languages

#### System Mapping

- Hardware aware environment

- Easy, iterative design partitioning

#### **Design Exploration**

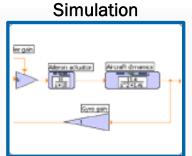

- Design simulation tools built in

- Analyze tradeoffs in implementations

#### **System Implementation**

- Deploy to hardware with one click

- Prototype with real-world signals

Collaborative DesignTeam

#### Single, Cohesive Toolchain

#### **Algorithm Development**

- C and .M Support

- LabVIEW (G)

- Multirate (SDF)

#### System Mapping

- Hardware aware environment

- Easy, iterative design partitioning

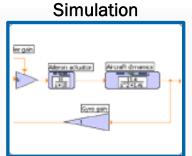

#### **Design Exploration**

- Design simulation tools built in

- Analyze tradeoffs in implementations

#### System Implementation

- Deploy to hardware with one click

- Prototype with real-world signals

Collaborative Design Team

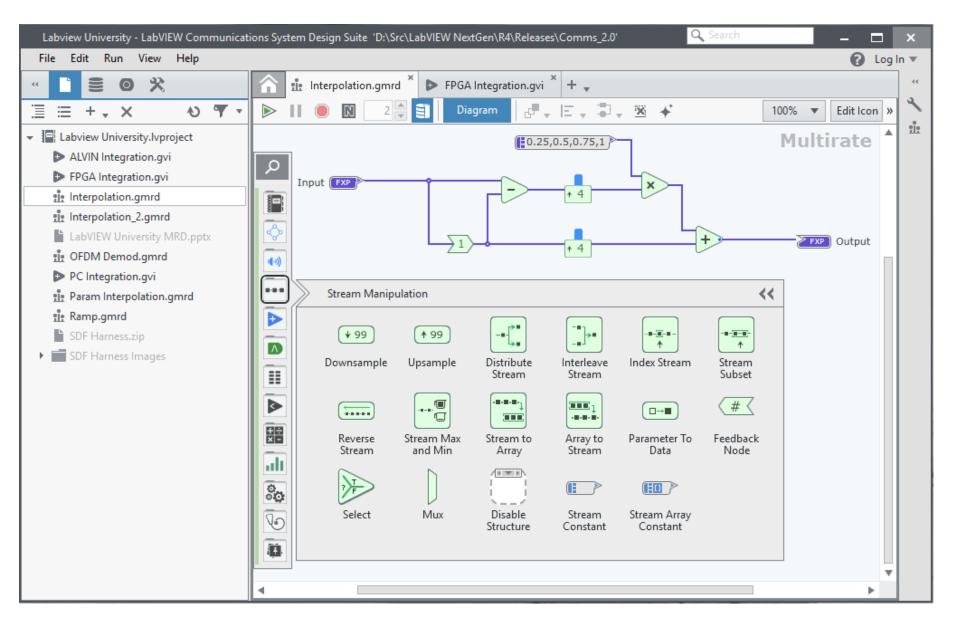

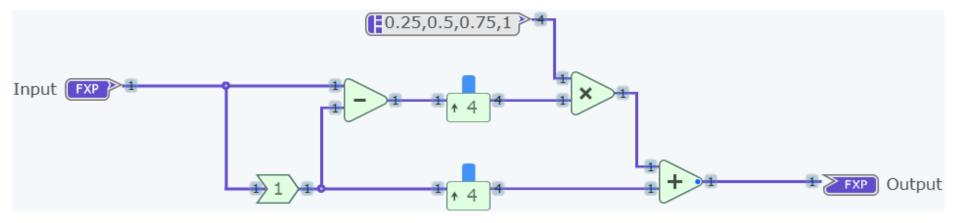

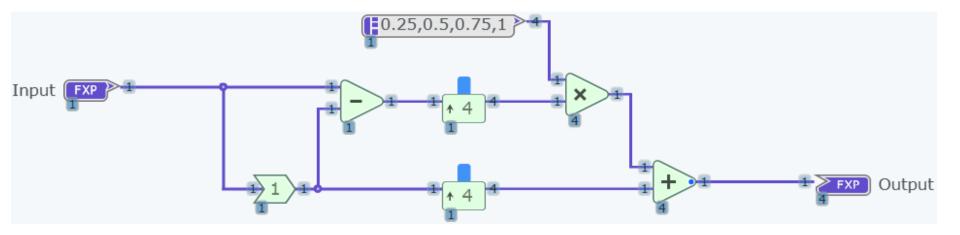

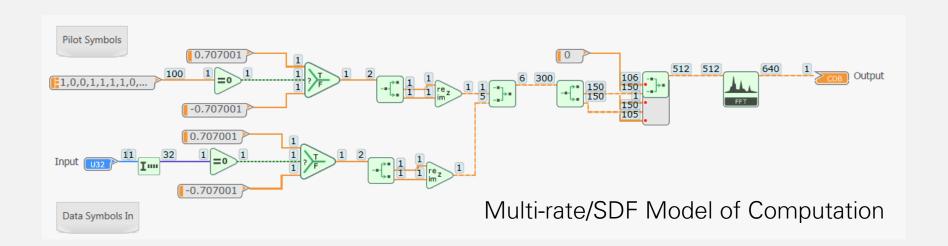

#### Multi-Rate Diagram

Enable high-level streaming Digital Signal Processing (DSP) algorithm implementation in hardware

- Parameterized SDF (Multi-Rate) dataflow

- Side-effect free

- Concurrent execution

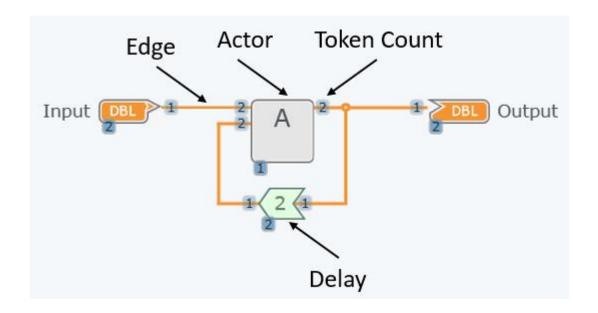

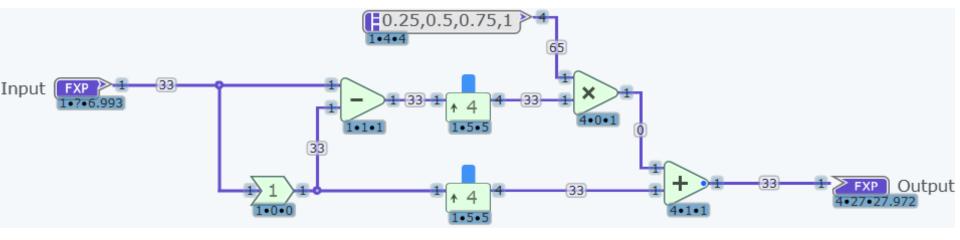

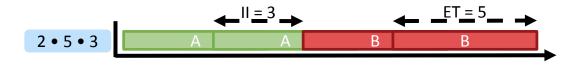

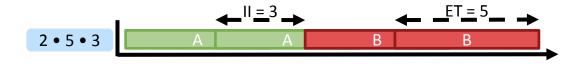

## SDF (MRD) Model of Computation

Repetition Count • Execution Time • Initiation Interval

Repetition Count • Execution Time • Initiation Interval

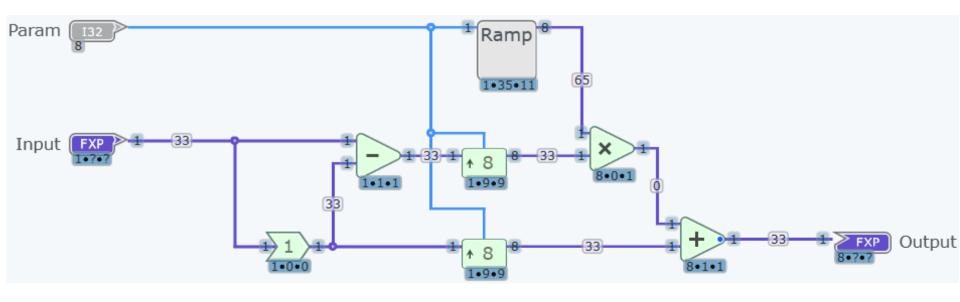

### Example: Parametric Linear Interpolation

Repetition Count • Execution Time • Initiation Interval

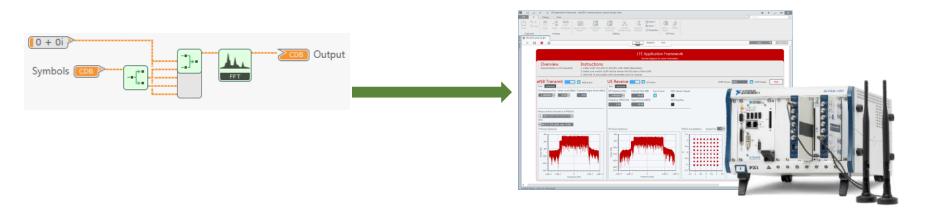

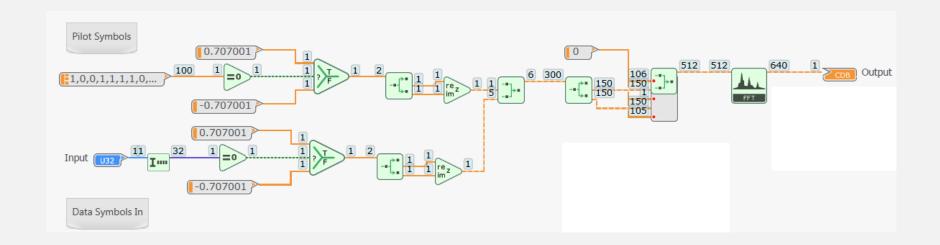

# Example: OFDM Transmitter

5 MHz, LTE-Like Design

- Symbol Mapping: 4 QAM

- Data/Pilot Structure: 1 Pilot (reference) for every 5 Data Symbols

- Frame Structure: 512 Elements [106 Zeros, 150 Data/Pilot, 1 Zero, 150 Data/Pilot, 105 Zeros]

- Cyclic Prefix Length: 128

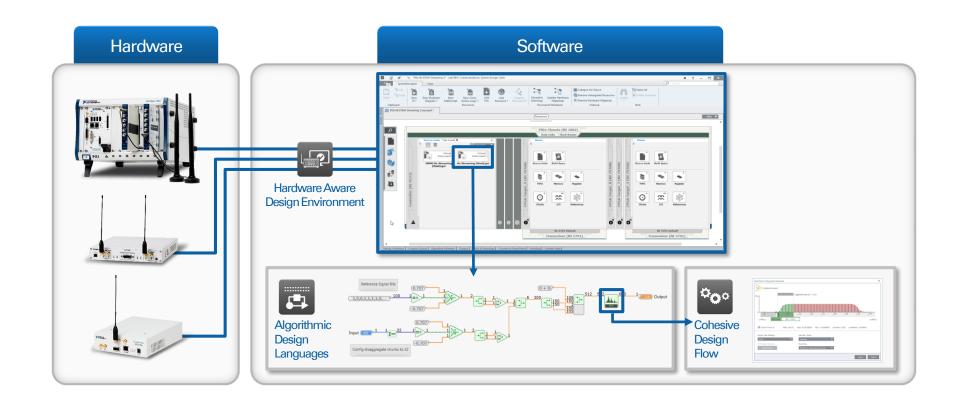

# Unified Design Flow

Collaborative Design Team

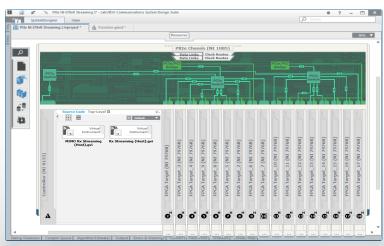

# Hardware Aware Design Environment

Interactive, visual representation of the physical system which:

- Enables system discovery and verification of system setup

- Provides hardware documentation and visualization of available resources

- Allows for design partitioning and deployment

- Enables articulation of system architecture

# Unified Design Flow

Collaborative Design Team

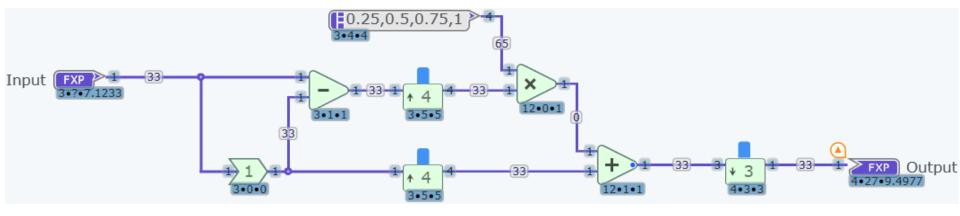

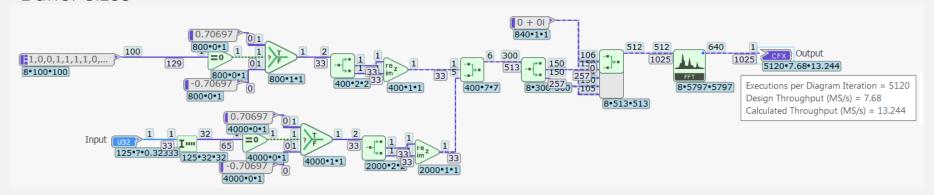

# Design Exploration for FPGA Deployment

Floating point design Fixpoint design Performance constraints:

Throughput, latency, resources

Simulation capability

# Design Exploration for FPGA Deployment

Float to Fix Point Conversion with a datadriven approach

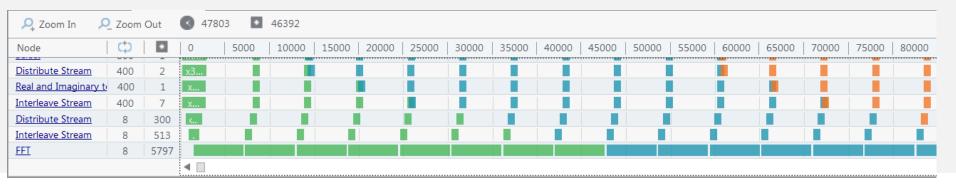

# Design Exploration for FPGA Deployment

#### Feedback on design based on constraints:

- Actual throughput

- Buffer sizes

Schedule View to analyze where the design can be further optimized

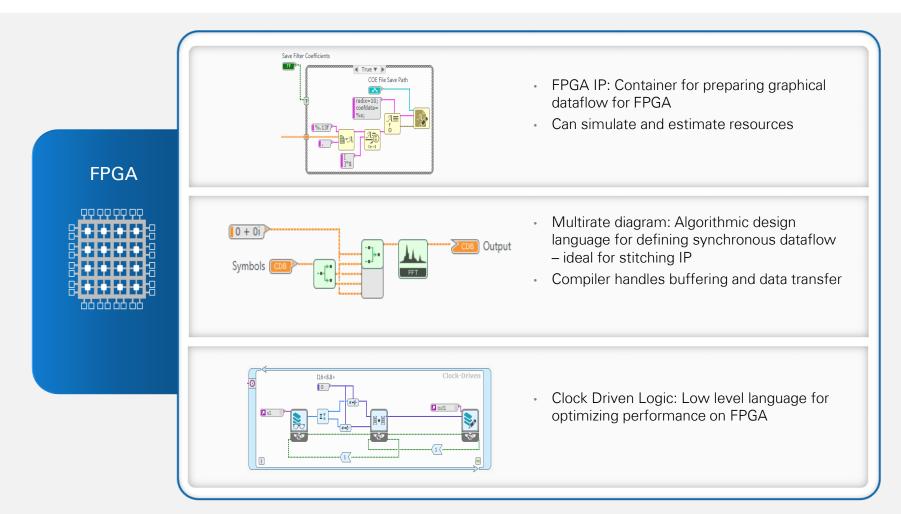

# Algorithm Design Languages: FPGA

# Unified Design Flow

Single, Cohesive Toolchain

# C and .M Support Algorithm design languages

# Hardware aware environment Easy, iterative design partitioning

Collaborative Design Team

#### Single, Cohesive Toolchain

#### **Algorithm Development**

- C and .M Support

- Algorithm design languages

#### System Mapping

- Hardware aware environment

- Easy, iterative design partitioning

#### **Design Exploration**

- Design simulation tools built in

- Analyze tradeoffs in implementations

#### **System Implementation**

- Deploy to hardware with one click

- Prototype with real-world signals

Collaborative DesignTeam

# Graphical System Design

A Platform-Based Approach for Measurement and Control