## **Objectives**

> After completing this module, you will be able to:

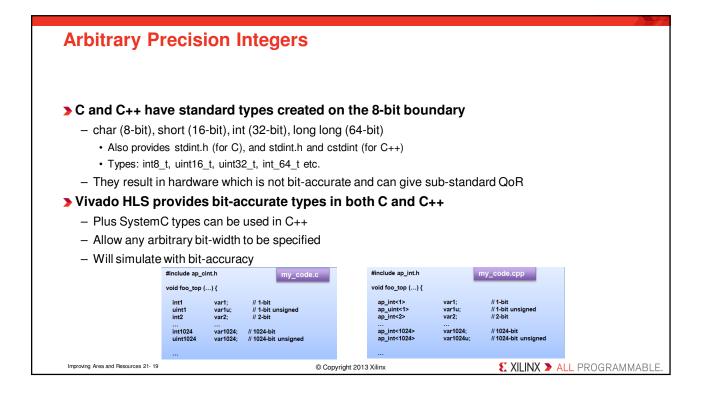

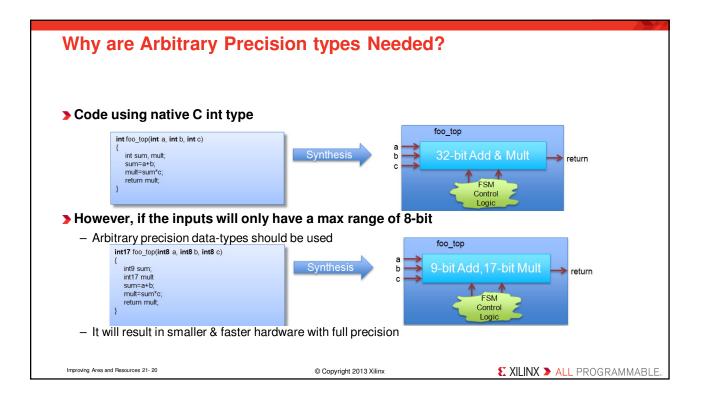

- Describe how arbitrary precision data types can reduce resource utilization

- List various area optimization techniques

- List means by which resource utilization can be reduced

Improving Area and Resources 21- 2

© Copyright 2013 Xilinx

**EXILINX >** ALL PROGRAMMABLE.

| Mapping Arrays                                                                                       |                                                                                                                                                                                                                                                    |                                                                                                                                               |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

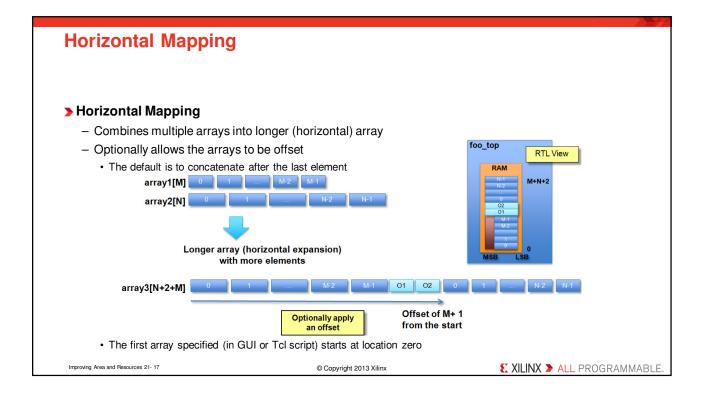

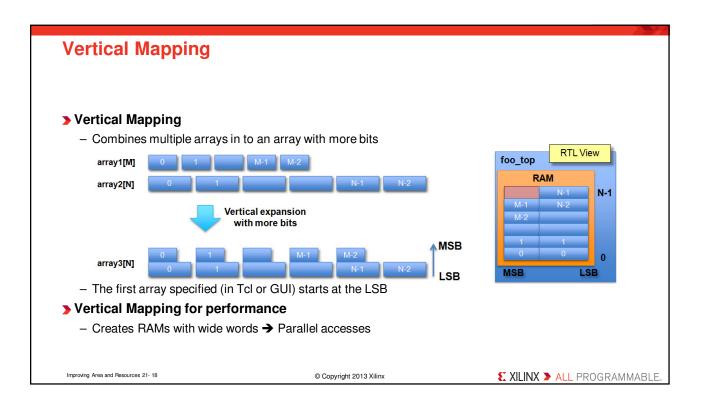

| <ul> <li>When arrays are in different function</li> <li>Arrays which are function arguing</li> </ul> | rrays<br>s very well<br>into larger arrays<br>thout code edits<br>apped<br>e same instance name<br><b>s to the type of mapping</b><br>ting performance<br>arrays involved are promoted to global<br>ons, the target becomes global<br><b>ments</b> | Vivado HLS Directive Editor Type Directive: ARRAY_MAP  Destination  Source File  Options variable (required): col_outbuf instance (optional): |

| <ul> <li>All must be part of the same function</li> </ul>                                            | on interface                                                                                                                                                                                                                                       |                                                                                                                                               |

| Improving Area and Resources 21- 16                                                                  | © Copyright 2013 Xilinx                                                                                                                                                                                                                            | € XILINX ➤ ALL PROGRAMMA                                                                                                                      |

| Summary                                             |                                                                       |                          |

|-----------------------------------------------------|-----------------------------------------------------------------------|--------------------------|

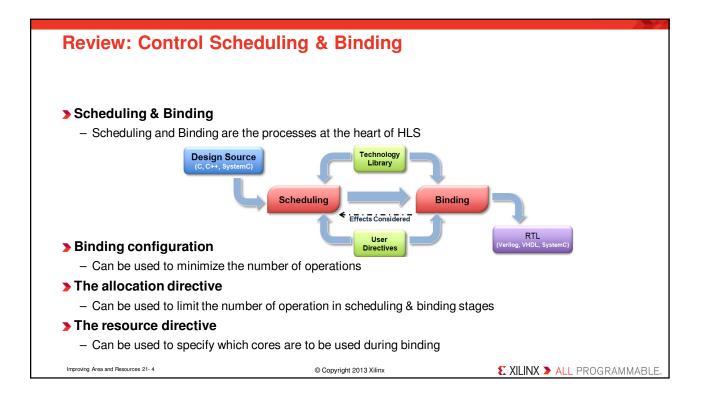

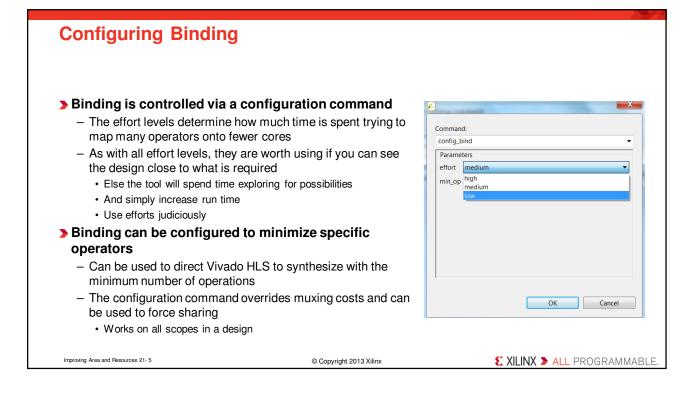

| Arbitrary precision data ty                         | e reduced using allocation and b<br>pes help controlling both the are | •                        |

| The design structure can I                          | -                                                                     |                          |

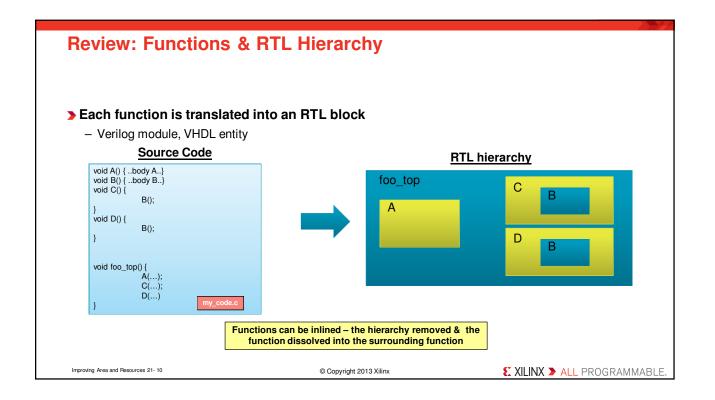

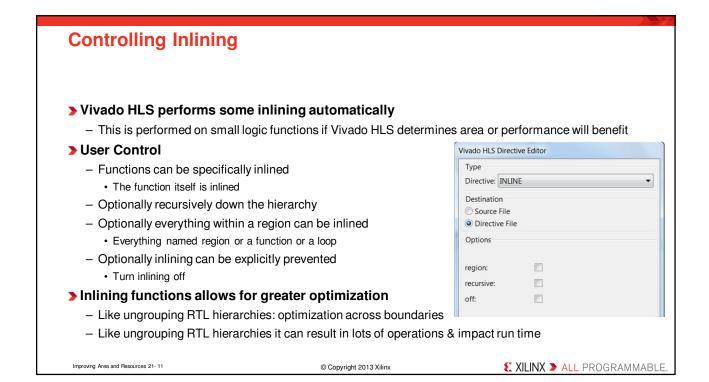

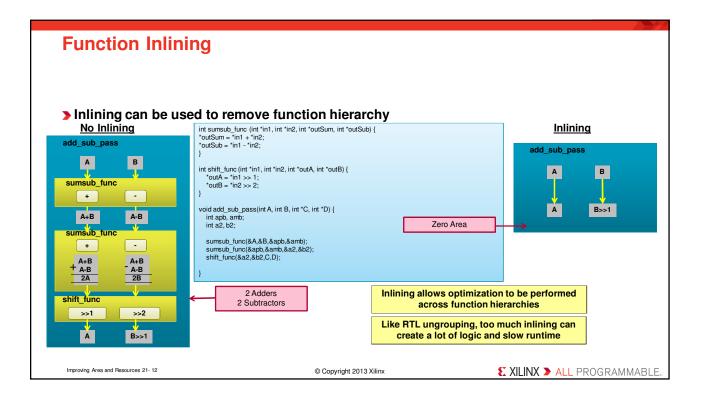

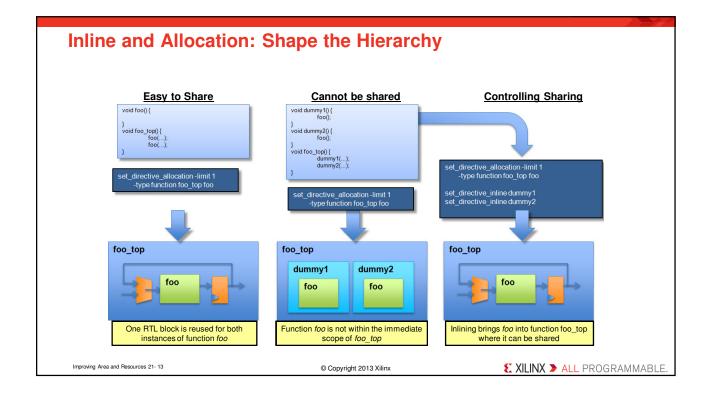

| <ul> <li>Inlining functions: direct imp</li> </ul>  | pact on RTL hierarchy & optimization po                               | ossibilities             |

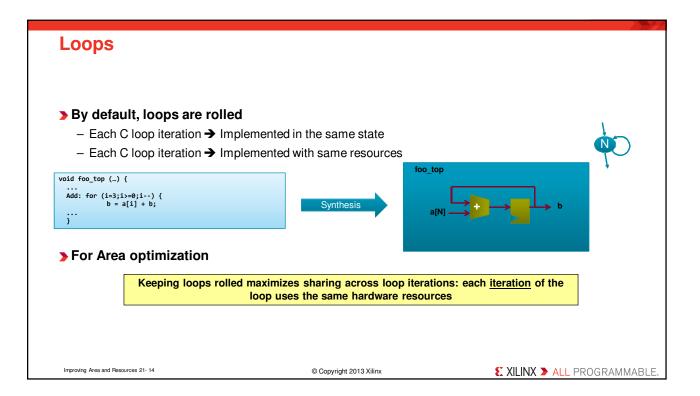

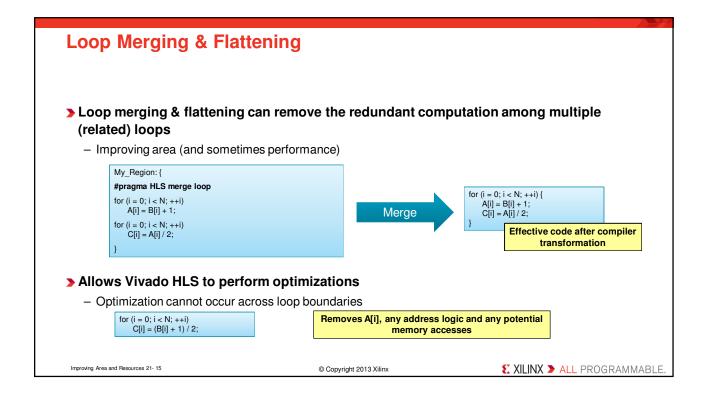

| <ul> <li>Loops: direct impact on reus</li> </ul>    | se of resources                                                       |                          |

| <ul> <li>Arrays: direct impact on the</li> </ul>    | RAM                                                                   |                          |

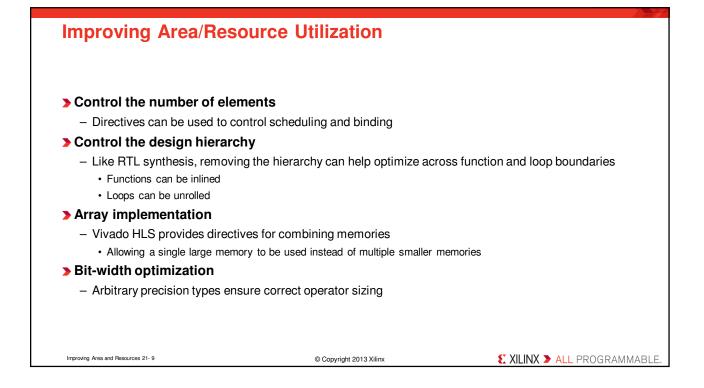

| > Major area optimization te                        | chniques                                                              |                          |

| <ul> <li>Minimize bit widths</li> </ul>             |                                                                       |                          |

| <ul> <li>Map smaller arrays into larg</li> </ul>    | jer arrays                                                            |                          |

| Make better use of existing I                       | RAMs                                                                  |                          |

| <ul> <li>Control loop hierarchy</li> </ul>          |                                                                       |                          |

| <ul> <li>Control function call hierarc</li> </ul>   | hy                                                                    |                          |

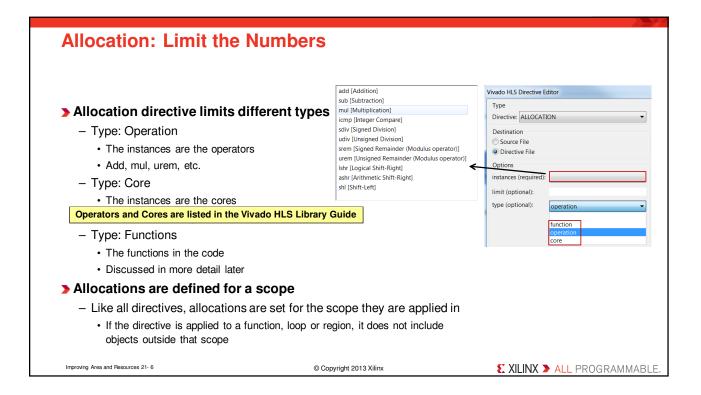

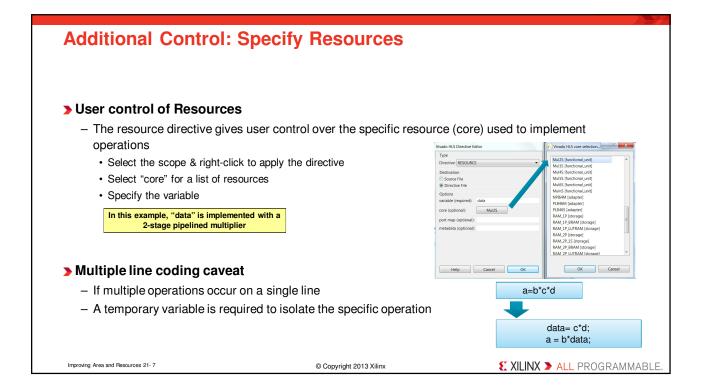

| <ul> <li>Control the number of operative</li> </ul> | ators and cores                                                       |                          |

|                                                     |                                                                       |                          |

| Improving Area and Resources 21- 22                 | © Copyright 2013 Xilinx                                               | XILINX ➤ ALL PROGRAMMABL |