The University of Texas at Austin

# **EE460M Lab Manual** Dept. of Electrical and Computer Eng.

# **Table of Contents**

| TABLE OF CONTENTS              | 2  |

|--------------------------------|----|

| ABOUT THE MANUAL               | 3  |

| LABS AT A GLANCE               | 4  |

| LAB POLICIES                   | 5  |

| FREQUENTLY ASKED QUESTIONS     | 6  |

| LAB ASSIGNMENT #0              | 16 |

| LAB ASSIGNMENT #1              | 18 |

| LAB ASSIGNMENT #2              | 22 |

| LAB ASSIGNMENT #3              | 27 |

| LAB ASSIGNMENT #4              | 4  |

| LAB ASSIGNMENT #5              | 4  |

| LAB ASSIGNMENT #6              | 13 |

| LAB ASSIGNMENT #7              | 18 |

| LAB ASSIGNMENT #8A             | 2  |

| LAB ASSIGNMENT #8B             | 22 |

| LAB ASSIGNMENT #9              | 25 |

| LAB ASSIGNMENT #10             | 28 |

| APPENDIX                       | 31 |

| LAB ASSIGNMENT – ARM PROCESSOR | 32 |

# About the manual

This document was created by consolidation of the various lab documents being used for EE460M (Digital Design using Verilog). It is intended to serve as a lab manual for students enrolled in EE460M at the University of Texas at Austin.

The creation process started towards the end of Spring 2011 and was accomplished by Aman Arora (TA, EE460M) under the guidance of Prof. Lizy John. In its present form, this document includes several changes (additions, deletions and modifications) incorporated over three semesters – Spring 2011, Fall 2011, Spring 2012. During the Spring/Fall 2013 semesters, all the labs were translated from VHDL to Verilog by Daniel Arulraj.

Several important modifications include:

- 1. Re-organization of Lab#1 and Lab#2 to remove several unimportant and quaint problems

- 2. Consolidation of tutorials which were spread over Lab#1 and Lab#2 into Lab#0

- 3. Addition of Lab#6B, which caters to design for test (DFT) concepts

- 4. Changes in values/design parameters in various labs

- 5. Re-organization of Lab#5 into three parts

- 6. Adding the ARM processor lab and the bowling score keeper lab in the appendix

- 7. Addition of several important details to improve clarity

- a. Mostly answers to students doubts

- b. Several diagrams

- c. Additional explanations

- 8. Convert the lab manual to Verilog

- 9. Added Lab#8,9,10

This document is currently maintained by Daniel Arulraj. He can be contacted through email at daniel.arulraj@utexas.edu. Please write to him in case of any questions or concerns or suggestions.

# Important: Do not print this entire document. This document will be updated during the semester.

# Labs at a glance

| S.No.  | Brief Description                                          | Objective                                                                                   | Duration  | Points<br>Possible |

|--------|------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------|--------------------|

| 0      | Tutorials – ModelSim and<br>Xilinx ISE and Nexys2<br>Board | Introduction to digital design<br>using FPGAs. Introduction to<br>simulation and synthesis. | 1 week    | 50                 |

| 1      | Subtractor and ALU                                         | Simple combinational circuit design                                                         | 1 week    | 100<br>(40+40+20)  |

| 2      | Excess-3 code converter and BCD counter                    | Simple sequential circuit design                                                            | 1 week    | 100<br>(40+30+30)  |

| 3      | Package sorter and<br>Traffic Light Controller             | More digital design. Introduction to testbenches.                                           | 1.5 weeks | 120<br>(20+50+50)  |

| 4      | Parking Meter                                              | Advanced digital design.<br>Interfacing with 7-segment<br>display and push buttons.         | 2 weeks   | 150                |

| 5      | A basic SNAKE game                                         | Interfacing with PS/2 Keyboard and VGA display                                              | 2 weeks   | 180<br>(50+50+80)  |

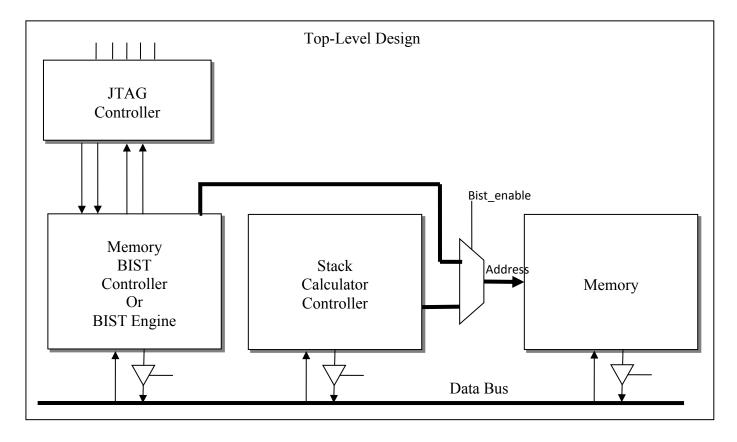

| 6      | Stack Calculator                                           | Using Block RAMs on FPGAs                                                                   | 1 week    | 100                |

| 7      | MIPS Processor                                             | Basic microprocessor design                                                                 | 2 weeks   | 150                |

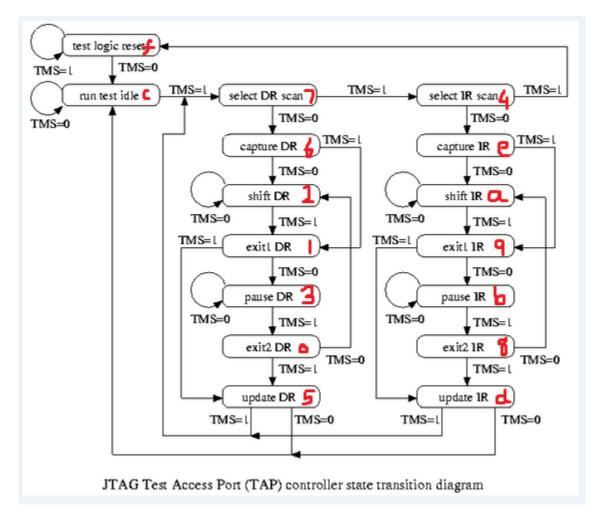

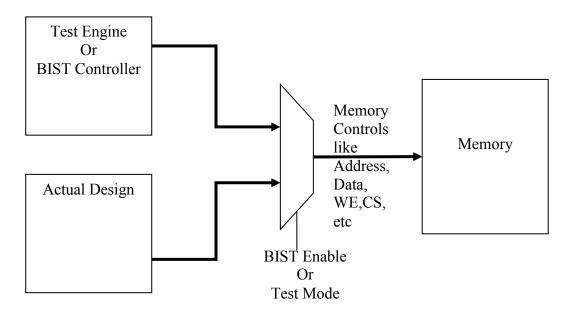

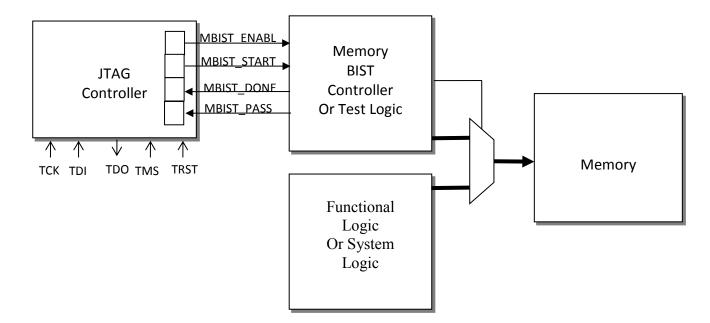

| 8      | Memory BIST                                                | Understanding JTAG and BIST                                                                 | 1 week    | 100                |

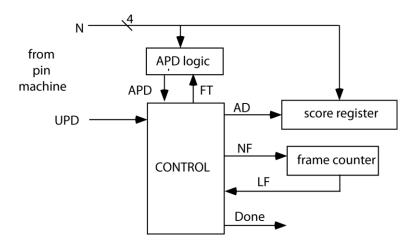

| 9-OPT  | Bowling Score Keeper                                       | State machines, logic design                                                                | 2 weeks   | HW (6%)            |

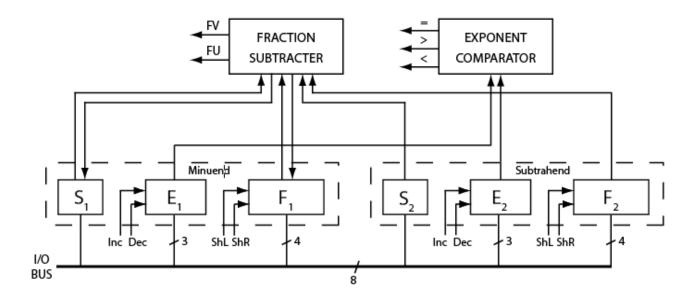

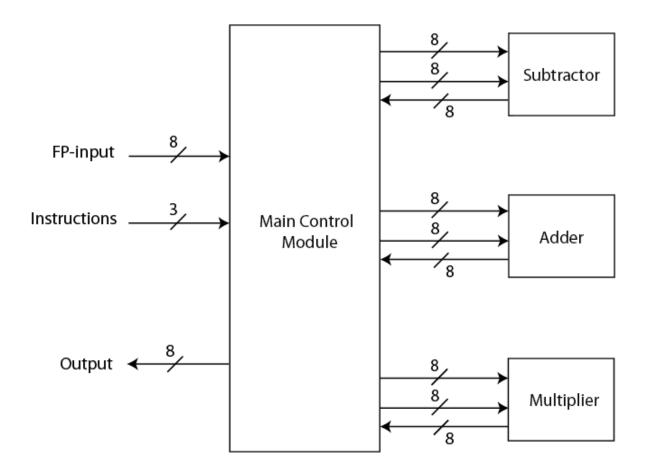

| 10-OPT | Floating Point Unit                                        | Arithmetic Units, logic design                                                              | 1.5 weeks | HW (4%)            |

# Important: Please check the schedule sheet on Canvas for the lab due dates

The OPTIONAL labs (9 and 10) are an alternate for paper and pencil homeworks.

# **Lab Policies**

- 1. You will (have access to and) work in the lab in ENS 302. This is also where TA office hours will be held.

- 2. This document, available on Canvas, will serve as the lab manual for the entire semester. The document contains all the lab information you need to do the labs (except for few codes in labs 6 and 7). You can work on your own pace throughout the semester, but you have to follow the due dates for submission (listed in the schedule document) and the check out procedures.

- 3. All communication will be done through Canvas. So, please keep checking Canvas for notifications and updates. Important information will also be emailed.

- 4. 15-minute lab discussion sessions will be held at appropriate dates (listed in the schedule document) before the lecture. These will be conducted by the TAs. It is advisable to read about that lab from the lab manual before coming to the class, so that you are better prepared to ask questions and resolve doubts.

- 5. Labs 0, 1 and 2 are to be done individually. Labs 3 through 7 can be done in groups of two. Also, working in groups does not mean that you work on separate parts of the lab. Both the group members are supposed to know and answer questions about all parts of the lab. You can switch partners whenever you want.

- 6. Grading will occur in two parts: submission and demo (checkout).

- 7. For submission, upload all relevant files (specified with each lab under the 'Submission Details' section) via Canvas. One of the members from each group should log into Canvas and go to "Assignment" section and then upload all the necessary files under the appropriate link.

- 8. Lab due dates (submission dates) are specified in the course schedule document on Canvas.

- 9. After you submit your files, you have to demonstrate your designs to one of the TA's in the ENS 302 lab. Once the lab is submitted, DO NOT make changes! You must demo with the code you submitted. In the event you decide to change the code for the demo, the day of the demo will be considered the turn-in date, and the appropriate late penalty will be applied.

- 10. A checkout sign-up sheet is available on Canvas. After every lab due date, the TAs will email the class to sign-up for a checkout slot. Put your name in that sign-up sheet and reserve a time-slot for your check out. Please reach the lab at least 5 minutes before your slot. In case of group labs (lab 3 and above), only one member of the group should submit the files but both members of a group must checkout together. So, the entries in the checkout slot registration sheet should contain two names.

- 11. In case you miss your check out slot, you can check out for that lab during office hours anytime before the next lab's due date. In other words, the TA's will not entertain requests for checking out labs older than the previous lab.

- 12. The possible points for each lab are mentioned in the 'Labs at a glance' section of this manual. Late submissions (not late checkouts) will lead to penalty according to the following rules:

- a. One day late submission less 10% of your normal score

- b. Two day late submission less 20% of your normal score

- c. Three day late submission less 30% of your normal score

Submissions late by more than 3 days will not be accepted and you will be marked zero (unless you have taken permission from the professor).

13. Sundays are not counted for late submissions. So, if a lab is due on Saturday and you submit it on Monday, it will be considered 1-day late submission.

# **Frequently Asked Questions**

# **MODELSIM**

# Q. In ModelSim 6, when I click the message saying *x* errors in the transcript window, the window that pops up does not show me any errors?

This is because you file name (complete path) has spaces in it. While using ModelSim, please make sure that the file name doesn't have any white spaces. In other words, do not have your programs saved on a path like "xyz\Documents and Settings\user1\lab 1\file.v". Please make a folder on the Z: drive of the computer you work on and keep your project/source files there.

#### Q. When I click on ModelSim, it gives me an error saying failed to checkout license.

In case invoking ModelSim shows a licensing error on the lab computers, please run the Licensing Wizard first (Start->Programs->ModelSim->Licensing Wizard), and then launch ModelSim.

#### Q. How do I create and run a do-file?

The ModelSim tutorial talks about creating a file of commands in the end (called a do-file), but does not explain how to do it clearly. Here is how you can do this: Basically, the commands like force, run, etc that you provide on the transcript window can be saved in a file and that file is called a "do-file". The benefit of having a do-file is to be able to re-run all the commands by just a single click, rather than typing them again and again. For example, if you have your do-file ready during the checkout, you can just execute it instead of typing the individual commands all over again.

There are two ways of creating a do-file.

- 1. You can manually write those commands in a file using a text editor and save it with a ".do" extension.

- 2. You can type the commands on the transcript window, and then have ModelSim create the file for you. For this, type the commands in the transcript window (keep the transcript window selected). Then go to "File->Save As", and then provide the name of the file with a .do extension.

To execute the commands in the do-file, make sure the transcript window is active. Then, go to "File -> Load" and then provide your do-file to the tool.

#### Q. Can I view variables on waveforms?

Viewing variables on the waves is just like viewing signals (of course, you should be simulating your design to view the waves). The 'Objects' window shows you the signals in a design. Similarly, the "Locals" window shows the variables in the selected module/always block. For seeing variables, go to the 'View' menu and click on 'Locals'. A 'Locals' window will appear.

When you are simulating, you can see that a "Sim" pane appears near to your "Project" and "Library" panes. Click on the "Sim" pane and it will show you the design hierarchy. You can click on any module or a line number of an always statement whose variables you want to see. Now, in the "Locals" window, you can click on variables and then drag to the waveform window.

# Q. Some signals in my design are not visible in the "Objects" window, and so I can't view their waveforms.

This is because ModelSim performs a series of optimizations on your design and can get rid of some signals. The 'optimized out' signals cannot be seen in the "Objects" window. You can disable optimization in two ways:

- 1. While starting simulation, instead of just double clicking on the module name in the "Library" window, right click and say "Simulate without Optimization".

- 2. On the transcript window, append " -novopt" to the "vsim" command

**Q.** Can I view waveforms of signals inside the design hierarchy (modules other than the top module) When you are simulating a design, you can see that a "Sim" pane appears near to your "Project" and "Library" panes. Click on the "Sim" pane and it will show you the design hierarchy. You can click on any module in the design. When you click on a module, the "Objects" window shows the signals in that module. Now, in the "Objects" window, you can click on signals and then drag to the waveform window (or you can right click a signal and say Add->To Wave->Selected Signals).

# Q. How can I change the way signals are shown on the waveforms (To change viewing 000101 to 5)

Right on the signal in the "Waves" window, got to "Radix" and select the one you want.

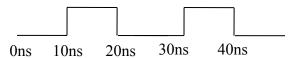

# Q. How can I create a clock using the force statements in ModelSim during simulation?

To create/generate a clock, you can use the following command:

# force clk 0 0 ns, 1 10 ns –repeat 20 ns

This command creates a clock of period 20 ns with 50% duty cycle as shown below:

You can change the period and duty cycle as you want by modifying the force statement appropriately.

# Q. I used the 'force' command to force a signal. Now I want the design to drive it. But it is just stuck to that value.

A force statement forces the specified value onto the specified signal at the specified time and then that value remains on that signal for the entire simulation. It can only be changed by another force statement.

Adding "-deposit" option to the "force" command puts the specified value on the specified signal at the specified time, but lets it change anytime after that (if another driver wants to modify/override it; for example an assignment statement in the design).

For example, let's assume that you have an output that you want to initialize to 0 at the beginning of the simulation. Assuming also that you have not initialized this output to 0 in your code, you may simply type: force Z 0 0 ns. You will note after running the simulation that Z never changes. To overcome this problem, change the above statement to: force –deposit Z 0 0 ns. The deposit will simply deposit the value of 0 to Z at 0 ns instead of freezing it at 0.

The "-cancel" option cancels the force on a signal at a specified time.

You can look into more options of the force statement by going to "Help -> PDF Documentation -> Reference Manual" in ModelSim.

# **XILINX ISE**

#### Q. Xilinx ISE is so slow! What should I do?

It is recommended, in general, to work on files in the local directories (C: drive, for example) while working with Xilinx ISE and ModelSim in the lab. Your desktop is a networked drive and these tools work really slow when they have to fetch files over the network. But since the files in local directories get cleaned up when you log out, make sure you make a copy somewhere before you logout.

#### Q. What is a UCF File? Can I hand write it instead of using the PACE window?

The UCF file is the file which tells Xilinx ISE to map the inputs and outputs of your design to specific pins on the FPGA. The file also has other things like clock constraints etc, but we are not going to be concerned about them in this lab. The PACE tool helps you graphically create the UCF file. However, you can manually write a UCF file too (it is just a text file with a specific format). This may sometime be required if the PACE tool does not work. Assuming the the PACE tool works in your first lab, to view the UCF generated by it, click on the UCF filename in the Design Hierarchy panel. Now, in the processes panel, expand 'User Constraints' by clicking on the '+' sign. Now double click, 'Edit Constraints'. This will open the UCF file in the right hand side of the window. The syntax is self-explanatory. So, if PACE doesn't work in any lab, open the UCF from a previous project, copy it to the current project and modify it manually for the current project's constraints.

# **VERILOG**

# Q. Can I model combinational logic using always statements? How?

Ideally, concurrent statements are used to model combinational logic and always statements are used to model sequential logic (flip flops and latches). However, always statements are not restricted to that. You can model combinational logic using them. But it is important to note that when using an always statement to make combinational logic, the sensitivity list of the always statement should contain all the signals which are being 'read' in that always block. In other words, to synthesize combinational logic using an always block, all inputs must appear in the sensitivity list.

For example, if you were to model a mux, you would say:

```

always @(a, b, sel)

begin

if (sel == 1) z <= a;

else z <= b;

end</pre>

```

Using a always statement to model combinational logic is handy because statements like if, case, etc (which are very useful and intuitive) can only be written inside always statements.

# Q. What care should I take when using the always statement to write sequential logic?

When using an always statement to model sequential logic, the only thing in the sensitivity list of the always statement should be the clock (or a reset signal, if it is an asynchronous reset). And there should be a' 'posedge' or 'negedge' in the sensitivity list before the clk. This is because flip-flops are edge triggered elements.

```

Flip-flop without a reset

```

```

always @(posedge clk) //positive edge triggered

begin

q <= d;

end

Flip-flop with an async reset

always @ (posedge clk, negedge rst) //positive edge triggered with reset

begin

if(rst == 0)

//async active low reset

begin

q <= 0;

end

else

begin

q <= d;

end

end

```

Flip-flop with a sync reset

```

always @ (posedge clk) //positive edge triggered

begin

if(rst == 0) //sync active low reset

begin

q <= 0;

end

```

```

else

begin

q <= d;

end

end

```

On the other hand, a latch is a level triggered element. A resettable latch can be modeled as:

```

always @(en, rst, d)

begin

if(rst == 0)

begin

q <= 0;

end

else if(en == 1)

begin

q <= d;

end

end</pre>

```

**Q.** Why can I not instantiate a module inside an 'if' statement (or an always block, for that matter)? It is important to realize that a module is not like 'calling' a function in C. It is an instantiation of that module.

Therefore, it cannot be conditional. If you have to instantiate a block in your design, it will be always present there.

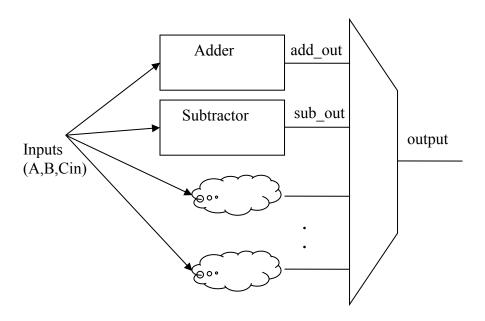

Let us take an example. Say you have an adder and a subtractor. You design's specifications say that when the input MODE is '1', the design should work as an adder, while when the MODE is '0', the design should work as an subtractor. Now, this does not mean that you can have something like this:

```

always(...)

begin

if(MODE == 1)

adder adder_inst(A,B,Sum);

else

subtractor subt_inst(A,B,Diff);

end

```

Since we are modeling hardware, we cannot say that if MODE is 1, Adder is 'called' and when MODE is 0, subtractor is 'called'. This is a wrong way of thinking.

Instead you should think of this as: Adder and Subtractor are always present. The output of the design can be driven by either the Adder or the Subtractor depending on MODE. So you should have something like this:

```

adder adder_inst(A,B,Sum);

subtractor subt_inst(A,B,Diff);

always(...)

begin

if(MODE == 1)

output_ALU <= Sum;

else

output_ALU <= Diff;

end

```

#### **GENERAL**

#### Q. What tests should the 'do' file that I submit on canvas contain?

It is always better to submit a do-file which has sufficient number of input combinations (not just the ones given in the lab description).

## Q. I am getting a multiple drivers error. What should I do?

A multiple driver error is because there is more than one thing driving a signal. This can happen if you are driving a signal from two sources: like one always block and one concurrent statement, or two always blocks. Realistically, it is not possible to do so (without having contention, which we are staying away from). There is nothing you can do to get rid of this, other than changing your design.

# Q. My design compiles successfully in ModelSim. When I simulate, I get weird errors (error loading design, etc) and I can't simulate.

The compilation process looks at individual modules in your design and checks for syntactical and semantic correctness. Simulation lets you apply inputs and observe outputs. Between compilation and simulation, is a step called elaboration (which is usually hidden from you, and happens when you start simulation in ModelSim). During this step the design hierarchy is generated. Connections between various modules, and search for entities referenced as components in a design, etc are done at this stage. If there is a problem at this stage (for example, there is a component declaration in your top module but the module for that component is missing), they are reported just before simulation. So, now you know where to look for when you get errors just when you start simulation.

# Q. Will setup and hold time be met in my simulation? Or If I add some logic between two stages in my design, will the delay affect the output? Or should I force my input sometime before the clock edge to satisfy setup and hold time constraints?

Remember that the simulations that you are doing in the lab are all RTL simulations. They are zero-delay simulations (assuming you are not modeling delays using '#' statements). Therefore, there is no concept of delays of gates or setup-hold time of flip-flops. If we were doing post-synthesis simulations, then we would have concerned timing issues.

# **GOOD DESIGN PRACTISES**

# Q. Are there any general 'good' design practices that I should follow?

- 1. Writing Verilog feels like writing software. But it is a good idea to think 'hardware' while writing code!

- 2. Do not use '#' (delay) statements in your designs in the lab. Testbenches may use these. Eg. To generate a clock signal in a testbench you can say "#10 clk = ~clk;"

- 3. A state machine can be designed using either a single always block (like Figure 2.56 in the text) or using two always blocks (like Figure 2.54 in the text). Both ways are correct. However, it is easier to design it using a single always block. Generally, the single always block partakes less debugging effort.

- 4. Stay away from 'variables' unless you are absolutely sure.

- 5. Concurrent statements are continuous drivers. Do not use them for initializations.

- 6. It is a good idea to have a reset signal in your design (even if not mentioned in the lab description). Use this signal to reset all the things you want to.

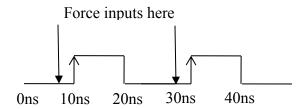

- 7. While simulating your design, it is always a good idea to stagger your inputs with respect to the active clock edge. For example, if your active clock edge is occurring at 10ns, apply your inputs sometime before 10ns, say at 8ns. This ensures that when your design was clocked, the input was successfully read. If your active edge occurs at 10ns and your input also changes at 10ns, then it becomes hard to see whether the input was successfully captured by the clock edge or not. Debugging becomes harder if you have your inputs like that.

- 8. Don't limit your testing to the input sequences mentioned with the problem statement. During the checkouts, the TAs will apply several input combinations to test your design. So, make sure to do a thorough testing of your design using sufficient number of inputs.

- 9. Generally, we tend to ignore warnings from the tools. But make sure you look at all the warnings after the synthesis process is completed. Sometimes there are problems in your design like missing connections, latches, etc. Such issues make the tool infer your design differently from what you want or expect it to be. These warnings might contain the reason why your design does not work on the board.

# Q. My design works in simulation. But it does not work on the board. What should I do?

There is no one sentence answer to this question. You can try the following things to help you debug your problem:

- 1. Follow the good design principles discussed above.

- 2. Look for any warnings in the synthesis report.

- 3. Make sure there are no latches in the synthesized output.

- 4. Follow the synthesis-friendly code guidelines discussed in the next question

# Q. My design works in simulation. But Xilinx ISE throws an error during synthesis, saying "Bad Synchronous Description". What am I doing wrong?

The one line answer to this question is that you are not writing synthesizable code. Here are a few tips:

1. posedge/negedge should only be used on clocks

2. An always statement used to model sequential logic should only have clock (and reset, if you need one) in the sensitivity list, and an always statement to model combinational logic should not have clock in the sensitivity list. (this is illustrated in detail below)

3. A signal cannot change on both negative and positive edges of clock (This is specific to the design you do in the lab because the FPGA hardware does not have dual edge triggered flops. This is true for

most industrial design also. However, there may be some very high end designs which use dual edge triggered flops, in which case this constraint on your code gets removed.)

4. Make sure the tool is able to decipher the value of each signal under each condition.

#### Synthesis friendly 'always' statements

A. If you use always statement for a combinational logic, make sure the sensitivity list contains all inputs. And the clock should not be amongst those inputs! If you feel like you need the clock, it means you want to write sequential logic. Think again!

B. All always blocks other than the ones used for combinational logic will have a structure similar to this:

```

always @(posedge clk, negedge rst)

begin

if(rst == 0) //async active low reset

begin

//initializations

end

else

begin //positive edge triggered sequential logic

//actual stuff

end

end

```

C. So, any always block in your design should fall into either of the following categories:

```

always @ (posedge clk, negedge rst) //model posedge triggered sequential logic with

reset

begin

//async active low reset

if(rst == 0)

begin

//initializations

end

else

begin

//actual stuff

end

end

always @(posedge clk) //model positive edge triggered sequential logic

begin

//stuff

end

always @(a,b,c) //model combinational logic

begin

//stuff

end

```

#### Q. Xiinx ISE reports there are latches in my design. Where am I going wrong?

Latches are caused when you forget an 'else' block in an 'if' or 'case' statement in a always block intended to make combinational logic. Look at your design and find such cases.

Example:

The following always statement was intended to make do some selection. It was expected that a mux will be generated for both f and g.

```

always @(sel, a, b, c)

begin

case (sel)

3'b000 : f <= a; g <= c;

3'b001 : f <= b; g <= d;

3'b010 : f <= a; g <= c;

3'b010 : f <= a; g <= c;

3'b011 : f <= b; g <= d;

3'b101 : f <= b; g <= d;

3'b101 : f <= a; g <= b;

endcase

end</pre>

```

But notice that the assignment to 'g' was missed in one case. And one case (100) was not mentioned. Therefore, latches were inferred for both 'g' and 'f'. Here is the correct way to write this:

```

always @(sel, a, b, c)

begin

case (sel)

3'b000 : f <= a; g <= c;

3'b001 : f <= b; g <= d;

3'b010 : f <= a; g <= c;

3'b011 : f <= b; g <= d;

3'b101 : f <= b; g <= d;

3'b101 : f <= a; g <= b;

default : f <= a; g <= b;

endcase

end</pre>

```

Also, in an always block used to model combinational logic, if you forget to assign all signals under all conditions, you will end up with latches. So, to synthesize combinational logic using an always block, all signals must be assigned under all conditions.

Example:

```

always @(state, a, b, c, d, e)

begin

case (state)

0: if (a == 0) next_state <= 1; //IDLE STATE

1: //INITIAL STATE

begin

if (a == 1) next_state <= 2;

else next_state <= 3;

end

2: ...</pre>

```

Since 'next\_state' is not assigned when a is '1', a latch is inferred. To avoid unwanted latches, a good way is to make sure you assign all signal under all possible conditions.

```

always @(state, a, b, c, d, e)

begin

case (state)

0: //IDLE STATE

begin

if (a == 0) next_state <= 1;

else next_state <= 0;

end

1: //INITIAL STATE

begin

if (a == 1) next_state <= 2;

else next_state <= 3;

end

2: ...</pre>

```

But an easier (sometimes; depends on functionality) way can be to create a default assignment for all the variables in the always block.

```

always @(state, a, b, c, d, e)

begin

next_state <= 0; //default assignment

case state

0: if (a == 0) next_state <= 1; //IDLE STATE

1: //INITIAL STATE

begin

if (a == 1) next_state <= 2;

else next_state <= 3;

end

2: ...</pre>

```

# Lab Assignment #0

This lab is a tutorial lab. You don't have to design anything in this lab, just go through the tutorials and perform them on the lab computers individually. In this course, in almost all the labs we will be doing the following steps:

Step 1: Writing Verilog code of the circuit we want to implement

**Step 2**: Simulating the Verilog code using a simulator (ModelSim) to check if the intended functionality has been achieved

**Step 3**: Synthesizing the Verilog code using a tool form Xilinx called ISE so that it can be programmed onto an FPGA

**Step 4**: Programming the FPGA (a Spartan3E series FPGA from Xilinx) on the lab board (called Nexys2 board) using a tool called Adept

**Step 5**: Applying inputs to and observing outputs from our circuit using the peripherals (like switches, buttons, LEDs, etc) on the Nexys2 board

To be able to do all this, we need to learn how to use ModelSim and Xilinx ISE tools, and we also need to understand the capabilities of the Nexys2 board and how can we program the Xilinx Spartan3E FPGA on it using Adept. The following activities will help you go through all the steps so you can learn and use the concepts in the upcoming labs.

# **Activity 1: ModelSim tutorial**

Mentor Graphic's Modelsim tool will be used to perform the functional simulation of our Verilog code for the course. This software is available in all of the ENS labs. Modelsim is also available as a free download with Xilinx's Webpack software so you can install it on your own computer..

Go through the "**Modelsim Tutorial**" posted on Canvas under "Files/Labs/Documentation". This tutorial goes through the basic steps in compiling and simulating within the Modelsim environment using a simple D-flipflop as an example.

# **Activity 2: Xilinx ISE tutorial**

The XILINX ISE tool is used to synthesize circuits and place & route them for a particular FPGA. Then, a BIT file needs to be generated (we use the Digilent Adept tool for that) which can be programmed onto the FPGA so that the FPGA now contains the circuit you designed. Go over the XILINX tutorial that has been posted on Canvas. You may also visit <u>www.xilinx.com</u> and browse the Spartan 3e manuals for help.

Go through the "Xilinx ISE tutorial" posted on Canvas under "Files/Labs/Documentation".

# Activity 3: Nexys2 board tutorial

Read through the **Nexys2 Board User Manual** on Canvas under "Files/Labs/Documentation" to understand the features and capabilities of the board to be used in all the labs. Then go through **Nexys2 Board Configuration** manual under "Files/Labs/Documentation". This document describes how to program the FPGA on the board.

# Activity 4: Xilinx ChipScope tutorial

The XILINX ChipScope tool is used for debugging FPGA based designs. It is a software based logic analyzer that allows monitoring the status of selected signals in a design in order to detect possible design errors. The basic concept is that you generate some components (called cores) using a tool (called Core Generator), add these cores to your design, synthesize it and then put it on the board. Then you open up a tool on your computer (called ChipScope Analyzer) and you can observe the signals of your design on the screen. Which signals you want to observe is declared when you integrate the cores in your design.

Go through the "Xilinx ChipScope tutorial" posted on Canvas under "Course/Labs/Lab Info".

# Questions

You should be able to answer (almost all of) the following questions after going through these tutorials:

- 1. What is the ModelSim? What is the role of the transcript window which appears on the bottom of the main ModelSim window?

- 2. What is a delta cycle in a Verilog simulator like ModelSim?

- 3. How do you create a do-file of commands entered in the transcript window in ModelSim?

- 4. Describe the roles and functionality of the following tools in the Xilinx ISE suite: Project Navigator, RTL schematic viewer, and PACE.

- 5. What is the purpose of using the Adept software?

- 6. Is it possible to display two digits using the 7SEG LEDs at the same time on the Nexys2 boards? Note there are only 7 pins corresponding to a single 7-segment digit.

- 7. If we want to use the push buttons on the board reliably, what should we do first to the incoming signal into the FPGA? How do we implement this in Verilog?

# Submission and Checkout details

Submit a text/doc/pdf file containing the answers to the questions given above on Canvas. Name the file "your\_last\_name.extension". You need to demonstrate that you performed the tutorials during the checkout. Also, you will be asked questions about various aspects covered in the tutorial. Your ability to answer them and your demonstration will decide your score.

# Lab Assignment #1

## Guideline

This lab is to be done individually. Each person does his/her own assignment and turns it in.

## **Objective**

To learn designing basic combinational circuits in Verilog and implementing them on an FPGA.

# **Problem 1: Subtractor Design**

- a. Write Verilog code for a 1-bit full subtractor using logic equations (Difference = A-B-Bin). If you use delays, make sure to simulate for long enough to see the final result.

- b. Write Verilog code for a 4-bit subtractor using the module defined in part (a) as a component. If you use delays, make sure to simulate for long enough to see the final result. Test it for the following input combinations:

- 1. A = 1001, B = 0011, Bin = 1

- 2. A = 0011, B = 0110, Bin = 1

1-bit full subtractor truth table:

| А | В | Bin | Diff | Bout |

|---|---|-----|------|------|

| 0 | 0 | 0   | 0    | 0    |

| 0 | 0 | 1   | 1    | 1    |

| 0 | 1 | 0   | 1    | 1    |

| 0 | 1 | 1   | 0    | 1    |

| 1 | 0 | 0   | 1    | 0    |

| 1 | 0 | 1   | 0    | 0    |

| 1 | 1 | 0   | 0    | 0    |

| 1 | 1 | 1   | 1    | 1    |

Verify that your design works correctly by using the "force" and "run" commands in the transcript window to provide inputs and observe outputs on the waveform window.

## **Problem 2: ALU Design**

Design an Arithmetic and Logic Unit (ALU) that implements 8 functions as described in Table 1. Table 1 also illustrates the encoding of the control input.

The 4-bit ALU has the following inputs:

- A: 4-bit input

- B: 4-bit input

- Cin: 1-bit input

- Output: 4-bit output

- Cout: 1-bit output

- Control: 3-bit control input

| Control | Instruction | Operation                                       |

|---------|-------------|-------------------------------------------------|

| 000     | Add         | Output <= A + B + Cin; Cout contains the carry  |

| 001     | Sub         | Output <= A – B - Cin; Cout contains the borrow |

| 010     | Or          | Output <= A or B                                |

| 011     | And         | Output <= A and B                               |

| 100     | Shl         | Output <= A[2:0] & '0'                          |

| 101     | Shr         | Output <= '0' & A[3:1]                          |

| 110     | Rol         | Output <= A[2:0] & A[3]                         |

| 111     | Ror         | Output <= A[0] & A [3:1]                        |

#### Table 1: ALU Instructions

The following points should be taken care of:

- Use a case statement (or a similar 'combinational' statement) that checks the input combination of "Code" and acts on A, B, and Cin as described in Table 1.

- The above circuit is completely combinational. The output should change as soon as the code combination or any of the input changes.

- You can use arithmetic and logical operators to realize your design.

Simulate this circuit by using the "force" and "run" statements in the transcript window to provide inputs and observe outputs on the waveform window.

# Problem 3: Synthesizing and implementing the subtractor on the FPGA

Create a new project in Xilinx ISE. Use the code for the 4-bit subtractor that you wrote in Problem 1. Synthesize and implement the design on the Spartan3E FPGA on Nexys2 board. Use the following pin assignments for creating the UCF file:

| А    | Switches[7->4] |

|------|----------------|

| В    | Switches[3->0] |

| Bin  | BTN0           |

| Diff | LED[3->0]      |

| Bout | LED4           |

Download the design onto the board and make sure it works as expected. Include the *design\_name.bit* file that you download to the board in your Canvas submission.

# **Useful Information**

1. For problem 2, you can use the subtractor block from problem 1 for doing the subtraction (although just using the arithmetic operators will make your design easier). If you use the subtractor from problem 1, remember that we are designing hardware. So, doing something like the following is incorrect:

```

module xyz(...)

always @(...)

case (control)

0 : four_bit_sub sub_inst(in1,in2,bin,output);

.....

```

First of all, it is important to realize that instantiating a module is not like 'calling' a function in C. Once instantiated, the module is always evaluating its inputs. Therefore, it cannot be conditional. It is always present. So, you should do something like this:

```

module xyz(...)

four_bit_sub sub_inst(in1,in2,bin,sub_out)

always @(...)

case (control)

0 : output <= sub out;</pre>

```

.....

- 2. Make sure that your designs work by testing them sufficiently thoroughly. You should not just use the test inputs in the lab description. Also, it is always better to submit a do-file which has sufficient number of input combinations (not just the ones given in the lab description).

- Do not use # statements in your design for providing delays.

#15 X <= A or B;</li>

In fact, you should never use the delay statement in the lab during the semester.

## **Submission Details**

All parts of this lab will be submitted on Canvas only. You will not need to submit anything as a hard copy. Please zip all relevant files into a single folder with the following naming scheme: *Lastname\_Lab#.zip*

#### Digital Systems Design Using Verilog

| Problem | Submission Requirements |

|---------|-------------------------|

| 1       | • Verilog file(s)       |

|         | • Do-file               |

| 2       | • Verilog file(s)       |

|         | • Do-file               |

| 3       | • Bit-file              |

|         | UCF File                |

# **Checkout Details**

You will be expected to describe briefly the codes for problems 1 and 2, simulate and show waveforms in Modelsim, and answer verbal questions. Also, for the last problem you will have to demonstrate that your circuit works on the board.

# Lab Assignment #2

## Guideline

This lab is to be done individually. Each person does his/her own assignment and turns it in.

## **Objective**

To learn designing basic sequential circuits in Verilog and implementing them on an FPGA.

# Problem 1: Excess-3 code converter design

In this problem, you will be designing an FSM using three different styles of Verilog coding: behavioral, dataflow, and structural. The following is the problem for which you will be designing the FSM:

A sequential circuit has one input (X), a clock input (CLK), and two outputs (S and V). X, S and V are all one-bit signals. X represents a 4-bit binary number N, which is input least significant bit first. S represents a 4-bit binary number equal to N + 3, which is output least significant bit first. At the time the fourth input occurs, V = 1 if N + 3 is too large to be represented by 4 bits; otherwise, V = 0. The value of S should be the proper value, not a don't care, in both cases. The circuit always resets after the fourth bit of X is received. Assume the sequential circuit is implemented with the following state table. The outputs are (S,V). All state changes occur on the falling edge of the clock pulse.

| Present State | Next State |     | Out | tput |

|---------------|------------|-----|-----|------|

|               | X=0        | X=1 | X=0 | X=1  |

| SO            | S1         | S2  | 1,0 | 0,0  |

| S1            | S3         | S4  | 1,0 | 0,0  |

| S2            | S4         | S4  | 0,0 | 1,0  |

| S3            | S5         | S5  | 0,0 | 1,0  |

| S4            | S5         | S6  | 1,0 | 0,0  |

| S5            | S0         | S0  | 0,0 | 1,0  |

| S6            | S0         | S0  | 1,0 | 0,1  |

**a.** Write a *behavioral Verilog description* using the state table shown above. Compile and simulate your code using the following test sequence:

X = 1011 1100 1101 ←

The first input bit is at the far right. This is the LSB of the first 4-bit value. Therefore, you will be adding 3 to 13, then to 12, and then to 11. While simulating, keep the period of the CLK to be 10ns. Change X 1/4 clock period after the rising edge of the clock.

**b.** Write a *data flow Verilog description* using the next state and output equations to describe the state machine. You can use Logic Aid to derive the logic equations. Assume the following state assignment:

S0 = 000, S1 = 010, S2 = 001, S3 = 101, S4 = 011, S5 = 100, S6=111

Compile and simulate your code using the same test sequence and timing as (a).

**c.** Write a *structural model* of the state machine in Verilog that contains the interconnection of gates and D flip-flops. Compile and simulate your code using the same test sequence and timing as (a).

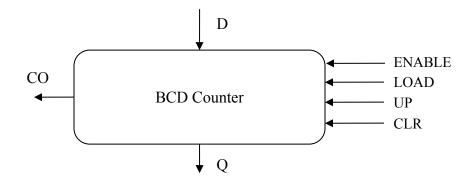

## **Problem 2: BCD Counter Design**

Implement a 1 digit BCD (binary coded decimal) counter. It should be a synchronous (4-bit) up/down decade counter with output Q that works as follows: All state changes occur on the rising edge of the *CLK* input, except the asynchronous clear (*CLR*). When *CLR* = 0, the counter is reset regardless of the values of the other inputs. You can keep the time period of the CLK signal to 10ns for simulating your design.

If the LOAD = ENABLE = 1, the data input *D* is loaded into the counter. If LOAD = 0 and ENABLE = UP = 1, the counter is incremented. If LOAD = 0, ENABLE = 1, and UP = 0, the counter is decremented. If ENABLE = 1 and UP = 1, the carry output (*CO*) = 1 when the counter's value is 9. If ENABLE = 1 and UP = 0, the carry output (*CO*) = 1 when the counter's value is 0.

- a. Write a Verilog description of the counter. You may implement your design in any style you wish. It will be easier to use a behavioral description which can be either written in the algorithmic way (eg. Count <= Count + 1 Figure 2.46 in the text) or a state machine way (eg. State <= Next\_State Figure 2.54/2.56 in the text). You may also use dataflow or structural descriptions, although that will be more work. Use the following simulation for your waveforms:</p>

- 1. Load counter with 6

- 2. Increment counter four times. You should get 9 and then 0.

- 3. Decrement counter once. You should get 9.

- 4. Clear the counter.

- b. Write a Verilog description of a decimal counter that uses two of the above counters to form a two-decade decimal up/down counter that counts up from 00 to 99 or down from 99 to 00. In other words, instantiate two single digit counters in a top module (the two-digit counter). You may need some extra logic in the top module too other than these instantiations. The top module will have these inputs and outputs: CLR, CLK, ENABLE, LOAD, UP, D1, D2, Q1, D2, CO. Use the following simulation for your waveforms:

- 1. Load counter with 97

- 2. Increment counter five times.

- 3. Do nothing for 2 clock periods

- 3. Decrement counter four times.

- 4. Clear the counter.

# Problem 3: Synthesizing and implementing the BCD counter on the FPGA

Use the code for the single digit BCD counter that you wrote in Problem 2a. Before you synthesize it and implement it on the board, you will have to modify your code a little bit. This is because the CLK signal available on the board is a high frequency signal (50 MHz). If you use this high frequency for your circuit, you will not be able to give proper inputs or see proper outputs to your design.

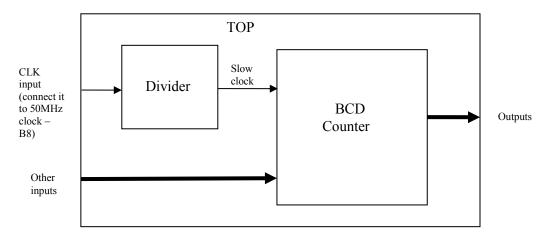

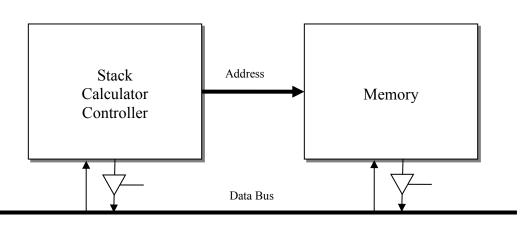

So, you need to add a clock divider to your Verilog description. Create two more entities in your design. Call one as *top* and another as *divider*. Make connections as shown in the following figure. Look at the codes given in the end of this document, understand them and see how they can be used as clock dividers.

To look for latches in your synthesized design, open the synthesis report generated by ISE by clicking "View Synthesis Report" under the "Synthesize-XST" option. In the synthesis report, look for "Macro Statistics" and see if any latches are being shown. Alternatively, you can look for "cell usage" in the report and there should not be any cells under "Flip Flops/Latches" having names starting with "L". Ensure that there are no latches in your design.

Also, after adding the counter/clock divider block to your design, simulate the top module in Modelsim before directly synthesizing using ISE to ensure that the counter/divider works. And while simulating, reduce the large values (like 5000000) in the counter to small values (say 50), so that simulation takes less time and the waveforms are legible. Don't forget to switch to the correct (large) value before synthesizing.

Synthesize the top module (which includes the divider and the 1-digit bcd counter) and use the following pin assignments. Download the design onto the board and make sure it works as expected.

| LOAD   | BTNO     |

|--------|----------|

| D      | SW[3:0]  |

| ENABLE | SW4      |

| UP     | SW5      |

| CLK    | B8       |

| COUNT  | LED[3:0] |

| CO     | LED4     |

| CLR    | SW6      |

# **Useful Information**

- 1. Don't limit your testing to the input sequences mentioned with the problem statement. During the checkouts, the TAs will apply several input combinations to test your design. So, make sure to do a thorough testing of your design using sufficient number of inputs.

- 2. While simulating your design, it is always a good idea to stagger your inputs with respect to the active clock edge. For example, if your active clock edge is occurring at 10ns, apply your inputs sometime before 10ns, say at 8ns. This ensures that when your design was clocked, the input was successfully read. If your active edge occurs at 10ns and your input also changes at 10ns, then it becomes hard to see whether the input was successfully captured by the clock edge or not.

3. A state machine can be designed using either a single always statement (like Figure 2.56 in the text) or using two always statements (like Figure 2.54 in the text). Both ways are correct. However, it is easier to design it using a single always statement. Generally, the single always statement partakes less debugging effort. This is good guideline to observe during the entire semester.

# **Submission Details**

All parts of this lab are to be submitted on Canvas. No hard-copy submission is needed. Please zip all your files into a single folder with the following naming scheme: *Lastname\_Lab#.zip*

| Problem | Submission Requirements             |

|---------|-------------------------------------|

| 1       | <ul> <li>Verilog file(s)</li> </ul> |

|         | • Do-file                           |

| 2       | <ul> <li>Verilog file(s)</li> </ul> |

|         | • Do-file                           |

| 3       | • Verilog file(s)                   |

|         | Bit-file and UCF File               |

# **Checkout Details**

During your checkout you will be expected to demonstrate each of the problems in the assignment and answer verbal questions about the assignment.

#### EE 460M

#### Example 1

```

module simpleDivider(clk50Mhz, slowClk);

input clk50Mhz; //fast clock

output slowClk; //slow clock

reg[26:0] counter;

assign slowClk= counter[26]; //(2^26 / 50E6) = 1.34seconds

initial

begin

counter = 0;

end

always @ (posedge clk50Mhz)

begin

counter <= counter + 1; //increment the counter every 20ns (1/50 Mhz) cycle.

end

```

#### endmodule

#### Example 2

```

module complexDivider(clk50Mhz, slowClk);

input clk50Mhz; //fast clock

//slow clock

output slowClk;

reg[26:0] counter;

initial

begin

counter = 0;

end

always @ (posedge clk50Mhz)

begin

if(counter == 25000000) begin

counter <= 1;</pre>

slowClk <= ~slowClk;</pre>

end

else begin

counter <= counter + 1;</pre>

end

end

```

```

endmodule

```

# Lab Assignment #3

## Guideline

This lab can be done with a partner. In fact, partnership is encouraged.

# **Objective**

- 1. Understanding the ASIC/FPGA design flow

- 2. More digital design sequential and combinational circuits.

- 3. Learn writing and using testbenches in Verilog

- 4. Implementing circuits on FPGA

# **Problem 1: ASIC/FPGA Design Flow**

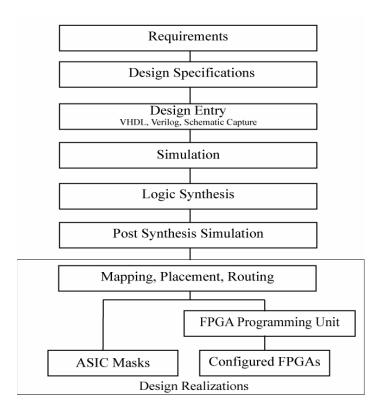

The following figure shows the design flow as described in chapter 2 of the text. Annotate each box in this figure with the answers to the following questions:

- a. What is the function of each box (answer in one line)?

- b. Which tool do you use in the lab to perform this step? If a step is not performed in the lab, mark it.

- c. What inputs are needed at each stage and what outputs are delivered at each stage?

#### Problem 2: Package Sorter (simulation only – using a testbench)

Design a package sorter to classify packages based on their weights and to keep track of packages of different categories. The sorter has an active high asynchronous reset and will keep track of packages since the last reset. Packages should be classified into 6 groups:

#### Spring 2014: Use configuration 2

#### **Configuration #1**

- i) between 1 and 200 grams

- ii) between 201 and 500 grams

- iii) between 501 and 800 grams

- iv) between 801 and 1000 grams

- v) between 1000 and 2000 grams

- vi) greater than 2000

#### **Configuration #2**

- i) between 1 and 250 grams

- ii) between 251 and 500 grams

- iii) between 501 and 750 grams

- iv) between 751 and 1500 grams

- v) between 1501 and 2000 grams

- vi) greater than 2000

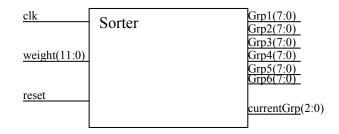

You need to decode weight measurements and classify them into various groups. The input to the circuit will be a 12-bit *unsigned* binary number (indicating the weight of the package), a clock signal, and a reset. One of the outputs will be *currentGrp*, a 3-bit unsigned number representing the current group number. There will also be six 8-bit *unsigned* outputs *Grp1-Grp6* representing the number of items weighed in each category since the last reset. The reset line is provided as input to allow these counts to be cleared.

The output lines have the following functionality:

*currentGrp[2:0]:* Outputs the group number for the weight currently being applied to the sorter. When a weight of zero is applied, it should output a zero. This should update as soon as a package weight changes and may not necessarily reflect the last group that a package was assigned to.

*Grp1-Grp6[7:0]:* Outputs the number of objects that have been weighed in each group since the last reset. These outputs should be zero when reset='1'.

Notice that the functionality of the two outputs is such that the description of *currentGrp* will be purely combinational since it does not depend on any previous inputs. But the description of *Grp1-Grp6* will be sequential since it depends not just on the current input but also on the previous inputs.

Any sequential output should change on the falling edge of the clock. Notice that the *clk* signal will be significantly faster than the duration of the weight signal. As such, you must ensure that the count is only updated once for a given input weight. Secondly, new objects can only be detected and sorted if the weight is allowed to go to zero. This is to ensure that any fluctuations in the weight after it has been sampled are not considered new items. Only the first weight after 0 updates a group count.

Test your design by using **a Verilog testbench** similar to Fig. 2-68 in the text. The testbench should use arrays (to set the inputs, to store the expected group counts and currentGrp values). Do not just use the example input. It is for illustrating the desired functionality. You are responsible for adequately testing your design, so make sure you test everything described for this problem.

#### Example input sequence

#### For Configuration 1

Reset  $\rightarrow$  Put 250grams on  $\rightarrow$  Take off  $\rightarrow$  Put on 300 grams  $\rightarrow$  Take off  $\rightarrow$  Put on 501grams  $\rightarrow$  Put 512 grams more [In your waveforms, this input sequence will look like this: reset -> 250 -> 0 -> 300 -> 0 -> 501 -> 1013]

At the end of this sequence, the outputs should be:

grp1 = grp4 = grp5 = 0x00 grp2 = 0x02 grp3 = 0x01 currentGrp = 0x5

Note that after 501 grams is sampled in grp3, adding 512 grams only updates the current group and not the grp5 count.

#### For Configuration 2

Reset  $\rightarrow$  Put 270grams on  $\rightarrow$  Take off  $\rightarrow$  Put on 300 grams  $\rightarrow$  Take off  $\rightarrow$  Put on 501grams  $\rightarrow$  Put 512 grams more [In your waveforms, this input sequence will look like this: reset -> 270 -> 0 -> 300 -> 0 -> 501 -> 1013]

At the end of this sequence, the outputs should be:

grp1 = grp4 = grp5 = 0x00 grp2 = 0x02 grp3 = 0x01 currentGrp = 0x04

Note that after 501 grams is sampled in grp3, adding 512 grams only updates the current group and not the grp4 count.

# **Problem 3: Traffic Light Controller (implementation – on an FPGA)**

Design a traffic light controller for an intersection with a main street, a side street, and a pedestrian crossing.

Traffic light A consists of three lights: Green (Ga), Yellow (Ya), and Red (Ra). Similarly, traffic light B consists of three lights: Green (Gb), Yellow (Yb), and Red (Rb). Lastly, the walk indicator consists of two lights: Green (Gw) and Red (Rw).

The normal sequence of operation is as follows: Ga Rb Rw, Ya Rb Rw, Ra Gb Rw, Ra Yb Rw, Ra Rb Gw, Ra Rb Rw, Ga Rb Rw... (repeat). The timings are as follows:

#### Spring 2014 : Use configuration 2

#### **Configuration 1**

Main (A) Street:

- Green: lasts 4 seconds.

- Yellow: lasts 2 seconds.

- Red: lasts 10 seconds.

Side (B) Street:

- Green: lasts 3 seconds.

- Yellow: lasts 1 seconds.

- Red: lasts 12 seconds.

#### Pedestrian Crossing:

- Green: lasts 2 second.

- Red: Flashes 4 seconds at 1Hz, then solid for 10 seconds

Maintenance mode:

- RST=1: Ra, Rb, and Rw all flash at 1Hz

- RST=0: Traffic lights should resume operation with Ga,Rb,Rw as initial state

#### **Configuration 2**

Main (A) Street:

- Green: lasts 3 seconds.

- Yellow: lasts 2 seconds.

- Red: lasts 8 seconds.

Side (B) Street:

- Green: lasts 3 seconds.

- Yellow: lasts 1 seconds.

- Red: lasts 9 seconds.

#### Pedestrian Crossing:

- Green: lasts 2 second.

- Red: Flashes 2 seconds at 2Hz, then solid for 9 seconds

Maintenance mode:

- RST=1: Ra, Rb, and Rw all flash at 1Hz

- RST=0: Traffic lights should resume operation with Ga,Rb,Rw as initial state

The above mentioned delays can be obtained through the use of counters, just like you divided 50MHz clock to generate a 1Hz (1 sec period) in Lab#2.

Your design steps are listed below:

- 1. Start by designing a state graph for the controller. You do not need to derive any equations, since you can model the state graph using behavioral Verilog code. Note that on designing your state graph, you will transition from one state to the other when the appropriate time has elapsed.

- 2. Write behavioral Verilog code that represents your state graph. For purposes of checking the functionality of your code, reduce the counter time to a small number during simulation, otherwise you may have to simulate your code through several simulation pages.

- 3. Once your code simulates properly, proceed to synthesizing it and implementing it on the FPGA. Read through the FAQs at the beginning of this manual to understand and clarify doubts about how to use always statement to make combinational logic and sequential logic, and how to avoid latches. The following table gives the IO connections for implementing the traffic light controller:

| Green Light street A:  | LED2 |

|------------------------|------|

| Yellow Light street A: | LED1 |

| Red Light street A:    | LED0 |

| Green Light street B:  | LED7 |

| Yellow Light street B: | LED6 |

| Red Light street B:    | LED5 |

| Green Light Ped Xing:  | LED3 |

| Red Light Ped Xing:    | LED4 |

| Rst (Maintenance mode) | SW0  |

There is something else that you need to do as well for this part of the lab. You need to generate three reports while implementing your design:

- 1. The synthesis report to find out the digital elements used by your design

- 2. The Place and Route report to find out the number of slices of the FPGA used by your design

- 3. The Static Timing report to find out the critical path in your design

To view these reports, go to the "Design Summary" tab in the Xilinx ISE window. The synthesis report can be seen by double-clicking "Synthesis Report" under "Detailed Reports". You can locate the digital elements (like gates, flops and latches) used by your design in this report. Of course, to be able to see this report, you should have synthesized your design. Ensure that there are no latches in your design. In the synthesis report, look for "Macro Statistics" and see if any latches are being shown. Alternatively, you can look for "cell usage" in the report and there should not be any cells under "Flip Flops/Latches" having names starting with "L".

The Place and Route Report will be located in the "Design Summary" tab under Detailed Reports -> Place and Route Report. The Static Timing Report should be in the same tab under "Detailed Reports" -> "Static Timing Report". For you to be able to see these reports, you should have run the "Implement Design" step. If the Post-PAR Static Timing Report is not generated, expand the "Implement Design" entry under the "Processes" window. Then expand the "Place & Route"

entry and run the "Generate Post-Place & Route Static Timing" process. In the place and route report, circle or otherwise note the number of slices used by your design, and in the static timing report, circle or otherwise note the critical delay of your design. Please note that Xilinx Timing Reports are sorted in 3-4 groups.

- i. Path from input port to register, reported in Setup/Hold to clock CLK group.

- ii. Path from register to output port, reported in Clock CLK to Pad group.

- iii. Path from register to register, reported in Clock to setup on destination clock CLK group.

- iv. Path from input port to output port, reported in Pad to Pad group.

For finding the critical delay in your design you need to look for the longest delay within each of these four groups.

# **Useful Information**

- 1. For the reports (STA, PAR and SYNTH), just copy the entire reports into text/doc files and highlight the parts which contain relevant information (like cell count, path delays, etc)

- 2. Sometimes Xilinx ISE does not show all the paths in the timing report. It will show just one or two paths. This is okay. Probably there is a bug in the tool. Just submit whatever you got.

# **Submission Details**

All parts of this lab are to be submitted on Canvas. No hard-copy submission is needed.

- Problem 1

- Text file/Word document containing the answers

- Problem 2

- Typed Verilog Code (.v file)

- Typed Testbench Code (.v file)

- Problem 3

- Typed Verilog Code (.v file)

- Synthesis report (.txt or .doc file)

- Place and Route Report with number of slices noted (.txt or .doc file)

- o Post-Place and Route Static Timing Report with critical delay noted (.txt or .doc file)

- [filename].bit file from compilation

- $\circ \quad \text{UCF file} \\$

# **Checkout Details**

During your checkout you will be expected to demonstrate each of the problems (both simulation and implementation if required for the problem) in the assignment and answer verbal questions about the assignment.

# Lab Assignment #4

#### Guideline

This lab can be done with a partner.

#### **Objective**

Your objective in this lab is to design (code, simulate and implement) a parking meter much like the ones around Austin. It should be able to simulate coins being added and show the appropriate time remaining. Also, it should flash slowly when less than 200 seconds are remaining and flash quickly when time has expired.

#### **Description**

You will design a finite state machine that will simulate the operation of a traffic meter. The buttons on the board will represent different coin denominations and the seven segment LED display will output the total amount of seconds remaining before the meter expires.

#### Spring 2014 : Use configuration 2

#### **Configuration 1**

| Button 0 | Add 30 seconds            |

|----------|---------------------------|

| Button 1 | Add 120 seconds           |

| Button 2 | Add 180 seconds           |

| Button 3 | Add 300 seconds           |

| Switch 0 | Reset time to 15 seconds  |

| Switch 1 | Reset time to 185 seconds |

As soon as a button is pushed, the time should be added immediately. When less than 180 seconds remain, the display should flash with period 2 seconds and duty cycle 50% (on for 1 sec and off for 1 sec; so you will see alternate counts on the display eg- 185, blank, 183, blank, 181...). When time has expired, the display should flash with period 1 sec and duty cycle 50% (on for 0.5 sec and off for 0.5 sec). For example, when the board starts, it should be in the 0 time remaining state and be flashing 0000 at a 0.5 second rate. If button 3 is then pushed, the display should read 300 seconds and begin counting down. When the time counts down to 200 seconds and button 2 is pushed, the display should then read 380 seconds (200 + 180). If switch 0 goes high, then the time should change to 15 seconds and flash accordingly.

#### **Configuration 2**

| Button 0 | Add 50 seconds            |

|----------|---------------------------|

| Button 1 | Add 150 seconds           |

| Button 2 | Add 200 seconds           |

| Button 3 | Add 500 seconds           |

| Switch 0 | Reset time to 10 seconds  |

| Switch 1 | Reset time to 205 seconds |

#### EE 460M

As soon as a button is pushed, the time should be added immediately. When less than 200 seconds remain, the display should flash with period 2 seconds and duty cycle 50% (on for 1 sec and off for 1 sec; so you will see alternate counts on the display like 200, blank, 198, blank, 196,...). Make sure you blink such that even values show up and odd values are blanked out. When time has expired, the display should flash with period 1 sec and duty cycle 50% (on for 0.5 sec and off for 0.5 sec).

For example, when the board starts, it should be in the 0 time remaining state and be flashing 0000 at a 0.5 second rate. If button 3 is then pushed, the display should read 500 seconds and begin counting down. When the time counts down to 180 seconds and button 2 is pushed, the display should then read 380 seconds (200 + 180). If switch 0 goes high, then the time should change to 10 seconds and flash accordingly.

The max value of time will be 9999 and any attempt to increment beyond 9999, should result in the counter defaulting to 9999 and counting down from there.

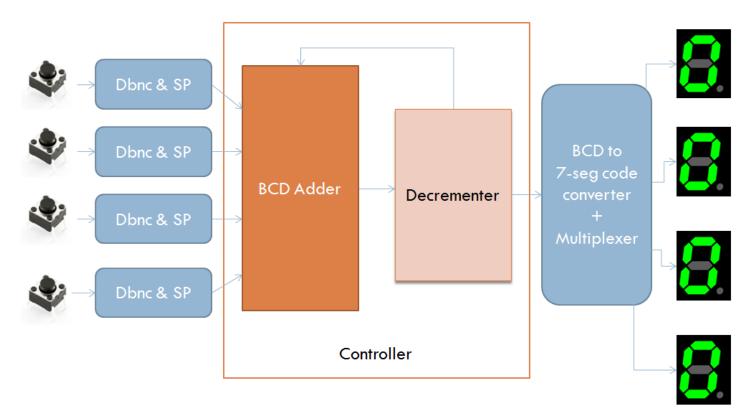

From a structural perspective, your circuit will consist of three parts:

- The input module, which takes the input from the buttons on the board,

- The output module, which displays the output on the 7-segment display, and

- The controller

Although it is not mandatory to follow this structural hierarchy, it is recommended that you implement the input and output parts in separate modules and make sure they are working correctly before putting the whole design together. You need to implement a de-bouncing circuit to make the input module work. The best way to this is to read, understand, and then implement the de-bouncing circuitry described in the textbook. For the output module you need to read the board manual and understand how to correctly drive the multi-digit 7-segment display. In the controller module, you will need to add the time count whenever a button is pushed and subtract the time count every second. You can design in a way such that you use all BCD operations (by having BCD addition and subtraction like the one shown in the following figure). However, you can also keep your counts in binary and then convert binary numbers to multiple digit BCD numbers before you send them to the output module. However, please note that you cannot divide by 10 using the Spartan 3E FPGA hardware. If you use the division operator in your Verilog, it will not synthesize to anything. Therefore, you CANNOT use any binary-to-BCD conversion methods that rely on dividing by 10.

**Digital Systems Design Using Verilog**

# **Useful Information**

- 1. Debouncer and Single Pulser circuitry is explained in section 4.7 of the text.

- 2. BCD Adder is described in section 4.2 of the text. If you don't want to use a BCD adder, you can use an approach similar to problem 4.13 (in the text) for binary to bcd conversion

- 3. BCD to 7-segment decoder is described in section 4.1 of the text. However, note that the polarities of signals (anodes and cathodes) are not the same as the ones in the text. Please refer to the board's manual for proper polarities.

- 4. Make sure you go through the Nexys board manual to understand how to multiplex the 7-segment displays.

- 5. Check for the overflow condition (saturation at 9999) in your code and make sure it works.

- 6. If you make the BCD Adder and Decrementer as a single always blocks running on 50MHz clock, your design might become easy. However, it is up to you to make them as two separate always blocks.

- 7. It is recommended that you simulate the design using either a test bench or by using the force & run commands from the transcript window.

- 8. In case your design does not work on the board, submit the testbench Verilog file and/or the .do file, and show the simulation during checkout for partial credit.

- 9. Ensure that there are no latches in your design when you implement it.

# **Submission Details**

All parts of this lab are to be submitted on Canvas. No hard-copy submission is needed.

- 1. All Verilog code

- 2. Any testbench code or do-files that you use

- 3. Bit file and UCF file

# **Checkout Details**

During checkout you will demonstrate the parking meter working on the board as well as in simulation. Also, you will be judged on how well you understand your code and other concepts like de-bouncing, multiplexing 7-segments and BCD addition.

# Lab Assignment #5

#### Guideline

This lab can be done with a partner.

#### **Objective**

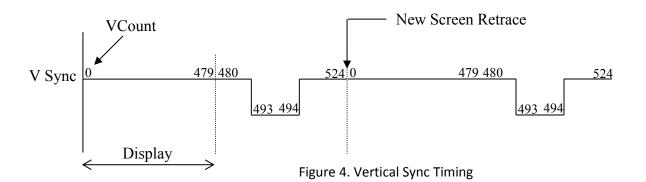

To develop a basic SNAKE game by interfacing a PS/2 Keyboard and VGA display with theboard

#### Reading

Before you start working on this lab, please read pages 7-12 of the Nexys2 Board User Manual. More info on the PS/2 protocol: <u>http://pcbheaven.com/wikipages/The\_PS2\_protocol/</u> More info on the VGA Standard: <u>http://www.ece.msstate.edu/~reese/EE4743/lectures/displays.pdf</u>

#### **Description**

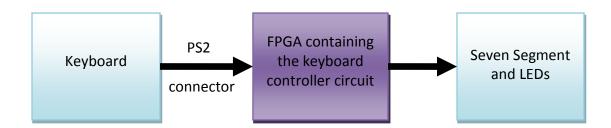

In this lab you will be required to create a simple keyboard controller and a VGA controller. The keyboard controller will enable communication from the keyboard. The VGA controller will be used to display some simple graphic patterns on the computer monitor attached to the board.

For the entire lab, keep in mind "How can I test this during early design and simulation stages?" It is recommended that you simulate the core components of your design to ensure the basic logic works correctly. After this, you can use the hardware to begin testing your design. Debugging through a relatively opaque hardware interface is difficult (e.g., trying to debug a graphics controller if the monitor doesn't display anything). Try to make your design very clear, simple, and modular. This allows you to relatively quickly diagnose problems and create potential solutions.

## **Submission details**

Submit the following things on Canvas:

- Verilog codes (design and testbenches/dofiles) for each part

- Waveforms for part (b)

- Bit files and UCF files for each part

#### **Checkout details**

Demonstrate the each part during the checkout to the TA.

## **Grading:**

Part A = 50pts (28%) Part B = 50pts (28%) Part C = 71pts (39%) + 9pts (5%) = 80pts Total: 180pts

Note: 5% of your grade will be based on creativity/uniqueness you add to your design in part C!

## Part A: Keyboard interface design (50pts)

In this part of the lab, you will be designing an interface for accepting values from the keyboard. In previous labs, we have been limited to accepting inputs from the 8 switches or the 4 buttons. In this lab, we will expand the input functionality by implementing a PS2 keyboard interface. The values sent from the keyboard will be displayed on the seven segment display on the Nexys2 board.

The PS2 protocol is a simple two-wire scheme that uses serial transmission to transmit the data to the board. While the two-wire bus is bi-directional in design, we will only be using it as an input to the FPGA. [Typically writing to the keyboard is used to reset, turn on the various indicator lights, etc.]

When a key is pressed, a sequence of bytes is sent serially over the two-wire bus. Each key on the keyboard is given a unique "scancode" (see Nexys2 board user manual). In order to detect when keys are initially pressed and then released, the keyboard will send a sequence of bytes for each key press. The first byte sent by the keyboard is typically called the "make code" and it represents the key that is pressed. The final byte sent by the keyboard is the "break code" which represents the key that was released.

For example, consider the situation where a user presses the letter 'a':

- 1) User presses the 'a' key

- 2) Keyboard sends "make code" (which is '1C' for the 'a' key) serially. The keyboard keeps sending the "make code" every 100ms until the user releases the key.

- 3) User releases the 'a' key

- 4) Keyboard sends the "key up" code 'F0'serially

- 5) Keyboard sends the "break code" (which is '1C' for the 'a' key) serially

We will only need to look for the "break code" bytes. So we can simply monitor the bits for the "key up" scan code which indicates that the key has been released. When this byte has been sent, the "break code" for the released key will be sent.

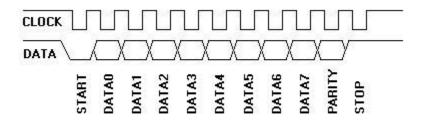

To transmit the sequence of bytes, the keyboard first forces the *DATA* line low to create the start bit. Bits are transmitted using the falling edge of *CLK* for synchronization. This is illustrated in Figure 1. The *DATA* signal changes state when the *CLK* signal is high, and *DATA* is valid for reading on the falling edge of *CLK*.

Figure 1. Device to Host Communication

So the basic operation of your design is as follows:

- On the falling edge of *CLK*, use a shift register to capture each bit of data

- When all 11 bits have been sent (start, scancode, parity, stop), you can look at the scancode and decide what to do

- If the scancode is a "key up" i.e. 'FO', you know that the next data sequence sent by the keyboard is the final scancode that you need.

- Capture the final scancode by following the same steps as above and output this value from your keyboard controller.

Display the lower 2 hex digits of the scancode received by the controller on the lower two seven segment displays (Note that some keys scan codes have 2 digits and some have 4 digits, see Fig. 14 on page 9 of the Board User Manual). You should also have a strobe signal to indicate that the keyboard controller is outputting a new keypress. A strobe signal is a short pulse on one of the board LEDs.

## **Useful Information**

- 1. Some keyboards in the LAB have a problem with the SPACE bar (probably the ones from HP). So, don't panic if your code breaks when you hit the SPACE bar. Just change the keyboard, and everything will be fine.

- 2. The 7-segment display should show the keycode of a key until a new key is pressed, at which time it starts to show the keycode of the new key.

- 3. The strobe signal's duration can be as much as you wish unless it is visible to us with naked eye.

- 4. There is an easy way of implementing the keyboard interface by using a 22-bit shift register in your design. Think about it! Talk to the TAs about it.

- 5. Some keys on the keyboard (like the arrow keys) are special in the sense that they send an additional code "E0" ahead of the scan code. Such keys are called extended keys. When an extended key is released and "E0 F0" code is sent followed by the scan code. So, irrespective of the type of key, the last two chunks of data when a key is released will be "F0" and the scan code.

- 6. The Nexys2 Board Manual shows the keycode for the key "z" as "1Z". This is a typo, the actual code is "1A".

- 7. For this design you should use the keyboard clock as an input to your module. Disregard what the Nexys2 Board Manual says.

- 8. Although the keyboard data signal is birectional, we will only be using it as an input for this lab.

- 9. In case you are getting an error related to the keyboard clock during the Place & Route step in Xilinx ISE (which says something like "Clock IOB/ clock component is not..."), please add the following line to your UCF file and then re-run the Place & Route step again.

#### NET "KCLK" CLOCK\_DEDICATED\_ROUTE = FALSE;

where KCLK is the name of keyboard clock signal in your design. To edit your UCF file, click on the UCF file name in the 'Sources' part of the window in Xilinx ISE. Now expand the "User constraints" in the "Processes" part of the window. Now double-click on "Edit Constraints". Now the UCF file will be loaded in the right side of the window. Edit the file as a normal text file and hit "Save".

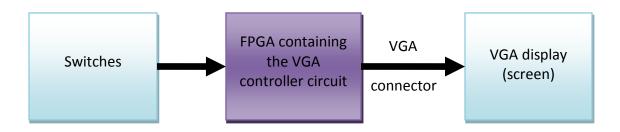

## Part B: VGA Interface Design (50pts)

In this part of the lab you will design a VGA controller to output graphics to the computer monitor connected to the Nexys2 board. In previous labs, we were limited to either the seven-segment display or the LEDs. In this lab, we expand on this functionality to allow graphical images to be displayed from the FPGA board.

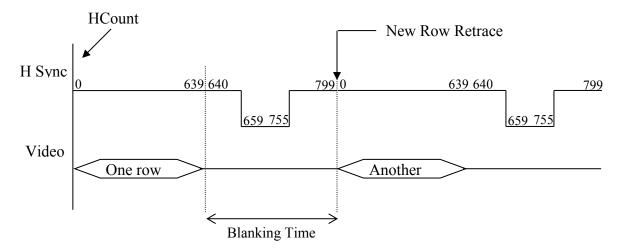

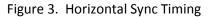

A VGA monitor operates using an electron beam that scans the screen row by row, starting at the upper left corner and ending at the lower-right corner. This beam moves using two synchronization signals, called *hsync* (horizontal synchronization), and *vsync* (vertical synchronization). The *hsync* signal tells the beam when to move to the next row. The *vsync* signal tells the beam when to move to back to the top of the screen. To display a picture on the screen, we simply generate these synchronization signals and provide the pixel color to display on the screen.