# OpenSPARC<sup>™</sup>T1 Processor Datasheet

8 Cores, 1.2 GHz, 3 Mbyte L2-cache, DDR2 SDRAM and J-Bus Interface

Sun Microsystems, Inc. www.sun.com

Part No. 819-5015-10 March 2006, Revision A

Submit comments about this document at: <a href="http://www.sun.com/hwdocs/feedback">http://www.sun.com/hwdocs/feedback</a>

Copyright 2006 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

This document and the product to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of the product or of this document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, Java, AnswerBook2, docs.sun.com, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and in other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and in other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun™ Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

U.S. Government Rights—Commercial use. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2006 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, Californie 95054, États-Unis. Tous droits réservés.

Sun Microsystems, Inc. possède les droits de propriété intellectuels relatifs à la technologie décrite dans ce document. En particulier, et sans limitation, ces droits de propriété intellectuels peuvent inclure un ou plusieurs des brevets américains listés sur le site http://www.sun.com/patents, un ou les plusieurs brevets supplémentaires ainsi que les demandes de brevet en attente aux les États-Unis et dans d'autres pays.

Ce document et le produit auquel il se rapporte sont protégés par un copyright et distribués sous licences, celles-ci en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a.

Tout logiciel tiers, sa technologie relative aux polices de caractères, comprise, est protégé par un copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit peuvent dériver des systèmes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque déposée aux États-Unis et dans d'autres pays, licenciée exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, Java, AnswerBook2, docs.sun.com, et Solaris sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc. aux États-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux États-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface utilisateur graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox dans la recherche et le développement du concept des interfaces utilisateur visuelles ou graphiques pour l'industrie informatique. Sun détient une license non exclusive de Xerox sur l'interface utilisateur graphique Xerox, cette licence couvrant également les licenciés de Sun implémentant les interfaces utilisateur graphiques OPEN LOOK et se conforment en outre aux licences écrites de Sun.

LA DOCUMENTATION EST FOURNIE "EN L'ÉTAT" ET TOUTES AUTRES CONDITIONS, DÉCLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES DANS LA LIMITE DE LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE À LA QUALITÉ MARCHANDE, À L'APTITUDE À UNE UTILISATION PARTICULIÈRE OU À L'ABSENCE DE CONTREFAÇON.

## Contents

- 1.1 Description 1–1

- 1.2 Features 1–1

- 1.3 Functional Overview 1–2

- 1.3.1 OpenSPARC T1 Description 1–2

- 1.3.2 OpenSPARC T1 Components 1–3

- 1.3.2.1 SPARC Core 1–4

- 1.3.2.2 Floating-Point Unit 1–4

- 1.3.2.3 L2-cache 1–4

- 1.3.2.4 DRAM Controller 1–4

- 1.3.2.5 I/O Bridge 1–5

- 1.3.2.6 J-Bus Interface 1–5

- 1.3.2.7 Serial System Interface 1–5

- 1.3.2.8 Electronic Fuse 1–5

- 1.3.3 OpenSPARC T1 Memory System 1–5

- 1.3.4 OpenSPARC T1 Clock Architecture 1–6

- 1.3.5 OpenSPARC T1 Reset Architecture 1–6

- 1.3.6 JTAG and Boundary Scan 1–7

- 1.3.7 OpenSPARC T1 Special RAS Features 1–7

- 1.3.7.1 Memory Chipkill Error Correction 1–7

- 1.3.7.2 Memory Hardware Scrubber 1–7

- 1.3.7.3 Thermal Diode and Throttle Control 1–7

- 1.3.7.4 Performance Counters 1–8

- 1.3.7.5 Shadow Scan 1–8

- 1.3.7.6 Debug Ports 1–8

- 1.4 Signal Description 1–8

- 1.4.1 Signal Overview 1–9

- 1.4.2 DDR2 400 SDRAM Interface Signals 1–10

- 1.4.3 J-Bus Signals 1–11

- 1.4.4 SSI Interface Signals 1–12

- 1.4.5 Debug Port Signals 1–12

- 1.4.6 System Control Signals 1–12

- 1.4.7 Test and Debug Signals 1–14

- 1.4.8 JTAG IEEE 1149.1 Test Access Port Controller Interface 1–15

- 1.4.9 Power, Ground, Spares, and Unconnected Pins 1–15

# Figures

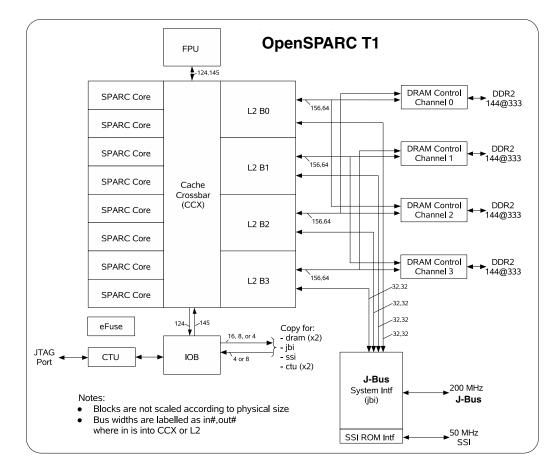

FIGURE 1-1 OpenSPARC T1 Block Diagram 1–3

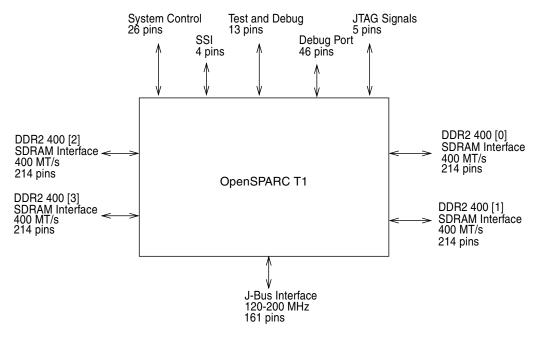

FIGURE 1-2 OpenSPARC T1 Signals 1–9

# Tables

| TABLE 1-1 | OpenSPARC T1 Signal Description 1–9                              |      |

|-----------|------------------------------------------------------------------|------|

| TABLE 1-2 | DDR2 400 SDRAM Memory Interface Signal Description 1-10          |      |

| TABLE 1-3 | J-Bus Signal Description 1–11                                    |      |

| TABLE 1-4 | SSI Signal Description 1–12                                      |      |

| TABLE 1-5 | Debug Port Signal Description 1–12                               |      |

| TABLE 1-6 | System Control Signal Description 1-12                           |      |

| TABLE 1-7 | Test and Debug Signal Description 1-14                           |      |

| TABLE 1-8 | JTAG- IEEE 1149.1 Test Access Port Interface Signal Descriptions | 1–15 |

## Preface

This document describes the OpenSPARC<sup>TM</sup> T1 processor, which is the first chip multiprocessor that fully implements the Sun<sup>TM</sup> Throughput Computing Initiative.

## How This Document Is Organized

This document is organized as described in the following paragraph.

Chapter 1 is a datasheet that describes the OpenSPARC T1 processor from Sun Microsystems, Inc.<sup>TM</sup>

# Using UNIX Commands

This document might not contain information about basic UNIX<sup>®</sup> commands and procedures such as shutting down the system, booting the system, and configuring devices. Refer to the following for this information:

- Software documentation that you received with your system

- Solaris<sup>TM</sup> Operating System documentation, which is at:

http://docs.sun.com

# Shell Prompts

| Shell                                 | Prompt        |  |

|---------------------------------------|---------------|--|

| C shell                               | machine-name% |  |

| C shell superuser                     | machine-name# |  |

| Bourne shell and Korn shell           | \$            |  |

| Bourne shell and Korn shell superuser | #             |  |

# **Typographic Conventions**

| Typeface* | Meaning                                                                                                                     | Examples                                                                                                                                                                         |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AaBbCc123 | The names of commands, files,<br>and directories; on-screen<br>computer output                                              | Edit your.login file.<br>Use ls -a to list all files.<br>% You have mail.                                                                                                        |  |  |

| AaBbCc123 | What you type, when contrasted with on-screen computer output                                                               | % <b>su</b><br>Password:                                                                                                                                                         |  |  |

| AaBbCc123 | Book titles, new words or terms,<br>words to be emphasized.<br>Replace command-line variables<br>with real names or values. | Read Chapter 6 in the <i>User's Guide</i> .<br>These are called <i>class</i> options.<br>You <i>must</i> be superuser to do this.<br>To delete a file, type rm <i>filename</i> . |  |  |

\* The settings on your browser might differ from these settings.

# **Related Documentation**

The documents listed as online are available at:

http://www.opensparc.net

| Application                                                        | Title                                                                                  | Part Number | Format | Location |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------|--------|----------|

| OpenSPARC T1 instruction set                                       | UltraSPARC Architecture 2005<br>Specification                                          | 950-4895-03 | PDF    | Online   |

| OpenSPARC T1 processor internal registers                          | <i>UltraSPARC T1 Supplement to the UltraSPARC Architecture 2005</i>                    | 819-3404-02 | PDF    | Online   |

| OpenSPARC T1 processor J-Bus and SSI interfaces                    | OpenSPARC T1 Processor<br>External Interface Specification                             | 818-5014-10 | PDF    | Download |

| OpenSPARC T1 megacells                                             | OpenSPARC T1 Processor<br>Megacell Specification                                       | 819-5016-10 | PDF    | Download |

| Running simulations and synthesis<br>on the OpenSPARC T1 processor | <i>OpenSPARC T1 Processor</i><br><i>Design and Verification</i><br><i>User's Guide</i> | 819-5019-10 | PDF    | Download |

# Documentation, Support, and Training

| Sun Function  | URL                               |

|---------------|-----------------------------------|

| Documentation | http://www.sun.com/documentation/ |

| Support       | http://www.sun.com/support/       |

| Training      | http://www.sun.com/training/      |

# Third-Party Web Sites

Sun is not responsible for the availability of third-party web sites mentioned in this document. Sun does not endorse and is not responsible or liable for any content, advertising, products, or other materials that are available on or through such sites or resources. Sun will not be responsible or liable for any actual or alleged damage or loss caused by or in connection with the use of or reliance on any such content, goods, or services that are available on or through such sites or resources.

## Sun Welcomes Your Comments

Sun is interested in improving its documentation and welcomes your comments and suggestions. You can submit your comments by going to:

http://www.sun.com/hwdocs/feedback

Please include the title and part number of your document with your feedback:

OpenSPARC T1 Processor Datasheet, part number 819-5015-10

CHAPTER

# **OpenSPARC** T1 Processor

This chapter gives details on the following topics:

- Description

- Features

- Functional Overview

- Signal Description

# 1.1 Description

The OpenSPARC T1 processor is the first chip multiprocessor that fully implements the Sun Throughput Computing Initiative. Each of the eight SPARC<sup>®</sup> processor cores has full hardware support for four threads. Each SPARC core has an instruction cache and data cache and fully associative instruction and data translation lookaside buffers (TLB). The eight SPARC cores are connected through a crossbar to an on-chip unified Level 2 cache (L2-cache). The four on-chip dynamic random access memory (DRAM) controllers directly interface to double data rate-synchronous DRAM (DDR2 SDRAM). In addition, there is an on-chip J-Bus controller. The OpenSPARC T1 processor is a highly integrated processor that implements the 64-bit SPARC V9 architecture. This processor targets commercial applications such as application servers and database servers.

## 1.2 Features

The OpenSPARC T1 processor features include the following:

CPU

SPARC V9 Architecture

- On-chip L2-cache

- 48-bit virtual, 40-bit physical address space

#### Caches

- 16 Kbyte primary instruction cache per core

- Parity

- 8 Kbyte primary data cache per core

- Parity

- 3 Mbyte unified L2-cache

- Error correction code (ECC)

- 12-way set-associative, 4 banks

#### Integration

- 8 cores, 4 threads per core

- Four 144-bit DDR2-533 SDRAM interfaces

- Quad error correction, octal error detection, chipkill ECC

- Optional 2-channel operation mode

- J-Bus Interface

- 2.56 Gbyte/sec peak effective bandwidth

- 128-bit address or data bus

- 150–200 MHz operation

# 1.3 Functional Overview

The section provides more detailed functional information.

## 1.3.1 OpenSPARC T1 Description

FIGURE 1-1 shows a block diagram of the OpenSPARC T1 processor illustrating the various interfaces and integrated components of the chip. The OpenSPARC T1 processor functions and capabilities include the following:

- Eight SPARC single-issue processor cores

- Support for four threads on each core

- 64-bit data paths

- 48-bit virtual address and 40-bit physical address space

- J-Bus controller

- 16 Kbyte primary instruction cache memory per core

- 8 Kbyte primary data cache memory per core

- 64-entry fully associative instruction TLB per core

- 64-entry fully associative data TLB per core

- 3 Mbyte unified L2-cache

- Four DRAM controllers interfacing to DDR2 SDRAM

FIGURE 1-1 OpenSPARC T1 Processor Block Diagram

## 1.3.2 OpenSPARC T1 Processor Components

This section provides further detail regarding the OpenSPARC T1 components.

#### 1.3.2.1 SPARC Core

Each SPARC core has hardware support for four threads. This support consists of a full register file (with eight register windows) per thread, with most of the address space identifiers (ASI), ancillary state registers (ASR), and privileged registers replicated per thread. The four threads share the instruction and data caches and TLBs. Each instruction cache is 16 Kbytes with a 32-byte line size. The data caches are write through, 8 Kbytes, and have a 16-byte line size. An autodemap feature is included with the TLBs to enable the multiple threads to update the TLB without locking.

#### 1.3.2.2 Floating-Point Unit

A single floating-point unit (FPU) is shared by all eight SPARC cores. The shared floating-point unit is sufficient for most commercial applications in which typically less than 1% of the instructions are floating-point operations.

#### 1.3.2.3 L2-cache

The L2-cache is banked four ways, with the bank selection based on physical address bits 7:6. The cache is 3 Mbyte, 12-way set-associative with pseudo-least recently used (LRU) replacement (replacement is based on a used bit scheme). The line size is 64 bytes. Unloaded access time is 23 cycles for an L1 data cache miss and 22 cycles for an L1 instruction cache miss.

#### 1.3.2.4 DRAM Controller

The OpenSPARC T1 processor's DRAM controller is banked four ways (a two-bank option is available for cost-constrained minimal memory configurations), with each L2 bank interacting with exactly one DRAM controller bank. The DRAM controller is interleaved based on physical address bits 7:6, so each DRAM controller bank must have identical dual in-line memory modules (DIMM) installed and enabled.

The OpenSPARC T1 processor uses DDR2 DIMMs and can support one or two ranks of stacked or unstacked DIMMs. Each DRAM bank/port is two-DIMMs wide (128 bit + 16 bit ECC). All installed DIMMs must be identical, and the same number of DIMMs (that is, ranks) must be installed on each DRAM controller port. The DRAM controller frequency is an exact ratio of the core frequency, where the core frequency must be at least three times the DRAM controller frequency. The double data rate (DDR) data buses transfer data at twice the frequency of the DRAM controller frequency.

#### 1.3.2.5 I/O Bridge

The I/O bridge (IOB) performs an address decode on I/O-addressable transactions and directs them to the appropriate internal block or to the appropriate external interface (J-Bus or serial system interface). In addition, the IOB maintains the register status for external interrupts.

#### 1.3.2.6 J-Bus Interface

The J-Bus interface (JBI) is the interconnect between the OpenSPARC T1 processor and the I/O subsystem. J-Bus is a 200 MHz, 128-bit wide, multiplexed address or data bus, used predominantly for direct memory access (DMA) traffic, plus the programmable input/output (PIO) traffic to control it.

The J-Bus interface is the block that interfaces to J-Bus, receiving and responding to DMA requests, routing them to the appropriate L2 banks, and also issuing PIO transactions on behalf of the processor threads and forwarding responses back.

#### 1.3.2.7 Serial System Interface

The OpenSPARC T1 processor has a 50 Mbyte/sec serial system interface (SSI) that connects to an external application specific integrated circuit (ASIC), which in turn interfaces to the boot read-only memory (ROM). In addition, the SSI supports PIO accesses across the SSI, thus supporting optional control status registers (CSR) or other interfaces within the ASIC.

#### 1.3.2.8 Electronic Fuse

The electronic fuse (e-Fuse) block contains configuration information that is electronically burned in as part of manufacturing, including part serial number and core available information.

### 1.3.3 OpenSPARC T1 Memory System

The OpenSPARC T1 chip supports four memory channels. For low-cost system configurations, a two-channel mode can be selected by means of software-programmable control registers. Each channel supports DDR2 JEDEC standard DIMMs. The type of DRAM components supported are 256 Mbit, 512 Mbit, 1 Gbit and 2 Gbit. The maximum speed of the DIMMs supported is 200 MHz clock (400 MHz data rate). The controller works on single-ended DQS only and has the capability to detect any double-nibble error or correct any single-nibble error

contained in one 144-bit chunk. The controller always assumes that additive latency (AL) is zero. The maximum physical address space supported by the controller is 128 Gbytes (37 bits of physical address).

The OpenSPARC T1 chip contains an on-die termination (ODT) feature that is selectable in the DRAM Read Enable Clock Invert, ODT enable mask, and VREF control register. The purpose of this feature is to improve read timing by reducing the intersymbol interference (ISI) effects on the network. This feature terminates the DQ and DQS pins with the equivalent of 150 ohms ( $\Omega$ ) to VDD18/2 under all conditions except when the DQ and DQS pins are enabled during write transactions.

Further information on memory initialization and DRAM control and status registers can be found in the memory controller section of the *UltraSPARC T1 Processor Supplement*.

### 1.3.4 OpenSPARC T1 Clock Architecture

Three synchronous clock domains are on the OpenSPARC T1 processor – CMP (for SPARC and caches), J-Bus (for IOB and JBI), and DRAM (for the DRAM controller and external DIMMs). All of these are sourced from the same phase-locked loop (PLL). Synchronization pulses are generated to control transmission of signals and data across clock domain boundaries.

The clock and test unit (CTU) is responsible for resetting the PLL and counting the lock period. Once sufficient time has passed to enable the PLL to have locked, the clock control logic is responsible for enabling distribution below the cluster levels by turning on cluster enables.

Further information on the OpenSPARC T1 clock architecture, including sequences for changing input clock frequency or clock ratios, clock control registers, PLL bypass, stop and scan support, and clock stretch, can be found in the *UltraSPARC T1 Processor Supplement*.

### 1.3.5 OpenSPARC T1 Reset Architecture

The processor has two flavors of reset – power-on reset (POR) and warm reset. POR is defined as the reset event arising from turning power on to the chip and is triggered by assertion of power-on reset. Warm reset encompasses all resets when the chip has been in operation prior to the event triggering the reset.

The reset state of software-visible registers is specified in the *UltraSPARC T1 Processor Supplement*.

### 1.3.6 JTAG and Boundary Scan

The CTU contains the JTAG block, which enables access to the shadow scan chains. The unit also has a control register (CREG) interface that enables the JTAG to issue reads of any I/O-addressable register, some ASI locations, and any memory location while the processor is in operation.

The OpenSPARC T1 processor contains an IEEE 1149.1-compliant test access port (TAP) controller with the standard five-pin JTAG interface. In addition to the standard IEEE 1149.1 instructions, roughly 20 private instructions provide access to the processor's design for testability (DFT) features.

### 1.3.7 OpenSPARC T1 Special RAS Features

The OpenSPARC T1 processor includes many special features for reliability, availability, serviceability (RAS), and related areas. Several of these are described in the following sections.

#### 1.3.7.1 Memory Chipkill Error Correction

The processor supports chipkill error correction for main memory. Any error contained within a single-aligned memory nibble (4b) can be corrected, and any error that is contained within any two nibbles can be detected as uncorrectable.

#### 1.3.7.2 Memory Hardware Scrubber

Each OpenSPARC T1 DRAM controller has a background hardware error scanner and scrubber to reduce the incidence of multinibble errors. If a correctable error is found, the error is logged, corrected, and written back (scrubbed in hardware) to memory. The L2-cache also has a background scanner and scrubber.

#### 1.3.7.3 Thermal Diode and Throttle Control

The processor has an on-chip thermal diode connected to I/O pins, enabling system hardware to obtain a rough measure of the chip temperature. If an overtemperature condition is detected, the CPU can be shut down, or CPU utilization can be throttled to reduce power consumption.

#### 1.3.7.4 Performance Counters

Each OpenSPARC T1 SPARC thread has two performance counters that count instructions plus occurrences of one other event. The possible other events include cache misses of various types, TLB traps, and store buffer full occurrences. Counts can be qualified to count events in User mode, Supervisor mode, or both.

Two counters in each DRAM controller can be used to count transactions and latency for different operations, which can be used to compute average latency.

The J-Bus unit also has two performance counters. Like the DRAM counters, these counters can be used to count events and latencies and to compute average latency.

#### 1.3.7.5 Shadow Scan

In addition to the usual scan chains, the processor has shadow scan capability. This enables scan extraction of some of the processor state while execution continues. Shadow scan is provided on a per-thread basis for the SPARC cores. The rest of the chip has a separate shadow scan chain.

#### 1.3.7.6 Debug Ports

The OpenSPARC T1 processor contains both a dedicated debug port (Debug Port A) and a J-Bus debug port (Debug Port B). The debug port target bandwidth for logic analysis is 40 bits at J-Bus frequency, which is matched to the width of a single internal debug port selection. This bandwidth is sufficient for an address header every J-Bus cycle.

# 1.4 Signal Description

This section provides a detailed description of OpenSPARC T1 signals. The signals are arranged in functional groups according to their associated interface.

### 1.4.1 Signal Overview

The processor primarily consists of DDR2 400 SDRAM signals and J-Bus signals. FIGURE 1-2 shows the main interfaces and the number of signals.

Total: 1111 Signal Pins

FIGURE 1-2 OpenSPARC T1 Signals

The following table lists the OpenSPARC T1 Processor signal pins including the I/O pins on each group. Spare pins are excluded from this description.

TABLE 1-1

OpenSPARC T1 Processor Signal Description

| Group                                         | Pins |

|-----------------------------------------------|------|

| DDR2 400 SDRAM interface signals (4 channels) | 856  |

| J-Bus interface signals                       | 161  |

| Serial system interface                       | 4    |

| Debug port signals                            | 46   |

| System control signals                        | 26   |

| Group                                       | Pins |

|---------------------------------------------|------|

| Test and debug signals                      | 13   |

| JTAG – IEEE 1149.1 test access port signals | 5    |

| Total number of OpenSPARC T1 signal pins    | 1111 |

TABLE 1-1

OpenSPARC T1 Processor Signal Description (Continued)

### 1.4.2 DDR2 400 SDRAM Interface Signals

The OpenSPARC T1 processor has four DDR2 SDRAM interface channels with 214 signals per channel for a total of 856 signals.

| SIGNAL NAME | I/O | ТҮРЕ                 | Vref | FUNCTION                                                                |

|-------------|-----|----------------------|------|-------------------------------------------------------------------------|

| DQ[127:0]*  | I/O | SSTL-18 <sup>+</sup> | 0.9‡ | DIMM memory bus (128 bits).                                             |

| DQS[35:0]   | I/O |                      |      | SDRAM data strobes (one strobe every four data bits).                   |

| св[15:0]    | I/O |                      |      | DIMM ECC check bits.                                                    |

| ADDR[14:0]  | 0   |                      |      | SDRAM address bus.                                                      |

| CK_P[3:0]   | 0   |                      |      | SDRAM clock outputs (positive lines of four differential signal pairs). |

| CK_N[3:0]   | 0   |                      |      | SDRAM clock outputs (negative lines of four differential signal pairs). |

| CKE         | 0   |                      |      | SDRAM clock enable.                                                     |

| CS_L[3:0]   | 0   |                      |      | SDRAM chip select lines (active low).                                   |

| RAS_L       | 0   |                      |      | SDRAM row address command (active low).                                 |

| CAS_L       | 0   |                      |      | SDRAM column address command (active low).                              |

| WE_L        | 0   |                      |      | SDRAM write enable command (active low).                                |

| BA[2:0]     | 0   |                      |      | SDRAM bank address.                                                     |

TABLE 1-2

DDR2 400 SDRAM Memory Interface Signal Description

\* The signal names shown are repeated for each of the four DDR2 channels. The actual pin names are the signal names as shown in the table preceded by the channel to which they belong. For example, the DQ pins on DDR2 channel 3 are named DRAM3\_DQ[127:0].

† SSTL-18 is 1.8 V I/O power, with 0.9 V pull-up reference

‡ Vref is generated internally to the OpenSPARC T1 Processor processor. No external Vref pin is provided.

## 1.4.3 J-Bus Signals

The OpenSPARC T1 processor has 161 J-Bus interface signals.

| TABLE 1-3 | J-Bus Signal Description |

|-----------|--------------------------|

|           |                          |

| SIGNAL NAME   | I/O | TYPE    | Vref    | FUNCTION                                                                                                                                       |

|---------------|-----|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| j_req4_in_l   | Ι   | DTL *   | 1.125 V | Incoming arbitration requests from other masters on J-Bus. Point-to-point topology.                                                            |

| j_req5_in_l   | Ι   |         |         | Incoming arbitration requests from other masters on J-Bus. Point-to-point topology.                                                            |

| j_req0_out_l  | 0   |         |         | Outgoing arbitration requests for J_AD. Point-to-<br>point topology.                                                                           |

| j_req1_out_l  | 0   |         |         | Outgoing arbitration requests for J_AD. Point-to-<br>point topology. (Functionally equivalent to<br>J_REQ0_OUT_L).                             |

| J_AD[127:0]   | I/O |         |         | J-Bus Address and Data multiplexed bus.                                                                                                        |

| J_ADP[3:0]    | I/O |         |         | Word parity for all J_AD transfer, and J_ADTYPE.                                                                                               |

| J_ADTYPE[7:0] | I/O |         |         | Identifies packet type on J_AD/J_ADP, and signal destination for returning read data. Read transaction ID for out of order data return.        |

| J_PACK0[2:0]  | I/O |         |         | Encoded snoop info and flow control, plus read data flow control, enabled by J_ID for port 0.                                                  |

| J_PACK1[2:0]  | I/O |         |         | Encoded snoop info and flow control, plus read data flow control, enabled by J_ID for port 1.                                                  |

| J_PACK4[2:0]  | I/O |         |         | Encoded snoop info and flow control, plus read data flow control, enabled by J_ID for port 4.                                                  |

| J_PACK5[2:0]  | I/O |         |         | Encoded snoop info and flow control, plus read data flow control, enabled by J_ID for port 5.                                                  |

| J_PAR         | Ι   |         |         | Control parity check for J_REQ and J_PACK, driven by JIO every cycle.                                                                          |

| J_ERR         | 0   |         |         | Not used functionally but driven by any agent that detects an error condition in the J-Bus logic.                                              |

| J_RST_L       | Ι   |         |         | System reset.                                                                                                                                  |

| J_CLK[1:0]    | Ι   | Reduced | PECL †  | Differential PECL clock reference for PLL (120–<br>200 MHz). J_CLK[0] is the positive sense clock<br>and J_CLK[1] is the negative sense clock. |

\* DTL is 1.5 V I/O power, with 1.125 V pull-up reference.

† 1.1 V supply rail.

### 1.4.4 SSI Interface Signals

The OpenSPARC T1 processor has a four-signal serial system interface.

TABLE 1-4

SSI Signal Description

| SIGNAL NAME | I/O | TYPE  | Vref   | FUNCTION                 |

|-------------|-----|-------|--------|--------------------------|

| SSI_MOSI    | 0   | HSTL* | 0.75 V | SSI master out, slave in |

| SSI_MISO    | Ι   |       |        | SSI master in, slave out |

| SSI_SCK     | 0   |       |        | SSI clock                |

| EXT_INT_L   | Ι   |       |        | External interrupt       |

\* HSTL is 1.5 V I/O power, with 0.75 V reference.

### 1.4.5 Debug Port Signals

The OpenSPARC T1 processor has 46 signals for a dedicated debug port.

TABLE 1-5

Debug Port Signal Description

| SIGNAL NAME   | I/O | TYPE  | Vref    | FUNCTION                          |

|---------------|-----|-------|---------|-----------------------------------|

| DBG_DQ[39:0]  |     | DTL * | 1.125 V | Debug output                      |

| DBG_CK_P[2:0] |     |       |         | Debug output clock, positive true |

| DBG_CK_N[2:0] |     |       |         | Debug output clock, negative true |

\* DTL is 1.5 V I/O power, with 1.125 V pull-up reference.

## 1.4.6 System Control Signals

The OpenSPARC T1 processor has 26 system control signals.

TABLE 1-6

System Control Signal Description

| SIGNAL NAME      | I/O | TYPE   | Vref | FUNCTION                               |

|------------------|-----|--------|------|----------------------------------------|

| DRAM01_P_REF_RES | Ι   | Analog |      | PFET PVT impedance reference resistor. |

| DRAM01_N_REF_RES | Ι   | Analog |      | NFET PVT impedance reference resistor. |

| DRAM23_P_REF_RES | Ι   | Analog |      | PFET PVT impedance reference resistor. |

| DRAM23_N_REF_RES | Ι   | Analog |      | NFET PVT impedance reference resistor. |

|                  |     |        |      |                                        |

| SIGNAL NAME    | I/O | TYPE   | Vref   | FUNCTION                                                                                                                                                                  |

|----------------|-----|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTL_R_VREF     | Ι   | Analog |        | DTL voltage reference (1.125 V).                                                                                                                                          |

| DTL_L_VREF     | Ι   | Analog |        | DTL voltage reference (1.125 V).                                                                                                                                          |

| JBUS_P_REF_RES | Ι   | Analog |        | PFET PVT impedance reference reference.                                                                                                                                   |

| JBUS_N_REF_RES | Ι   | Analog |        | NFET PVT impedance reference resistor.                                                                                                                                    |

| DBG_VREF       | Ι   | Analog |        | Debug port voltage reference (DTL signaling type, 1.125 V).                                                                                                               |

| DIODE_TOP[2:0] | 0   | Analog |        | Thermal diode – DIODE_TOP[2] is the<br>emitter; DIODE_TOP[1] is the collector<br>(P-substrate); DIODE_TOP[0] is the base.                                                 |

| diode_bot[2:0] | 0   | Analog |        | Thermal diode – DIODE_BOT[2] is the<br>emitter; DIODE_BOT[1] is the collector<br>(P-substrate); DIODE_BOT[0] is the base.                                                 |

| TEMP_TRIG      | Ι   | HSTL   | 0.75 V | Interrupt input from temperature sensor.                                                                                                                                  |

| PWRON_RST_L    | Ι   | CMOS   |        | Power-on reset.                                                                                                                                                           |

| PLL_CHAR_IN    | Ι   | CMOS   |        | Enables core clocks to be viewed through<br>external differential pins. Also used to<br>put PCM into "2-pin" mode. If high at<br>reset, "Tester Warm Reset" is performed. |

| HSTL_VREF      | Ι   | Analog |        | HSTL Voltage reference (0.75 V).                                                                                                                                          |

| VDD_SENSE      | 0   | Analog |        | Core vdd sense pins (+). Three pins total.                                                                                                                                |

| VSS_SENSE      | 0   | Analog |        | Core vss sense pins (-). Three pins total.                                                                                                                                |

| VREG_SELBG_L   | Ι   | CMOS   |        | PLL voltage regulator bandgap select –<br>selects which voltage reference to use for<br>the on-chip analog voltage regulator.<br>0 = select bandgap, $1 = 0.611*Vdda$ .   |

TABLE 1-6

System Control Signal Description (Continued)

## 1.4.7 Test and Debug Signals

The OpenSPARC T1 processor has 13 test and debug signals.

| SIGNAL NAME     | I/O | TYPE   | Vref    | FUNCTION                                                                                                        |

|-----------------|-----|--------|---------|-----------------------------------------------------------------------------------------------------------------|

| CLKOBS[1:0]     | 0   | SSTL   |         | Enables core clock parameters to be observed.<br>Controlled through PLL_CHAR_IN pin.                            |

| TSR_TESTIO[1:0] | 0   | Analog |         | Temperature sensor analog out. Experimental<br>temperature sensor. Not for use in system<br>designs.            |

| DO_BIST         | Ι   | DTL    | 1.125 V | Activate built-in self test.                                                                                    |

| TRIGIN          | Ι   | HSTL   | 0.75 V  | Stop clock based on external event. When DO_BIST is asserted during reset, TRIGIN controls BISI/BIST selection. |

| TEST_MODE       | Ι   | CMOS   |         | Mux pins into tester mode.                                                                                      |

| PGRM_EN         | Ι   | CMOS   |         | e-Fuse program enable.                                                                                          |

| PMI             | Ι   | CMOS   |         | Process control module input pin.                                                                               |

| РМО             | 0   | CMOS   |         | Process control module output pin.                                                                              |

| BURNIN          | Ι   | CMOS   |         | Sets burnin mode for PCM modules.                                                                               |

| CLK_STRETCH     | Ι   | HSTL   | 0.75 V  | Clock stretch pin for tester.                                                                                   |

| тск2            | Ι   | CMOS   |         | Test clock input (for parallel scan use only).                                                                  |

### 8 JTAG – IEEE 1149.1 Test Access Port Controller Interface

The OpenSPARC T1 processor has five JTAG test access port (TAP) controller interface signals.

| TABLE 1-8 | JTAG- IEEE 1149.1 Test Access Port Interface Signal Descriptions |

|-----------|------------------------------------------------------------------|

|-----------|------------------------------------------------------------------|

| SIGNAL NAME | I/O | TYPE | Vref | FUNCTION                                                                                                                          |

|-------------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| TRST_L      | Ι   | CMOS |      | IEEE 1149 test reset input (active low).<br>Includes an on-chip pull-up resistor with a<br>value between 1.2k ohms and 4.5k ohms. |

| TMS         | Ι   |      |      | IEEE 1149 test mode select input. Includes an on-chip pull-up resistor with a value between 1.2k ohms and 4.5k ohms.              |

| TDI         | Ι   |      |      | IEEE 1149 test data input. Includes an on-chip<br>pull-up resistor with a value between 1.2k<br>ohms and 4.5k ohms.               |

| ТСК         | Ι   |      |      | IEEE 1149 test clock input.                                                                                                       |

| TDO         | 0   |      |      | IEEE 1149 test data output.                                                                                                       |

### 1.4.9 Power, Ground, Spares, and Unconnected Pins

Required power, ground, spares, and unconnected pins are physical-implementation dependent.

1.4.8