Fall 2006

VLSI Design FINAL EXAM. J. Abraham December 13, 2006

Name: Exam, No. 3

- Open Book, Open Notes.

- Time Limit: 3 hours (pace yourself).

- Check for 8 pages in exam.

- Write all your answers in the spaces/boxes provided.

- Show any calculations in these pages using the back of the pages if needed.

- State clearly any assumptions made.

#### 1. (10 points)

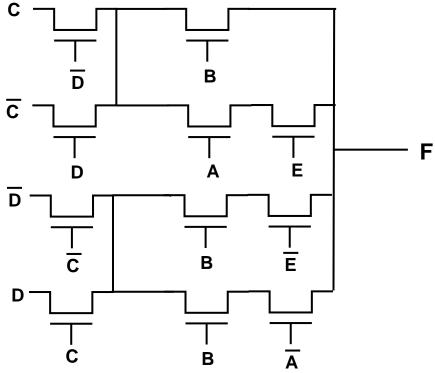

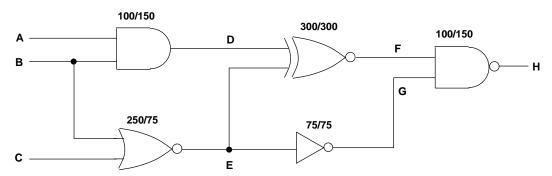

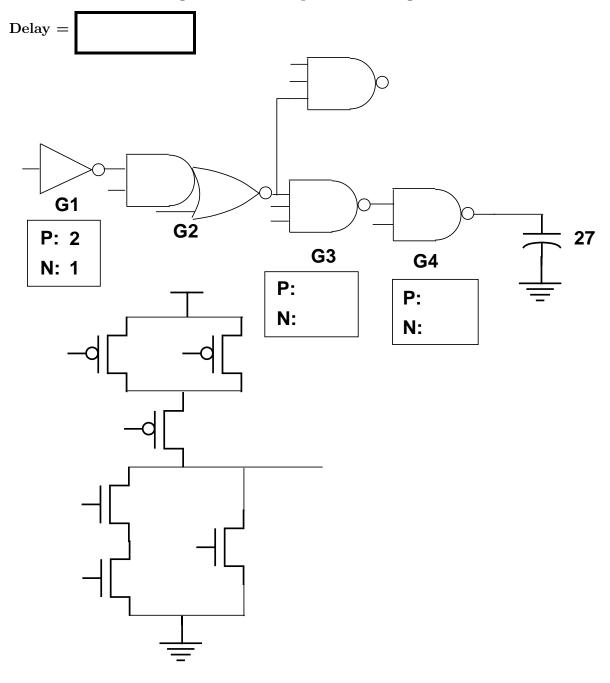

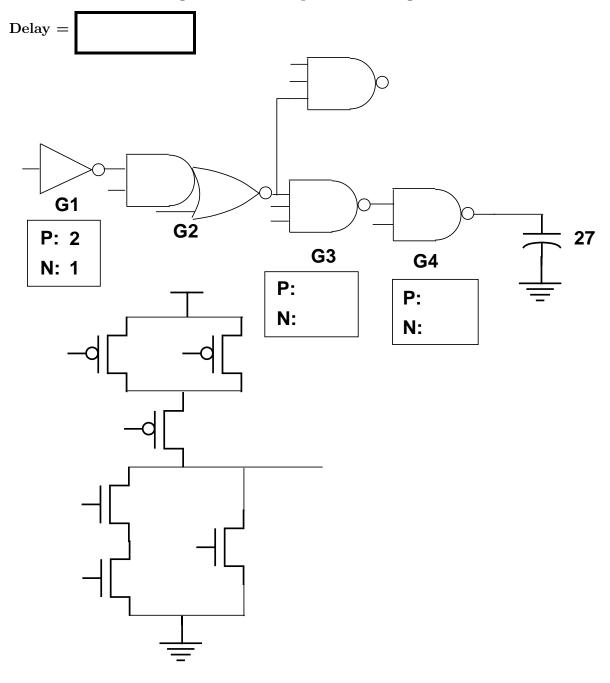

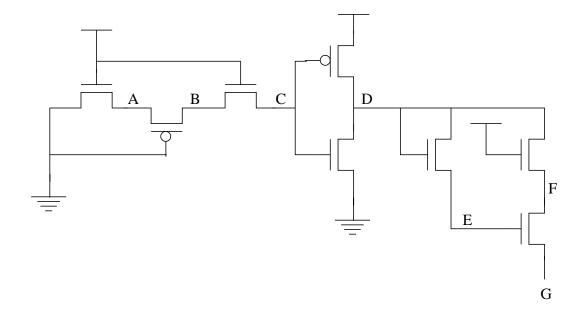

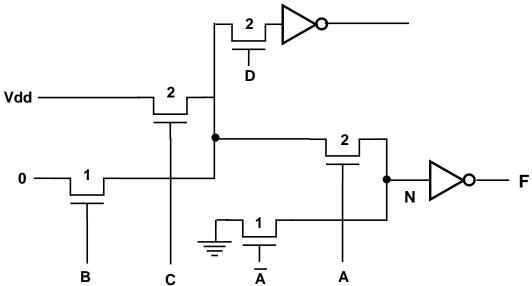

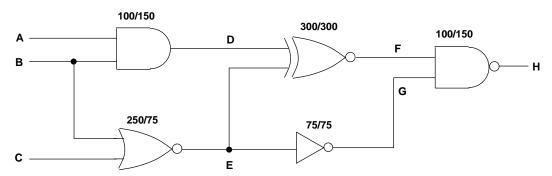

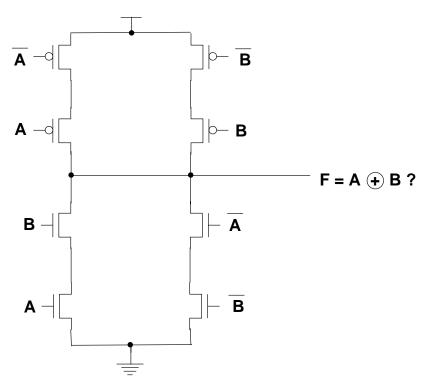

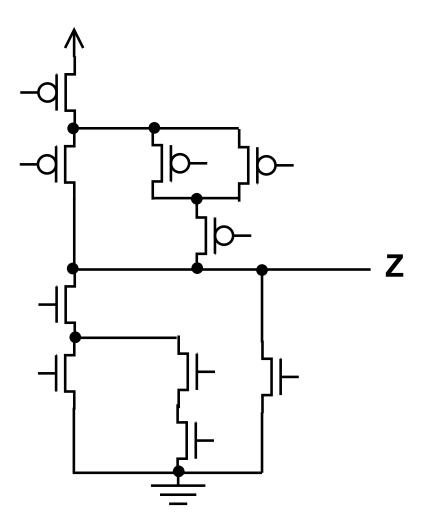

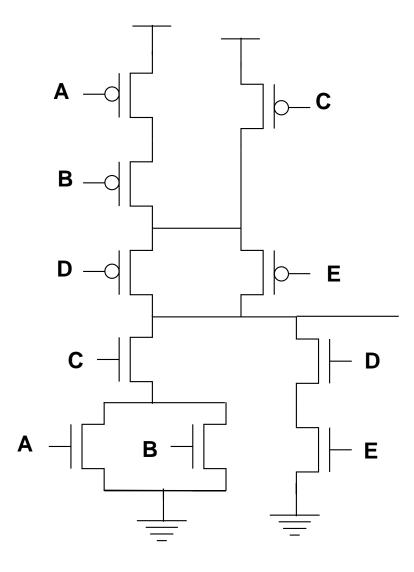

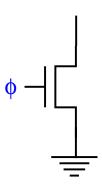

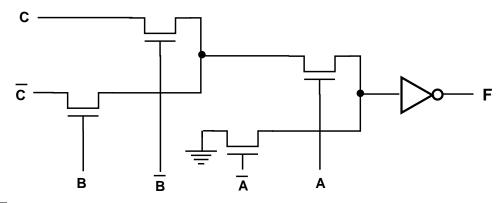

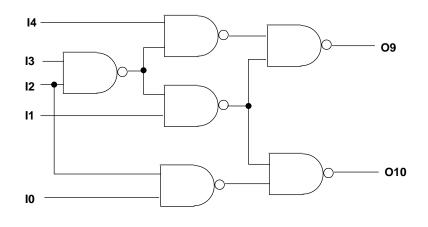

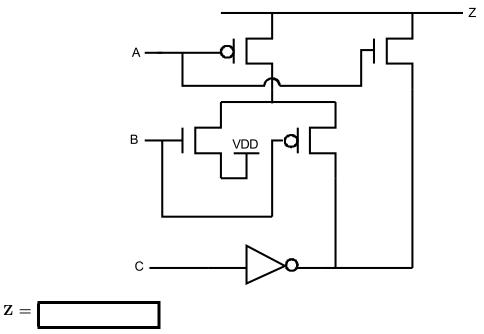

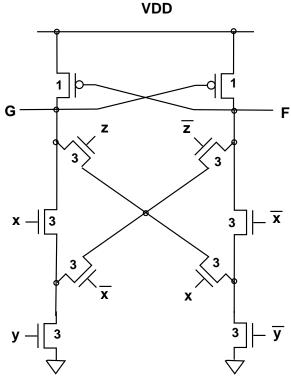

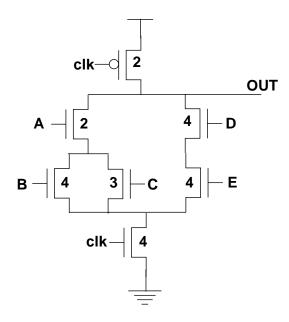

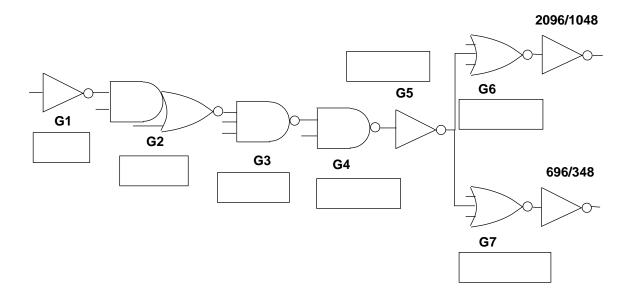

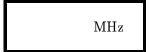

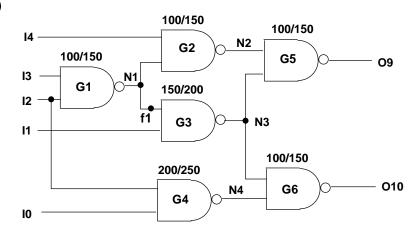

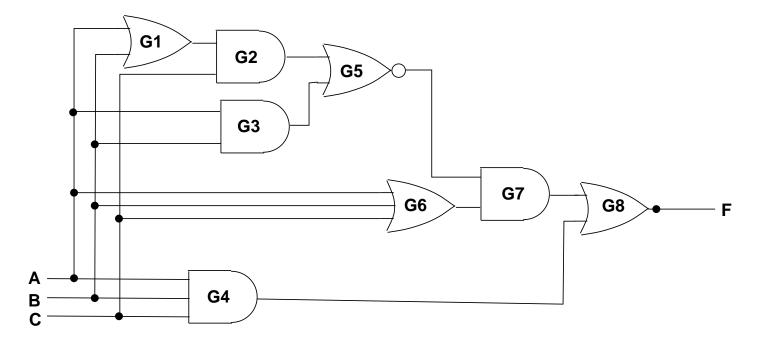

Write down the logic function implemented by the circuit below; use parantheses in the expression to reduce the number of literals.

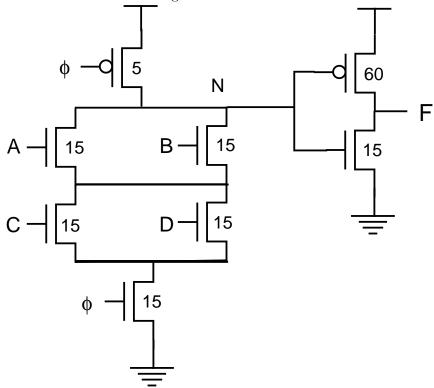

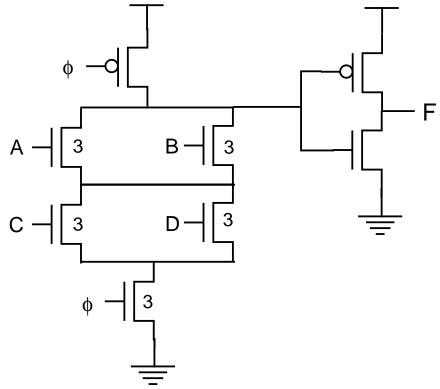

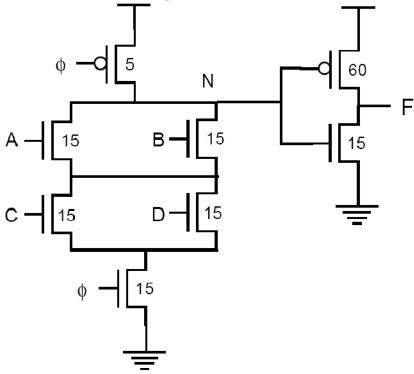

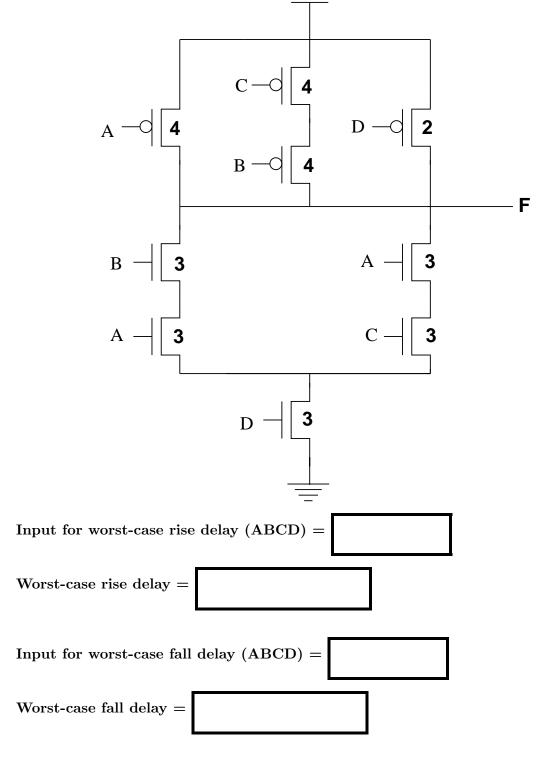

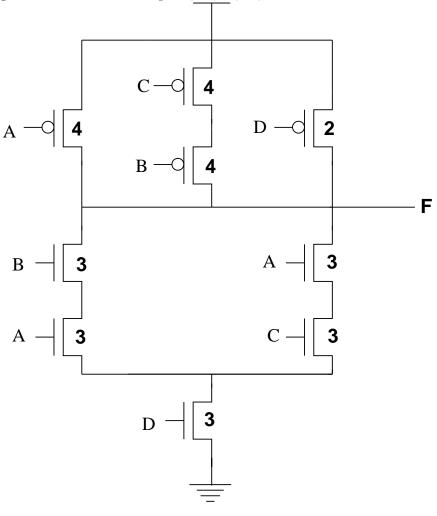

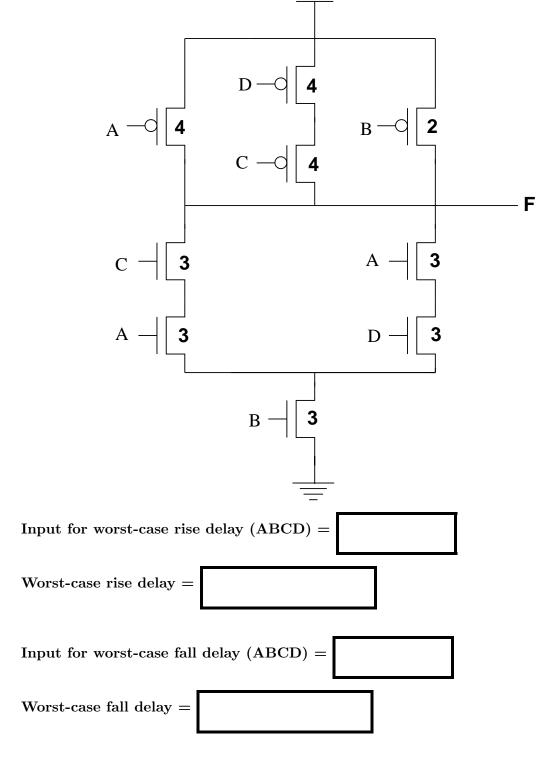

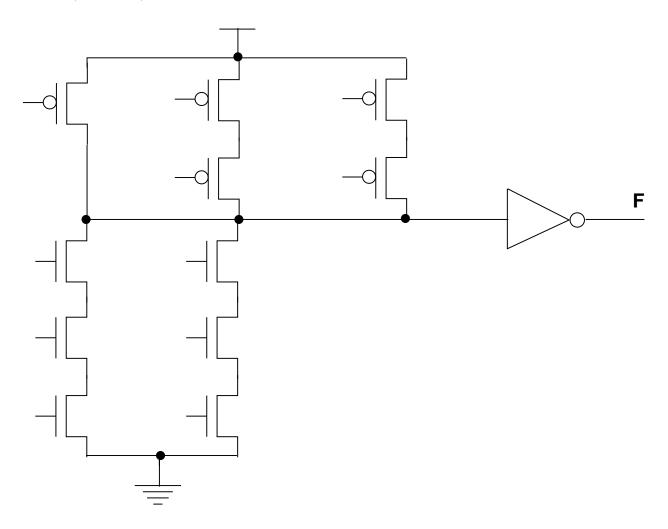

Find the largest as well as contimination delays for both 0-1 and 1-0 transitions for the circuit below. The widths of the transistors are given. Assume that a minimum width transistor will have an on-resistance of **R** and a gate capacitance of **C**; the source and drain capacitances are also C, and there is **no** sharing of diffusions. Give the input combinations which produce the respective delays (assuming that the internal nodes are charged or discharged as appropriate).

Input (ABCD) producing the largest rise delay:

Largest rise delay =

Input (ABCD) producing the largest fall delay:

Largest fall delay =

Input (ABCD) producing the smallest rise delay:

Contamination rise delay =

Input (ABCD) producing the smallest fall delay:

Contamination fall delay =

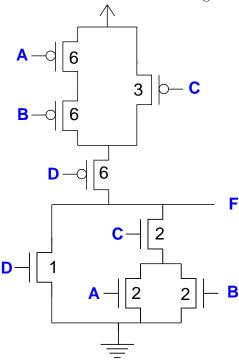

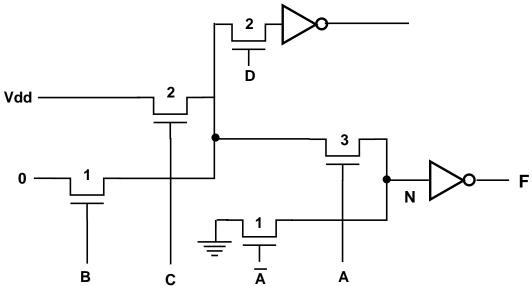

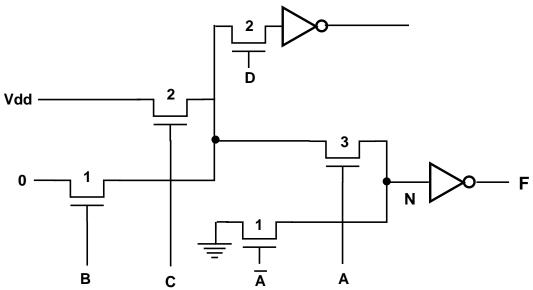

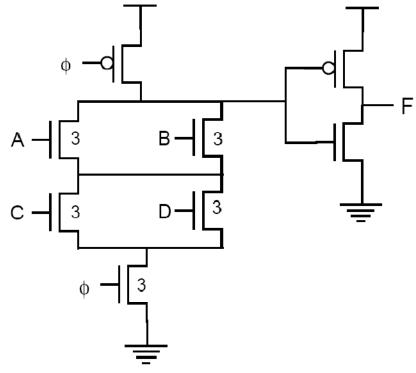

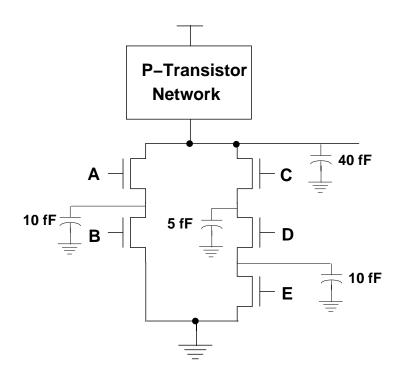

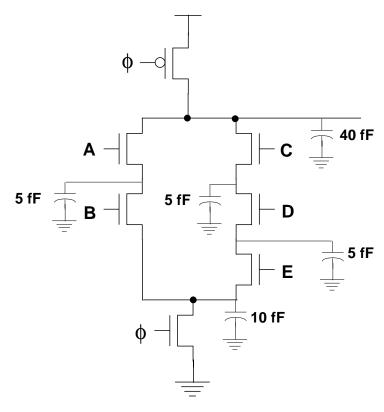

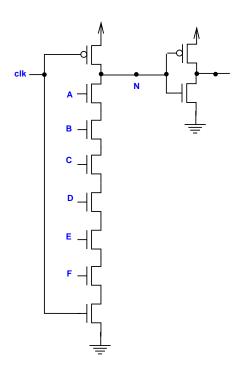

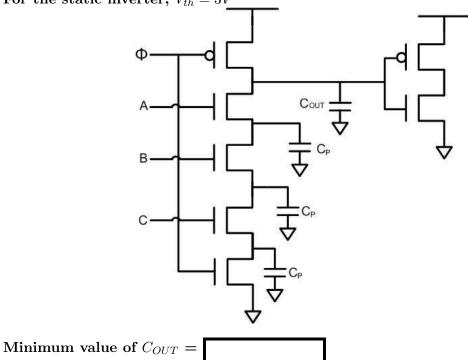

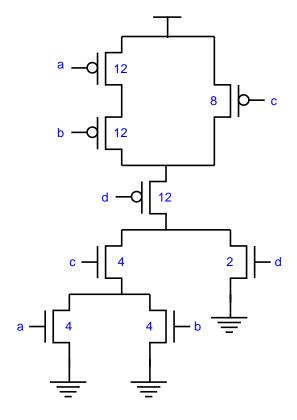

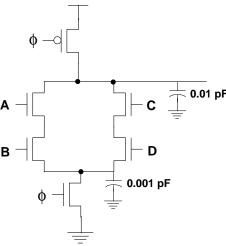

The domino circuit has the widths of the transistors shown next to them. Assume that a minimum width transistor has a gate capacitance of C, with the source and drain capacitances also each equal to C. Assume no sharing of diffusion.

(a) Under the worst-case input sequence, what is the largest voltage drop on the dynamic node, N?

(b) Give a sequence of inputs (ABCD) which will cause the voltage drop on N.

(c) How should the static inverter be sized to cause a voltage drop (noise) of at most 20% on the node N?

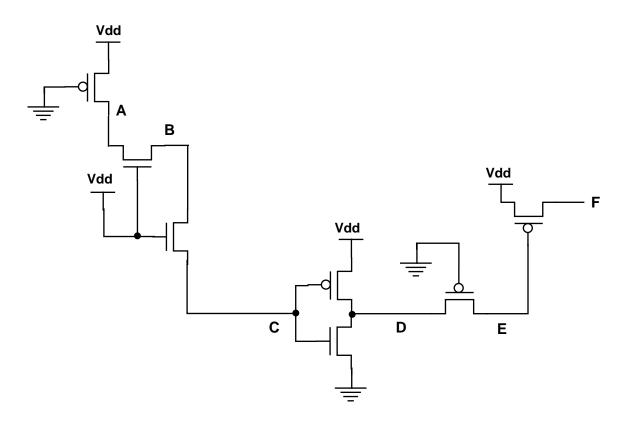

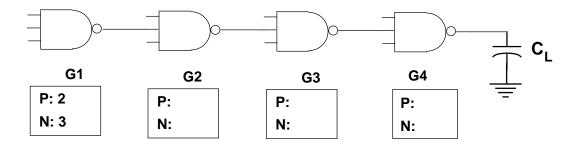

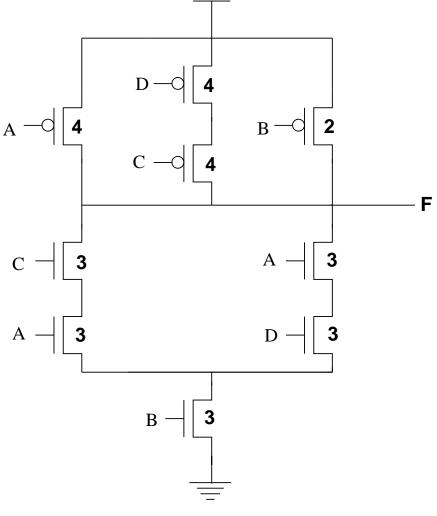

The best stage effort for a domino circuit has been found to be between 2.0 and 2.76 (for unfooted and footed blocks). The circuit below has the transistor widths labeled for the dynamic portion. The static inverter is a standard Hi-Skew with a logical effort of 5/6.

(a) If the stage effort is 2.5, what would be the corresponding path electrical effort, H (using the standard logical effort formulation)?

(b) What would be the delay of the circuit for the design in (a)?

(c) What would be the sizes of the P and N transistors in the static inverter (for the same design)?

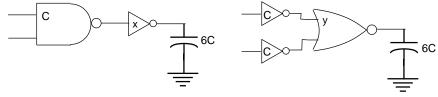

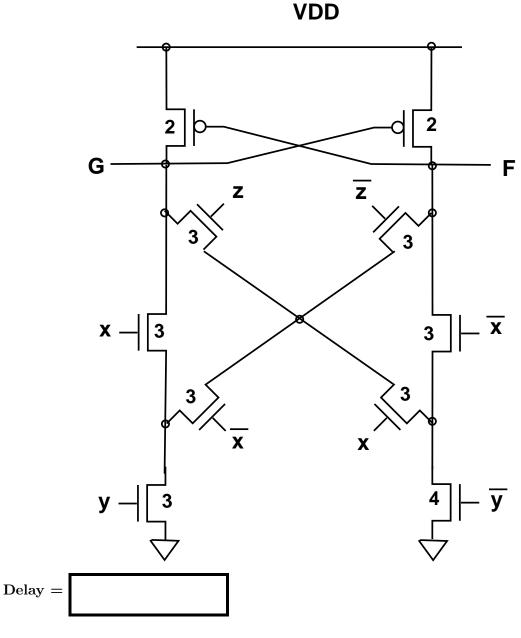

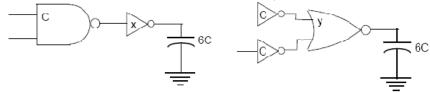

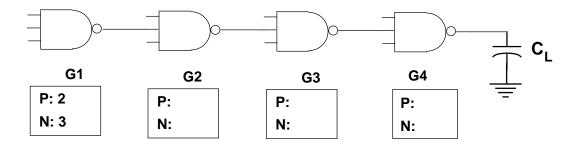

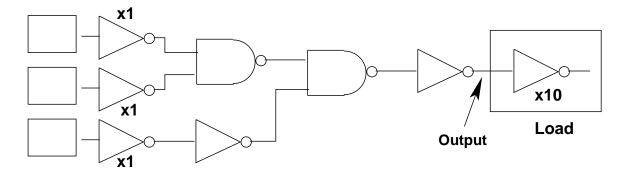

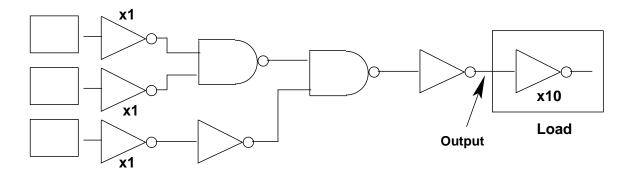

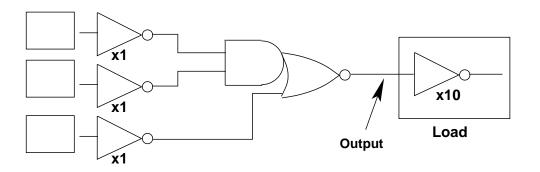

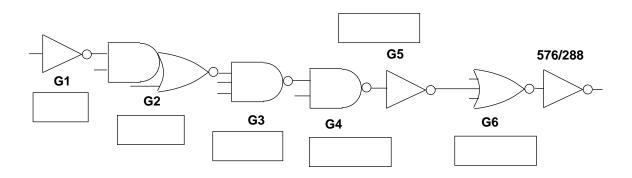

Consider the two different implementations of an AND gate below. Both have an input capacitance of C and both must drive a load six times the capacitance of each of the inputs.

(a) What is the path effort of each design?

(b) Which design will be the fastest? Explain.

(c) Compute the sizes of the logic gates, x and y to achieve the least delay.

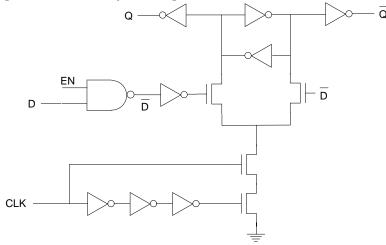

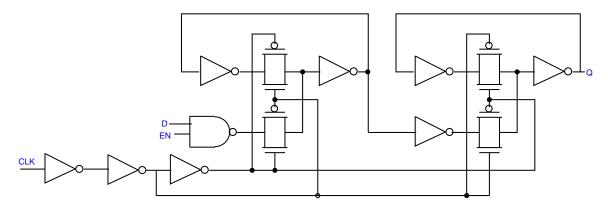

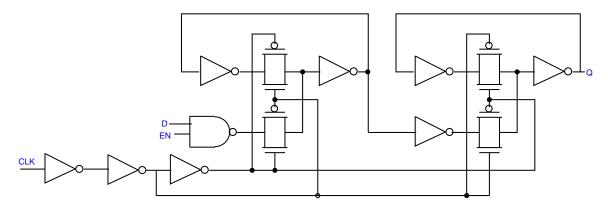

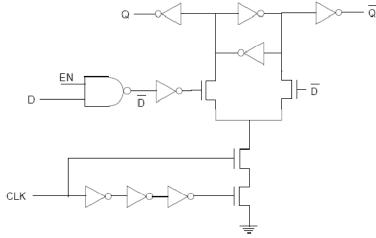

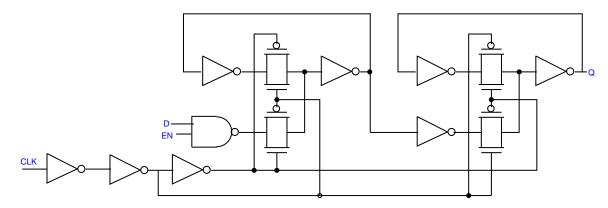

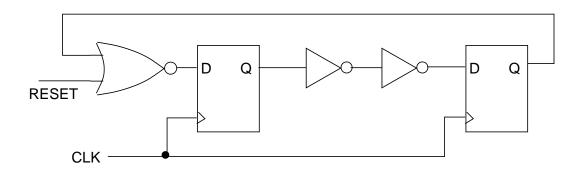

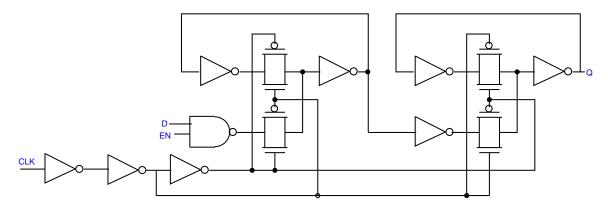

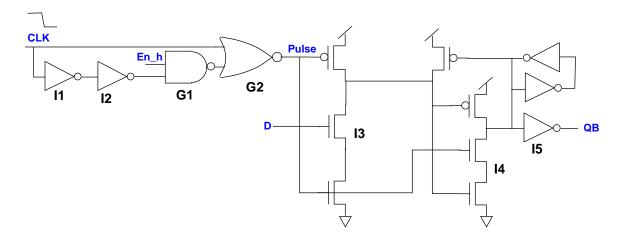

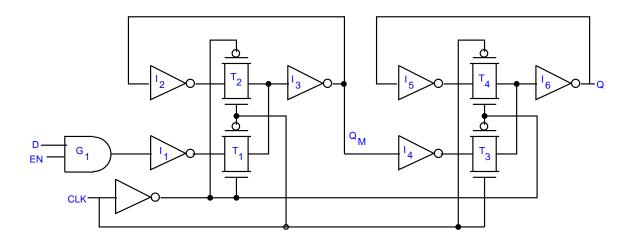

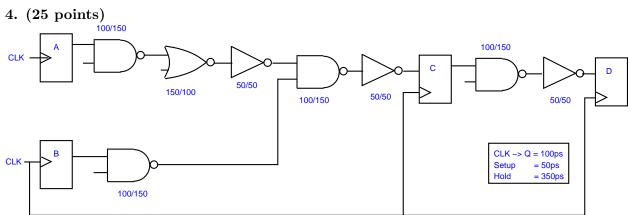

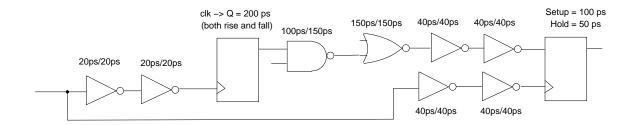

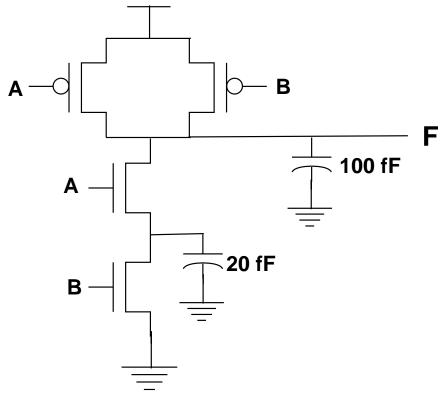

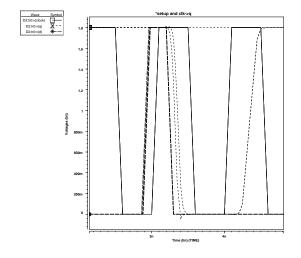

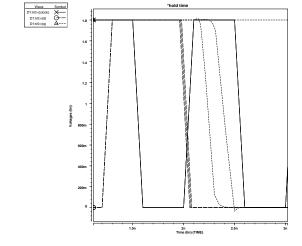

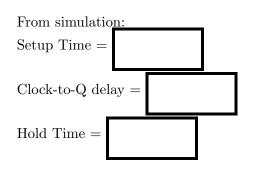

The inverters in the flip-flop below have rise and fall delays of 50 pS. The NAND gate has a rise delay of 100 pS and a fall delay of 150 pS.

Neglecting the delay of the nMOS transistors, what are the parameters of the flip-flop?

(a) Setup time

(b) Hold time

(c) CLK-Q delay

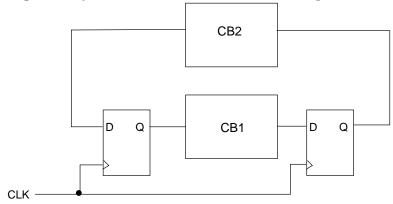

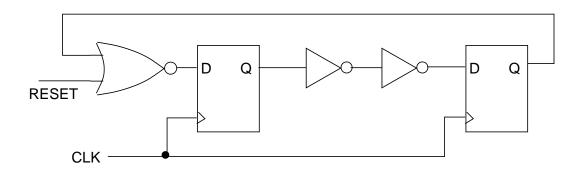

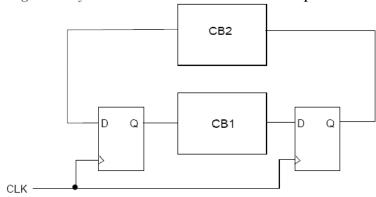

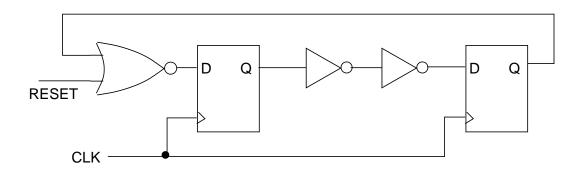

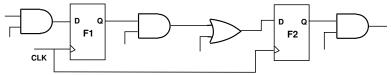

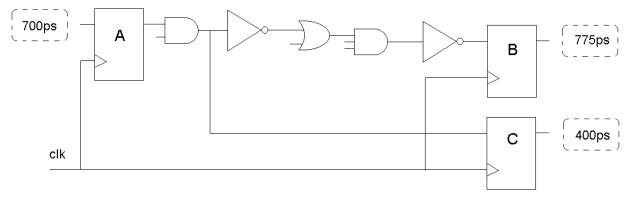

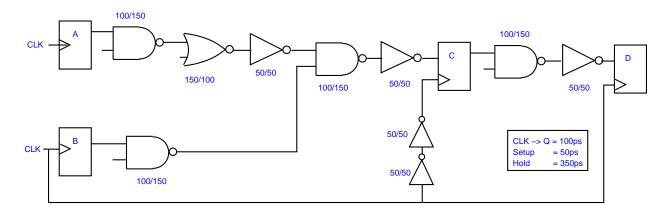

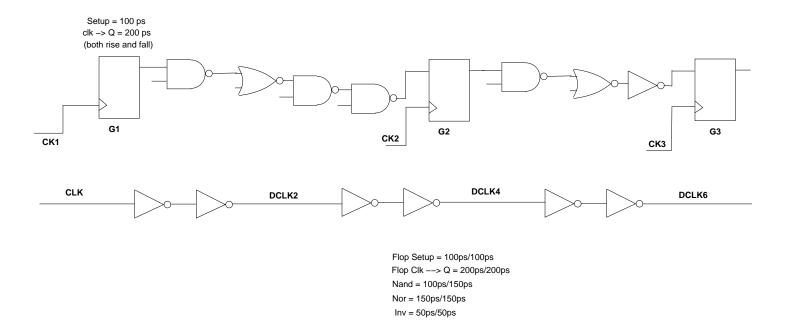

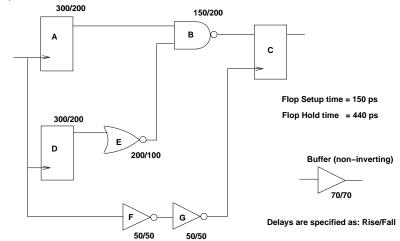

The sequential circuit below has two flops and two combinational blocks, CB1 and CB2. The design is made using a library which includes inverters with a 25 pS rise and fall delay.

The parameters of the flops are:  $t_{pcq} = 100pS$ ,  $t_{ccq} = 20pS$ ,  $t_{setup} = 50pS$ ,  $t_{hold} = 100pS$

The parameters of the combinational block are as follows.

CB1:  $t_{pd} = 250pS, t_{cd} = 100pS$ CB2:  $t_{pd} = 350pS, t_{cd} = 50pS$

(a) Will the circuit work correctly? Explain and, if not, suggest a fix which will not affect the maximum frequency at which the circuit can be operated.

(b) If the circuit can be operated correctly, what is the maximum frequency at which it will work correctly?

(c) Suggest a modification to the clock circuitry to increase the frequency found in (b). Explain.

An embedded hardware accelerator in a system-on-chip is designed in a 1 V, 90 nm process, and has 1 million logic transistors with an average width of  $12\lambda$ . The gate capacitance,  $C_g = 2fF/\mu m$ . The gates have an activity factor of 0.2.

(a) What is the maximum clock frequency if the dynamic power should not exceed 20 mW?

(b) If the subthreshold leakage is  $20nA/\mu m$  and the gate leakage is  $2nA/\mu m$ , and if half the transistors are off (on average), what is the leakage power?

VLSI Design EXAM. II J. Abraham November 20, 2006

Name: Exam, No. 2

• Open Book, Open Notes.

- Time Limit: 75 minutes (pace yourself).

- Check for 6 pages in exam.

- Write all your answers in the spaces/boxes provided.

- Show any calculations in these pages using the back of the pages if needed.

- State clearly any assumptions made.

#### 1. (20 points)

Fall 2006

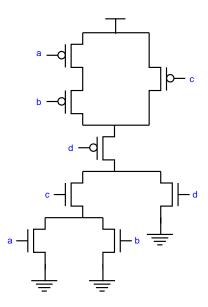

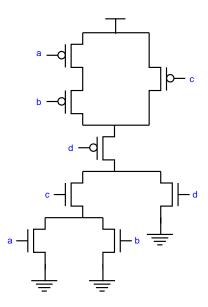

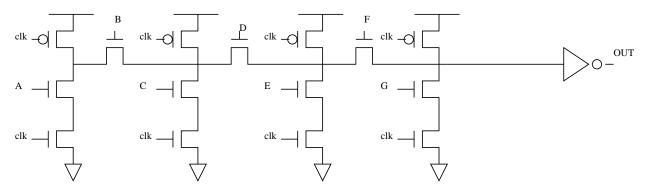

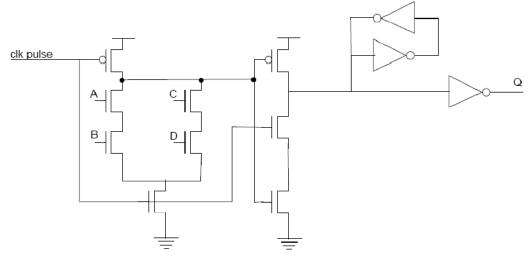

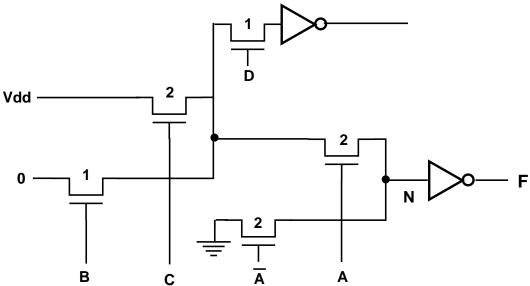

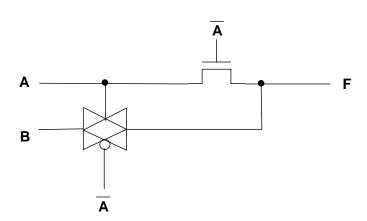

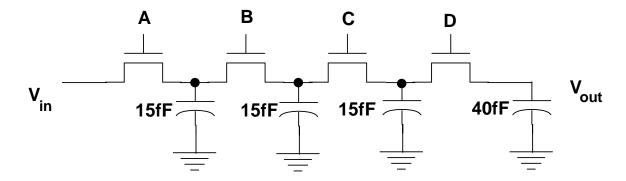

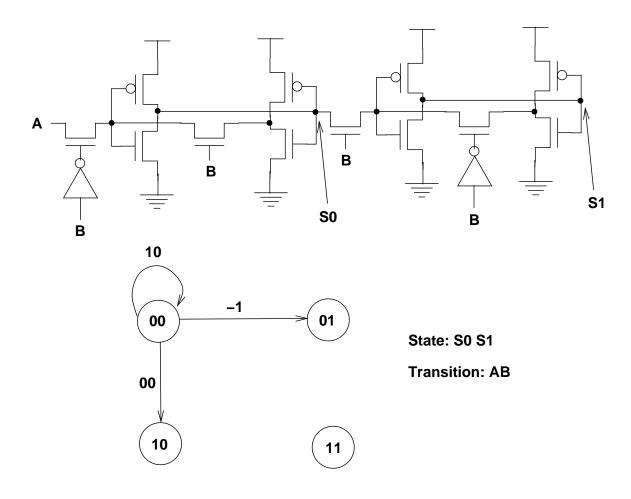

The inverters in the circuit below have minimum-sized transistors and the widths of the pass transistors are shown in the figure. Assume that the diffusion capacitance of a transistor is equal to its gate capacitance, and that a minimum sized transistor has gate and diffusion capacitance equal to C. In addition,  $V_{dd} = 2V$ ,  $V_{tn} = 0.3V$  and  $|V_{tp}| = 0.4V$ .

The sequence ABCD = (0011, 1001) is given as input to the circuit. Write down the voltage on node N just after the sequence is applied.

Voltage on Node N =

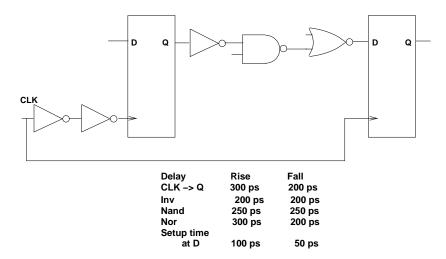

The components of the flip-flop below have the following rise/fall delays (in picoseconds).

Nand gate: 75/125

Transmission gate: 75/75

Inverter: 50/50

What are the values of the following flip-flop parameters (which a designer needs to use to calculate the performance of a system)?

| (a) | ${\bf Setup}$ | time = | ps |

|-----|---------------|--------|----|

|     |               |        | 1  |

(c) Clock-to-Q delay =

$$\boxed{}$$

ps

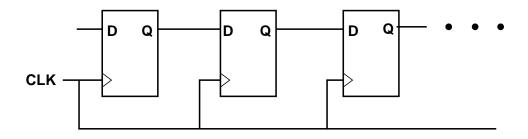

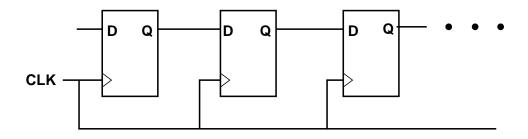

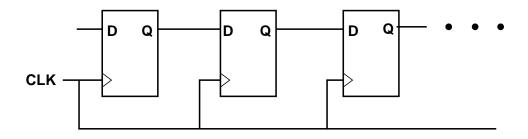

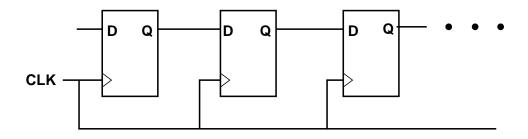

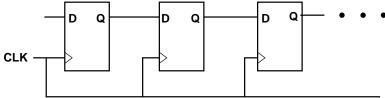

The flops used in the shift register below have a setup time of 100 ps, a maximum clock-Q delay of 150 ps, and a minimum clock-Q delay of 100 ps.

(a) How fast can this circuit be clocked?

(b) What is the limit on the hold time of the flops at this frequency?

| Hold time < | ps |

|-------------|----|

|             |    |

(c) What is the limit on the hold time of the flops at a frequency of 1 GHz?

| Hold time < |  | ps |

|-------------|--|----|

|-------------|--|----|

(d) What is the limit on the hold time of the flops if the circuit is clocked at a frequency of 100 MHz?

| ${\bf Hold\ time} <$ |  | ps |

|----------------------|--|----|

|----------------------|--|----|

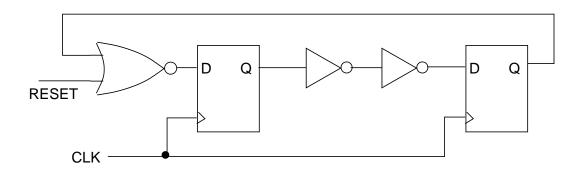

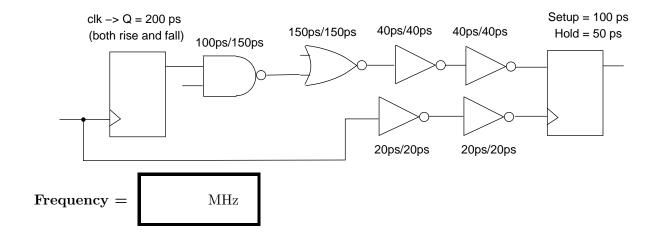

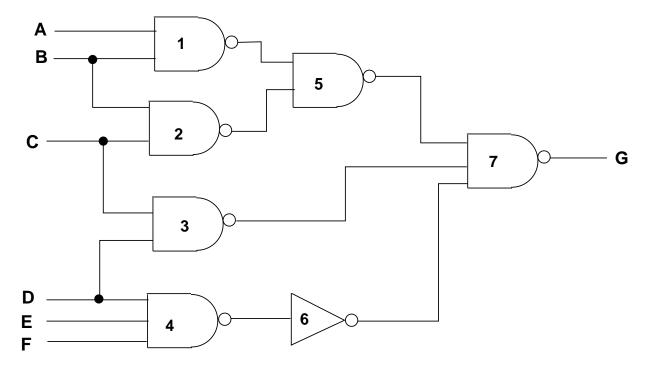

(a) What is the highest frequency at which the following circuit can be operated correctly? The parameters of the components are as follows.

Inverter:  $t_{pd} = 200ps$ ,  $t_{cd} = 100ps$

**2-input** NOR:  $t_{pd} = 200ps$ ,  $t_{cd} = 150ps$

D-flop:  $t_{pd}=200ps$   $t_{cd}=0ps$ , Setup time = 300 ps, Hold time = 100 ps.

${\bf Maximum~Clock~frequency = \boxed{ \ \ \, } {\bf MHz} \\$

(b) If the two inverters are removed (the Q of the first flop is connected to the D of the second), what will be the highest frequency at which the circuit can be operated. Explain your answer.

$Maximum\ Clock\ frequency = \boxed{\hspace{1cm}MHz}$

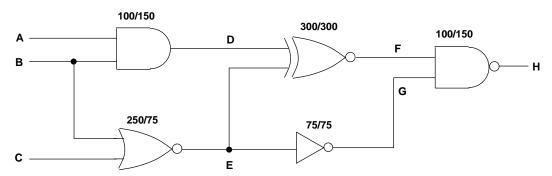

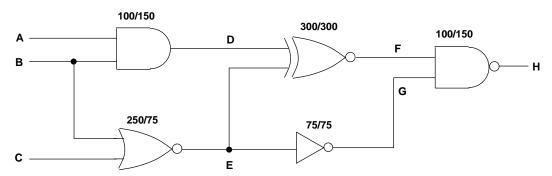

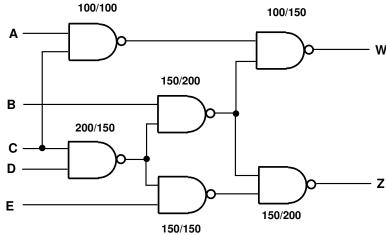

(a) Write down all the paths from input B to the output and the worst-case and lowest delays for each path in the circuit below. The rise and fall times (in picoseconds) for each gate are shown over the gate symbol as risetime/falltime.

For example, the paths from input A to the output, and the delays are:

Path Worst-case delay Lowest delay ADFH 600 ps 500 ps

- (b) Give the test sequences for the following cases:

- (i) Rising input on B, path BDFH

(i) Falling input on B, path BEFH

(ii) Rising input on B, path BEFH

VLSI Design EXAM. II

J. Abraham November 20, 2006

Name: Exam, No. 2

- Open Book, Open Notes.

- Time Limit: 75 minutes (pace yourself).

- Check for 6 pages in exam.

- Write all your answers in the spaces/boxes provided.

- Show any calculations in these pages using the back of the pages if needed.

- State clearly any assumptions made.

#### 1. (20 points)

Fall 2006

The inverters in the circuit below have minimum-sized transistors and the widths of the pass transistors are shown in the figure. Assume that the diffusion capacitance of a transistor is equal to its gate capacitance, and that a minimum sized transistor has gate and diffusion capacitance equal to C. In addition,  $V_{dd} = 2V$ ,  $V_{tn} = 0.3V$  and  $|V_{tp}| = 0.4V$ .

The sequence ABCD = (0011, 1001) is given as input to the circuit. Write down the voltage on node N just after the sequence is applied.

Voltage on Node N =

The components of the flip-flop below have the following rise/fall delays (in picoseconds).

Nand gate: 75/125

Transmission gate: 75/75

Inverter: 50/50

What are the values of the following flip-flop parameters (which a designer needs to use to calculate the performance of a system)?

| (a) | ${\bf Setup}$ | time = | ps |

|-----|---------------|--------|----|

|     |               |        | 1  |

(c) Clock-to-Q delay =

$$\boxed{}$$

ps

The flops used in the shift register below have a setup time of 100 ps, a maximum clock-Q delay of 150 ps, and a minimum clock-Q delay of 100 ps.

(a) How fast can this circuit be clocked?

(b) What is the limit on the hold time of the flops at this frequency?

| Hold time < | ps |

|-------------|----|

|             |    |

(c) What is the limit on the hold time of the flops at a frequency of 1 GHz?

| Hold time < |  | ps |

|-------------|--|----|

|-------------|--|----|

(d) What is the limit on the hold time of the flops if the circuit is clocked at a frequency of 100 MHz?

| ${\bf Hold\ time} <$ |  | ps |

|----------------------|--|----|

|----------------------|--|----|

(a) What is the highest frequency at which the following circuit can be operated correctly? The parameters of the components are as follows.

Inverter:  $t_{pd} = 200ps$ ,  $t_{cd} = 100ps$

**2-input** NOR:  $t_{pd} = 200ps$ ,  $t_{cd} = 150ps$

D-flop:  $t_{pd}=200ps$   $t_{cd}=0ps$ , Setup time = 300 ps, Hold time = 100 ps.

${\bf Maximum~Clock~frequency = \boxed{ \ \ \, } {\bf MHz} \\$

(b) If the two inverters are removed (the Q of the first flop is connected to the D of the second), what will be the highest frequency at which the circuit can be operated. Explain your answer.

$Maximum\ Clock\ frequency = \boxed{\hspace{1cm}MHz}$

(a) Write down all the paths from input B to the output and the worst-case and lowest delays for each path in the circuit below. The rise and fall times (in picoseconds) for each gate are shown over the gate symbol as risetime/falltime.

For example, the paths from input A to the output, and the delays are:

Path Worst-case delay Lowest delay ADFH 600 ps 500 ps

- (b) Give the test sequences for the following cases:

- (i) Rising input on B, path BDFH

(i) Falling input on B, path BEFH

(ii) Rising input on B, path BEFH

VLSI Design EXAM. I

Spring 2006

J. Abraham March 1, 2006

Name: Student, A

Open Book, Open Notes. Time Limit: 75 minutes (pace yourself). Check for 5 pages in exam.

Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 15  |        |

| 2       | 20  |        |

| 3       | 20  |        |

| 4       | 25  |        |

| 5       | 20  |        |

| TOTAL   | 100 |        |

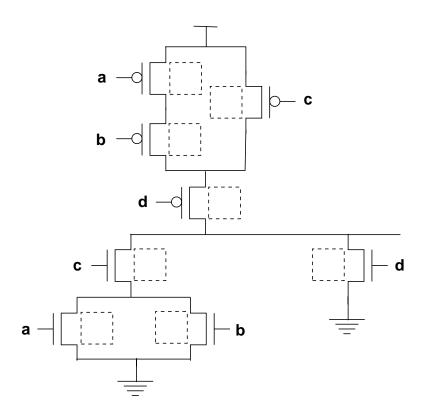

#### 1. (15 points)

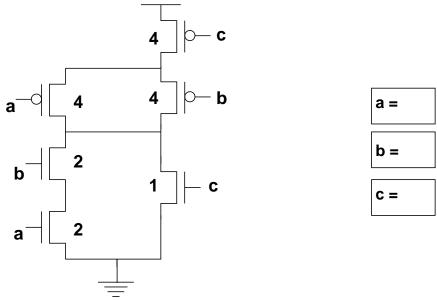

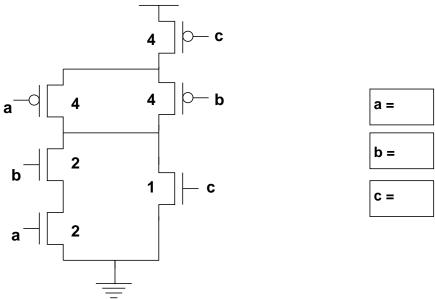

Size the transistors in the circuit below so that it has the same drive strength, in the worst case, as an inverter that has PW = 3 and NW = 2. Use the smallest widths possible to achieve this ratio. Write down the size next to each transistor.

2. (20 points) Find the voltages at each of the nodes, A, B, C, D, E and F below. Use the following circuit parameters:

$V_{dd} = 5V, V_{tn} = 0.5V, |V_{tp}| = 1.5V.$

| A =             |  |

|-----------------|--|

| $\mathbf{B} = $ |  |

$$E =$$

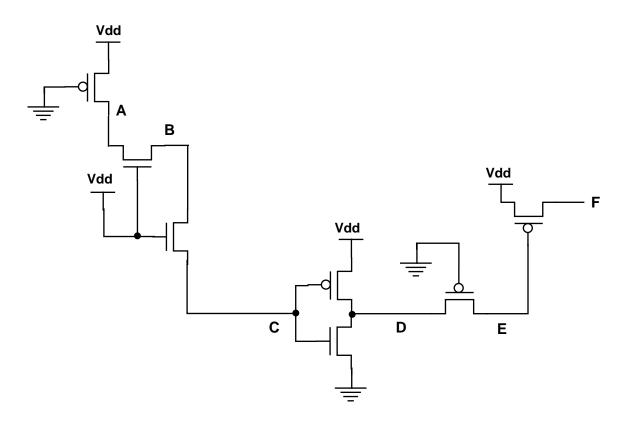

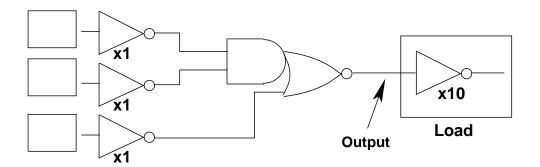

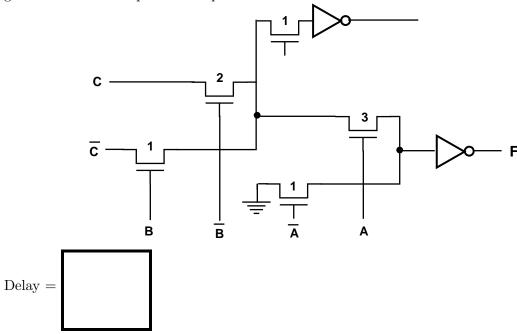

Use the Elmore delay approximation to find the worst-case fall delay at output F for the following circuit. The gate sizes of the transistors are shown in the figure. Use the assumption that the diffusion capacitance is equal to the gate capacitance and that a minimum sized transistor has gate and diffusion capacitance equal to C. The resistance of a nMOS transistor with unit width is R. Also assume NO sharing of diffusion regions.

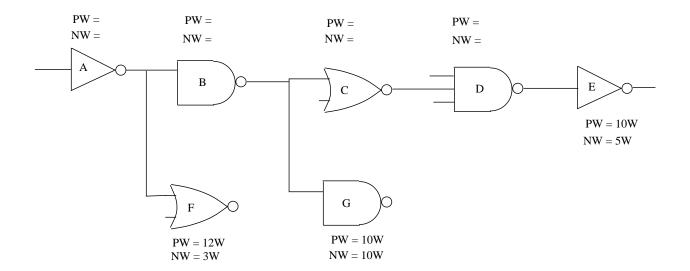

Find the sizes of the transistors for the circuit below for the least delay from the input to the output. Label the sizes in the boxes for the simple gates and besides the transistors in the figure for the compound AOI21 gate.

| 5. (         | (20 | points) | ١ |

|--------------|-----|---------|---|

| <b>U</b> • ( | 40  | pomb    | , |

A four-level circuit has been designed to have the least delay, D, from input to output, which can be written as the sum of the path effort delay and the path parasitic delay,  $D = D_F + P$ .

(a) If the output capacitance is now 2 times the original capacitance, with all other parameters remaining the same, what will be the increase in delay of the circuit as a multiple of the original path effort delay,  $D_F$ ?

| Increase in Delay = |  |

|---------------------|--|

| 3                   |  |

(b) What will be the increase in delay if the output capacitance is the same, but the parasitic delay is now 2 times the original?

| Increase in Delay = |  |

|---------------------|--|

|---------------------|--|

(c) If the original circuit is designed using 3-input NAND gates, what will be the increase in delay, as a fraction of  $D_F$  if each gate is replaced with a 3-input NOR gate (with the output capacitance remaining the same)?

| (Delay Increase)/ $D_F =$ |  |

|---------------------------|--|

|                           |  |

VLSI Design EXAM. I

Spring 2006

J. Abraham March 1, 2006

Name: Student, A

Open Book, Open Notes. Time Limit: 75 minutes (pace yourself). Check for 5 pages in exam.

Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 15  |        |

| 2       | 20  |        |

| 3       | 20  |        |

| 4       | 25  |        |

| 5       | 20  |        |

| TOTAL   | 100 |        |

#### 1. (15 points)

Size the transistors in the circuit below so that it has the same drive strength, in the worst case, as an inverter that has PW = 3 and NW = 2. Use the smallest widths possible to achieve this ratio. Write down the size next to each transistor.

2. (20 points) Find the voltages at each of the nodes, A, B, C, D, E and F below. Use the following circuit parameters:

$V_{dd} = 5V, V_{tn} = 0.5V, |V_{tp}| = 1.5V.$

| A =             |  |

|-----------------|--|

| $\mathbf{B} = $ |  |

$$E =$$

Use the Elmore delay approximation to find the worst-case fall delay at output F for the following circuit. The gate sizes of the transistors are shown in the figure. Use the assumption that the diffusion capacitance is equal to the gate capacitance and that a minimum sized transistor has gate and diffusion capacitance equal to C. The resistance of a nMOS transistor with unit width is R. Also assume NO sharing of diffusion regions.

Find the sizes of the transistors for the circuit below for the least delay from the input to the output. Label the sizes in the boxes for the simple gates and besides the transistors in the figure for the compound AOI21 gate.

| 5. (         | (20 | points) | ١ |

|--------------|-----|---------|---|

| <b>U</b> • ( | 40  | pomb    | , |

A four-level circuit has been designed to have the least delay, D, from input to output, which can be written as the sum of the path effort delay and the path parasitic delay,  $D = D_F + P$ .

(a) If the output capacitance is now 2 times the original capacitance, with all other parameters remaining the same, what will be the increase in delay of the circuit as a multiple of the original path effort delay,  $D_F$ ?

| Increase in Delay = |  |

|---------------------|--|

| 3                   |  |

(b) What will be the increase in delay if the output capacitance is the same, but the parasitic delay is now 2 times the original?

| Increase in Delay = |  |

|---------------------|--|

|---------------------|--|

(c) If the original circuit is designed using 3-input NAND gates, what will be the increase in delay, as a fraction of  $D_F$  if each gate is replaced with a 3-input NOR gate (with the output capacitance remaining the same)?

| (Delay Increase)/ $D_F =$ |  |

|---------------------------|--|

|                           |  |

## NAME:

- Time = 180 mins

- Closed book/notes; one crib sheet

- Write your answers on the exam

- Show your work and give explanations

- Absolutely no questions will be entertained—if you feel a question is ambiguous or incomplete, make and state reasonable assumptions.

# Manufacturing

Write 2-3 sentence descriptions of the following terms:

• Lithography

$\bullet$  Chemical-mechanical polishing

• Ion-implantation

# Layout

Draw the mask defining the polysilicon of a unit inverter in a 100nm process.

## Transistor theory

Suppose you designed a unit inverter in a  $0.1\mu$  CMOS process. The inverter is designed in static CMOS (i.e., the standard way) for equal rise and fall times, specifically, the nmos device is minimum length and width, and the pmos device is minimum length and  $2\times$  minimum width.

The manufacturing process can result in upto

- a 10% variation in the width, and

- $\bullet$  a 25% variation in the length

for the actual device that is fabricated.

(This is true for both nmos and pmos devices, and the variations are independent.)

Assume that the supply voltage is 1 Volt, and  $|V_T| = 0.2V$  for both nmos and pmos devices.

Recall that in the absence of variation, the inverter switching threshold voltage<sup>1</sup> will be  $V_{DD}/2$ .

In the presence of variation within the ranges above, what is the minimum and maximum switching threshold?

12 marks

<sup>&</sup>lt;sup>1</sup>the inverter switching threshold voltage is the input voltage for which  $V_{out} = V_{DD}/2$

## Circuit families

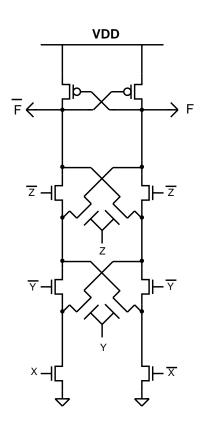

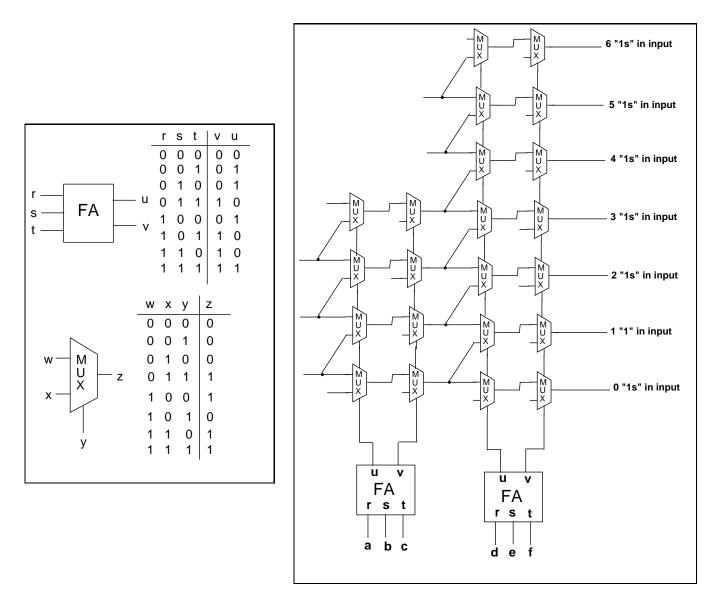

1. For the dynamic circuit below, write the function computed at the output as a function of the inputs.

## 8 marks

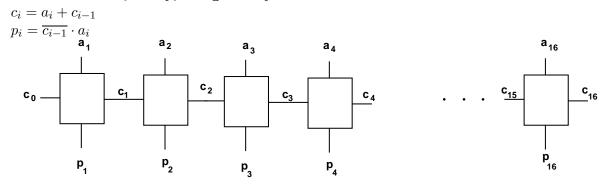

2. Describe how the circuit above could be used in a high-performance adder.

## 5 marks

## Datapath

You are to design logic that takes 8 bits of input  $A_0, A_1, \ldots, A_7$ , and outputs 8 bits of output  $B_0, B_1, \ldots, B_7$ .

The outputs are defined by the following equation:

$$B_i = A_0 + A_1 + \dots + A_i$$

You are required to use nothing but 2-input OR gates.

You must compute the outputs using as few OR gates as possible, subject to the constraint that there are no more than 3 gates on any path from input to output.

## Adders

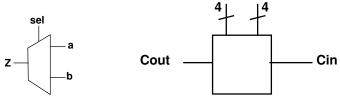

A full-adder has 3 inputs and 2 outputs; the outputs implement the following two logic equations:

$$C_{out} = A \cdot B + B \cdot C_{in} + A \cdot C_{in}$$

$S_{out} = A \oplus B \oplus C_{in}$

Show that if the inputs to the full-adder are inverted, then so are the outputs.

Use this fact to design a 4-bit ripple carry adder in static CMOS with reduced delay.

## Delay Analysis

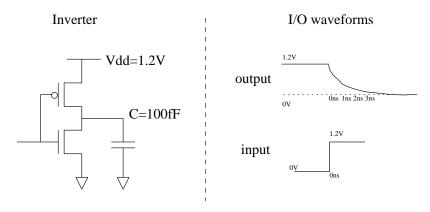

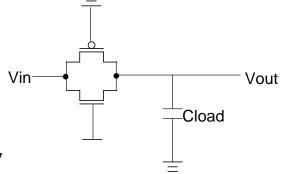

Consider the circuit shown below. From the plot of  $V_{out}$  vs. time, estimate the effective resistance of the NMOS transistor. (Assume that all the capacitance seen on the output of the inverter is lumped into C.)

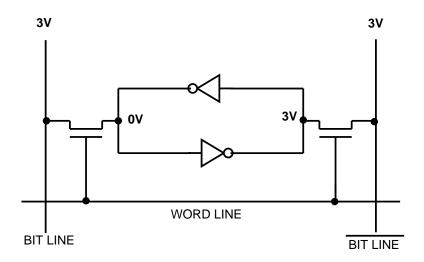

#### RAMs

1. Draw a 6-T SRAM cell at the transistor level.

2. What must the relative sizes of the transistors in a 6-T SRAM cell be to guarantee read-stability and write stability? Explain how these sizes guarantee read-stability and write-stability.

## ${\it Test/Verification}$

1. What is the most common way in which a chip fails because of manufacturing defects?

### 4 marks

2. Describe BIST. Specifically address benefits and shortcomings, in addition to the underlying principles.

12 marks

#### Power

Consider a ROM in a 100 nm process, with a  $1.2~\mathrm{V}$  supply. The ROM has  $64~\mathrm{words}$ , each  $32~\mathrm{bits}$  wide.

The ROM uses pseudo-nmos decoders. The pmos pull-up transistor has a  $\beta$  of  $75\mu A/V^2$  and  $|V_{tp}|=0.4V$ .

Compute the static power drawn by the ROM  $\underline{\text{decode logic}}$ .

#### Power

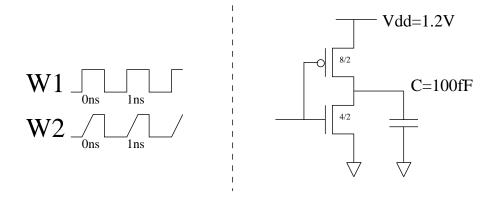

The inverter is implemented in a 100 nm process. Compute the power consumed by the inverter below when it is driven by the input W1—a square wave which swings from 0V to supply, with a duty cycle of 50% and frequency of 1 Ghz..

Does the power increase, decrease or stay the same when the input is W2?

#### **Scaling**

1. Give the single most important reason why gate oxide thickness has reduced as processes have scaled.

#### 4 marks

2. In a 65nm process, under the best of circumstances—highest metal layer, optimum repeatering, no coupling, etc.—the delay of interconnect is of the order of 50 ps/mm. This translates into a delay of 1000 ps for a wire traveling from one end of a 10mm x 10mm die to the diagonally opposite end. Does this imply that such a design cannot run faster than 1 Ghz?

6 marks

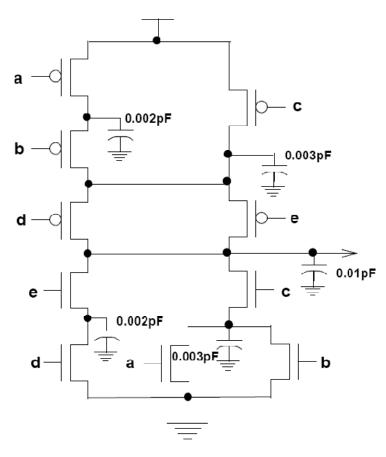

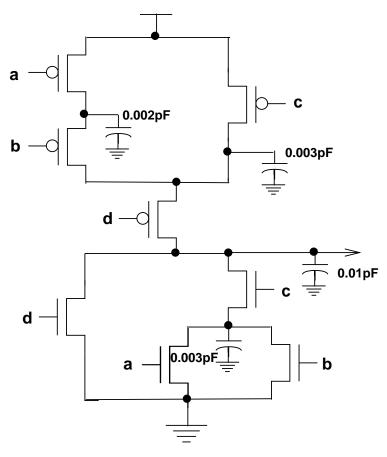

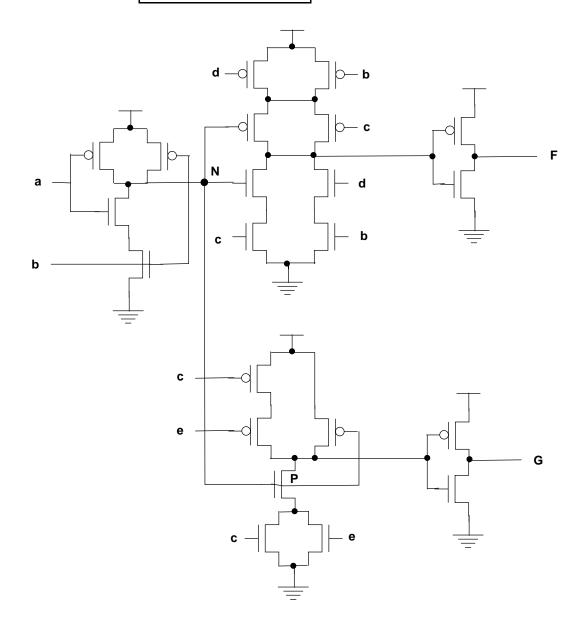

In the static CMOS circuit below, the on-resistance of each n-channel transistor is 5 KOhms and that of a p-channel transistor is 10 KOhms. The gate capacitance of an n-channel transistor is 0.02pF and p-channel transistor is 0.03pF. The source/drain capacitance of an n-channel transistor is 0.001pF and for a p-channel transistor is 0.002pF. The routing capacitances for interconnections are lumped at the nodes as shown.

(a) Find the delay when (a b c d e) makes the following transitions: 0 0 0 0 0  $\Rightarrow$  0 0 0 1 1  $\Rightarrow$  0 0 0 0 1.

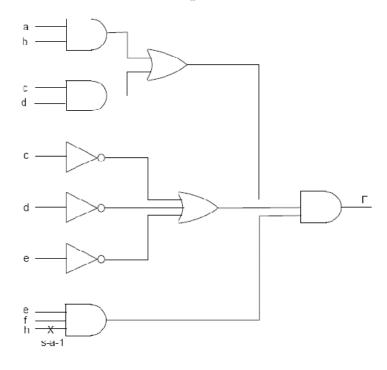

(a) Find a test for the line h stuck-at-1 in the figure below.

(b) Perform test generation for the following faults and explain the results.

- (i) g s-a-0

- (ii) e s-a-1

- (iii) f s-a-0

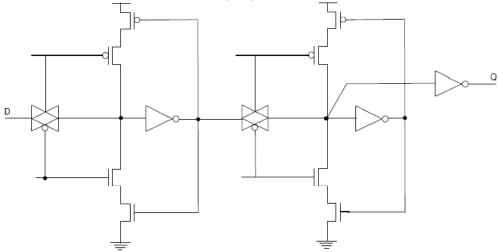

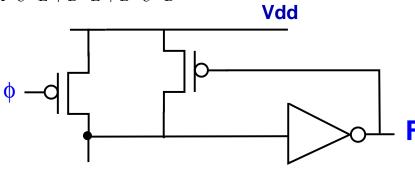

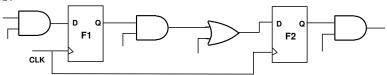

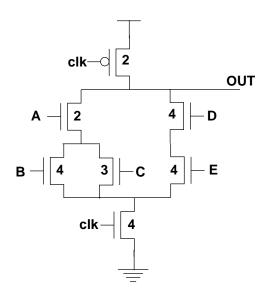

(a) Label the four inputs in the circuit below with the clock symbols CLK and CLKB (complement of CLK) so that the flop latches at the falling edge of the clock.

(b) Analyze the following circuit and write down the equation for its function.

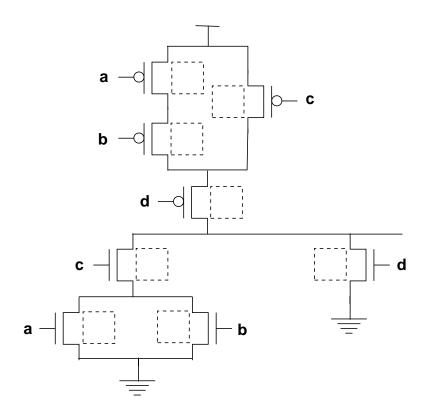

a) Draw the schematic for a <u>static</u> CMOS network for the following function using the minimum number of transistor. Do NOT assume that the inverted inputs are available.

$$Y = A'B'C' + ABC' + A'B'C + ABC$$

b) Draw a Domino CMOS schematic (with PMOS precharge and feedback hold device) of the following functions F1 and F2 using the minimal number of transistors.

$$F1 = (M \cdot N + W) \cdot P \cdot (Q \cdot R + S \cdot T)$$

$$F2 = T \cdot S + R \cdot Q$$

a) Write down the function OUT implemented by the circuit below: Minimize the number of transistors and draw the new schematic. Do NOT assume that the complementary inputs are available.

Describe the regions of operation for the NMOS and PMOS device in the transmission gate shown below in terms of linear, saturation and cutoff as the capacitor is charged or discharged:  $\,=\,$

$$Vtn = 1.0V Vtp=1.0V$$

#### a) Initial conditions: Vin = 5.0V Vout = 0.0V

| Condition              | PMOS Region | NMOS Region |

|------------------------|-------------|-------------|

| Vin = 5.0V Vout = 0.0V |             |             |

| Vin = 5.0V Vout = 2.5V |             |             |

| Vin = 5.0V Vout = 5.0V |             |             |

#### b) Initial conditions: Vin = 0.0V Vout = 5.0V

| Condition              | PMOS Region | NMOS Region |

|------------------------|-------------|-------------|

| Vin = 0.0V Vout = 5.0V |             |             |

| Vin = 0.0V Vout = 2.5V |             |             |

| Vin = 0.0V Vout = 0.0V |             |             |

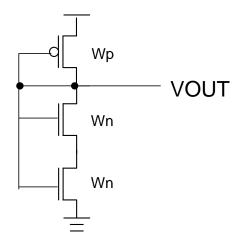

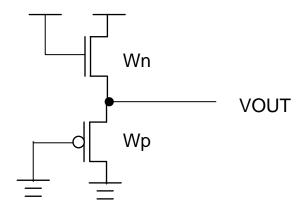

a) Determine the voltage on node VOUT.

Assume:  $\mu_n = 2 \cdot \mu_p$  Ln = Lp Vtn = Vtp

Both transistors are operating in the saturation region.

Express value on VOUT as a function of Wn, Wp and VDD

**b)** Determine the voltage on node VOUT.

Both transistors are operating in the saturation region.

Express value on VOUT as a function of Wn, Wp and VDD

| a) | Explain how the parasitic (field) transistor is formed between two n-channel transistors. How would you reduce the effects of these parasitic transistors?                                                                                                                 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b) | How does a "dummy collector" prevent latch up?                                                                                                                                                                                                                             |

|    |                                                                                                                                                                                                                                                                            |

|    |                                                                                                                                                                                                                                                                            |

| a) | Explain how the shape of the input waveform to a CMOS inverter alters the delay through the gate.                                                                                                                                                                          |

| b) | Explain how you would estimate and plan the clock distribution scheme in a chip. Summarize the parameters that are relevant and explain how your scheme deals with these.                                                                                                  |

|    |                                                                                                                                                                                                                                                                            |

| a) | What limits the VDD supply voltage in a CMOS technology (i.e., how low or high car you set it)? Explain what you expect the effects of these two voltage extremes to be on the internal circuits. Suggest situations where both of these voltage extremes might be of use. |

| b) | Suggest the approaches you would take to reduce the power dissipation of a CMOS chip.                                                                                                                                                                                      |

|    |                                                                                                                                                                                                                                                                            |

|    |                                                                                                                                                                                                                                                                            |

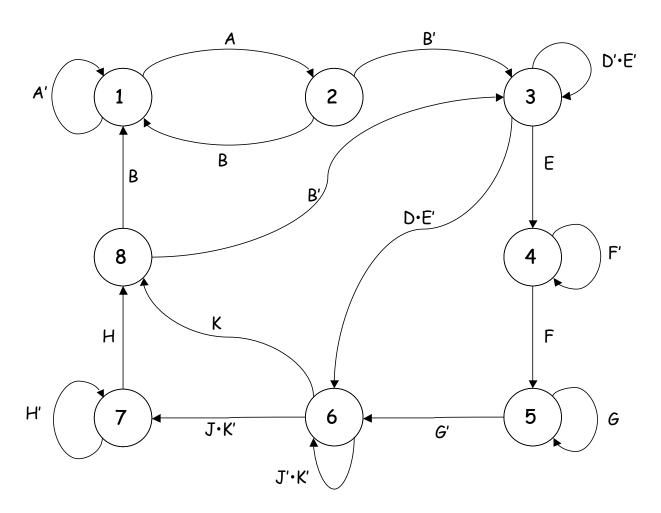

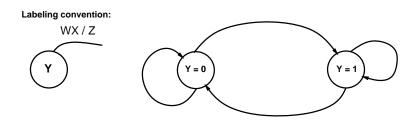

a) Complete the following state diagram for arcs: 8->3 6->7 3->6

Confirm that all other arcs are correct. If not, correct the equation(s).

b) How many memory elements (Flip-Flops) are required to implement the state machine for:

One-Hot Encoding:

Fully Encoded:

c) How many inputs are required for the state machine including state inputs for:

One-Hot Encoding:

Fully Encoded:

d) Fill out the following State Table for the state machine described above:

| Current<br>State | А | В | D | E | F | G | Н | J | К | <i>Next</i><br>State |

|------------------|---|---|---|---|---|---|---|---|---|----------------------|

| 1                | 0 |   |   |   |   |   |   |   |   | 1                    |

| 1                | 1 |   |   |   |   |   |   |   |   | 2                    |

| 2                |   | 1 |   |   |   |   |   |   |   | 1                    |

| 2                |   | 0 |   |   |   |   |   |   |   | 3                    |

| 3                |   |   | 0 | 0 |   |   |   |   |   | 3                    |

| 3                |   |   |   | 1 |   |   |   |   |   | 4                    |

| 3                |   |   | 1 | 0 |   |   |   |   |   | 6                    |

| 4                |   |   |   |   | 0 |   |   |   |   | 4                    |

| 4                |   |   |   |   | 1 |   |   |   |   | 5                    |

| 5                |   |   |   |   |   | 1 |   |   |   | 5                    |

| 5                |   |   |   |   |   | 0 |   |   |   | 6                    |

| 6                |   |   |   |   |   |   |   | 0 | 0 | 6                    |

| 6                |   |   |   |   |   |   |   | 1 | 0 | 7                    |

| 6                |   |   |   |   |   |   |   |   | 1 | 8                    |

| 7                |   |   |   |   |   |   | 0 |   |   | 7                    |

| 7                |   |   |   |   |   |   | 1 |   |   | 8                    |

| 8                |   | 0 |   |   |   |   |   |   |   | 3                    |

| 8                |   | 1 |   |   |   |   |   |   |   | 1                    |

|                  |   |   |   |   |   |   |   |   |   |                      |

|                  |   |   |   |   |   |   |   |   |   |                      |

- a) Find vector(s) that allow the detection of a SA-1 and SA-0 fault on node F.

- SA-1: Cannot detect.

SA-0: ABCD { 001X, 111X } D is a don't care

b) Find vector(s) that allow the detection of a SA-1 and SA-0 fault on node G.

SA-1: ABCD {11XX } C & D are don't care

SA-0: ABCD { 1000, 101X, 011X }

c) Find vector(s) that allow the detection of a SA-1 and SA-0 fault on node H.

SA-1: ABCD { 0101, 0100, 0001, 1101 }

SA-0: ABCD { 011X, 10XX }

d) Find vector(s) that allow the detection of a SA-1 and SA-0 fault on node K.

SA-1: ABCD {011X }

SA-0: ABCD { 001X, 111X }

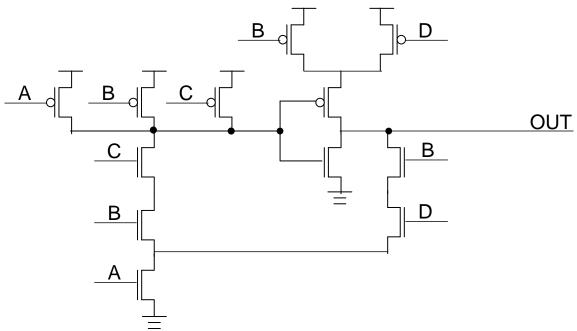

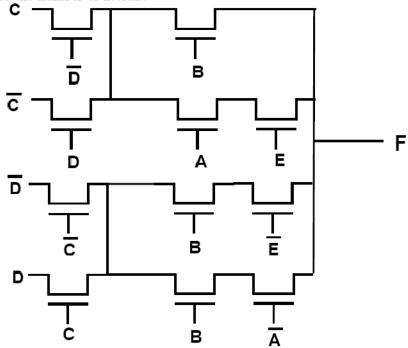

Write down the logic function implemented by the circuit below; use parantheses in the expression to reduce the number of literals.

F =

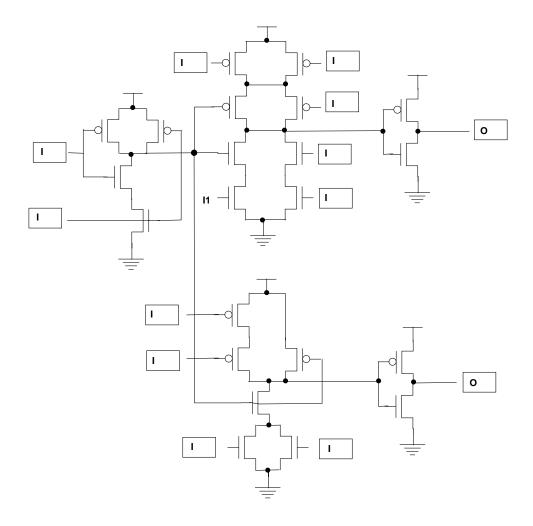

Find the largest as well as contimination delays for both 0-1 and 1-0 transitions for the circuit below. The widths of the transistors are given. Assume that a minimum width transistor will have an on-resistance of **R** and a gate capacitance of **C**; the source and drain capacitances are also C, and there is **no** sharing of diffusions. Give the input combinations which produce the respective delays (assuming that the internal nodes are charged or discharged as appropriate).

Input (ABCD) producing the largest rise delay:

$Largest\ rise\ delay=$

Input (ABCD) producing the largest fall delay:

Largest fall delay =

Input (ABCD) producing the smallest rise delay:

Contamination rise delay =

Input (ABCD) producing the smallest fall delay:

Contamination fall delay =

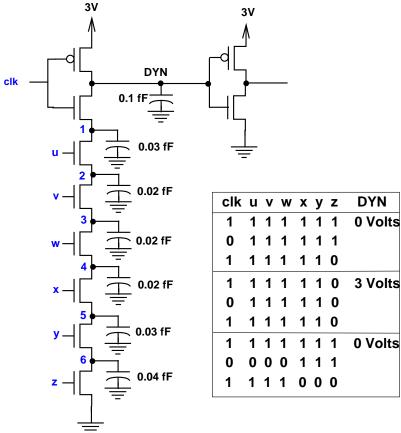

The domino circuit has the widths of the transistors shown next to them. Assume that a minimum width transistor has a gate capacitance of C, with the source and drain capacitances also each equal to C. Assume no sharing of diffusion.

(a) Under the worst-case input sequence, what is the largest voltage drop on the dynamic node, N?

(b) Give a sequence of inputs (ABCD) which will cause the voltage drop on N.

(c) How should the static inverter be sized to cause a voltage drop (noise) of at most 20% on the node N?

The best stage effort for a domino circuit has been found to be between 2.0 and 2.76 (for unfooted and footed blocks). The circuit below has the transistor widths labeled for the dynamic portion. The static inverter is a standard Hi-Skew with a logical effort of 5/6.

(a) If the stage effort is 2.5, what would be the corresponding path electrical effort, H (using the standard logical effort formulation)?

(b) What would be the delay of the circuit for the design in (a)?

(c) What would be the sizes of the P and N transistors in the static inverter (for the same design)?

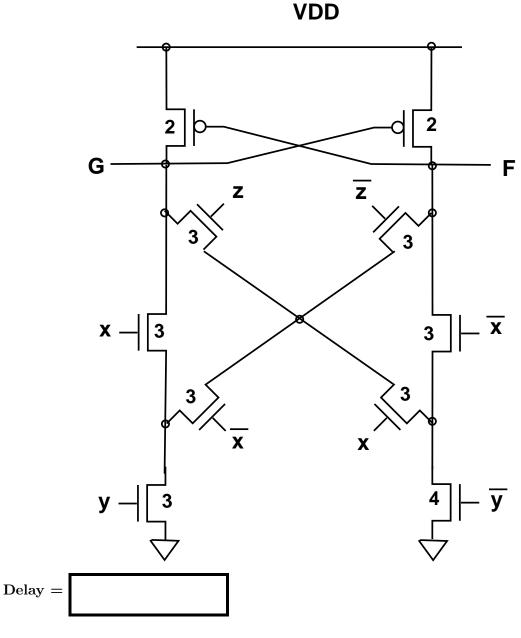

Consider the two different implementations of an AND gate below. Both have an input capacitance of C and both must drive a load six times the capacitance of each of the inputs.

(a) What is the path effort of each design?

(b) Which design will be the fastest? Explain.

(c) Compute the sizes of the logic gates,  ${\bf x}$  and  ${\bf y}$  to achieve the least delay.

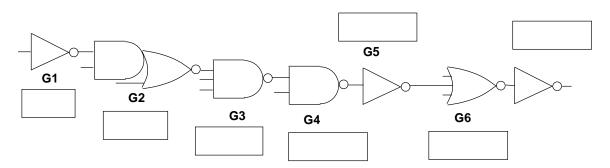

The inverters in the flip-flop below have rise and fall delays of 50 pS. The NAND gate has a rise delay of 100 pS and a fall delay of 150 pS.

Neglecting the delay of the nMOS transistors, what are the parameters of the flip-flop?

- (a) Setup time

- (b) Hold time

- (c) CLK-Q delay

The sequential circuit below has two flops and two combinational blocks, CB1 and CB2. The design is made using a library which includes inverters with a 25 pS rise and fall delay.

The parameters of the flops are:  $t_{pcq}=100pS, \quad t_{ccq}=20pS, \quad t_{setup}=50pS, \quad t_{hold}=100ps$

The parameters of the combinational block are as follows.

CB1:  $t_{pd} = 250pS, t_{cd} = 100pS$ CB2:  $t_{pd} = 350pS, t_{cd} = 50pS$

(a) Will the circuit work correctly? Explain and, if not, suggest a fix which will not affect the maximum frequency at which the circuit can be operated.

(b) If the circuit can be operated correctly, what is the maximum frequency at which it will work correctly?

(c) Suggest a modification to the clock circuitry to increase the frequency found in (b). Explain.

An embedded hardware accelerator in a system-on-chip is designed in a 1 V, 90 nm process, and has 1 million logic transistors with an average width of  $12\lambda$ . The gate capacitance,  $C_g = 2fF/\mu m$ . The gates have an activity factor of 0.2.

(a) What is the maximum clock frequency if the dynamic power should not exceed 20 mW?

(b) If the subthreshold leakage is  $20nA/\mu m$  and the gate leakage is  $2nA/\mu m$ , and if half the transistors are off (on average), what is the leakage power?

## 360R — Final

# Name:

- $\bullet$  Time = 180 mins, Max marks 111

- Closed book/notes; one crib sheet

- $\bullet$  Write your answers on the exam

- Show your work and give explanations

Figures are shown on separate pages at the end.

## Layout

The cross-sectional view of an inverter is given in Figure Cross-Section. Identify the various regions as being SiO2, Poly, Metal, VDD, Gnd, n+, p+, n-well, and p-substrate.

#### Transistor theory

Suppose you were to design an NMOS transistor in a  $0.5\mu m$  CMOS process. The transistor width is  $2.0\mu m$ , and length is  $0.5\mu m$ .

The manufacturing process could result in a 25% variation in the threshold voltage, a 20% variation in the oxide thickness, and a  $0.1\mu\mathrm{m}$  variation in the width and in the length, for the actual device that is fabricated.

Assume that  $V_{GS} = V_{DS} = 3V$ ; the threshold voltage is 0.5V.

What is the ratio of the maximum value of the drain current to the minimum value of the drain current that could flow through the fabricated device when it is in saturation?

#### Circuit families

1. What problem with dynamic logic does domino dynamic logic overcome, and what is the primary limitation of domino dynamic logic?

#### 5 marks

2. Give a transistor level schematic for a domino logic implementation of the function  $A \cdot B \cdot C \cdot D \cdot E \cdot F$ . No domino gate should have more than two inputs.

(You are not required to specify devices sizes, just draw the transistors and the connections between them.)

#### Datapath

The FF1 ("find-first-one") function takes an n-bit input vector A[n-1:0], and returns and n-bit output B[n-1:0], where B[i]=1 if and only if A[i]=1 and for all j>i, A[j]=0.

Describe how you would implement the "find-first-one" (FF1) function on n inputs using static gates, specifically 2-input NAND, 2 i/p NOR, and INVERTERs.

Credit will be given to efficient solutions.

#### Adders

Recall that a full-adder implements the following two logic equations:

$$C_{out} = A \cdot B + B \cdot C_{in} + A \cdot C_{in}$$

$S_{out} = A \oplus B \oplus C_{in}$

It is easy to show (e.g., by examining the truth table for these equations) that if the inputs to the full-adder are inverted, then so are the output. How can this fact be used to reduce the delay of a ripple-carry adder? Illustrate your reasoning on a 4-bit ripple carry adder.

## Delay Analysis

Consider the circuit shown in Figure Delay-Analysis. From the plot of  $V_{out}$  vs. time, estimate the effective resistance of the NMOS transistor. (Assume that all the capacitance seen on the output of the inverter is lumped into C.)

#### RAMs

1. Describe three **similarities** between SRAMs and DRAMs. What is the single biggest **difference** between an SRAM and DRAM? How do SRAMs and DRAMs **compare** in performance and in density?

2. Describe how you would use a 32 entry 8-bit word SRAM to implement a queue. Assume the queue read and writes are exclusive. Your queue has to signal whether it's full or empty. (You can use additional registers and logic.)

#### Test/Verification

1. How do scan flops help simplify the problem of manufacturing test?

#### 4 marks

2. Suppose you were designing a microprocessor.

One approach to functionally verifying the processor is to ignore the internal units (e.g., the cache, the ALU, the pipeline control logic, et.c), and simply write large sets of test programs, and run them on both the RTL and the golder reference model (typically written in C).

What are the two most significant benefits to verifying the internal units additionally?

4 marks

#### Deep Submicron

Suppose you were designing a chip in 45 nm technology, and you wanted to minimize power consumption.

The manufacturing process offers you two kinds of transistors—type F, which has a low  $V_T$  and a thin gate oxide, and type S, which has a high  $V_T$  and a thick gate oxide.

How do the type F and S transistors differ in terms of their power consumption and performance? How would you exploit them to reduce power in your design? (Be specific.)

9 marks

#### VLSI Design EXAM. I

J. Abraham October 16, 2006

Name: Student, no. 4

• Open Book, Open Notes.

Fall 2006

- Time Limit: 75 minutes (pace yourself).

- Check for 6 pages in exam.

- Write all your answers in the spaces/boxes provided.

- Show any calculations in these pages using the back of the pages if needed.

- State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 20  |        |

| 2       | 20  |        |

| 3       | 20  |        |

| 4       | 20  |        |

| 5       | 20  |        |

| TOTAL   | 100 |        |

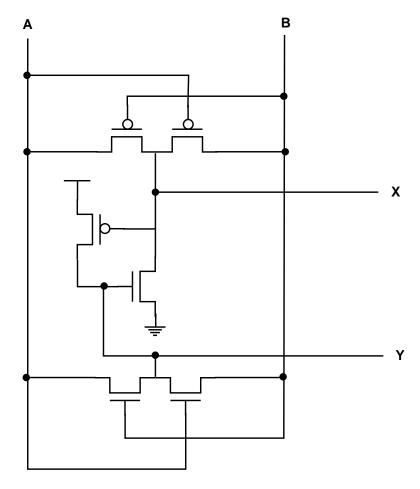

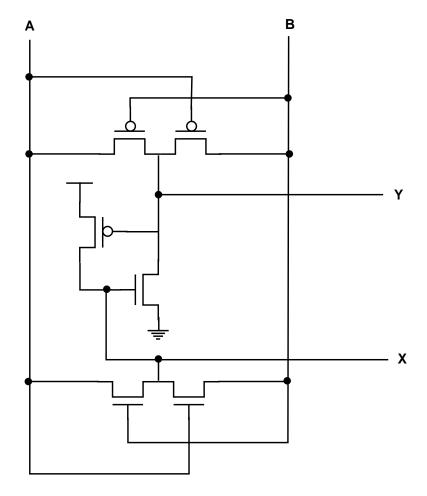

Find the functions  $\mathbf X$  and  $\mathbf Y$  implemented by the following circuit.

Write down the voltages at A, B, C, D, E, F, G in the following circuits, assuming that the initial voltage on each node is 1.5 volts. The relevant transistor parameters are,  $V_{dd}=3V,\ V_{tn}=0.5V$  and  $|V_{tp}|=0.7V$ .

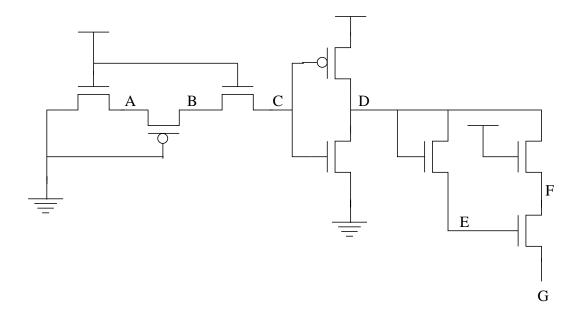

Use the Elmore delay approximation to find the *worst-case* rise and fall delays at output F for the following circuit. The gate sizes of the transistors are shown in the figure. Use the assumption that the diffusion capacitance is equal to the gate capacitance and that a minimum sized transistor has gate and diffusion capacitance equal to C. The resistance of a nMOS transistor with unit width is R and the resistance of a pMOS transistor with width of 2 is also R. Also assume NO sharing of diffusion regions.

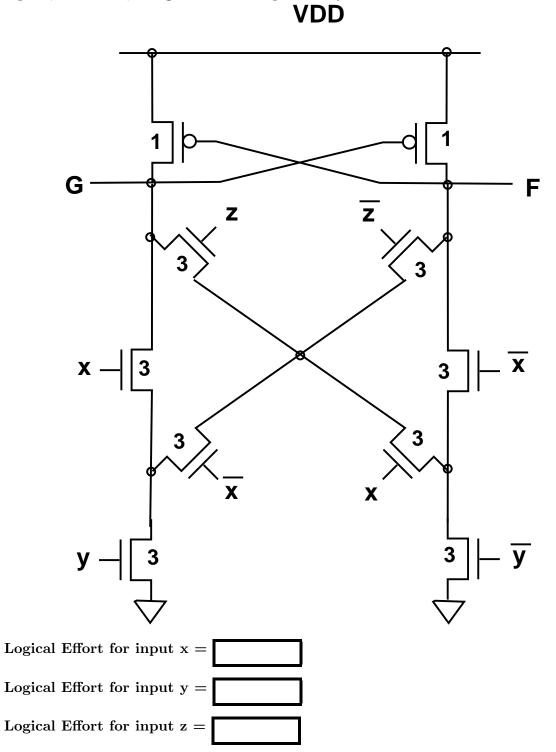

Find the logical efforts for the inputs, A, B, C, and D in the circuit below.

| Logical effort of $A =$ |  |

|-------------------------|--|

| Logical effort of $B =$ |  |

| Logical effort of $C =$ |  |

| Logical effort of $D =$ |  |

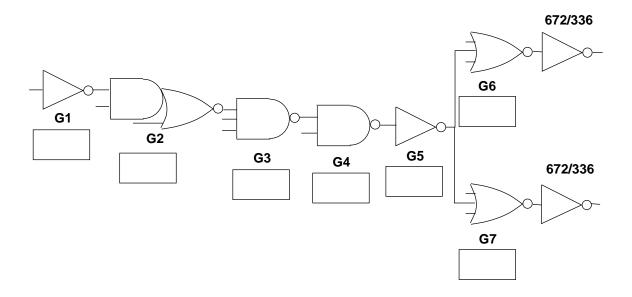

(a) Find the sizes of the P and N transistors in the gates below if the output capacitance  $C_L$  is 840 units.

(b) If a chain of n inverters, starting with a 2:1 inverter, is driving a load of  $3C_L$ , what is the input capacitance at each stage for the least delay?

(c) Would the input capacitance in (b) depend on the type of gate being used in each stage? Explain.

VLSI Design EXAM. II J. Abraham November 20, 2006

Name: Exam, No. 4

• Open Book, Open Notes.

• Time Limit: 75 minutes (pace yourself).

• Check for 6 pages in exam.

• Write all your answers in the spaces/boxes provided.

• Show any calculations in these pages using the back of the pages if needed.

• State clearly any assumptions made.

#### 1. (20 points)

Fall 2006

The inverters in the circuit below have minimum-sized transistors and the widths of the pass transistors are shown in the figure. Assume that the diffusion capacitance of a transistor is equal to its gate capacitance, and that a minimum sized transistor has gate and diffusion capacitance equal to C. In addition,  $V_{dd} = 2V$ ,  $V_{tn} = 0.3V$  and  $|V_{tp}| = 0.4V$ .

The sequence ABCD = (0011, 1001) is given as input to the circuit. Write down the voltage on node N just after the sequence is applied.

Voltage on Node N =

The components of the flip-flop below have the following rise/fall delays (in picoseconds).

Nand gate: 150/200

Transmission gate: 150/150

Inverter: 125/125

What are the values of the following flip-flop parameters (which a designer needs to use to calculate the performance of a system)?

| (a) | ${\bf Setup}$ | time = | ps |

|-----|---------------|--------|----|

|     |               |        | 1  |

(c) Clock-to-Q delay =

$$\boxed{}$$

ps

The flops used in the shift register below have a setup time of 100 ps, a maximum clock-Q delay of 150 ps, and a minimum clock-Q delay of 100 ps.

(a) How fast can this circuit be clocked?

(b) What is the limit on the hold time of the flops at this frequency?

| Hold time < | ps |

|-------------|----|

|             |    |

(c) What is the limit on the hold time of the flops at a frequency of 1 GHz?

| Hold time < |  | ps |

|-------------|--|----|

|-------------|--|----|

(d) What is the limit on the hold time of the flops if the circuit is clocked at a frequency of 100 MHz?

| ${\bf Hold\ time} <$ |  | ps |

|----------------------|--|----|

|----------------------|--|----|

(a) What is the highest frequency at which the following circuit can be operated correctly? The parameters of the components are as follows.

Inverter:  $t_{pd} = 200ps$ ,  $t_{cd} = 100ps$

**2-input** NOR:  $t_{pd} = 200ps$ ,  $t_{cd} = 150ps$

D-flop:  $t_{pd}=200ps$   $t_{cd}=0ps$ , Setup time = 300 ps, Hold time = 100 ps.

${\bf Maximum~Clock~frequency = \boxed{ \ \ \, } {\bf MHz} \\$

(b) If the two inverters are removed (the Q of the first flop is connected to the D of the second), what will be the highest frequency at which the circuit can be operated. Explain your answer.

$Maximum\ Clock\ frequency = \boxed{\hspace{1cm}MHz}$

(a) Write down all the paths from input B to the output and the worst-case and lowest delays for each path in the circuit below. The rise and fall times (in picoseconds) for each gate are shown over the gate symbol as risetime/falltime.

For example, the paths from input A to the output, and the delays are:

Path Worst-case delay Lowest delay ADFH 600 ps 500 ps

- (b) Give the test sequences for the following cases:

- (i) Rising input on B, path BDFH

(i) Falling input on B, path BEFH

(ii) Rising input on B, path BEFH

#### VLSI Design EXAM. I

J. Abraham October 16, 2006

Name: Student, no. 4

• Open Book, Open Notes.

Fall 2006

- Time Limit: 75 minutes (pace yourself).

- Check for 6 pages in exam.

- Write all your answers in the spaces/boxes provided.

- Show any calculations in these pages using the back of the pages if needed.

- State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 20  |        |

| 2       | 20  |        |

| 3       | 20  |        |

| 4       | 20  |        |

| 5       | 20  |        |

| TOTAL   | 100 |        |

Find the functions X and Y implemented by the following circuit and check the appropriate boxes.

Write down the voltages at A, B, C, D, E, F, G in the following circuits, assuming that the initial voltage on each node is 1.0 volts. The relevant transistor parameters are,  $V_{dd}=2V,\ V_{tn}=0.4V$  and  $|V_{tp}|=0.6V$ .

Use the Elmore delay approximation to find the worst-case rise and fall delays at output F for the following circuit. The gate sizes of the transistors are shown in the figure. Use the assumption that the diffusion capacitance is equal to the gate capacitance and that a minimum sized transistor has gate and diffusion capacitance equal to C. The resistance of a nMOS transistor with unit width is R and the resistance of a pMOS transistor with width of 2 is also R. Also assume NO sharing of diffusion regions.

Find the logical efforts for the inputs, A, B, C, and D in the circuit below.

| $   \text{Logical effort of B} = \left  \right  $ |  |

|---------------------------------------------------|--|

|                                                   |  |

| Logical effort of D =                             |  |

(a) Find the sizes of the P and N transistors in the gates below if the output capacitance  $C_L$  is 1043 units.

(b) If a chain of n inverters, starting with a 2:1 inverter, is driving a load of  $3C_L$ , what is the input capacitance at each stage for the least delay?

(c) Would the input capacitance in (b) depend on the type of gate being used in each stage? Explain.

VLSI Design EXAM. II J. Abraham November 20, 2006

Name: Exam, No. 3

- Open Book, Open Notes.

- Time Limit: 75 minutes (pace yourself).

- Check for 6 pages in exam.

- Write all your answers in the spaces/boxes provided.

- Show any calculations in these pages using the back of the pages if needed.

- State clearly any assumptions made.

#### 1. (20 points)

Fall 2006

The inverters in the circuit below have minimum-sized transistors and the widths of the pass transistors are shown in the figure. Assume that the diffusion capacitance of a transistor is equal to its gate capacitance, and that a minimum sized transistor has gate and diffusion capacitance equal to C. In addition,  $V_{dd} = 2V$ ,  $V_{tn} = 0.3V$  and  $|V_{tp}| = 0.4V$ .

The sequence ABCD = (0011, 1001) is given as input to the circuit. Write down the voltage on node N just after the sequence is applied.

Voltage on Node N =

The components of the flip-flop below have the following rise/fall delays (in picoseconds).

Nand gate: 125/175

Transmission gate: 125/125

Inverter: 100/100

What are the values of the following flip-flop parameters (which a designer needs to use to calculate the performance of a system)?

| (a) | ${\bf Setup}$ | time = | ps |

|-----|---------------|--------|----|

|     |               |        | 1  |

(c) Clock-to-Q delay =

$$\boxed{}$$

ps

The flops used in the shift register below have a setup time of 100 ps, a maximum clock-Q delay of 150 ps, and a minimum clock-Q delay of 100 ps.

(a) How fast can this circuit be clocked?

(b) What is the limit on the hold time of the flops at this frequency?

| Hold time < | ps |

|-------------|----|

|             |    |

(c) What is the limit on the hold time of the flops at a frequency of 1 GHz?

| Hold time < |  | ps |

|-------------|--|----|

|-------------|--|----|

(d) What is the limit on the hold time of the flops if the circuit is clocked at a frequency of 100 MHz?

| ${\bf Hold\ time} <$ |  | ps |

|----------------------|--|----|

|----------------------|--|----|

(a) What is the highest frequency at which the following circuit can be operated correctly? The parameters of the components are as follows.

Inverter:  $t_{pd} = 200ps$ ,  $t_{cd} = 100ps$

**2-input** NOR:  $t_{pd} = 200ps$ ,  $t_{cd} = 150ps$

D-flop:  $t_{pd}=200ps$   $t_{cd}=0ps$ , Setup time = 300 ps, Hold time = 100 ps.

${\bf Maximum~Clock~frequency = \boxed{ \ \ \, } {\bf MHz} \\$

(b) If the two inverters are removed (the Q of the first flop is connected to the D of the second), what will be the highest frequency at which the circuit can be operated. Explain your answer.

$Maximum\ Clock\ frequency = \boxed{\hspace{1cm}MHz}$

(a) Write down all the paths from input B to the output and the worst-case and lowest delays for each path in the circuit below. The rise and fall times (in picoseconds) for each gate are shown over the gate symbol as risetime/falltime.

For example, the paths from input A to the output, and the delays are:

Path Worst-case delay Lowest delay ADFH 600 ps 500 ps

- (b) Give the test sequences for the following cases:

- (i) Rising input on B, path BDFH

(i) Falling input on B, path BEFH

(ii) Rising input on B, path BEFH

| Name: |  |

|-------|--|

|       |  |

Open Book, Open Notes. Time Limit: 1 hour, 15 minutes (pace yourself). Check for 5 pages in exam.

Write your work and all your answers in these pages. Use the back of the pages for scratch work if needed. State clearly any assumptions made.

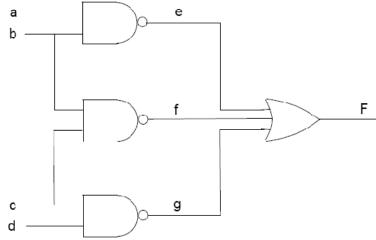

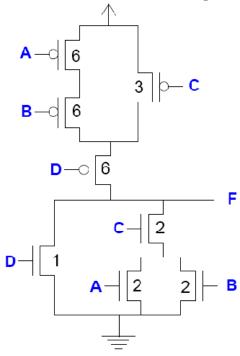

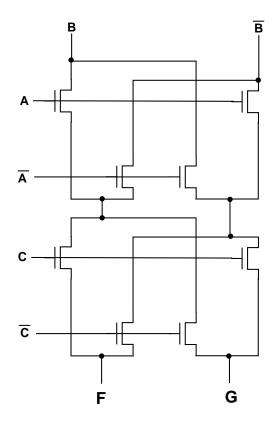

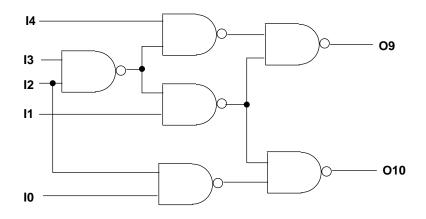

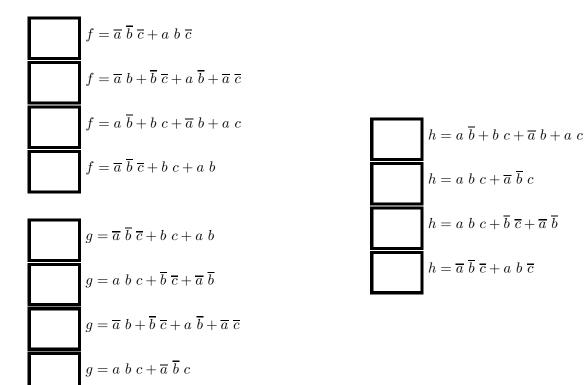

1. (20 points) Write down the functions, F and G, implemented by the circuits below.

(a)

(b)

(a) The following circuit is supposed to implement the function  $Y=abc+\overline{a}\overline{b}c+\overline{a}b\overline{c}+a\overline{b}\overline{c}$

Label the inputs in the figure below so that the circuit correctly implements the function.

(b) The CMOS network below was supposed to implement the function  $F = A \oplus B$ . Point out the mistake in the design, and correct it **without increasing the delay**.

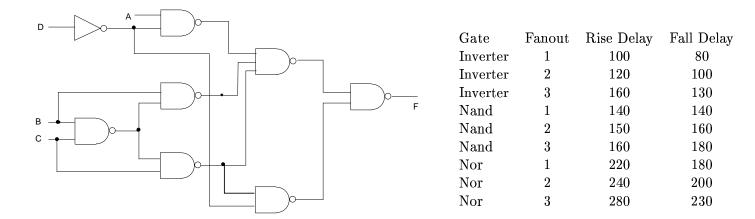

A circuit and the parameters of its library cells are given below.

Find the longest **functional paths** from inputs B and D to F. Write down the logic values on in inputs which will propagate a transition through the longest paths, and give the rise and fall delays for the paths.

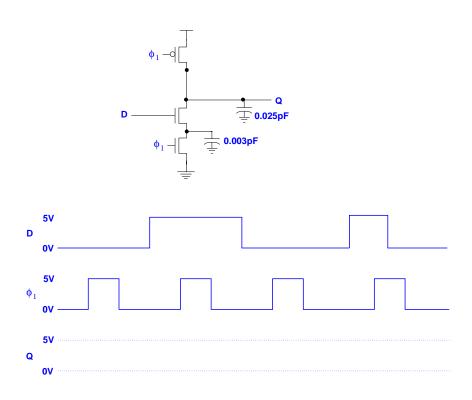

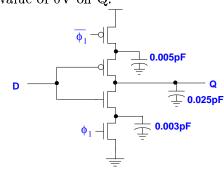

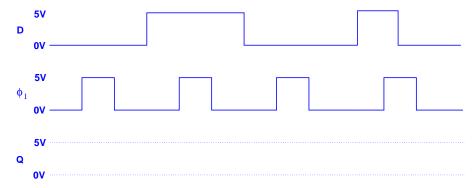

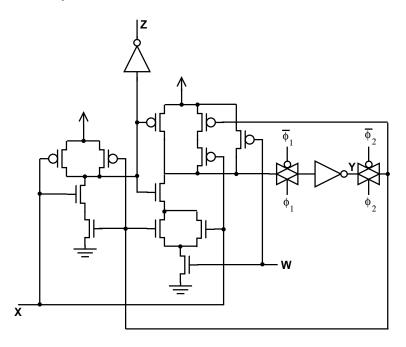

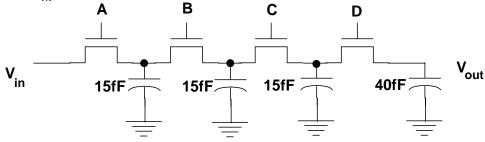

Draw the waveform at the output Q in the circuit below, in response to the input and clock waveform shown. Indicate the approximate value of the voltage at the transitions of  $\phi_1$  whenever it changes significantly. The TOTAL capacitance at the nodes, including drain and parasitic capacitances, is indicated in the figures.

## (b) Assume an initial value of 0V on Q.

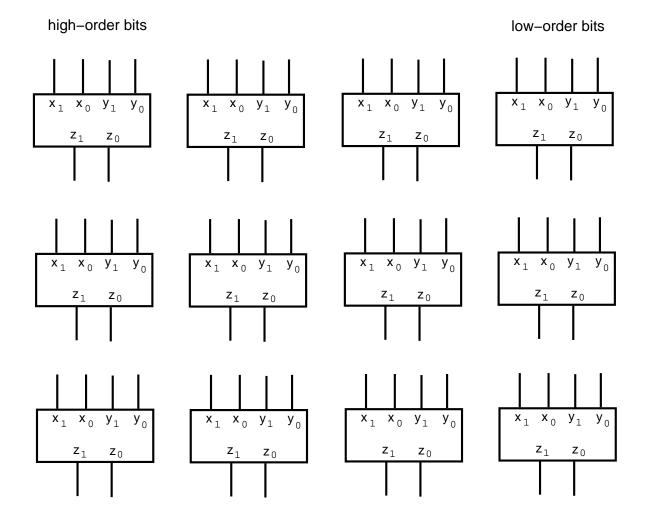

A 2-bit comparator cell which takes inputs  $X = x_1x_0$  and  $Y = y_1y_0$ , and produces a 2-bit result Z can be specified as follows:

$$X > Y, Z = 10$$

$$X < Y, Z = 01$$

$$X = Y$$

,  $Z = 00$  or 11.

If each cell has some fixed delay, show how the cells may be interconnected to compare two 8-bit numbers with three cell delays (you should use ONLY the cells, and do not need to use all of them).

EE82M Fall 2002 VLSI I EXAM. I J. Abraham October 14, 2002

Name: EXAM, No. 1

Open Book, Open Notes. Time Limit: 50 minutes (pace yourself). Check for 6 pages in exam.

Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 15  |        |

| 2       | 20  |        |

| 3       | 20  |        |

| 4       | 20  |        |

| 5       | 25  |        |

| TOTAL   | 100 |        |

# 1. (15 points)

Label the inputs of the static CMOS circuit below so that it implements the following function:

$$Z = \overline{ac + a\overline{c}bd + f + aef}$$

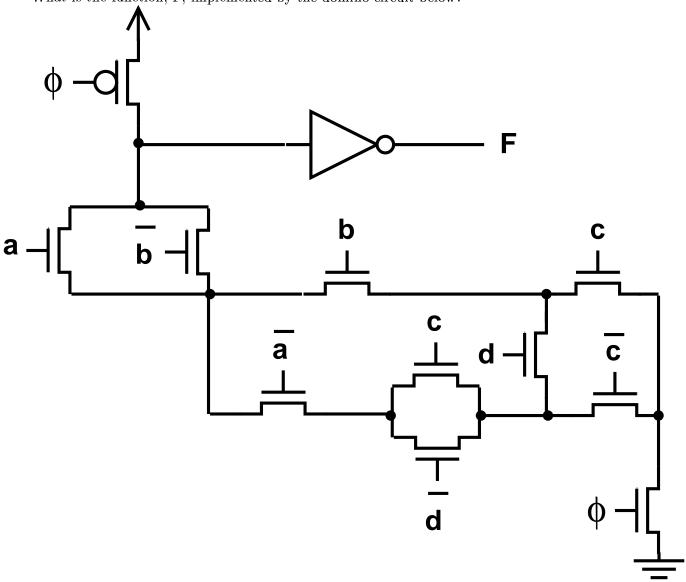

What is the function, F, implemented by the domino circuit below?

$$F = a \ b \ (c+d) + \overline{a} \ \overline{b} \ \overline{(c \oplus d)}$$

$$F = b \ (c+d) + \overline{a} \ \overline{(c \oplus d)}$$

$$F = b \ c \ (a+d) + \overline{b} \ \overline{c} \ \overline{(a \oplus d)}$$

$$F = b \ (a+d) + \overline{c} \ \overline{(a \oplus d)}$$

$$F = a \ d \ (b+c) + \overline{a} \ \overline{d} \ \overline{(b \oplus c)}$$

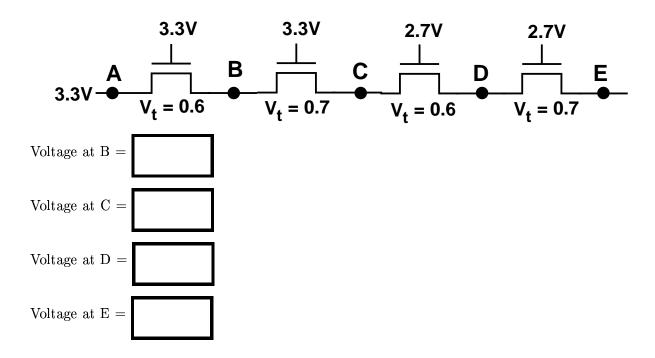

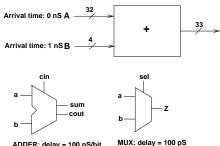

Write down the voltages at the nodes B, C, D and E in the circuit below, given the voltages at A and the gate inputs of the transistors. Each transistor is labeled with its  $V_t$  value.

In the circuit below,  $V_{DD}$  is 3 Volts, and  $V_{tn}$  is 0.25 Volts.

Initially,  $V_{out} = 0$ , and A is logic 1 (at  $V_{DD}$ ).

Find the value of  $V_{out}$  after A becomes logic 0.

$$V_{out} =$$

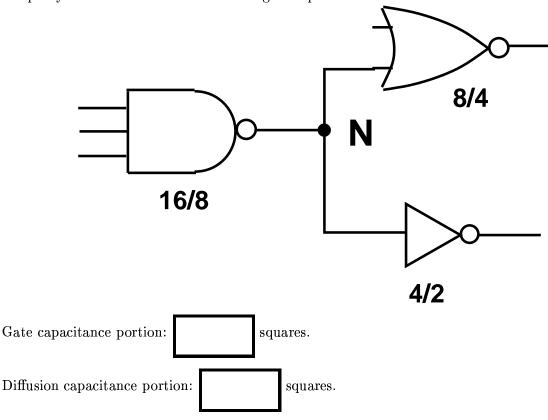

Find the capacitance (gate and diffusion) at the node N in the circuit below, implemented in static CMOS technology, in terms of unit squares of gate capacitance.

Each transistor in the circuit has minimum length (of 1 unit), and each gate is labeled with the widths of the P and N transistors (P width/N width), in units of the minimum length. (For example, a gate labeled 16/8 would have P-channel transistors with a width of 16 units and the N-channel transistors would have a width of 8 units.)

Each diffusion area extends 2 units from the polysilicon. The diffusion capacitance has the following characteristics:

Area: 1 square of diffusion = 0.25 unit gate capacitance

Periphery: 1 unit of diffusion = 0.1 unit gate capacitance.

Name: STUDENT1, GRAD1

Open Book, Open Notes. Time Limit: 75 minutes (pace yourself). Check for 7 pages in exam.

Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 15  |        |

| 2       | 15  |        |

| 3       | 15  |        |

| 4       | 20  |        |

| 5       | 20  |        |

| 6       | 15  |        |

| TOTAL   | 100 |        |

#### 1. (15 points)

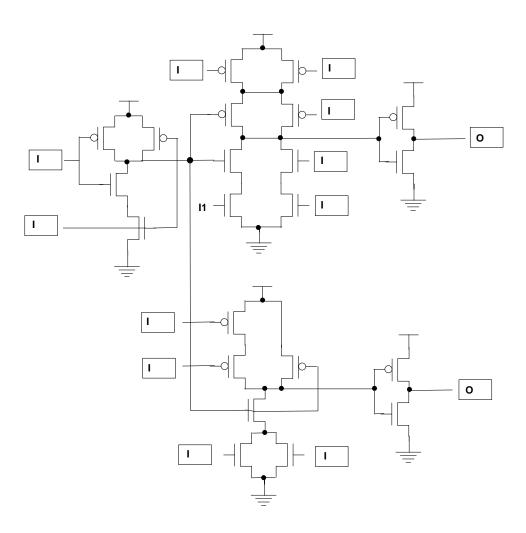

Find the functions F and G implemented by the following circuit and check the appropriate boxes.

$$F = \overline{A} \overline{B} C + A \overline{B} \overline{C} + \overline{A} B \overline{C} + \overline{A} \overline{B} \overline{C}$$

$$F = \overline{A} \overline{B} C + \overline{A} B \overline{C} + A \overline{B} \overline{C} + A B C$$

$$F = \overline{A} \overline{B} \overline{C} + A \overline{B} C + \overline{A} B C + A B \overline{C}$$

$$F = A B \overline{C} + \overline{A} B C + A \overline{B} C + A B C$$

$$G = \overline{A} \ \overline{B} \ C + A \ \overline{B} \ \overline{C} + \overline{A} \ B \ \overline{C} + \overline{A} \ \overline{B} \ \overline{C}$$

$$G = \overline{A} \ \overline{B} \ C + \overline{A} \ B \ \overline{C} + A \ \overline{B} \ \overline{C} + A \ B \ C$$

$$G = \overline{A} \ \overline{B} \ \overline{C} + A \ \overline{B} \ C + \overline{A} \ B \ C + A \ B \ \overline{C}$$

$$G = A B \overline{C} + \overline{A} B C + A \overline{B} C + A B C$$

| 2. (15 points | <b>2</b> . | (15) | points | ) |

|---------------|------------|------|--------|---|

|---------------|------------|------|--------|---|

| A                   | design   | decis        | sion  | was   | $\mathbf{made}$ | to   | change    | the  | $V_T$ | of   | the                    | PMOS        | trans  | sistor         | in  | an   | inver | $	ext{ter.}$ | The |

|---------------------|----------|--------------|-------|-------|-----------------|------|-----------|------|-------|------|------------------------|-------------|--------|----------------|-----|------|-------|--------------|-----|

| $\operatorname{tr}$ | ansistor | has          | a thi | resho | old vol         | ltag | e of -0.4 | 4V w | vith  | zero | su                     | bstrate     | bias,  | and            | its | γ is | -0.4. | Find         | the |

| su                  | bstrate  | $_{ m bias}$ | whic  | ch wi | ill cha         | nge  | the $V_T$ | to - | 0.50  | V. ( | $(\mathrm{Us}\epsilon$ | $2\Phi_F =$ | = 0.6V | <sup>7</sup> ) |     |      |       |              |     |

| Substrate Bias $=$ |  |

|--------------------|--|

|                    |  |

## 3. (15 points)

Size the following gate such that it has the same drive strength as inverter that has a PW=3 and NW=2.

(PW, NW are the widths of the PMOS and NMOS transistors, respectively.)

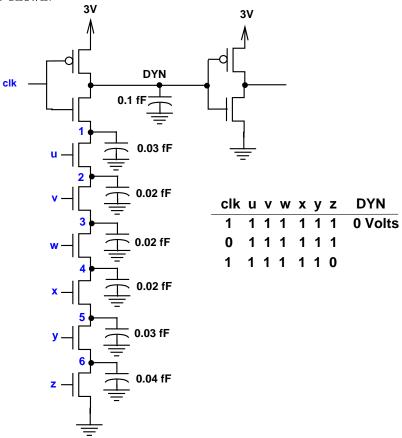

The n-channel transistors in the following portion of a CMOS circuit have an on-resistance of 5  $K\Omega$ . The total source and drain (diffusion) capacitances of an n-channel transistor are 5 fF each. The parasitic (wiring, etc.) capacitances are shown lumped at the internal nodes. The output load capacitance includes the diffusion capacitance of the P-Network, wiring capacitances, and the output load capacitances.

(a) Assume that all load and internal capacitances have been charged to  $V_{DD}$ . Which of the following input vectors will result in the longest  $t_{pHL}$ ?

ABCDE = 00111

ABCDE = 10111

ABCDE = 11000

ABCDE = 11111

ABCDE = 01111

(b) Assuming all the capacitors are initially charged to  $V_{DD}$ , use the Elmore delay approximation to find the value of  $t_{pHL}$  for the input vector ABCDE = 01111.

$t_{pHL} =$

Calculate the voltages on the node  $\mathbf{DYN}$  in the circuit below under the initial condition and input **sequence** shown.

The following drawing shows part of a domino CMOS design. Draw the NMOS network which will realize the following function F using only 5 N-channel transistors.

$$F = A \cdot B + A \cdot C \cdot E + D \cdot E + B \cdot C \cdot D$$

EE360R/EE382M Spring 2002

# Introduction to VLSI Design Exam. I

J. A. Abraham, R. S. Tupuri February 28, 2002

| Name: |  |

|-------|--|

|       |  |

|       |  |

Open Book, Open Notes. Time Limit: 1 hour, 15 minutes (pace yourself). Check for 5 pages in exam.

Write your work and all your answers in these pages. Use the back of the pages for scratch work if needed. State clearly any assumptions made.

1. (20 points) Label the inputs of the circuit below so that it implements the function

$$F = a \cdot (b \cdot c + \overline{b} \cdot \overline{c})$$

Implement the following function, F, using static CMOS logic with the minimum number of transistors.

$$F = \overline{(a+b+c)\cdot d\cdot (\overline{a\cdot b})}$$

Implement the following functions using a single logic network with the minimum number of transistors.

$$F_1 = a \cdot \overline{b} \cdot d$$

$$F_2 = a \cdot \overline{b} \cdot \overline{c} \cdot d + (\overline{a} + b + \overline{d}) \cdot c$$

Four n-channel transistors in a pass transistor chain are shown below. The input voltage,  $V_{in}$  is set to 3 Volts, and  $V_{tn}$  is 0.25 Volts.

Initially,  $V_{out}$  is 0 Volts, and ABCD = 1110.

Then, the inputs are switched to ABCD = 0011.

Find the final value of  $V_{out}$ .

The n-channel transistors in the following portion of a domino circuit have an on-resistance of 5  $K\Omega$ . The source/drain capacitance of an n-channel transistor is 5 fF, and that of the p-channel transistor is 10 fF. The parasitic and output load capacitances are shown lumped at the nodes.

(a) Identify the input combination for the the worst-case fall time, and estimate it using the Penfield-Rubenstein approach.

(b) What is the input combination for the best-case fall time, and it's estimated value?

# VLSI Design

J. Abraham EXAM. I March 2, 2005

| #005 |       | Class (382M/360R): |

|------|-------|--------------------|

|      |       |                    |

|      | Name: |                    |

Open Book, Open Notes. Time Limit: 75 minutes (pace yourself). Check for 7 pages in exam. Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 15  |        |

| 2       | 15  |        |

| 3       | 15  |        |

| 4       | 20  |        |

| 5       | 20  |        |

| TOTAL   | 100 |        |

Spring 2005

Find the function F implemented by the following circuit and check the appropriate box.

$$F = \overline{A} + \overline{B} C + B \overline{C}$$

$$F = \overline{A} + B C + \overline{B} \overline{C}$$

$$F = A + \overline{B} C + B \overline{C}$$

$$F = \overline{B} + A C + \overline{A} \overline{C}$$

$$F = B + A C + \overline{A} \overline{C}$$

$$F = \overline{C} + A B + \overline{A} \overline{B}$$

$$F = C + A B + \overline{A} \overline{B}$$

$$F = A + B \ C + \overline{B} \ \overline{C}$$

The gate level circuit below has been implemented with the transistor netlist at the bottom. Label the transistor gate inputs and the circuit outputs so that the gate level circuit is correctly implemented by the transistor circuit.

Calculate the ratio of maximum delay to minimum delay for NAND gates of various inputs, for the case where the gates are not driving any load and fill in the table below. Assume that the unit gate capacitance is the same as the unit diffusion capacitance, and that diffusion is shared in the nMOS stack, but NOT in the pMOS network.

Include all the capacitances seen on the output node.

For the minimum delay for the output falling, assume that the latest arriving signal is connected closest to the output, and that the earlier signals have discharged their respective capacitors.

Perform the calculation for NAND gates which are sized so that the equivalent inverter is 2:1.

|                  | 2-input | 3-input | 4-input |

|------------------|---------|---------|---------|

| Output $0 \to 1$ |         |         |         |

| Output $1 \to 0$ |         |         |         |

(a) Calculate the logical effort of the a, b and c inputs of the following AND-OR-INVERT (AOI) gate.

(b) Compute the delays of the following paths (from each input to output (before the load)) using logical effort. The load inverter is ten times bigger than the input inverters. The parasitic delay of the AOI gate is 3, that of a NAND gate is 2 and that of an inverter is 1. Show your work.

Calculate the Elmore delay from C to F in the circuit below. The widths of the pass transistors are shown, and the inverters have minimum-sized transistors. Assume that the diffusion capacitance of a transistor is equal to its gate capacitance, and that a minimum sized transistor has gate and diffusion capacitance equal to C.

EE360R/EE382M Fall 2001

# Introduction to VLSI Design Exam. II

J. A. Abraham, R. S. Tupuri November 8, 2001

| Name: |  |

|-------|--|

|       |  |

Open Book, Open Notes. Time Limit: 1 hour, 15 minutes (pace yourself). Check for 5 pages in exam.

Write your work and all your answers in these pages. Use the back of the pages for scratch work if needed. State clearly any assumptions made.

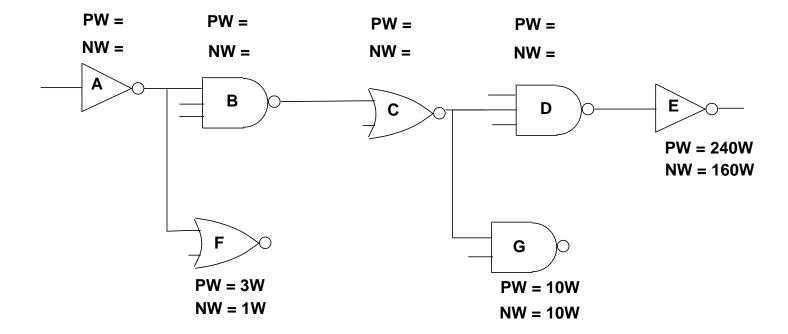

1. (25 points) Size the following path (A, B, C, D) using a 2:1 P:N ratio and a stage ratio of 3. Indicate the size of P and N transistors in the gates A, B, C and D.

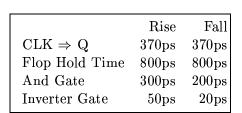

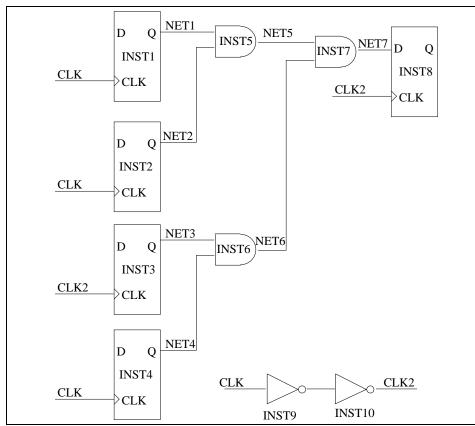

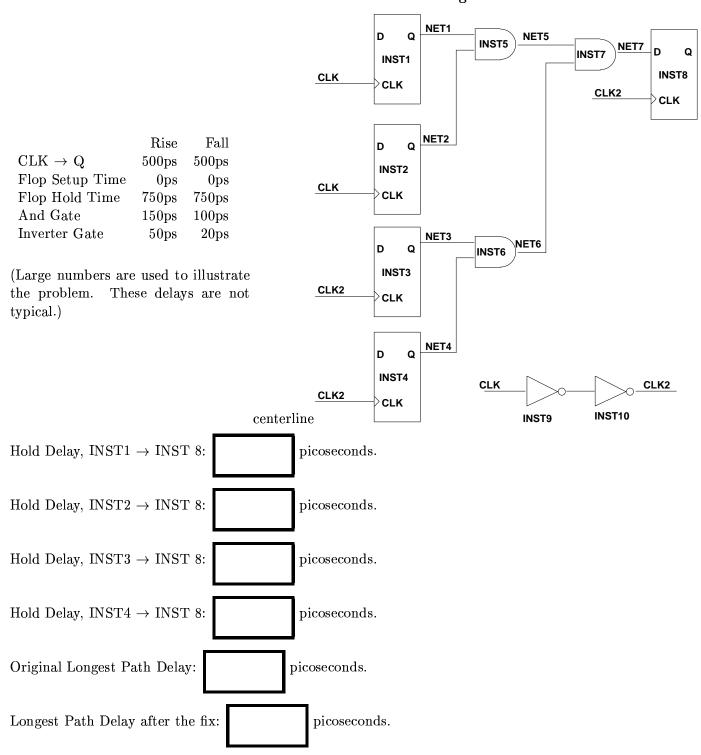

Identify if there are any hold time problems from the source flops (INST1, INST2, INST3 and INST4) to INST8 in the following circuit. If there are any, indicate by how much the hold time is violated and suggest a fix. Use the delays from the table below. Do not insert additional delays for the paths that have no hold violations.

In the static CMOS circuit below, the on-resistance of each n-channel transistor is 5 KOhms and that of a p-channel transistor is 10 KOhms. The gate capacitance of an n-channel transistor is 0.02pF and p-channel transistor is 0.03pF. The source/drain capacitance of an n-channel transistor is 0.001pF and for a p-channel transistor is 0.002pF. The routing capacitances for interconnections are lumped at the nodes as shown.

- (a) A faulty circuit (after manufacture) has a "slow to fall" fault due to the n-channel transistor with input **a** having an abnormally high on-resistance of 50 kOhms. Find a test for the fault.

- (b) Using the Penfield-Rubenstein technique, find the fall delay for the circuit without a fault, as well as that of the faulty circuit.

Delay of circuit without fault =

Delay of faulty circuit =

(a) The circuit below has two inputs, W and X, and one output Z. It has two states, implemented by the state variable Y. Complete the State Diagram for the circuit, labeling the arcs as indicated with the appropriate binary values of W, X and Z.

(b) What does the circuit do?

EE382M Fall 2002 VLSI I EXAM. II J. Abraham November 25, 2002

Name: STUDENT, GRADUATE

Open Book, Open Notes. Time Limit: 75 minutes (pace yourself). Check for 7 pages in exam.

Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 15  |        |

| 2       | 10  |        |

| 3       | 20  |        |

| 4       | 20  |        |

| 5       | 15  |        |

| 6       | 20  |        |

| TOTAL   | 100 |        |

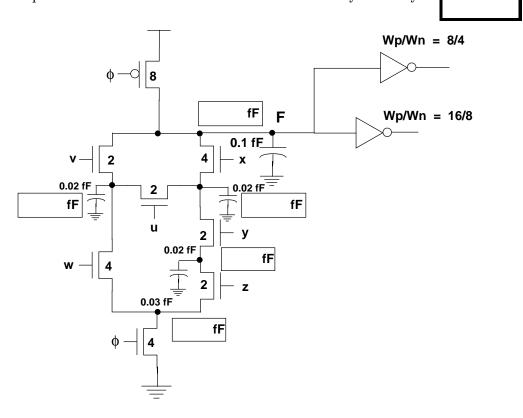

Using the Penfield-Rubenstein approach, find the **worst-case** time for the output of the following domino-CMOS gate to fall from 1 to 0 (when the clock  $\phi$  goes from 0 to 1). The widths of the n-channel transistors in the domino circuit as well as the widths of the N- and P-channel transistors in the inverters are indicated in the figure. The parasitic capacitances are lumped at each node as shown. Use the following technology parameters:

On-resistance of n-channel transistor: 1000  $\Omega/\Box$

Gate capacitance: 0.3 femtoFarads/ $\square$

Approximate the diffusion capacitance (including area and periphery) as 0.25 femto-

Farads/unit gate width

Write down the total capacitance at each node (in the box provided).

What are the input values which will result in the worst-case delay? uvwxy =

Total (max.) fall time: picoseconds.

Size the following gate such that it has the same drive strength as inverter that has a PW=3 and NW=2.

Size the following transistors using a 3:2 P:N ratio and a stage ratio of 4. Indicate the sizes of the P and N transistors in gates A, B, C and D. In the case where the result is a fraction, round up (i.e., 3.2, 3.5 and 3.7 all round up to 4). Note that rounding needs to be done only when you determine PW and NW, and not in the middle of the calculation.

Identify if there are any hold time problems from the source flops (INST1, INST2, INST3 and INST4) to INST8 in the following circuit. If there are any, indicate by how much the hold time is violated and suggest a fix. Use the delays from the table below. Do not insert additional delays in the paths that have no hold violations. Identify the longest path delay before and after fixing the hold time violations. **Draw the fix with the lowest cost on the figure.**

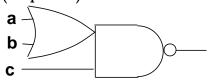

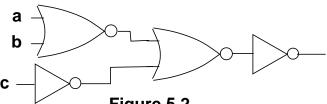

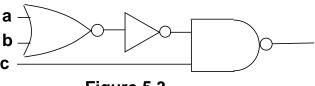

Figure 5.1

Figure 5.2

Figure 5.3

1 INV

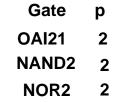

- (a) Find the logical effort of the OAI21 gate inputs in Figure 5.1.

- (b) Find the delays from a and c to y for all the three circuits above.

- (c) Which of the above circuits do you recommend if the latest arriving signal is connected to

The a input

The b input

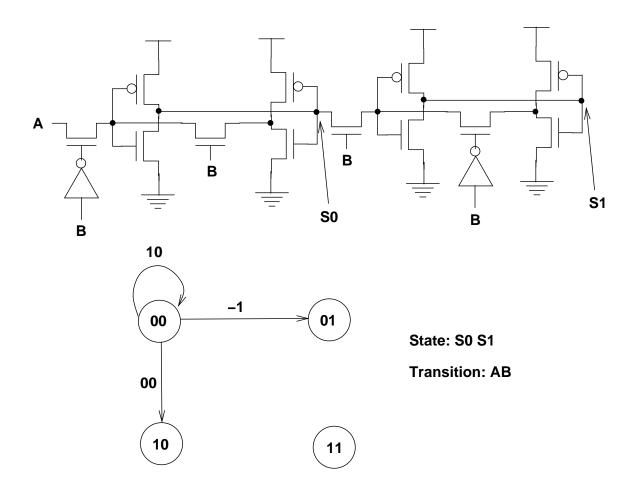

Complete the state transition diagram for the circuit below ("-" represents a "don't-care").

EE360R Fall 2003

# Computer-Aided IC Design EXAM. II

J. Abraham November 11, 2003

| Name: | Student, | $\mathbf{B}$ |

|-------|----------|--------------|

|-------|----------|--------------|

| Signature:                               |  |

|------------------------------------------|--|

| ~ 1 5 11 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 |  |

Open Book, Open Notes. Time Limit: 90 minutes (pace yourself). Check for 6 pages in exam. Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made. You will not receive partial credit if you don't show your steps toward the solution.

| PROBLEM | MAX | POINTS |

|---------|-----|--------|

| 1       | 20  |        |

| 2       | 15  |        |

| 3       | 20  |        |

| 4       | 20  |        |

| 5       | 25  |        |

| TOTAL   | 100 |        |

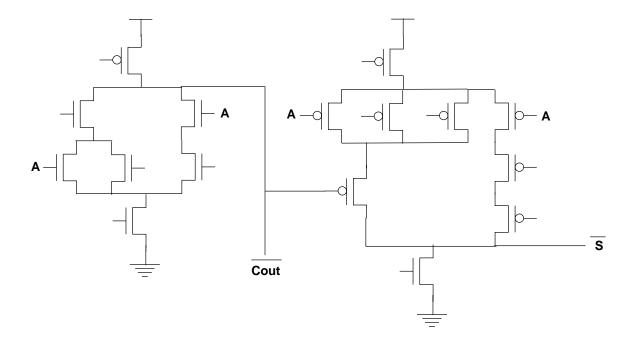

The dynamic circuit below is designed to take inputs A, B and C, and produce the complement of the sum  $(\overline{S})$  and Carry out  $(\overline{C_{out}})$  signals for a full adder.

Label the appropriate lines with the signals A, B, C, and the clocks,  $\phi$  and  $\overline{\phi}$ , as appropriate, so that the circuit will perform the function of a full adder.

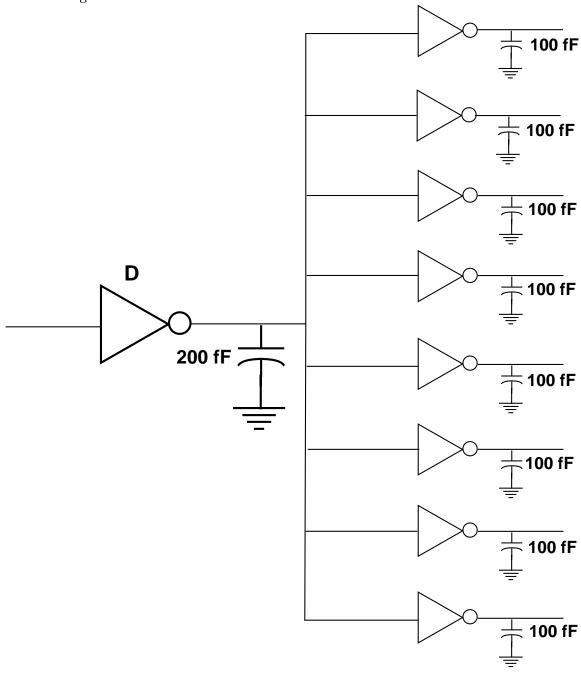

The circuit below is implemented in a 0.18  $\mu$  technology with a power supply of 2 Volts. All inverters have the P- and N-channel transistors sized so that the on-resistances are identical. The transistors comprising the inverter labeled D have on-resistances of 50  $\Omega/\Box$ , and the transistors for the other inverters have on-resistances of 100  $\Omega/\Box$ . The total capacitance of each of the nets is labeled in the figure.

What is the power consumed in this circuit when operating at 750 MHz?

Size the following paths using:

Stage ratio =

$$3$$

P:N =  $2:1$

Stay as close as possible to the above ratios.

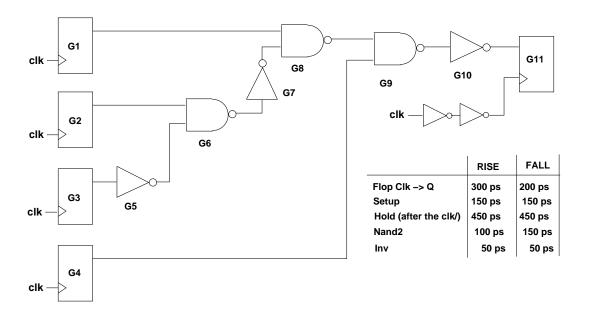

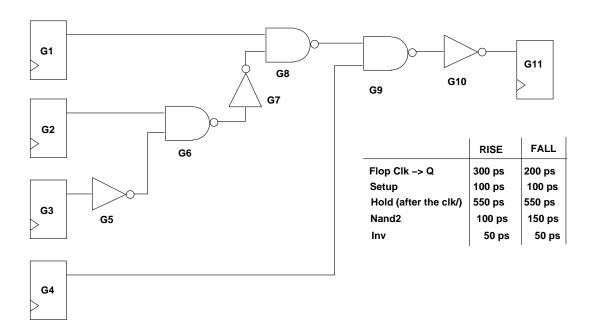

The flip-flop in the figure below has the delays of the various components labeled (delay of the NAND gate is G1, etc.) Find the approximate setup time, hold time and clock-to-QB delay in terms of the delays of the basic gates and inverters (example, delay = G1 + I2). Use the single value of delay (I3 and I4) for the dynamic and clocked inverters shown at the transistor level.

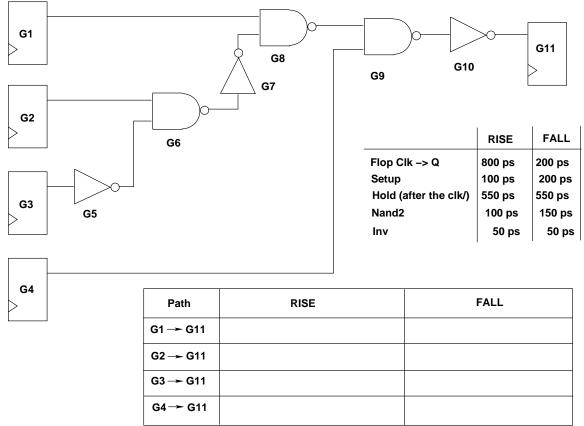

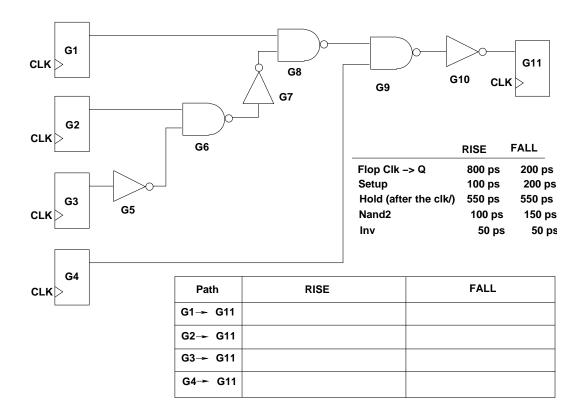

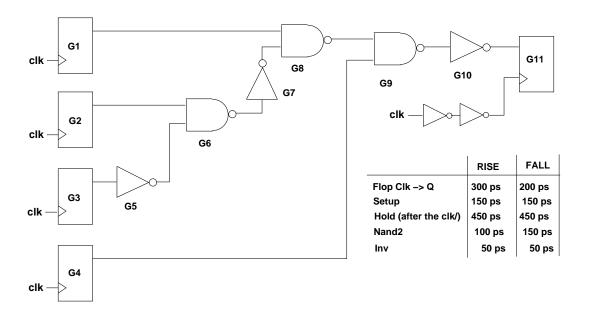

Identify if there are any hold time problems from the source flops (G1, G2, G3 and G4) to G11 in the following circuit. Sum the delays along the paths and show the amount of the violation under "Fail" (a negative number indicates that there is no hold-time violation.

Use the delays from the table below.

If there is any violation, show the fix on the circuit below (by using chains of inverters in the appropriate path). The additional inverters should impact as little of the circuit delay as possible.

| Path     | RISE at G11 input | Fail? | FALL at G11 input | Fail? |

|----------|-------------------|-------|-------------------|-------|

| G1 → G11 |                   |       |                   |       |

| G2 → G11 |                   |       |                   |       |

| G3 → G11 |                   |       |                   |       |

| G4→ G11  |                   |       |                   |       |

What is the maximum frequency of operation after fixing any hold-time violation?

MHz

EE360R/EE382M Spring 2002

# Introduction to VLSI Design Exam. II

J. A. Abraham, R. S. Tupuri April 18, 2002

Open Book, Open Notes. Time Limit: 1 hour, 15 minutes (pace yourself). Check for 6 pages in exam.

Write your work and all your answers in the boxes provided for them. Use the back of the pages for scratch work if needed. State clearly any assumptions made.

### 1. (20 points)

(a) Size the following complex gate so that it has the drive strength of an equivalent inverter with PW = 3 and NW = 2.

# (b) Size the following paths using:

Stage ratio = 4 P:N = 2:1

Stay as close as possible to the above ratios.

Frequency =

(a) Identify if there are any hold time problems from the source flops (G1, G2, G3 and G4) to G11 in the following circuit. If there are any, indicate by how much the hold time is violated and suggest a fix. Use the delays from the table below.

What is the maximum frequency of operation after fixing any hold-time violation?

MHz

MHz

The gate level circuit below has been partially implemented with the transistor netlist at the bottom. Label the transistor gate inputs and the circuit outputs so that the gate level circuit is correctly implemented.

(a) Calculate the logical effort of the a, b and c inputs of the following AND-OR-INVERT (AOI) gate.

(b) Compute the delays of the following paths (from each input to output (before the load)) using logical effort. The load inverter is ten times bigger than the input inverters. The parasitic delay of the AOI gate is 3, that of a NAND gate is 2 and that of an inverter is 1.

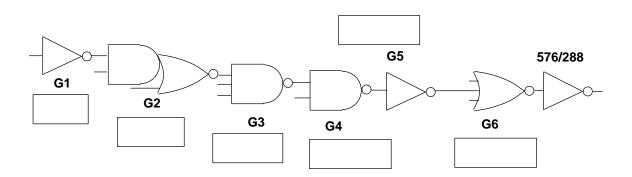

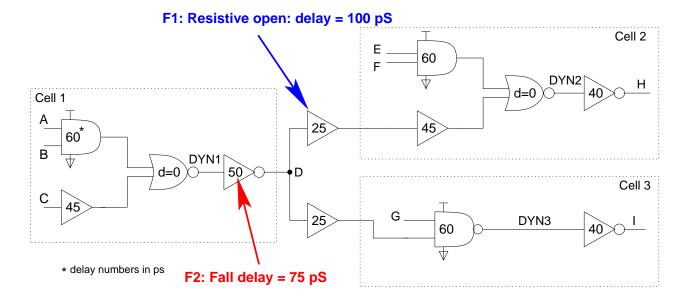

#### 5. (20 points)

The following circuit is a logic model, extracted from three interconnected domino-logic cells at the transistor level, of a block between latches in a design which is supposed to have a cycle time of 250 picoseconds (excluding flop setup and clock-to-Q delays). The numbers on the logic symbols indicate the delays in picoseconds (the buffers model the wire delays).

There are two potential defects, F1 and F2, which cause delay faults (the rise/fall delay of a gate or the delay of the interconnect is increased to the number shown). Find tests for the two faults indicated (consider only one fault at a time), with values 0, 1 or X (don't care) for the variables.

Test for fault F1:

| Α | В | С | D | E | F | G | Н | I |

|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |

Test for fault F2:

| A | В | C | D | Е | F | G | Η | - |

|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |

EE360R/EE382M Spring 2005

# Introduction to VLSI Design Exam. II

J. A. Abraham April 27, 2005

Class (382M/360R): \_\_\_\_\_

| Name: |  |  |  |  |

|-------|--|--|--|--|

|       |  |  |  |  |

|       |  |  |  |  |

|       |  |  |  |  |

|       |  |  |  |  |

Open Book, Open Notes. Time Limit: 1 hour, 15 minutes (pace yourself). Check for 5 pages in exam.

Write your work and all your answers in the boxes provided for them. Use the back of the pages for scratch work if needed. State clearly any assumptions made.

#### 1. (20 points)

(a) Determine the worst-case charge sharing noise on the output of the N of the dynamic gate below as a function of  $V_{DD}$ , when the input is ABCDEF = 111101.

Assume that the diffusion capacitance on uncontacted nodes is half the gate capacitance and that on contacted nodes is equal to the gate capacitance. Also assume that all the nMOS transistors are minimum sized and the pMOS transistors are twice the width of the nMOS transistors.

(b) What is the worst-case noise over all possible inputs?

# 2. (20 points)

Write down the approximate setup time, hold time and clock-to-Q delay in the flip-flop below, in terms of the delays of the basic gates and inverters (example, I2 + T2 + I3).

(a) Identify if there are any hold time problems from the source flops (G1, G2, G3 and G4) to G11 in the following circuit. If there are any, indicate by how much the hold time is violated and suggest a fix which minimizes the impact on the delay of the circuit. Use the delays from the table below.

What is the maximum frequency of operation after fixing any hold-time violation?

MHz

#### 4. (20 points)

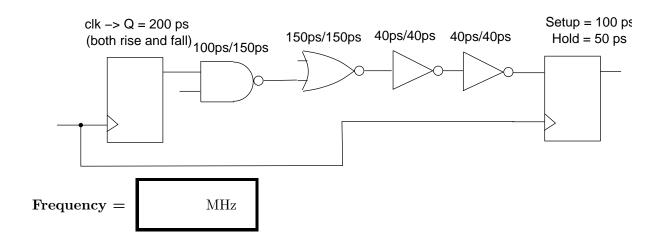

(a) What is the maximum frequency at which the following design can operate?

(b) What is the maximum frequency at which the following design can operate?

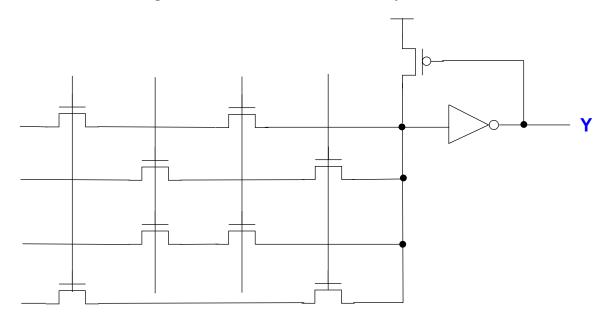

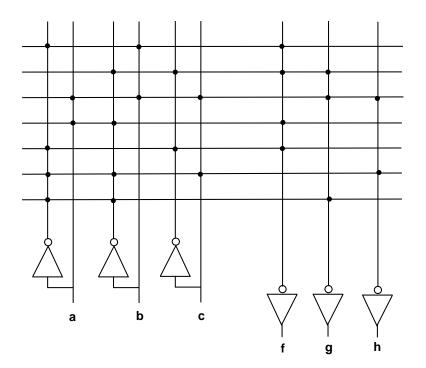

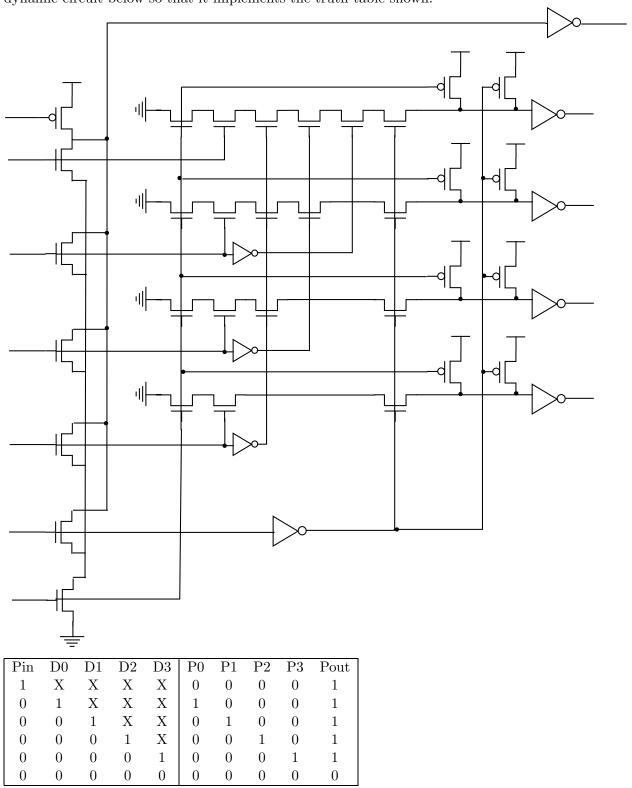

Identify the functions, f, g and h implemented by the PLA below, drawn in dot notation.

VLSI Design EXAM. II

Spring 2006

April 12, 2006

Name: Exam, No. 1

J. Abraham

Open Book, Open Notes. Time Limit: 75 minutes (pace yourself). Check for 5 pages in exam.

Write all your answers in the spaces/boxes provided.

Show any calculations in these pages using the back of the pages if needed. State clearly any assumptions made.

#### 1. (20 points)

The circuit below has the following parameters for the components:

Clock period = 90 nS with a 50% duty cycle

$t_{clk-q} = 40 \text{ nS}$

$t_{setup} = 20 \text{ nS}$

$t_{hold} = 45 \text{ nS}$

AND gate delay = 15 nS

OR gate delay = 20 nS

Inverter delay = 5 nS

Assume that the logic before F1 and after F2 has arbitrary slack and is impervious to timing issues.