# Lecture 6: Non-ideal (real) transistors

#### **Mark McDermott**

**Electrical and Computer Engineering The University of Texas at Austin**

9/18/18 VLSI-1 Class Notes

## **Agenda**

- Transistor I-V Review

- Non-ideal Transistor Behavior

- High Field Effects

- Mobility Degradation

- Velocity Saturation

- Channel Length Modulation

- Threshold Voltage Effects

- Body Effect

- Drain-Induced Barrier Lowering

- Short Channel Effect

- Leakage

- Subthreshold Leakage

- Gate Leakage

- Junction Leakage

- Process and Environmental Variations

#### **Ideal Transistor I-V**

#### Shockley 1<sup>st</sup> order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{cutoff} \\ \beta \left( V_{gs} - V_t - \frac{V_{ds}}{2} \right) V_{ds} & V_{ds} < V_{dsat} & \text{linear} \\ \frac{\beta}{2} \left( V_{gs} - V_t \right)^2 & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

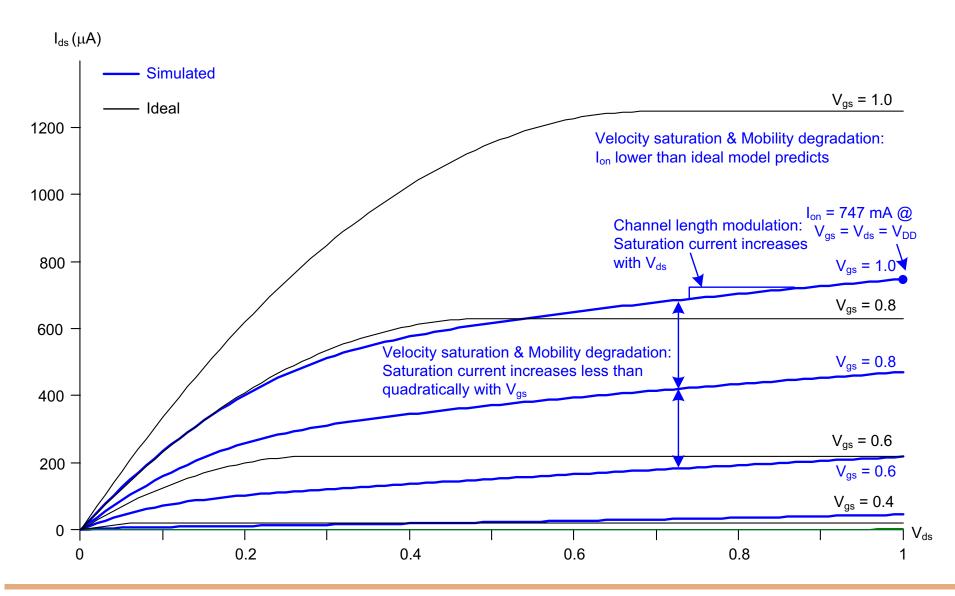

#### 65 nm IBM process, $V_{DD} = 1.0 \text{ V}$

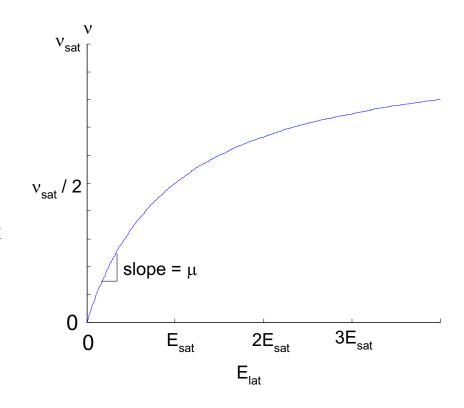

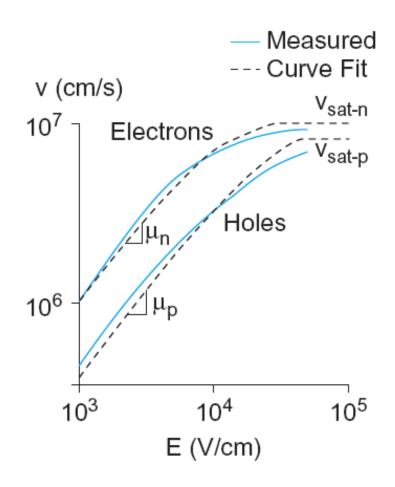

# **Velocity Saturation**

- We assumed carrier velocity / E-field

- $v = \mu E_{lat} = \mu V_{ds}/L$

- At high fields, this ceases to be true

- Carriers scatter off atoms

- Velocity reaches v<sub>sat</sub>

- Electrons: 6-10 x 10<sup>6</sup> cm/s

- Holes: 4-8 x 10<sup>6</sup> cm/s

#### **Better model is:**

9/18/18

$$v = \frac{\mu E_{\text{lat}}}{1 + \frac{E_{\text{lat}}}{E_{\text{sat}}}} \Rightarrow v_{\text{sat}} = \mu E_{\text{sat}}$$

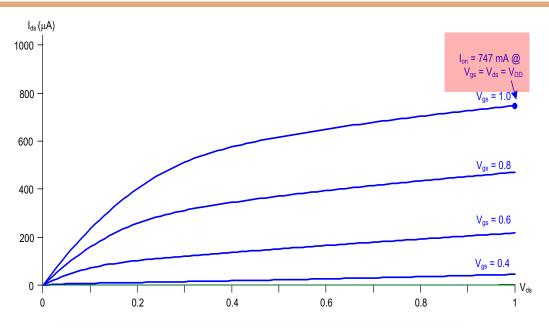

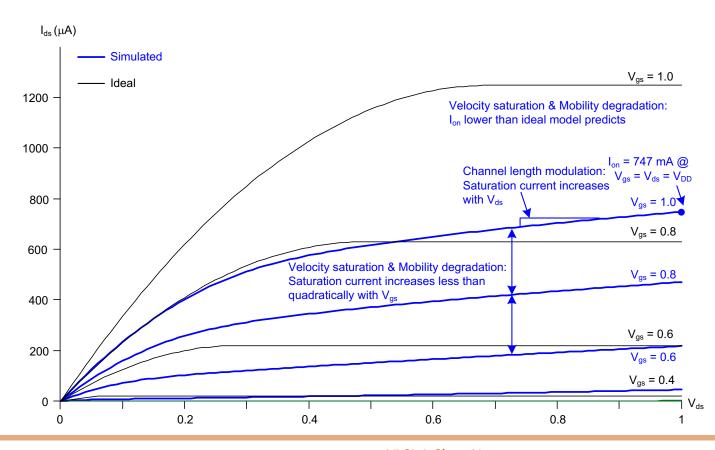

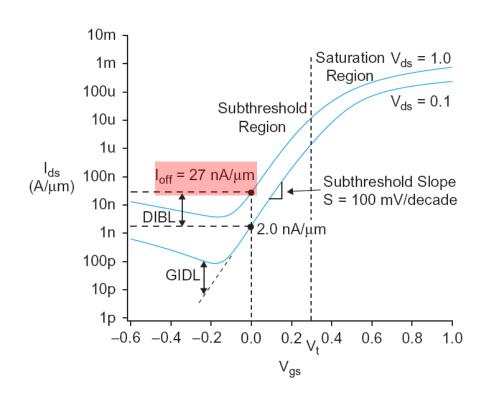

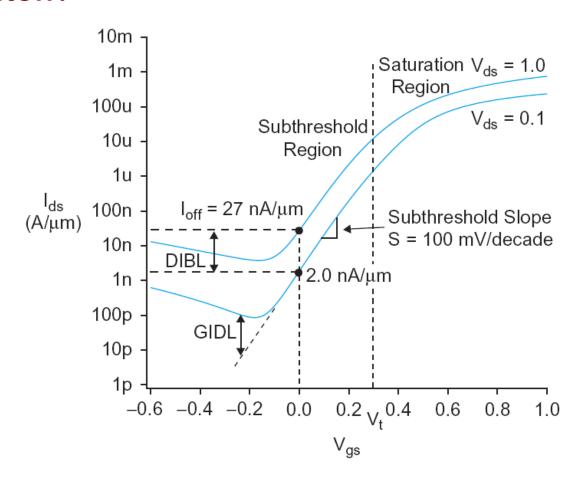

#### **ON and OFF Current**

I<sub>on</sub> = I<sub>ds</sub> @ V<sub>gs</sub> = V<sub>ds</sub> = V<sub>DD</sub>

Saturation

I<sub>off</sub> = I<sub>ds</sub> @ V<sub>gs</sub> = 0, V<sub>ds</sub> = V<sub>DD</sub>

Cutoff

#### **Electric Fields Effects**

- Vertical electric field: E<sub>vert</sub> = Vgs / tox

- Attracts carriers into channel

- **−** Long channel:  $Q_{channel} \propto E_{vert}$

- Lateral electric field: E<sub>lat</sub> = Vds / L

- Accelerates carriers from drain to source

- Long channel:  $v = \mu E_{lat}$

## **Mobility Degradation**

- High E<sub>vert</sub> effectively reduces mobility

- Collisions with oxide interface

$$\mu_{\text{eff}-n} = \frac{540 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}}{1 + \left(\frac{V_{gs} + V_t}{0.54 \frac{\text{V}}{\text{nm}} t_{\text{ox}}}\right)^{1.85}}$$

$$\mu_{\text{eff}-p} = \frac{185 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}}{1 + \frac{\left| V_{gs} + 1.5 V_t \right|}{0.338 \frac{\text{V}}{\text{nm}} t_{\text{ox}}}}$$

## **Velocity Saturation**

## At high E<sub>lat</sub>, carrier velocity rolls off

- Carriers scatter off atoms in silicon lattice

- Velocity reaches v<sub>sat</sub>

- Electrons: 10<sup>7</sup> cm/s

- Holes: 8 x 10<sup>6</sup> cm/s

- Better model

$$v = \begin{cases} \frac{\mu_{\text{eff}} E}{E} & E < E_c \\ 1 + \frac{E}{E_c} & E \ge E_c \end{cases}$$

where, by continuity, the critical electric field is

$$E_c = \frac{2v_{\text{sat}}}{\mu_{\text{eff}}}$$

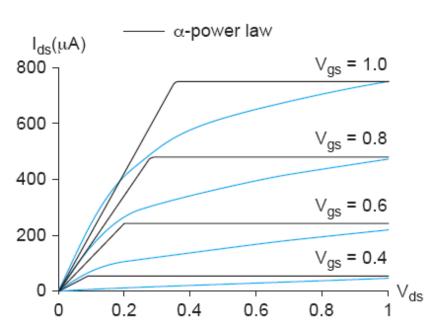

## **Velocity Saturation I-V Effects**

Ideal transistor ON current increases with V<sub>DD</sub><sup>2</sup>

$$I_{ds} = \mu C_{ox} \frac{W}{L} \frac{(V_{gs} - V_{t})^{2}}{2} = \frac{\beta}{2} (V_{gs} - V_{t})^{2}$$

Velocity-saturated ON current increases with V<sub>DD</sub>

$$I_{ds} = C_{ox}W(V_{gs} - V_t)v_{max}$$

- Real transistors are partially velocity saturated

- Approximate with  $\alpha$ -power law model

- I<sub>ds</sub>  $\propto$  V<sub>DD</sub> $^{\alpha}$

- $-1 < \alpha < 2$  determined empirically

## α-Power Model

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{cutoff} \\ I_{dsat} \frac{V_{ds}}{V_{dsat}} & V_{ds} < V_{dsat} & \text{linear} \\ I_{dsat} & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

$$I_{dsat} = P_c \frac{\beta}{2} \left( V_{gs} - V_t \right)^{\alpha}$$

$$V_{dsat} = P_v \left( V_{gs} - V_t \right)^{\alpha/2}$$

where  $\alpha$ ,  $\beta P_c$ , and  $P_v$  are empirically derived

#### —— Simulated

#### UTEECE

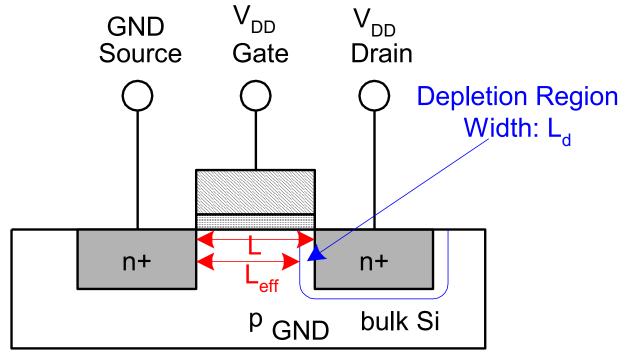

## **Channel Length Modulation**

- Reverse-biased p-n junctions form a depletion region

- Region between n and p with no carriers

- Width of depletion L<sub>d</sub> region grows with reverse bias

- $-L_{eff} = L L_{d}$

- Shorter L<sub>eff</sub> = more current

- I<sub>ds</sub> increases with V<sub>ds</sub>

- Even in saturation

## **Channel Length Modulation I-V Curve**

- $\lambda$  = channel length modulation coefficient

- Empirically fit to I-V characteristics

$$I_{ds} = \frac{\beta}{2} \left( V_{gs} - V_t \right)^2 \left( 1 + \lambda V_{ds} \right)$$

#### UTEECE

## **Threshold Voltage Effects**

- Vt is Vgs for which the channel starts to invert

- Ideal models assumed Vt is constant

- Really depends (weakly) on almost everything else:

- Body voltage: Body Effect

- Drain voltage: Drain-Induced Barrier Lowering

- Channel length: Short Channel Effect

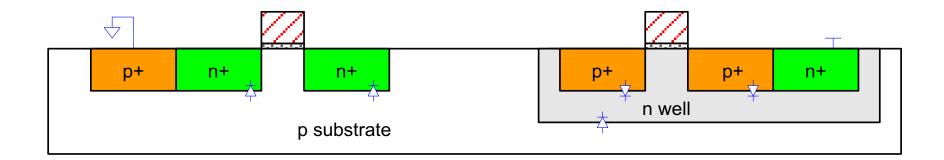

## **Body Effect**

- Body is a fourth transistor terminal

- V<sub>sb</sub> affects the charge required to invert the channel

- Increasing V<sub>s</sub> or decreasing V<sub>b</sub> increases V<sub>t</sub>

$$V_{t} = V_{t0} + \gamma \left( \sqrt{\phi_{s} + V_{sb}} - \sqrt{\phi_{s}} \right)$$

•  $\phi_s$  = surface potential at threshold

$$\phi_s = 2v_T \ln \frac{N_A}{n_i}$$

- Depends on doping level N<sub>A</sub>

- And intrinsic carrier concentration n<sub>i</sub>

- γ = body effect coefficient

$$\gamma = \frac{t_{\text{ox}}}{\varepsilon_{\text{ox}}} \sqrt{2q\varepsilon_{\text{si}}N_A} = \frac{\sqrt{2q\varepsilon_{\text{si}}N_A}}{C_{\text{ox}}}$$

# **Body Effect (Cont)**

For small source-to-body voltage, treat as linear

$$V_t = V_{t0} + k_{\gamma} V_{sb}$$

$$k_{\gamma} = \frac{\gamma}{2\sqrt{\phi_s}} = \frac{\sqrt{\frac{q\varepsilon_{si}N_A}{v_T \ln \frac{N_A}{n_i}}}}{2C_{ox}}$$

Electric field from drain affects channel

More pronounced in small transistors where the drain is closer to

the channel

- Drain-Induced Barrier Lowering

- Drain voltage also affect Vt

$$V_t' = V_t - \eta V_{ds}$$

High drain voltage causes current to increase.

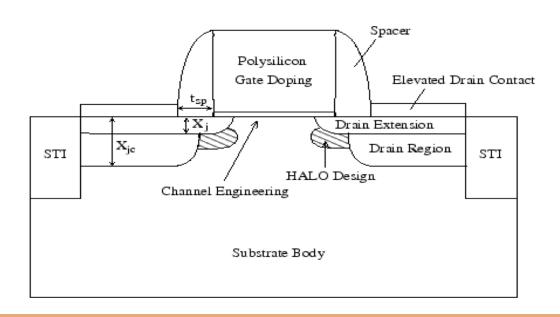

#### **Short Channel Effect**

- In small transistors, source/drain depletion regions extend into the channel

- Impacts the amount of charge required to invert the channel

- And thus makes Vt a function of channel length

- Short channel effect: Vt increases with L

- Some processes exhibit a reverse short channel effect in which Vt decreases with L

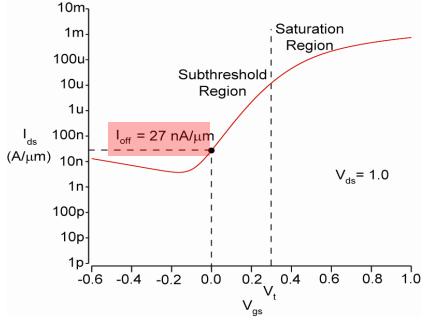

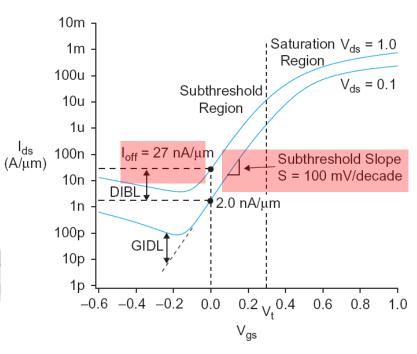

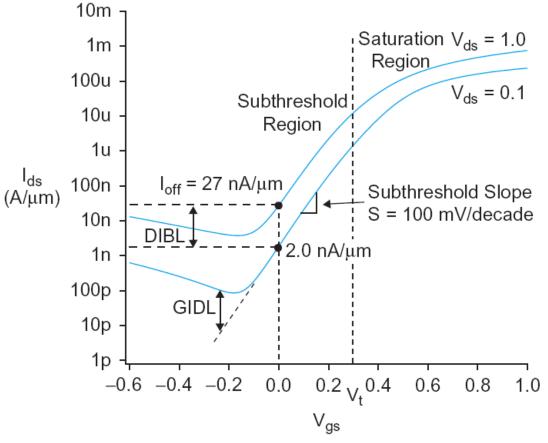

## Leakage

- What about current in cutoff?

- Simulated results

- What differs?Current doesn't go to 0 in cutoff

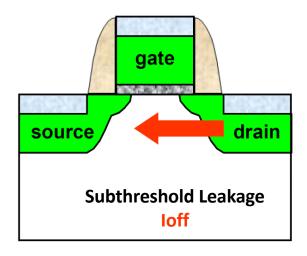

## **Leakage Sources**

- Subthreshold conduction

- Transistors don't turn completely OFF

- Junction leakage

- Reverse-biased PN junction diode current

- Gate leakage

- Tunneling through ultra-thin gate dielectric

Subthreshold leakage is the biggest source in modern transistors

## **Subthreshold Leakage**

Subthreshold leakage exponential with V<sub>gs</sub>

$$I_{ds} = I_{ds0} e^{\frac{V_{gs} - V_{t0} + \eta V_{ds} - k_{\gamma} V_{sb}}{n v_T}} \left( 1 - e^{\frac{-V_{ds}}{v_T}} \right)$$

- n is process dependent

- typically 1.3-1.7

- Rewrite relative to I<sub>off</sub> on log scale

$$I_{ds} = I_{\text{off}} 10^{\frac{V_{gs} + \eta \left(V_{ds} - V_{dd}\right) - k\gamma V_{sb}}{S}} \left(1 - e^{\frac{-V_{ds}}{v_t}}\right)$$

S ≈ 100 mV/decade @ room temperature

$$S = \left[\frac{d\left(\log_{10} I_{ds}\right)}{dV_{gs}}\right]^{-1} = nv_T \ln 10$$

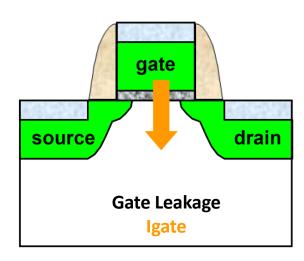

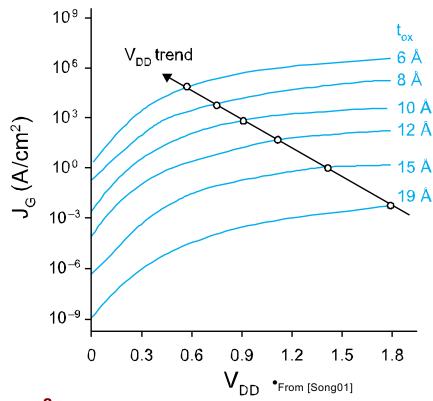

## **Gate Leakage**

- Carriers tunnel thorough very thin gate oxides

- Exponentially sensitive to tox and VDD

$$I_{\text{gate}} = W\!A \! \left( \frac{V_{D\!D}}{t_{\text{ox}}} \right)^{\! 2} \mathrm{e}^{-B \frac{t_{\text{ox}}}{V_{D\!D}}}$$

- A and B are tech constants

- Greater for electrons

- nMOS gates leak more

- Negligible for older processes (tox > 20 Å)

- Critically important at 65 nm and below (tox ≈ 10.5 Å)

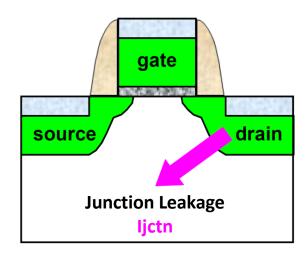

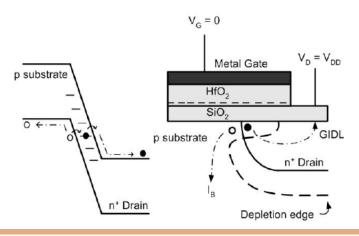

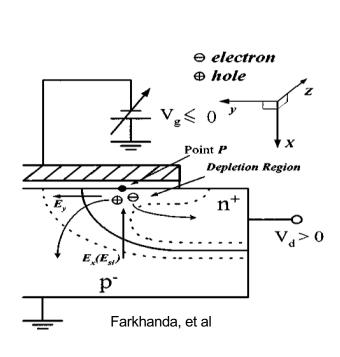

## **Junction Leakage**

- Reverse-biased p-n junctions have some leakage

- Ordinary diode leakage

- Band-to-band tunneling (BTBT)

- Gate-induced drain leakage (GIDL)

$$I_D = I_S \left( e^{\frac{V_D}{v_T}} - 1 \right)$$

- At any significant negative diode voltage, I<sub>D</sub> = -I<sub>s</sub>

- I<sub>s</sub> depends on doping levels

- And area and perimeter of diffusion regions

- Typically < 1 fA/mm2 for > 60nm technologies

## **Band-to-Band Tunneling**

- Tunneling across heavily doped p-n junctions

- Especially sidewall between drain & channel when halo doping is used to increase V<sub>t</sub>

- Increases junction leakage to significant levels

$$I_{BTBT} = WX_j A \frac{E_j}{E_g^{0.5}} V_{dd} e^{-B \frac{E_g^{1.5}}{E_j}}$$

$$I_{BTBT} = WX_j A \frac{E_j}{E_g^{0.5}} V_{dd} \, \mathrm{e}^{-B \frac{E_g^{1.5}}{E_j}} \qquad \qquad E_j = \sqrt{\frac{2 \mathrm{q} N_{halo} N_{sd}}{\varepsilon \left(N_{halo} + N_{sd}\right)}} \bigg( V_{DD} + v_T \ln \frac{N_{halo} N_{sd}}{n_i^2} \bigg)$$

- X<sub>i</sub>: sidewall junction depth

- E<sub>g</sub>: bandgap voltage

- A, B: tech constants

- Occurs at overlap between gate and drain

- Most pronounced when drain is at  $V_{\text{DD}}$ , gate is at a negative voltage

Negates efforts to reduce subthreshold leakage using a negative gate voltage

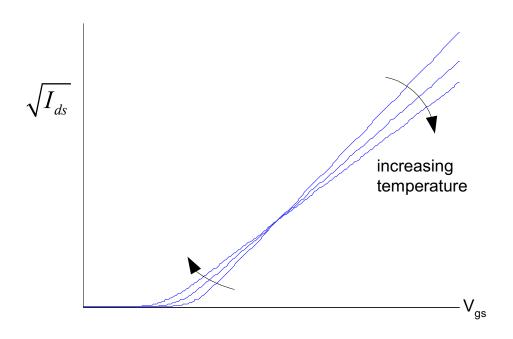

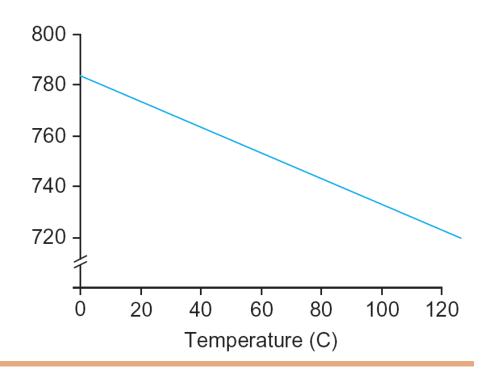

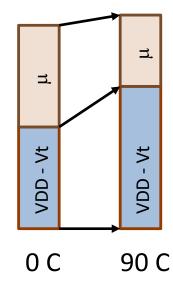

## **Temperature Sensitivity**

- Increasing temperature

- Reduces mobility

- Reduces Vt

- ION decreases with temperature

- IOFF increases with temperature

# **Reverse Temperature Effect**

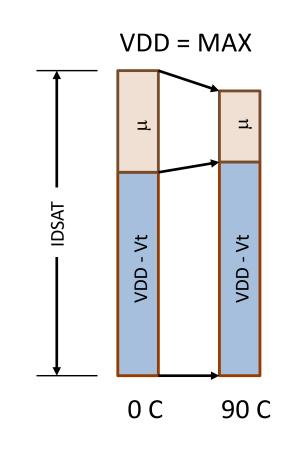

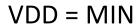

$IDSAT = \mu * W * (VDD - Vt)^{\alpha}$

#### **OBSERVATIONS:**

Mobility ( $\mu$ ) and **Vt** both drop at high temperature.

The (VDD-Vt) quantity increases at high temperature, but it is not enough to compensate for the  $\mu$  drop; as a result, IDSAT drops for high VDD values.

The (VDD-Vt) quantity increases at a faster rate for low VDD; it is enough to compensate the  $\mu$  drop. As a result, IDSAT increases for low VDD and high temperatures; this is called the REVERSE TEMPERATURE EFFECT.

#### So What?

- So what if transistors are not ideal?

- They still behave like switches.

- But these effects matter for...

- Supply voltage choice

- Logical effort

- Quiescent power consumption

- Pass transistors

- Temperature of operation

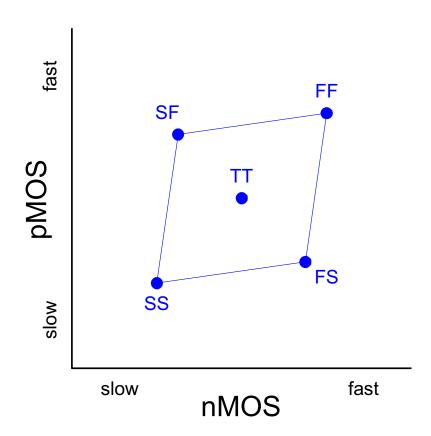

#### **Process Corners**

- Process corners describe worst case variations

- If a design works in all corners, it will probably work for any variation.

- Describe corners with 3 letters (T, F, S) typical, fast, slow

- Transistor speed (NMOS, PMOS)

- Voltage

- Temperature

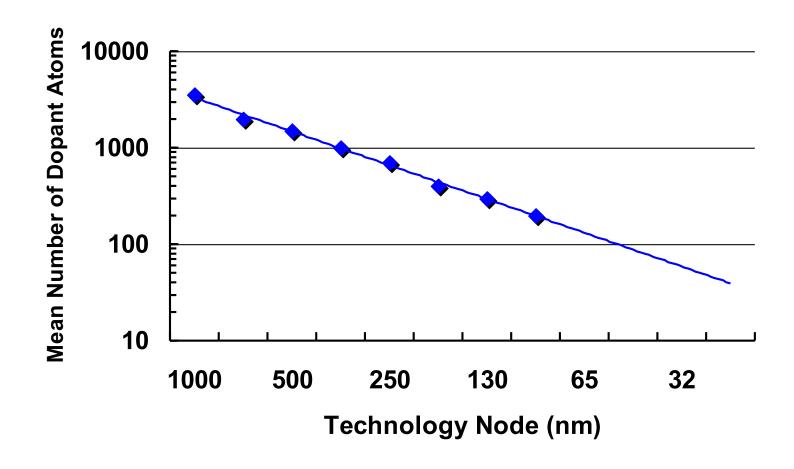

#### **Parameter Variation**

- Transistors have uncertainty in parameters

- Process: Leff, Vt, tox of nMOS and pMOS

- Vary around typical (T) values

- Fast (F)

- Leff: short

- Vt: low

- tox: thin

- Slow (S): opposite

- Not all parameters are independent for nMOS and pMOS

VDD and Temp also vary in time and space

Fast corner:

– VDD: high

– Temp: low

| Corner | Voltage | Temperature |  |

|--------|---------|-------------|--|

| F      | 1.98    | 0 C         |  |

| Т      | 1.8     | 70 C        |  |

| S      | 1.62    | 125 C       |  |

# **Important Corners**

Some critical simulation corners include

| Purpose              | nMOS | pMOS | V <sub>DD</sub> | Temp |

|----------------------|------|------|-----------------|------|

| Cycle time           | S    | S    | S               | S    |

| Power                | F    | F    | F               | F    |

| Subthreshold leakage | F    | F    | F               | S    |

# **Backup**

9/18/18 VLSI-1 Class Notes

Chandu Visweswariah, IBM Thomas J. Watson Research Center

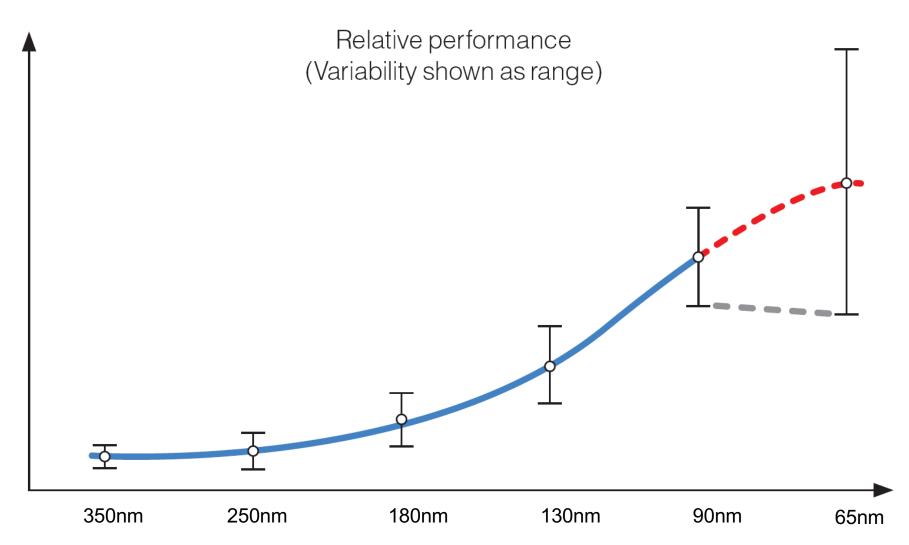

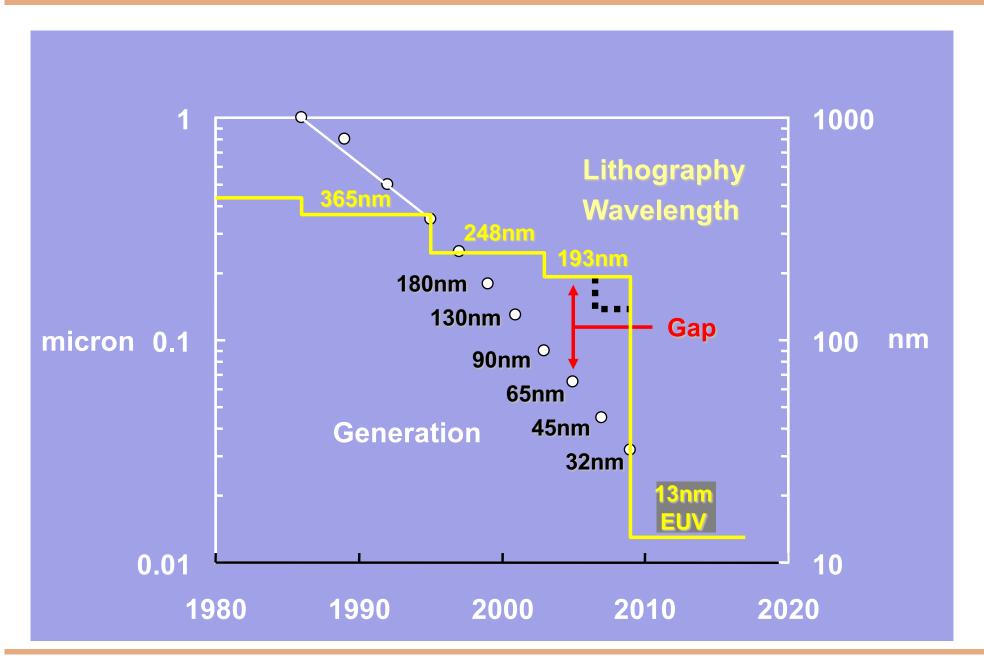

## **Sub-wavelength Lithography Adds Variations**

#### Sources of variation

#### Process variations

Ion implantation, photolithography, gate etch, thermal processing, tolerance in the size of the mask image, mask alignment, angle of the etched polysilicon, temperature, polishing, planarization

#### Subtle layout dependencies

- Transistor orientation

- Post OPC effects

#### Tool errors

Gate delay model, waveform model, etc.

#### Human errors

Designer overwriting the tool results

F. Dartu: Variation Impact on High Performance Circuits