## Department of Electrical and Computer Engineering The University of Texas at Austin

EE 379K, Fall, 2000 Yale Patt, Instructor TAs: Kathy Buchheit, Laura Funderburg, Chandresh Jain, Onur Mutlu, Danny Nold, Kameswar Subramaniam, Francis Tseng, Brian Ward Exam 1, October 4, 2000

| Name (2 points):       |

|------------------------|

|                        |

| Problem 1 (18 points): |

| Problem 2 (15 points): |

| Problem 3 (10 points): |

| Problem 4 (15 points): |

| Problem 5 (15 points): |

| Problem 6 (15 points): |

| Problem 7 (10 points): |

|                        |

| Total (100 points):    |

Note: Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space provided.

Note: Please be sure your name is recorded on each sheet of the exam.

## GOOD LUCK!

| Name:                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem 1 (18 points):                                                                                                                                             |

| Part I (6 points): A memory's addressibility is 64 bits. What does that tell you about the size of the MAR and MDR? About the size of the MAR:                     |

| About the size of the MDR:                                                                                                                                         |

| Part II (6 points): You wish to express -64 as a 2's complement number. How many bits do you need (the minimum number):                                            |

| With this number of bits, what is the largest positive number you can represent (please give answer in both decimal and binary):                                   |

| With this number of bits, what is the largest unsigned number you can represent (please give answer in both decimal and binary):                                   |

| Part III (6 points): We want to increase the number of registers that we can specify in the LC-2 ADD instruction to 32. Do you see any problem with that? Explain. |

## Problem 2 (15 points):

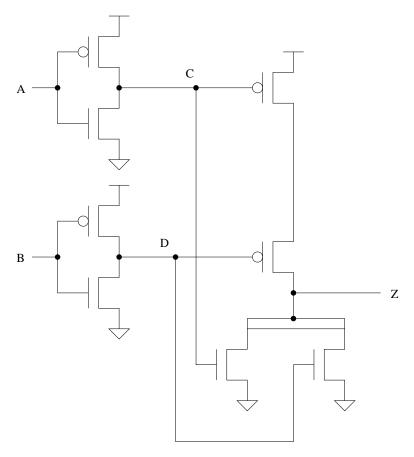

For the following transistor circuit, fill in the truth table.

What is Z in terms of A and B?

| Problem 3 (10 | points):   |                      |             |                     |                                                       |               |                                         |  |

|---------------|------------|----------------------|-------------|---------------------|-------------------------------------------------------|---------------|-----------------------------------------|--|

|               | below, if  | f the register sp    | pecified by | the row can         | be change                                             | ed during th  | R? the MAR? the Mae phase of the instru |  |

|               |            | For the i            | instruction | whose opco          | de is 0001                                            | (ADD):        |                                         |  |

|               |            | Fetch<br>Instruction | Decode      | Evaluate<br>Address | Fetch<br>Data                                         | Execute       | Store<br>Result                         |  |

|               | PC<br>IR   |                      |             |                     |                                                       |               |                                         |  |

|               | MAR<br>MDR |                      |             |                     |                                                       |               |                                         |  |

|               | 111210     |                      |             |                     |                                                       |               |                                         |  |

|               |            |                      | instruction | whose opc           |                                                       | 0 (LD):       |                                         |  |

|               |            | Fetch<br>Instruction | Decode      | Evaluate<br>Address | Fetch<br>Data                                         | Execute       | Store<br>Result                         |  |

|               | PC<br>IR   |                      |             |                     |                                                       |               |                                         |  |

|               | MAR<br>MDR |                      |             |                     |                                                       |               |                                         |  |

|               | WIDIC      |                      |             |                     |                                                       |               |                                         |  |

|               |            |                      | instruction | n whose ope         |                                                       | 1 (ST):       |                                         |  |

|               |            | Fetch<br>Instruction | Decode      | Evaluate<br>Address | $egin{array}{c} 	ext{Fetch} \ 	ext{Data} \end{array}$ | Execute       | Store<br>Result                         |  |

|               | PC<br>IR   |                      |             |                     |                                                       |               |                                         |  |

|               | MAR        |                      |             |                     |                                                       |               |                                         |  |

|               | MDR        |                      |             |                     |                                                       |               |                                         |  |

|               | _          |                      | _           |                     | (                                                     |               |                                         |  |

|               | F          | or the instructi     | ion whose ( | ·                   | ,                                                     | rol instruct: |                                         |  |

|               |            | Fetch<br>Instruction | Decode      | Evaluate<br>Address | Fetch<br>Data                                         | Execute       | Store<br>Result                         |  |

|               | PC         |                      |             |                     |                                                       |               |                                         |  |

|               | IR<br>MAR  |                      |             |                     |                                                       |               |                                         |  |

Name:\_\_\_\_

MDR

| Name: | : |  |

|-------|---|--|

|       |   |  |

## Problem 4 (15 points):

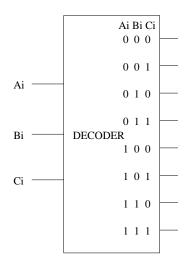

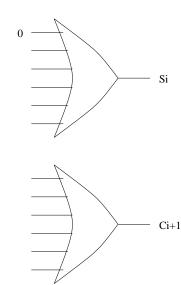

Recall that the ADDER was built with individual \*slices\* that produced a Sum bit and Carry\_out bit based on the two operand bits A and B and the Carry\_in bit. We called such an element a Full Adder. Suppose we have a 3-to-8 Decoder and two six input OR gates, as shown. Can we connect them so that we have a Full Adder? If so, please do. [Hint: if an input to an OR gate is not needed, we can simply put a input 0 on it and it will have no effect on anything. For example, see figure.]

The LC-2 does not have an opcode for the logical function OR. That is, there is no instruction in the LC-2

Name:\_

(3):

(4):

Problem 5 (15 points):

0101 110 100 000 101

| Name: |  |  |  |

|-------|--|--|--|

|       |  |  |  |

Problem 6 (15 points):

Define a new 8-bit floating point format with 1 sign bit, 4 bits of exponent, using an excess-7 code (that is, the bias is 7), and 3 bits of fraction. If xE5 is the bit pattern for a number in this 8-bit floating point format, what value does it have (express as a decimal number):

Problem 7 (10 points):

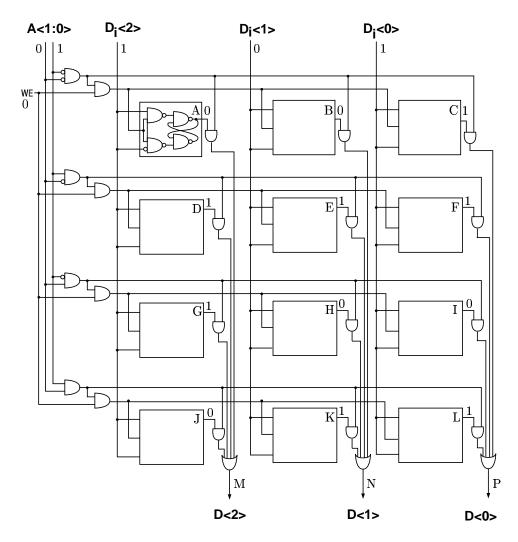

Shown below is our favorite memory, a  $2^2$  by 3 bit memory. We have labeled each of the 12 gated latches A, B, C, D, E, F, G, H, I, J, K, L and the lines D < 2:0 > M, N, P. We have also indicated the values on certain wires.

Part A: What are the values at M and N and P?

**Part B:** Suppose WE changes from 0 to 1 for a short period of time and then changes back to 0. Which of the values A, B, C, D, E, F, G, H, I, J, K, L are different from what they were in Part A? What are their new values?