Two 4-bit 2's complement numbers, n and m, are added, yielding s, the 4-bit result. Determine, using only the AND, OR, and NOT logical operations, if an overflow has occurred during the addition? Construct a logic circuit that does this. The inputs to the logic circuit are n[3:0], m[3:0], and s[3:0]. The output is 0 if no overflow occurs and 1 if an overflow does occur.

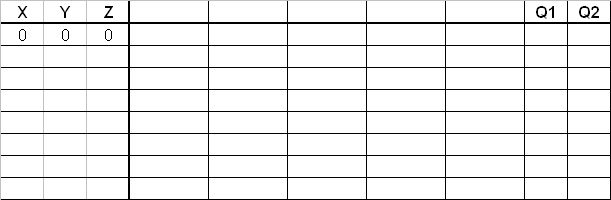

Fill in the truth table for the equations given. The first line is done as an example. We have intentionally left several blank output columns for you to use as you wish.

Q2 = NOT ((Y OR Z) AND (X AND Y AND Z))

Write the decimal equivalents for these IEEE floating point numbers

- 0 10000000 00000000000000000000000

- 1 10000011 00010000000000000000000

- 0 11111111 00000000000000000000000

- 1 10000000 10010000000000000000000

(Please refer to the figure for problem 3.7 on page 84 of the book) The circuit has a major flaw. Can you identify it? Hint: Evaluate the circuit for all sets of inputs.

- Draw a transistor-level diagram for a three-input AND gate

and a three-input OR gate. Do this by extending the designs from

Figures 3.6a and 3.7a. (These figures can be found in the book on pages

56 & 57 respectively).

- Replace the transistors in your diagrams from part (a)

with either a wire or no wire to reflect the circuit’s operation when

the following inputs are applied:

- A = 1, B = 0, C = 0

- A = 0, B = 0, C = 0

- A = 1, B = 1, C = 1

- How many output lines will a five-input decoder have?

- How many output lines will an eight-input decoder have?

- How many output lines will an n-input decoder have? (n can be any number)

Figure 1

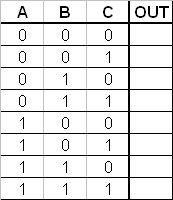

Figure 2

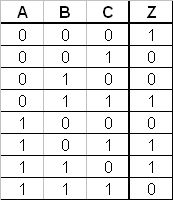

- Complete a truth table for the gate-level logic circuit shown in Figure 2 above.

- What do you notice about the input combinations that give an output value of 1? What do you notice about the input combinations that give an output value of 0?

Given the following truth table, generate the gate-level logic circuit, using the implementation algorithm referred to in Section 3.3.4.

Logic circuit 1 in Figure 3.36 (page 87 of the book) has inputs A, B, C. Logic circuit 2 in Figure 3.37 (page 87 of the book) has inputs A and B. Both logic circuits have an output D. There is a fundamental difference between the behavioral characteristics of these two circuits. What is it? Hint: What happens when the voltage at input A goes from 0 to 1 in both circuits?

Implement a 4-to-1 mux using only 2-to-1 muxes making sure to properly connect all of the terminals. Remember that you will have 4 inputs (A, B, C, and D), 2 control signals (S1 and S0), and 1 output (OUT). After implementing the 4-1 mux, fill in the truth table below.

- Figure 3.39 (page 89 of the book) shows a logic circuit that appears in many of today’s processors. Each of the boxes is a full-adder circuit. What does the value on the wire X do? That is, what is the difference in the output of this circuit if X = 0 versus if X = 1?

- Construct a logic diagram that implements an adder/subtracter. That is, the logic circuit will compute A + B or A – B depending on the value of X. Hint: Use the logic diagram of Figure 3.39 as a building block.