# Department of Electrical and Computer Engineering The University of Texas at Austin

EE 360N, Spring 2007 Yale Patt, Instructor Chang Joo Lee, Rustam Miftakhutdinov, Poorna Samanta, TAs Final Exam, May 11, 2007

| Name: | SOLUTIONS              |  |

|-------|------------------------|--|

|       |                        |  |

|       | Problem 1 (30 points): |  |

|       | Problem 2 (10 points): |  |

|       | Problem 3 (10 points): |  |

|       | Problem 4 (15 points): |  |

|       | Problem 5 (20 points): |  |

|       | Problem 6 (20 points): |  |

|       | Problem 7 (20 points): |  |

|       | Total (125 points):    |  |

Note: Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space provided.

Note: Please be sure your name is recorded on each sheet of the exam.

**GOOD LUCK!**

| Name:                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|

| Problem 1 (30 points)                                                                                                         |

| Part a (4 points): A RAM cell stores one bit of information. That storage is accomplished                                     |

|                                                                                                                               |

| in an SRAM cell by A pair of cross-coupled inverters                                                                          |

| and in a DRAM cell by Charge stored on a capacitor                                                                            |

| Part b (5 points): Amdahi's Law says that the maximum speedup I can get on a multiprocessor for                               |

| an algorithm that is 95% vectorizable is 20                                                                                   |

| To achieve that speedup, I need processors.                                                                                   |

| Part c (5 points): Recall that asynchronous I/O with central arbitration requires at least the following bus control signals: |

| $BR_i$ , $BG_i$ (for all priority levels i), $BBSY$ , $SACK$ , $MSYN$ , $SSYN$                                                |

| What signal does the PAU receive, indicating that a device controller has accepted being bus master for the next bus cycle?   |

| SACK                                                                                                                          |

| What does the PAU do as a result of receiving this signal?                                                                    |

| PAU de-asserts the BG signal                                                                                                  |

| Name: | <br> | <br> |  |

|-------|------|------|--|

|       |      |      |  |

Problem 1 continued:

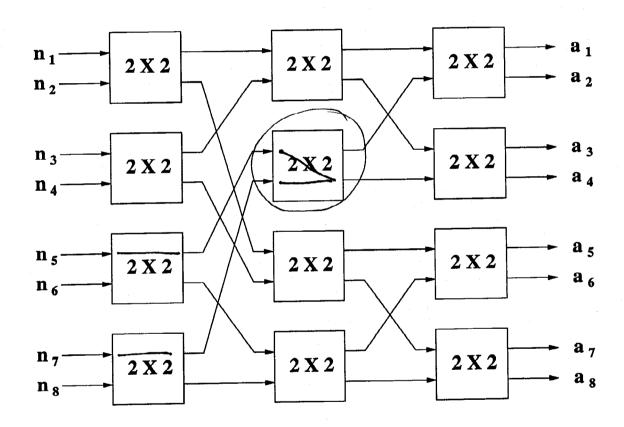

Part d (6 points): Recall that Omega networks are better than buses with respect to

contention

and better than full crossbars with respect to

cost

Suppose  $n_5$  wants to talk to  $a_3$  and  $n_7$  wants to talk to  $a_4$  in the following Omega network in the same cycle. Can they do it? Show how by tracing the paths on the Omega network below, or explain why not in ten words or less in the box provided.

They cannot do it in the same cycle since they collide in the circled switch.

| Name:                                                                                                                                                                                                                                    |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Problem 1 continued:                                                                                                                                                                                                                     |          |

| Part e (5 points): A Directory based Cache Coherency scheme has five processors, each with a private cache. Cache line X has directory information as follows: 100111. Processor 2 wants to read a value in this cache line, and takes a | <u>ب</u> |

| what can you tell me about the Cache Coherency logic? Please be specific.                                                                                                                                                                | P        |

| The logic is faulty. The "private" bit can not be set AND more than one occessor has the line in its cache.                                                                                                                              |          |

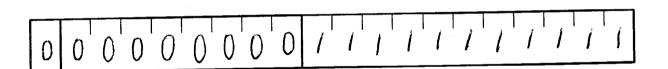

Part f (5 points): Suppose a new floating point data type is invented, which follows all the insights of the IEEE Standard. The only difference is it has 11 fraction bits and 8 exponent bits. Show below the representation for the largest positive subnormal number, using this format.

| Name:                                                                                                                                                        |                                                       |                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------|

| Problem 2 (10 points):                                                                                                                                       |                                                       |                                                |

| We discussed multiplication as a sequence of shi iteration) in class. Now, on the exam, we wish to                                                           | fts/adds in EE 316. We extend it to 3 bits per iterat | ended it to Booth's algorithm (2 bits per ion. |

| A truth table to describe the combinational logic<br>the 3 bits of the multiplier and the input borrow<br>an Add or Subtract signal, a subsequent left shift | bit. The 4 outputs are a                              | left shift of the multiplicand by $k_1$ bits,  |

| For the case where the 3 bits of the multiplier are                                                                                                          | 110 and the input borrow b                            | it is 0, specify the 4 outputs listed below.   |

|                                                                                                                                                              |                                                       |                                                |

| 1. Left shift the multiplicand                                                                                                                               | 1                                                     | bits to the left.                              |

| 2. Perform the operation of A                                                                                                                                | dd / Subtract (circle one)                            | in the ALU.                                    |

| 3. Left shift the multiplicand                                                                                                                               | 2                                                     | bits to the left.                              |

|                                                                                                                                                              |                                                       |                                                |

4. Set the Borrow bit to 0 /(1)circle one).

| Name:   |      |  |

|---------|------|--|

| Ivailic | <br> |  |

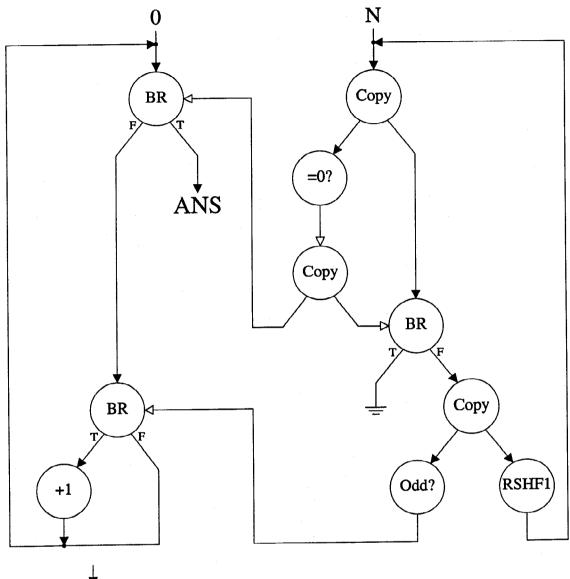

## Problem 3 (10 points)

Consider the following data flow graph:

Note that node Odd? outputs True if its input is odd and False if its input is even.

What does the data flow graph above do?

Answer: Counts the number of ones in the binary representation of N.

| Name: |

|-------|

|-------|

### Problem 4 (15 points):

An array A consists of 1536 one-byte elements, stored in 1536 consecutive locations of memory, starting at address x4000. (Hint: 1536 = 1024 + 512)

A programmer wishes to add 10 to every 8th element, but does so by the very curious method of adding 1 to every 8th element, and then iterating that process ten times. The C program segment looks like this:

Assume that the compiler allocates registers for the loop variables i and index. The processor has a 1 KB, 2-way set associative cache. You may assume that the cache is initially empty. You may leave the answers for the following questions as fractions. Please show your work.

Part a (5 points): For a cache line size of 16 bytes, calculate the miss ratio if the perfect LRU replacement policy is used.

No. of misses periteration =

$$\frac{1536}{16}$$

Miss ratio:

$$\frac{1536 \times 10}{16} = \frac{1}{4}$$

Part b (10 points): Suppose the cache line is 4 bytes. All other parameters remain the same. Circle the replacement policy which would give the least number of misses. Also, calculate the miss ratio for your chosen replacement policy.

Miss ratio:

$$\frac{192 + 128 \times 9}{1536 \times 2 \times 10} = \frac{7}{20} = \frac{7}{120} = \frac{1}{120} = \frac{1}{12$$

| Name: |

|-------|

|-------|

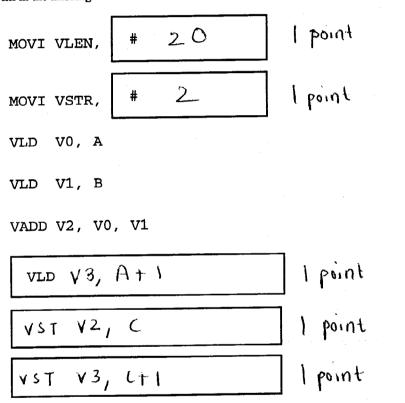

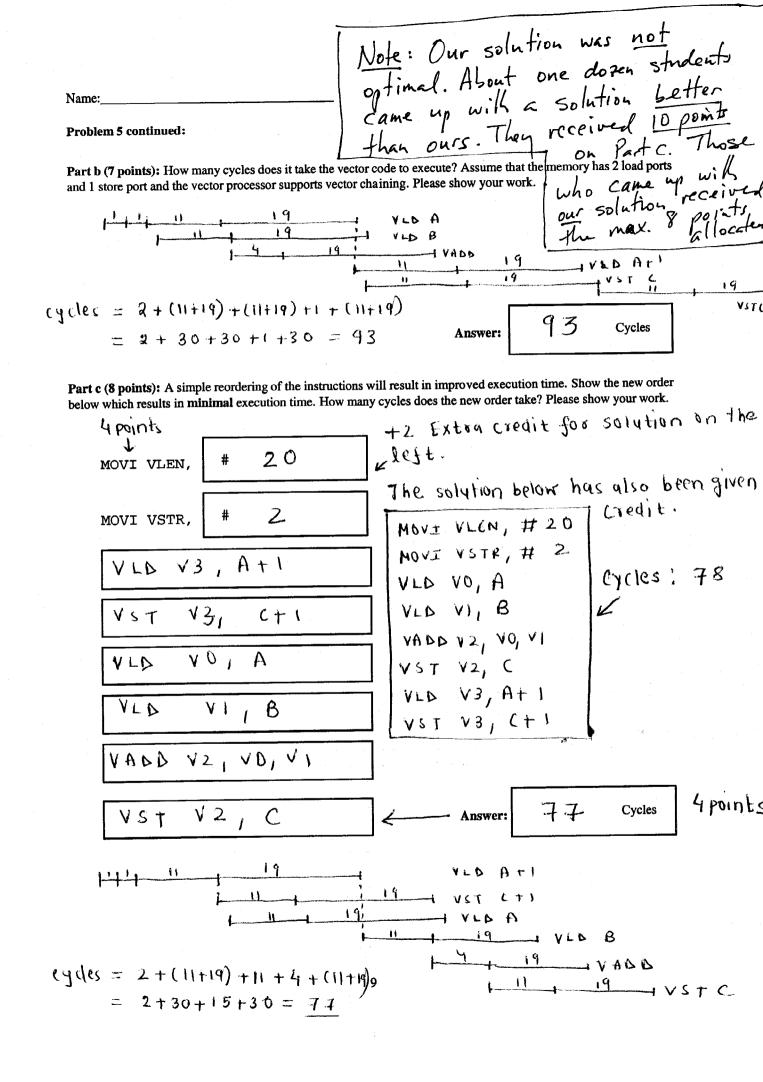

# Problem 5 (20 points)

An in-order vector processor with 11 cycle memory latency, 16-way interleaved memory and 8 vector registers of length 64 is used to execute the vector code resulting from compiling the following high-level language program segment:

Part a (5 points): Shown below is the vector code produce by the compiler with some information missing. Your job is to fill in the missing information.

You have available the following vector instructions:

```

MOVI VLEN, #n ; (1 cycle)

MOVI VSTR, #n ; (1 cycle)

VADD Vi, Vj, Vk ; Vi is dest, Vj, Vk are sources (4 staged pipelined adder)

VLD Vi, A + k ; Vi gets loaded with contents of memory, starting at A + k

VST Vi, A + k ; Contents of Vi gets stored in memory, starting at A + k

```

| Name: |

|-------|

|-------|

#### Problem 6 (20 points)

Consider the following two-level virtual memory system for the LC-3b. Recall that the user page table is located in the system virtual space:

Virtual Address Space:

64KB

Number of Page Frames:

32

User Space Range: System Space Range: x0000 to x7FFF x8000 to xFFFF

Page Size:

Page Table Entry Size:

256 bytes 2 bytes

The system does not include a Translation Lookaside Buffer and a cache. Each Page Table Entry (PTE) contains valid (V), Modified (M), Reference (R) bits and Page Frame Number(PFN). The PTE format is as follows:

| 15 |   |   |   | 11 | 10 |   |   |           |     | 0 |

|----|---|---|---|----|----|---|---|-----------|-----|---|

| V  | 0 | 0 | 0 | M  | R  | 0 | 0 | <u></u> ] | PFN |   |

Part a (2 points): How many bits are needed for the address bus to the physical memory? Show the computation.

$$2^{5} \times 2^{8} = 2^{13}$$

Answer:

13

Part b (18 points): The machine stopped at a breakpoint and the following state information was observed:

Note: SBR is the System Page Table Base Register and UBR is the User Page Table Base Register. Each points to the first entry of the corresponding page table.

After execution resumed, the machine issued the following successive seven physical memory requests, uninterrupted by any page faults, access control violations, or anything else. Note that each entry is incomplete. Your job: complete the seven entries.

| Access # | PA     | Access | Data  | Identity of Item Being Accessed |    |

|----------|--------|--------|-------|---------------------------------|----|

| 1        | x0040  | Read   | x8C18 | PTE for System Page X20         |    |

| 2        | x 1860 | Read   | x8410 | PTE for User Page X30           |    |

| 3        | xiolo  | Read   |       | The instruction STW R7, R2, #2  |    |

| 4        | x0040  | Read   | x8C18 | PTE for System Page X20         |    |

| 5        | x1880  | Read   | x8008 | PTE for User Page X40           |    |

|          | x1880  |        |       | PTE for User Page X40. Set Mand | Rb |

| 7        | x0804  |        |       | Pata stored by the STW instruct |    |

Note: The last column should identify what is being read specifically. For example: "The instruction LDB R0,R1,#0," "The PTE for User Virtual Page 0," "PTE for System Virtual Page 0," etc.

Name:

## Problem 7 (20 points)

We are designing a 42-bit floating point format similar to the IEEE standard discussed in class. We have decided on the sizes of the exponent and fraction fields as shown below:

| S | Exponent | Fraction |

|---|----------|----------|

| 1 | 10       | 31       |

However, we have not yet decided on the bias of the exponent. Please use N for the bias in your answers to parts a, b, and c below.

Part a (5 points): What is the smallest positive number represented by this format (Min)?

$$Min = 2^{-31} \times 2^{1-N}$$

Part b (5 points): What is the largest positive finite number represented by this format (Max)?

$$Max = (2-2^{31}) \times 2 \boxed{1022-N}$$

| Name: |

|-------|

|-------|

#### Problem 7 continued:

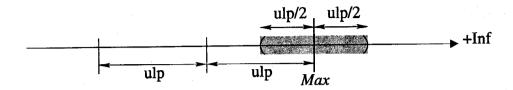

Part c (5 points): In class, we defined the range of real values rounded to Min if the round to nearest rounding mode is used. The shaded range in the figure below represents the real values rounded to Max. Any number to the right of that range is rounded to positive infinity.

We want to choose the bias (N) so that for any positive finite number x represented exactly by our floating point format, its reciprocal (1/x) can also be represented (after rounding to nearest) as a positive finite number.

That means

$$\frac{1}{Min}$$

must be less than  $(2-2^{32}) \times 2^{1022-N}$   $(Max + \frac{ULP}{2})$

2 and,

$$\frac{1}{Max}$$

must be greater than  $2^{-32} \times 2^{1-N}$  (Min  $-\frac{ULP}{2}$ )

Part d (5 points): Compute the bias that will allow the results in part c to hold. NOTE: In part c you have created two inequalities in N. Solve those 2 inequalities.

inequalities in N. Solve those 2 inequalities.

$$\frac{1}{2^{-31} \times 2^{1-N}} < (2-2^{-32}) \times 2^{1022-N} \Rightarrow 2^{N+30} < (1-2^{-33}) \times 2^{1023-N}$$

$$\Rightarrow 2^{N+30} < 2^{1023-N} \quad (N \text{ is in teger})$$

$$2^{-32} \times 2^{1-N} < \frac{1}{(2-2^{-31}) \times 2^{1022-N}} \Rightarrow 2^{N+31} > (1-2^{-32}) \times 2^{1023-N}$$

$$\Rightarrow 2^{N+34} > 2^{1023-N}$$

(N is integer

$$\Rightarrow 2^{N+30} < 2^{1023-N} \le 2^{N+31}$$

$$\Rightarrow 2^{1023-N} = 2^{N+31}$$

$$\Rightarrow 2N = 992 \Rightarrow N = 496$$

13