# Department of Electrical and Computer Engineering The University of Texas at Austin

EE 306, Fall, 2008 Yale Patt, Instructor TAs: Jeffrey Allan, Arvind Chandrababu, Eiman Ebrahimi, Aravind Jakkani, Khubaib, Allison Korczynski, Pratyusha Nidamaluri, Zrinka Puljiz, Che-Chun Su, Christopher Wiley. Exam 1, October 08, 2008 Problem 1 (20 points): Problem 2 (20 points):\_\_\_\_\_ Problem 3 (15 points):\_\_\_\_\_ Problem 4 (15 points):\_\_\_\_\_ Problem 5 (15 points): Problem 6 (15 points):\_\_\_\_\_ Total (100 points):\_\_\_\_\_ Note: Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space provided. Note: Please be sure your name is written legibly on each sheet of the exam.

GOOD LUCK!

I will not cheat on this exam.

Signature

| Name:                                                                                                 |                                      |

|-------------------------------------------------------------------------------------------------------|--------------------------------------|

| Problem 1 (20 points)                                                                                 |                                      |

| Part a (4 points): For what values of A,B,C,D,E, and F will the output                                | nt of the 6-input AND gate be 1.     |

|                                                                                                       |                                      |

| A B C D E F  Part b (4 points): Add the two numbers. They are in base 7. Your res                     | sult should also be in base 7.       |

| 56042 03561                                                                                           |                                      |

| Part c (4 points): The value -5 can be represented by strings of 0s an types. Please show them below. | d 1s according to the following data |

|                                                                                                       | 8 bit 2's complement integer         |

|                                                                                                       | in ASCII                             |

32 bit floating point

| Name: |

|-------|

|-------|

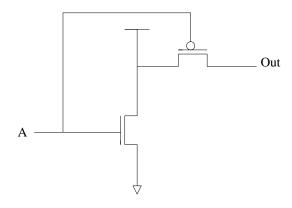

Part d (4 points): An Aggie knew that an inverter contained one P-type transistor and one N-type transistor, but he wired them up wrong, as shown below.

| What is the value of Out when A=0: |  |

|------------------------------------|--|

| What is the value of Out when A=1: |  |

Part e (4 points): When a computer executes an instruction, the state of the computer is changed as a result of that execution. Is there any difference in the state of the LC-3 computer as a result of executing instruction 1 below vs executing instruction 2 below? Explain. We can assume the state of the LC-3 computer before execution is the same in both cases.

instruction 1: 0001 000 000 1 00000 register 0 <-- register 0 + #0 instruction 2: 0000 111 000000000 branch to PC' + #0 if any of N,Z,or P is set Put your answer (no more than 20 words) in the box below.

### Problem 2 (20 points)

Part a (7 points): A program wishes to load a value from memory into register 1, and on the basis of the value loaded, execute code starting at x3040 if the value loaded is positive, execute code starting at x3080 if the value loaded is negative, or execute code starting at location x3003 if the value loaded is zero. The first instruction of this program (load a value into register R1) is shown in x3000.

Your job: write the instructions for locations x3001 and x3002.

| x3000: | 0010 001 011111111 |

|--------|--------------------|

| x3001: |                    |

| x3002: |                    |

**Part b** (7 points): The program segment below starts execution at x3000. When the program halts, what is contained in register 0?

```

x3000: 0101 000 000 1 00000 ;register 0 <-- 0 x3001: 0001 000 000 1 00001 ;register 0 <-- register 0 + 1 x3002: 0000 001 1111111110 ;branch p -2 x3003: 1111 0000 0010 0101 ;TRAP x25

```

Part c (6 points): Two of the outputs of a 3 to 8 decoder are used as inputs to an AND gate as shown below.

Do you have enough information to say for certain what the output of f is?

If yes, give the value of f and explain why you have enough information. If no, explain what further information you need.

| Name: | 2. |  |

|-------|----|--|

|       |    |  |

## Problem 3 (15 points)

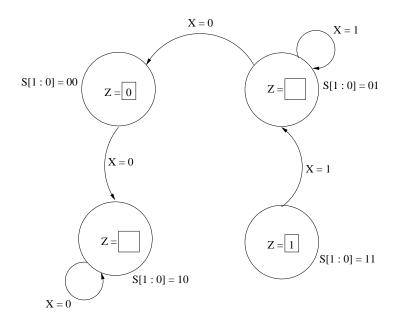

Shown below is a state diagram for a 4 state machine, and the truth table showing the behavior of this state machine. Some of the entries in both are missing.

Note that the states are labeled 00, 01, 10, and 11 and the output of each state Z (0 or 1) is shown in each state. The input is shown as X.

Your job, complete both the truth table and the state machine.

| S[1] | ] S[0 | X | S'[1] | ] S'[0 | ] Z |

|------|-------|---|-------|--------|-----|

| 0    | 0     | 0 |       |        |     |

| 0    | 0     | 1 | 1     | 1      |     |

| 0    | 1     | 0 |       |        |     |

| 0    | 1     | 1 |       |        | 1   |

| 1    | 0     | 0 |       |        | 0   |

| 1    | 0     | 1 | 0     | 1      |     |

| 1    | 1     | 0 | 0     | 0      |     |

| 1    | 1     | 1 |       |        |     |

|      |       |   | ı     |        |     |

| Name: | e: |  |

|-------|----|--|

|       |    |  |

## Problem 4 (15 points)

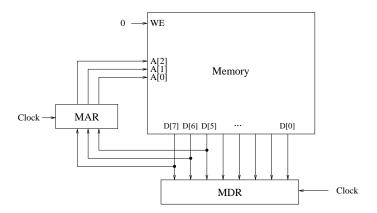

Shown below is a byte-addressible memory consisting of 8 locations, and its associated MAR and MDR. Both MAR and MDR consist of flip flops which are latched at the start of each clock cycle based on the values on their corresponding input lines. A memory read is initiated every cycle and the data is available by the end of that cycle.

Just before the start of cycle 1, MAR contains 000, MDR contains 00010101, and the contents of each memory location is as shown.

| Memory Location | Value    |

|-----------------|----------|

| x0              | 01010000 |

| x1              | 11110001 |

| x2              | 10000011 |

| x3              | 00010101 |

| x4              | 11000110 |

| x5              | 10101011 |

| x6              | 00111001 |

| x7              | 01100010 |

| ı | (a) | What.     | do | MAR and   | MDR   | contain | inst | hefore | the  | end | of c | vele  | 1 |

|---|-----|-----------|----|-----------|-------|---------|------|--------|------|-----|------|-------|---|

| ı | (cu | , vv mata | uo | minim and | MIDIU | Comain  | usu  | DCIOLC | ULLU | CHU | OI C | y OIO | 1 |

| MAR: |  | MDR: |  |

|------|--|------|--|

|------|--|------|--|

(b) What does MDR contain just before the end of cycle 4.

| MDR: |  |

|------|--|

|      |  |

Please show your work.

| Name: |  |

|-------|--|

|       |  |

#### Problem 5 (15 points)

An operate instruction present in most ISAs is MOD (example: MOD C,A,B). The result is the remainder one gets when the dividend A is divided by the divisor B. It is sometimes written: A mod B. That is,  $10 \mod 3 = 1$ .  $20 \mod 6 = 2$ .

Since the LC-3 does not have a MOD instruction, we wish to write a program to produce the result: A mod B. It will require dividing A by B. Since the LC-3 does not have a Divide instruction either, we will extend the idea we used in class to multiply two numbers together by successive additions. That is, we can perform Division by successively subtracting the divisor from the dividend the proper number of times.

The program below will produce A mod B, the remainder when we divide A by B, and store the remainder in location x3102. The dividend (A) is initially in location x3100 and the divisor (B) is initially in location x3101.

Your job: fill in the missing instructions so the program works correctly.

| 0011 0000 0000 0000                                               | ; Starts at x3000                                                                                                                      |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0010 001 011111111<br>0010 010 011111111                          | ; Loads A from x3100 into R1; Loads B from x3101 into R2                                                                               |

|                                                                   |                                                                                                                                        |

| 0001 010 010 1 00001<br>0001 001 001 000 010<br>0000 011 11111111 | ; Adds 1 to R2 and stores in R2<br>; Adds R1 and R2 and stores result in R1<br>; If zero or positive, branches to previous instruction |

| 0010 010 011111010                                                | ; Loads value from x3101 into R2                                                                                                       |

|                                                                   |                                                                                                                                        |

| 0011 001 011111001                                                | ; Stores value in R1 into x3102                                                                                                        |

| 1111 0000 00100101                                                | ; Halt                                                                                                                                 |

| Name: | : |

|-------|---|

|       |   |

#### Problem 6 (15 points)

One of the opcodes we have not considered yet in class is LDI (1010), which stands for Load Indirect. It is almost identical to LD (0010), which you already know. The difference is as follows: Both instructions use PC' + offset9 to compute a memory address. In the case of LD, the contents of the corresponding memory location is the value that gets loaded into the specified register. In the case of LDI, the contents of that memory location is the ADDRESS of the memory location that contains the value to be loaded into the specified register.

For example, if the instruction  $0010\ 011\ 01111111111$  is in location x3000, and location x3100 contains x5000, you know that the computer will load x5000 into register 3. If instead, the instruction  $1010\ 011\ 0111111111$  is in location x3000, and x3100 contains x5000, and location x5000 contains x0008, the computer would load the value x0008 into register 3.

All instructions are processed, clock cycle by clock cycle, as the computer goes through the FETCH, DE-CODE, etc. phases of the instruction cycle.

Your job: Fill in the table below, showing the contents of each of the registers at the end of each clock cycle. Use as many clock cycles as you need. It is not necessary to use all that are provided.

At the start of clock cycle 1:

| Memory Location | Value |  |

|-----------------|-------|--|

| x3030           | xA882 |  |

| x30B3           | x6000 |  |

| x6000           | x0002 |  |

Note: Recall that during a clock cycle, combinational logic is carried out, based on the values in the registers at the start of that clock cycle. The results of that combinational logic are latched into the registers at the end of the clock cycle (and ONLY at the end of the clock cycle), so as to be available to the logic in the next (subsequent) clock cycle.

Note: Assume a memory access takes one clock cycle. That is, the memory read uses the contents available in MAR at the start of the clock cycle to determine the location to be read, and latches the data from that location into MDR at the end of the clock cycle.

Note: We have provided the data sheet for LDI from Appendix A, and the state machine of the LC-3 from Appendix C, although neither may be necessary.

|                    | $\mathbf{PC}$ | IR    | MAR   | MDR   | ${ m Reg} \; 4$ |

|--------------------|---------------|-------|-------|-------|-----------------|

| Before Execution   | x3030         | x1540 | x302F | x1540 | x0005           |

| At end of cycle 1  |               |       |       |       |                 |

| At end of cycle 2  |               |       |       |       |                 |

| At end of cycle 3  |               |       |       |       |                 |

| At end of cycle 4  |               |       |       |       |                 |

| At end of cycle 5  |               |       |       |       |                 |

| At end of cycle 6  |               |       |       |       |                 |

| At end of cycle 7  |               |       |       |       |                 |

| At end of cycle 8  |               |       |       |       |                 |

| At end of cycle 9  |               |       |       |       |                 |

| At end of cycle 10 |               |       |       |       |                 |

| At end of cycle 11 |               |       |       |       |                 |

| At end of cycle 12 |               |       |       |       |                 |