## VMM User Guide

Version E-2011.03 March 2011

Comments? E-mail your comments about this manual to: vcs\_support@synopsys.com.

#### **Copyright Notice and Proprietary Information**

Copyright © 2011 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

#### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

"This document is duplicated with the permission of Synopsys, Inc., for the exclusive use of \_\_\_\_\_ and its employees. This is copy number \_\_\_\_\_

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Registered Trademarks (®)**

Synopsys, AEON, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, CoMET, Confirma, CODE V, Design Compiler, DesignWare, EMBED-IT!, Formality, Galaxy Custom Designer, Global Synthesis, HAPS, HapsTrak, HDL Analyst, HSIM, HSPICE, Identify, Leda, LightTools, MAST, METeor, ModelTools, NanoSim, NOVeA, OpenVera, ORA, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Sonic Focus, STAR Memory System, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

#### Trademarks (™)

AFGen, Apollo, ARC, ASAP, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIM<sup>plus</sup>, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Intelli, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Macro-PLUS, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, ORAengineering, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, RippledMixer, Saturn, Scirocco, Scirocco-i, SiWare, Star-RCXT, Star-SimXT, StarRC, System Compiler, System Designer, Taurus, TotalRecall, TSUPREM-4, VCSi, VHDL Compiler, VMC, and Worksheet Buffer are trademarks of Synopsys, Inc.

#### Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license. ARM and AMBA are registered trademarks of ARM Limited. Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

# Contents

# 1 Introduction

| Overview                                                              |

|-----------------------------------------------------------------------|

| VMM Benefits:                                                         |

| Ease of Use                                                           |

| Reuse                                                                 |

| Effectiveness                                                         |

| How to Use This User Guide? 1-8                                       |

| Basic Concepts of VMM 1-9                                             |

| Building Blocks - Class Library 1-10                                  |

| Verification Environments and Execution Control Phases 1-12           |

| Enhanced Verification Performance and Flexibility                     |

| Debug and Analysis: Message Service Class and Transaction Debug. 1-15 |

| What's New in VMM? 1-16                                               |

| UML Diagram 1-17                                                      |

| Resources                                                             |

# 2 Architecting Verification Environments

| Overview               | 2-2  |

|------------------------|------|

| Testbench Architecture | 2-2  |

| Signal Layer           | 2-6  |

| Command Layer          | 2-15 |

VMM User Guide

| Functional Layer 2-17                                          |

|----------------------------------------------------------------|

| Scenario Layer                                                 |

| Test Layer                                                     |

| Sub-environments 2-23                                          |

| Constructing and Controlling Environments 2-28                 |

| Quick Transaction Modeling Style 2-30                          |

| Understanding Implicit and Explicit Phasing                    |

| Composing Explicitly Phased Environments                       |

| Composing Explicitly Phased Sub-Environments                   |

| Composing Implicitly Phased Environments/Sub-Environments 2-48 |

| Reaching Consensus for Terminating Simulation                  |

| Architecting Verification IP (VIP)                             |

| VIP and Testbench Components                                   |

| Transactions                                                   |

| Transactors                                                    |

| Communication                                                  |

| Environments and Sub-Environments 2-73                         |

| Testing VIPs                                                   |

| Advanced Usage                                                 |

| Mixed Phasing 2-75                                             |

# **3** Modeling Transactions

| Overview                          |

|-----------------------------------|

| Class Properties/Data Members 3-8 |

| Quick Transaction Modeling Style  |

| Message Service in Transaction    |

| Randomizing Transaction Members   |

| Context References                |

| Inheritance and OOP               |

| Handling Transaction Payloads     |

| /lethods                          |

| Factory Service for Transactions  |

| Constraints                          | <br>3-20 |

|--------------------------------------|----------|

| Shorthand Macros                     | <br>3-23 |

| User-Defined Implementations         | <br>3-25 |

| Unsupported Data Types               | <br>3-31 |

| rand_mode() copy in Shorthand Macros | <br>3-34 |

# 4 Modeling Transactors and Timelines

| Overview                                                   |

|------------------------------------------------------------|

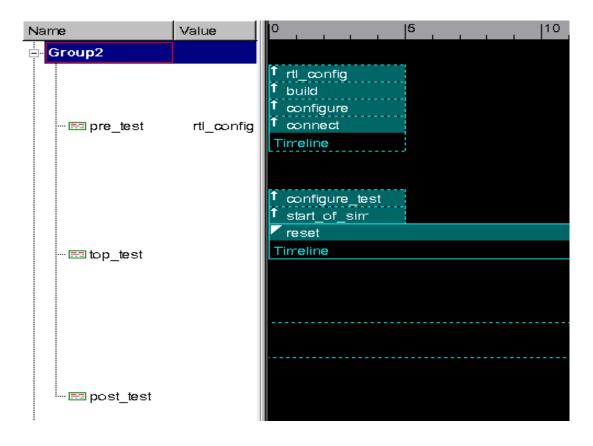

| Transactor Phasing                                         |

| Explicit Transactor Phasing 4-7                            |

| Implicit Phasing 4-14                                      |

| Threads and Processes Versus Phases                        |

| Physical-Level Interfaces                                  |

| Transactor Callbacks 4-26                                  |

| Advanced Usage                                             |

| User-defined vmm_xactor Member Default Implementation 4-31 |

| User-Defined Implicit Phases                               |

| Skipping an Implicit Phase 4-35                            |

| Disabling an Implicit Component 4-35                       |

| Synchronizing on Implicit Phase Execution                  |

| Breakpoints on Implicit Phasing 4-38                       |

| Concatenation of Tests 4-40                                |

| Explicitly Phasing Timelines 4-42                          |

# 5 Communication

| Overview                                   | 5-2 |

|--------------------------------------------|-----|

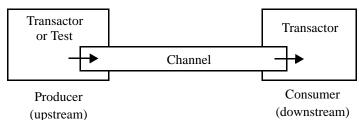

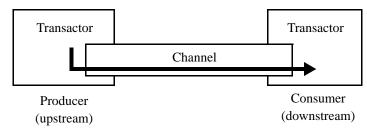

| Channel                                    | 5-3 |

| Channel Declaration (vmm_channel_typed)    | 5-4 |

| Channel Declaration (vmm_channel)          | 5-5 |

| Connection of Channels Between Transactors | 5-5 |

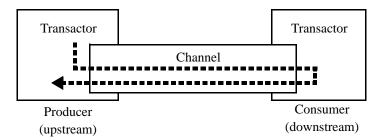

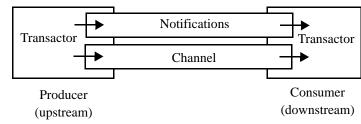

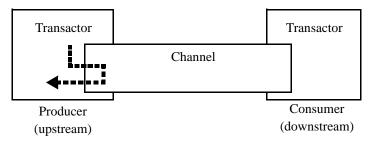

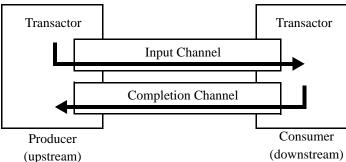

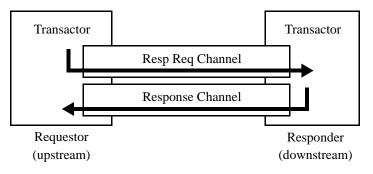

| Channel Completion and Response Models     | 5-8 |

VMM User Guide

| Typical Channel Execution Model                              | 5-8 |

|--------------------------------------------------------------|-----|

| Channel Record/Playback                                      | -12 |

| Completion Using Notification (vmm_notify) 5-                | -14 |

| Notification Service Class 5-                                | -15 |

| Notify Observer                                              | -17 |

| Transport Interfaces in OSCI TLM2.0 5-                       | -18 |

| Blocking Transport                                           | -20 |

| Non-Blocking Transport 5-                                    | -22 |

| Sockets                                                      | -24 |

| Connecting Blocking Components to Non-blocking Components 5- | -26 |

| Generic Payload                                              | -29 |

| Broadcasting Using TLM2.0 5-                                 | -32 |

| Analysis Port Usage with Many Observers                      | -32 |

| Analysis Port Multiple Ports Per Observer                    | -34 |

| Shorthand Macro IDs                                          | -35 |

| Peer IDs                                                     | -36 |

| Interoperability Between vmm_channel and TLM2.05-            | -38 |

| Connecting vmm_channel and TLM interface                     | -38 |

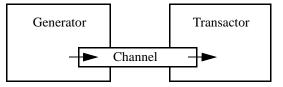

| TLM2.0 Accessing Generators5                                 | -40 |

| Forward Path Non-Blocking Connection                         | -41 |

| Bidirectional Non-Blocking Connection                        | -42 |

| Advanced Usage                                               | -44 |

| Updating Data in Analysis Ports From vmm_notify              | -44 |

| Connect Utility (vmm_connect)5                               | -46 |

| Channel Non-Atomic Transaction Execution                     | -48 |

| Channel Out-of-Order Atomic Execution Model                  | -49 |

| Channel Passive Response                                     | -55 |

| Channel Reactive Response                                    | -57 |

| vmm_tlm_reactive_if                                          | -61 |

# 6 Implementing Tests & Scenarios

| Overview | <br> |

|----------|------|

|          |      |

| Generating Stimulus                          |

|----------------------------------------------|

| Random Stimulus                              |

| Directed Stimulus6-                          |

| Generating Exceptions 6-1                    |

| Embedded Stimulus 6-1                        |

| Controlling Random Generation 6-2            |

| Modeling Scenarios                           |

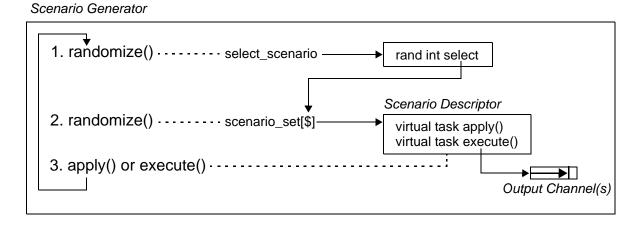

| Architecture of the Generators               |

| Scenario Selection 6-2                       |

| Modeling Generators                          |

| Atomic Generation                            |

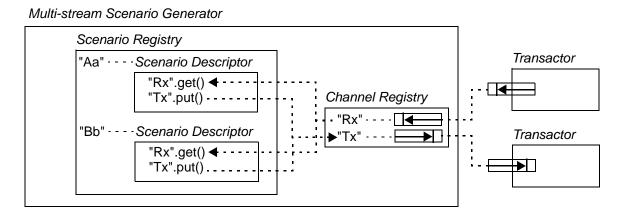

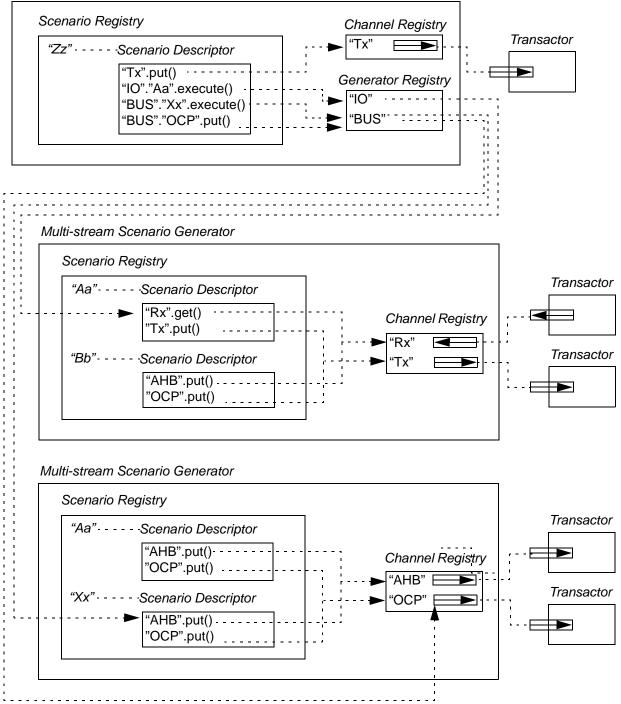

| Multiple-Stream Scenarios6-2                 |

| Single-Stream Scenarios 6-4                  |

| Parameterized Atomic and Scenario Generators |

| Implementing Testcases                       |

| Creating an Explicitly Phased Test           |

| Creating an Implicitly Phased Test           |

| Running Tests                                |

# 7 Common Infrastructure and Services

| Common Object                    |

|----------------------------------|

| Overview                         |

| Setting Object Relationships 7-2 |

| Finding Objects                  |

| Printing and Displaying Objects  |

| Object Traversing                |

| Namespaces                       |

| Message Service                  |

| Overview                         |

| Message Source                   |

| Message Type                     |

| Message Severity                 |

VMM User Guide

| Message Filters                                               | 7-14 |

|---------------------------------------------------------------|------|

| Simulation Handling                                           | 7-14 |

| Shorthand Macros                                              | 7-15 |

| Issuing Messages                                              | 7-16 |

| Filtering Messages.                                           |      |

| Redirecting Message to File                                   | 7-19 |

| Promotion and Demotion                                        |      |

| Message Catcher                                               | 7-20 |

| Message Callbacks                                             |      |

| Stop Simulation Depending Upon Error Number                   |      |

| Class Factory Service                                         |      |

| Overview                                                      |      |

| Modeling a Transaction to be Factory Enabled                  | 7-28 |

| Creating Factories                                            | 7-31 |

| Replacing Factories                                           | 7-32 |

| Factory for Parameterized Classes                             |      |

| Factory for Atomic Generators.                                | 7-36 |

| Factory for Scenario Generators                               |      |

| Modifying a Testbench Structure Using a Factory               |      |

| Options & Configurations Service                              |      |

| Overview                                                      |      |

| Hierarchical Options (vmm_opts)                               | 7-43 |

| Specifying Placeholders for Hierarchical Options              | 7-44 |

| Setting Hierarchical Options                                  | 7-45 |

| Setting Hierarchical Options on Command Line                  | 7-46 |

| Structural Configurations                                     | 7-48 |

| Specifying Structural Configuration Parameters in Transactors | 7-50 |

| Setting Structural Configuration Parameters                   | 7-51 |

| Setting Options on Command Line                               | 7-52 |

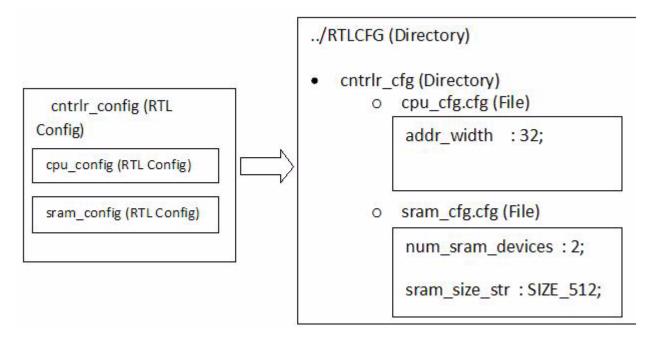

| RTL Configuration                                             |      |

| Defining RTL Configuration Parameters                         |      |

| Using RTL Configuration in vmm_unit Extension                 |      |

| First Pass: Generation of RTL Configuration Files    | 7-56 |

|------------------------------------------------------|------|

| Second Pass: Simulation Using RTL Configuration File | 7-57 |

| Simple Match Patterns                                | 7-58 |

| Overview                                             | 7-58 |

| Pattern Matching Rules                               | 7-59 |

## 8 Methodology Guide

| Recommendations           |

|---------------------------|

| Transactions              |

| Message Service           |

| Transactors               |

| Callbacks                 |

| Channels                  |

| Environments              |

| Tests and Generators      |

| Channels and TLM Ports    |

| Configuration             |

| Rules                     |

| Transactions              |

| Message Service           |

| Transactors               |

| Callbacks                 |

| Channels                  |

| Environments              |

| Notifications             |

| Tests and Generators 8-15 |

# 9 Optimizing, Debugging and Customizing VMM

| Optimizing VMM Components |                   | 9-2 |

|---------------------------|-------------------|-----|

| Garbage-Collecting vmm    | _object Instances | 9-2 |

| Optimizing vmm_log Usage              | . 9-3 |

|---------------------------------------|-------|

| Static vmm_log Instances              | . 9-4 |

| vmm_log Instances in vmm_channel      | . 9-6 |

| Transaction and Environment Debugging | . 9-7 |

| Usage                                 | . 9-7 |

| Built-in Transaction Recording        | . 9-8 |

| Custom Transaction Recording          | 9-12  |

| Customizing VMM                       | 9-16  |

| Adding to the Standard Library        | 9-16  |

| Customizing Base Classes              | 9-18  |

| Symbolic Base Class                   | 9-19  |

| Customizing Utility Classes           | 9-22  |

| Symbolic Utility Class                | 9-23  |

| Underpinning Classes                  | 9-24  |

| Base Classes as IP                    | 9-27  |

# 10 Primers

| Multi-Stream Scenario Generator Primer        | 10-2  |

|-----------------------------------------------|-------|

| Introduction                                  | 10-2  |

| Step1: Creation of Scenario Class             | 10-3  |

| Step 2: Usage of Logical Channels in MSS      | 10-4  |

| Step 3: Registration of MSS in MSSG           | 10-5  |

| Complete Example of a Simple MSSG             | 10-6  |

| Class Factory Service Primer                  | 10-10 |

| Introduction                                  | 10-10 |

| Step 1: Modeling Classes to be Factory Ready  | 10-11 |

| Step 2: Instantiating a Factory in Transactor | 10-14 |

| Step 3: Instantiating a MSS Factory in MSSG   | 10-15 |

| Step 4: Replacing a Factory                   | 10-16 |

| Step 4a: Replacing a Factory by a New One     | 10-17 |

| Step 4b: Replacing a Factory by a Copy        | 10-19 |

| Summary                                       | 10-20 |

| Hierarchical Configuration Primer                       | 10-22 |

|---------------------------------------------------------|-------|

|                                                         |       |

| Step 1: Setting/Getting Global Options                  |       |

| Step 2: Setting/Getting Hierarchical Options            |       |

| Step 3: Getting Structural Options                      |       |

| Step 4: Setting Options                                 |       |

| Step 4a: Setting Options with set_*                     |       |

| Step 4b: Setting Options in Command Line.               |       |

| Step 4c: Setting Options With Command File              |       |

|                                                         |       |

| RTL Configuration Primer                                |       |

|                                                         |       |

| Step 1: Defining RTL Configurations                     | 10-34 |

| Step 2: Nested RTL Configurations                       |       |

| Step 3: Instantiating RTL Configurations                |       |

| Step 4: Generating RTL Configuration File               | 10-37 |

| Step 5: Simulation Using RTL Configuration File.        |       |

|                                                         | 10-39 |

| Implicitly Phased Master Transactor Primer              | 10-40 |

|                                                         |       |

| The Protocol.                                           | 10-40 |

| The Verification Components.                            | 10-41 |

| Step 2: Instantiating and Connecting the DUT            | 10-44 |

| Step 3: Modeling the APB Transaction                    | 10-45 |

| Step 4: Modeling the Master Transactor                  | 10-47 |

| Step 5: Implementing an Observer                        | 10-56 |

| Step 6: Instantiating the Components in the Environment | 10-56 |

| Step 7: Implementing Sanity Test                        | 10-58 |

| Step 8: Adding Debug Messages                           | 10-60 |

| Step 9: Implementing Transaction Generator              | 10-61 |

| Step 10: Implementing the Top-Level File                | 10-61 |

## A Standard Library Classes (Part 1)

| VMM Standard Library Class List                           | A-2     |

|-----------------------------------------------------------|---------|

| factory                                                   |         |

| vmm_atomic_gen#(T)                                        |         |

| <pre><class-name>_atomic_gen_callbacks</class-name></pre> |         |

| vmm_atomic_scenario#(T)                                   |         |

| vmm_broadcast                                             | A-30    |

| vmm_channel                                               | A-44    |

| VMM Channel Relationships                                 | . A-45  |

| VMM Channel Record or Replay                              | . A-47  |

| vmm_channel_typed#(type)                                  | . A-102 |

| vmm_connect#(T,N,D)                                       |         |

| vmm_consensus                                             | A-117   |

| vmm_data                                                  | A-147   |

| vmm_env                                                   | A-207   |

| vmm_group                                                 | A-245   |

| vmm_group_callbacks                                       | . A-247 |

| vmm_log                                                   | . A-254 |

| vmm_log_msg                                               | . A-310 |

| vmm_log_callback                                          | . A-320 |

| vmm_log_catcher                                           | A-326   |

| vmm_log_format                                            |         |

| vmm_ms_scenario                                           | A-341   |

| vmm_ms_scenario_gen                                       | . A-351 |

| vmm_notification                                          | . A-418 |

| vmm_notify                                                | . A-423 |

| vmm_notify_callbacks                                      | . A-448 |

| vmm_notify_observer#(T,D)                                 | . A-451 |

| vmm_object                                                | . A-455 |

| vmm_object_iter                                           | . A-490 |

| vmm_opts                                                  | A-494   |

# B Standard Library Classes (Part 2)

| VMM Standard Library Class List                  | B-2   |

|--------------------------------------------------|-------|

| vmm_phase                                        |       |

| vmm_phase_def                                    | B-18  |

| vmm_rtl_config_DW_format                         |       |

| vmm_rtl_config                                   |       |

| vmm_rtl_config_file_format                       |       |

| vmm_scenario                                     |       |

| vmm_scenario_gen#(T, text)                       | B-95  |

| <class-name>_scenario</class-name>               |       |

| <class-name>_atomic_scenario</class-name>        | B-158 |

| <class-name>_scenario_election</class-name>      | B-161 |

| <class-name>_scenario_gen_callbacks</class-name> | B-170 |

| vmm_scheduler                                    |       |

| vmm_scheduler_election                           | B-191 |

| vmm_ss_scenario#(T)                              | B-204 |

| vmm_simulation                                   | B-205 |

| vmm_subenv                                       | B-214 |

| vmm_test                                         | B-246 |

| vmm_test_registry                                | B-257 |

| vmm_timeline                                     | B-261 |

| vmm_timeline_callbacks                           | B-285 |

| vmm_tlm                                          | B-288 |

| vmm_tlm_extension_base                           | B-290 |

| vmm_tlm_generic_payload                          | B-291 |

| vmm_tlm_analysis_port#(I,D)                      | B-300 |

| vmm_tlm_analysis_export#(T,D)                    | B-302 |

| 'vmm_tlm_analysis_export(SUFFIX)                 | B-304 |

| vmm_tlm_b_transport_export#(T,D)                 | B-305 |

| vmm_tlm_b_transport_port #(I,D)                  | B-310 |

| vmm_tlm_export_base #(D,P)                       | B-313 |

| vmm_tlm_nb_transport_bw_export#(T,D,P)           | B-325 |

| vmm_tlm_nb_transport_bw_port#(I,D,P)             | B-330 |

| vmm_tlm_nb_transport_export#(T,D,P)              | B-333 |

| vmm_tlm_nb_transport_fw_export#(T,D,P)           | B-336 |

| vmm_tlm_nb_transport_fw_port#(I,D,P)               | -341 |

|----------------------------------------------------|------|

| vmm_tlm_nb_transport_port#(I,D,P)B·                | -344 |

| vmm_tlm_port_base#(D,P)                            | -347 |

| vmm_tlm_initiator_socket#(I,D,P)                   | -356 |

| vmm_tlm_target_socket#(T,D,P)B·                    | -359 |

| vmm_tlm_transport_interconnect#(DATA)B·            | -363 |

| vmm_tlm_transport_interconnect_base#(DATA,PHASE)B· | -365 |

| vmm_tlm_reactive_if #(DATA, q_size)                | -370 |

| vmm_unit                                           | -377 |

| vmm_versionB·                                      | -406 |

| vmm_voterB·                                        | -413 |

| vmm_xactorB·                                       | -417 |

| Summary                                            | -417 |

| vmm_xactor_callbacksB·                             | -477 |

| vmm_xactor_iterB·                                  | -478 |

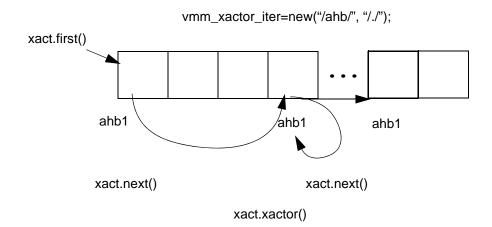

| Using the vmm_xactor_iter Class B-                 | -479 |

| Using the Shorthand Macro `foreach_vmm_xactor()B-  | -480 |

# C Command Line Reference

# D Release Notes

| New Features in VMM User Guide . | <br> | <br> | D-1 |

|----------------------------------|------|------|-----|

| New Base Classes                 | <br> | <br> | D-1 |

# 1

# Introduction

The Verification Methodology Manual (VMM) describes the framework for developing re-usable verification components, sub-environments and environments.

This framework enables higher productivity, reuse and interoperability. VMM provides a class library and defines industry best practices with coding guidelines and rules. The set of guidelines and recommendations paves the path for creating highly efficient transaction-level, constrained-random verification environments using SystemVerilog.

This chapter introduces the main concepts of VMM and its usage models in the following sections:

- Overview

- How to Use This User Guide?

- Basic Concepts of VMM

- What's New in VMM?

- UML Diagram

- Resources

#### Overview

Winning in competitive electronic systems and computer industries requires continuous delivery of high quality and feature-rich products efficiently. To this end, companies constantly seek innovative ways to improve their product development cycles.

Electronic designs have become so complex that design development often relies on ready-made foundations of design and verification blocks. This translates into the requirement of even more complex verification components and environments. With an evershrinking time-to-market window, verification task has become crucial within the complex system and chip design flow.

Companies strive to raise productivity and quality of design verification, streamline and reduce the time it takes to functionally validate a design before fabrication.

We see that today's chip designs require work at many levels of abstractions - high-level abstract models, transaction-level models and gate level netlist.

Design components in many levels of abstractions are frequently reused and expanded. Complications in their integration - be it internal design blocks or third party IPs, together with their verification environments, can unexpectedly delay the development. A well structured verification environment and its components such as verification IPs, should smoothen the path for integration, capability for horizontal and vertical reuse. It should also offer flexibility to create tests for verifying various design configurations, all design operating modes and to generate meaningful information for debugging.

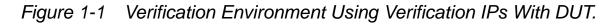

Figure 1-1 is an example for using VIPs for verifying design under test (DUT).

A layered verification architecture such as VMM, uses the following flow to provide flexibility and reusability for development of testbenches for use from block level to chip and system-level verification.

VMM User Guide

Based on a robust verification plan, the test components define specific configurations and requirements. The test information provides the means for transactors to create transactions used by a generator to produce random sequences of transactions. A monitor gathers information from transactions passed through the Design Under Test (DUT). A scoreboard is used to compare observed transactions against expected results. Functional coverage measures the verification requirements that have been actually met by the tests.

When verification engineers build a verification environment on top of a well defined and structured base, the overall development is faster. The verification task can quickly shift to generation of tests and scenarios that stimulate the DUT for unearthing hidden bugs. This is possible only if the actual implementation of a verification environment follows well defined standard guidelines.

#### VMM Benefits:

By using VMM, you can take advantage of the following benefits:

- Avoid common implementation mistakes

- Set clear expectations for verification components and features

- Reduce development time, integration time, and engineers' ramp up time as a result of the known expectations

VMM guidelines help you to develop a well defined and thoughtthrough verification environment that is,

- Easy to use (modular, flexible, customizable)

- Reusable (from block level to top level; from one project to another project)

- Effective (help identify design bugs faster, optimized for superior performances, easy to debug)

#### Ease of Use

- **Modularity:** The layered development of a verification environment lets you create logically partitioned components which can be connected with minimum effort. Each verification component serves a specific purpose and performs a specific set of functions. Components such as verification IPs, form the building blocks of a verification environment.

- **Flexibility:** The test stimulus generation using built-in classes and generators provide complete flexibility for tests that cover the entire functionality of the DUT. The ability to mix implicit and explicit phasing promotes complete flexibility and reuse of verification components. The class factory service provides faster stimulus configuration and reuse. Configuration options provide flexibility to control testbench functionality from the runtime command line.

- **Customization:** The ability to weave a user-defined class library into the standard library allows you to provide highly specialized specific features and capabilities that might be missing in the standard version.

#### Reuse

- **Horizontal**: You can reuse the environment components between projects. This is made possible by the underlying methodology and layered-base architecture, which enables reuse of transactors, verification components and IPs. The compliance tests and standard protocol scenarios can be reused across projects and design implementations.

- Vertical: You can reuse the environment components from blocklevel to subsystem-level and system-level verification. This is made possible by the sub-environment architecture, which enables easy vertical reuse. Transactor phases can be automatically run or called in the environment. This can be implicitly or explicitly controlled respectively. Both explicitly and implicitly phased sub-environments provide this vertical reuse functionality. Implicitly phased environments simplify incorporation of user-defined phases, addition, deletion and reordering of phases in transactors. Multiple timelines, reuse of verification environments and components achieve fine-grained controllability over phasing in a sub-system.

- Diagonal: You can reuse the environment components by various platforms such as, RTL simulation, hardware acceleration and virtual prototyping. The Register Abstraction Layer (RAL) and Hardware Abstraction Layer (HAL) packages provide mechanisms for leveraging testcases and sequences for diagonal reuse. Based on the VMM methodology, these utilities can enhance and ease software debug. RAL provides a unified register-modeling scheme that can be fully reused in various verification environments. HAL provides reuse of existing verification environments for hardware and virtual platforms. For details, see the VMM Application Library user guide.

#### Effectiveness

- **Bug-finding methodology**: Increase in design complexity has made constrained-random test generation and functional coverage analysis an essential part of a verification environment. Constrained random stimulus enables the automation of creating a huge number of test scenarios, which would be impossible to replicate manually. VMM provides sound guidelines for efficient modeling of transactors and constraining transactions. Given tests results, functional coverage analysis provides an indication for test quality and verification goals completion.

- **Optimized for performance**: VMM classes have been architected for peak performance, avoiding run-time interpretations and expression evaluation. Additionally, for further improvements in compilation and simulation performance, you can easily turn off some features that are not used.

- **Debug**: Because intricacy and complexity of testcases and scenarios immensely stress the DUT, it is crucial to leverage from tools and mechanisms for debugging the environment and stimulus at higher level of abstraction. VMM provides consistent use of message logging, recording and viewing of transactions and components states. These facilities help debug of complex designs and tests.

#### How to Use This User Guide?

The following sections provide a practical usage overview of the VMM core functionality:

- Chapter 2, "Architecting Verification Environments", introduces best practices and usage of base classes to create layered verification environment and components. An overview of creating sub-environments, controlling transactors within an environment is reviewed here.

- Chapter 3, "Modeling Transactions", describes guidelines for modeling transactions.

- Chapter 4, "Modeling Transactors and Timelines", reviews the basic transactor modeling techniques with explicit/implicit phasing. Callback mechanisms and shorthand macros usage are reviewed here.

- Chapter 5, "Communication", describes, transaction-level interfaces for transactors and mechanisms for passing transactions/data between transactors such as drivers/monitors and scoreboards. Channel, TLM transport and analysis port and notifications are reviewed here.

- Chapter 6, "Implementing Tests & Scenarios", provides various scenario generation mechanisms including the multiple-stream scenario generator (MSSG) classes and features.

- Chapter 7, "Common Infrastructure and Services", introduces infrastructure and elements of VMM. The vmm\_object class, message services, factory services as well as hierarchical options usage and configuration setup are discussed here.

- Chapter 8, "Methodology Guide", provides the methodology for extending the VMM standard library.

- Chapter 9, "Optimizing, Debugging and Customizing VMM", provides various coding recommendations to optimize performance and describes embedded system functions in VCS helping VMM transaction debug.

- Chapter 10, "Primers", provides procedural examples for understanding MSSG, class factory service, hierarchical options, RTL configurations and modeling a master transactor.

- Appendix A, "Standard Library Classes (Part 1)" and Appendix C, "Command Line Reference" include references to standard library classes and command line switches.

#### **Basic Concepts of VMM**

VMM includes a proven industry-standard verification methodology based on an object-oriented programming model supported by SystemVerilog.

VMM class library provides common infrastructure and services which enable a quick start in building an advanced verification environment. It provides application packages for improving productivity. Using a well-defined and easily accessible library such as VMM, guarantees interoperability of verification components and environments from different sources.

#### **Building Blocks - Class Library**

This section provides an overview of the main VMM class library and utilities used as building blocks for basic verification components. For a complete list and functionality, see Appendix A, "Standard Library Classes (Part 1)" and Appendix C, "Command Line Reference".

#### vmm\_object

The vmm\_object virtual base class is used as the common base class for all VMM classes. Classes derived from vmm\_object and any VMM base class can form a searchable and named object hierarchy.

For details, see Chapter 7, "Common Infrastructure and Services".

#### vmm\_data [Transactions/Data model]

The  $vmm_data$  virtual base class is extended to model transactions. This class includes a set of properties, methods and macros required to deal with transactions for different types of designs. For example: allocate(), copy(), display().

For details on vmm\_data and transaction modeling, see Chapter 3, "Modeling Transactions".

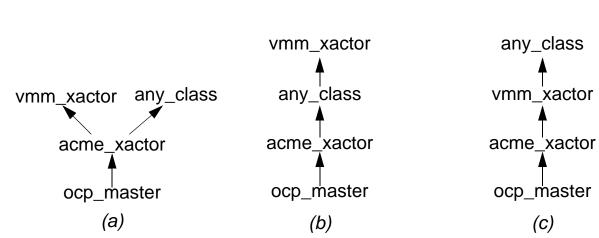

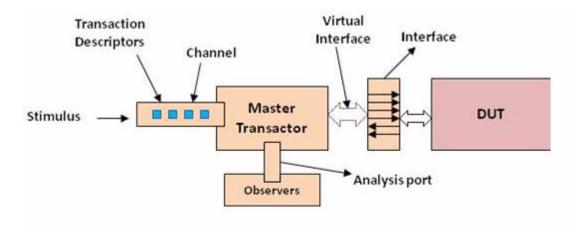

#### vmm\_xactor Transactors, such as Drivers, Monitors]

The vmm\_xactor virtual base class is extended to model all kinds of transactors such as, bus-functional models, monitors and generators. This class includes properties and methods used to configure and control different types of transactors. For details on vmm\_xactor class, see Chapter 4, "Modeling Transactors and Timelines".

#### `vmm\_channel [Communication, Transaction Passing]

The `vmm\_channel class defines a transaction-level interface class that serves as the conduit for transaction exchange between transactors in the verification environment. The channel class includes properties and methods used to control the flow of transactions between transactors. For example: full\_level(), size(), is\_full().

For details on channel class, see Chapter 5, "Communication".

# vmm\_tlm\_\* [Communication, Transport Interface Mechanisms]

The vmm\_tlm\* classes emulate the following OSCI TLM 2.0 transport interfaces: blocking, non-blocking, socket, generic payload and analysis port.

For details on vmm\_tlm\_\* class, see Chapter 5, "Communication".

#### vmm\_ms\_scenario and vmm\_ms\_scenario\_gen

The general purpose MSSG controls, schedules and randomizes multiple stimulus scenarios. Multi-stream scenarios are able to inject stimulus or react to response on multiple channels. You can also create hierarchical scenarios that are composed of other multistream scenarios.

For details, see Chapter 6, "Implementing Tests & Scenarios".

#### vmm\_class\_factory [VMM factory service]

The factory service provides a simple set of APIs to replace any kind of object, transaction, scenario, or transactor with a similar object as required by a specific test.

For details on the factory services, see Chapter 7, "Common Infrastructure and Services".

#### `vmm\_callback

Callbacks are used to incorporate new mechanisms and routines once a verification environment and its components have been developed. Callback routines are registered in the main routines and executed (or called back) at certain user-defined simulation points. The `vmm\_callback macro defines a callback class that contains methods to be executed when registered callbacks are called.

For details on callbacks, see Chapter 4, "Modeling Transactors and Timelines".

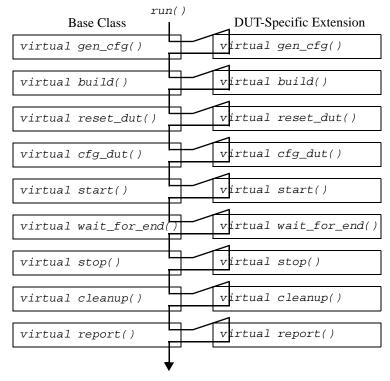

# Verification Environments and Execution Control Phases

Phasing refers to the overall progression of a simulation. Execution of a simulation is divided into predefined phases. All verification components within an environment are synchronized to the phases so that their actions can be coordinated throughout. VMM supports explicit, implicit, and mixed phasing.

For details, see Chapter 2, "Architecting Verification Environments".

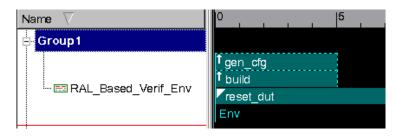

#### vmm\_group

The vmm\_group class is extended to create sub-environment and environments with implicit phasing. All transactors instantiated in this environment have their phases automatically called at the appropriate time.

For details, see Chapter 4, "Modeling Transactors and Timelines".

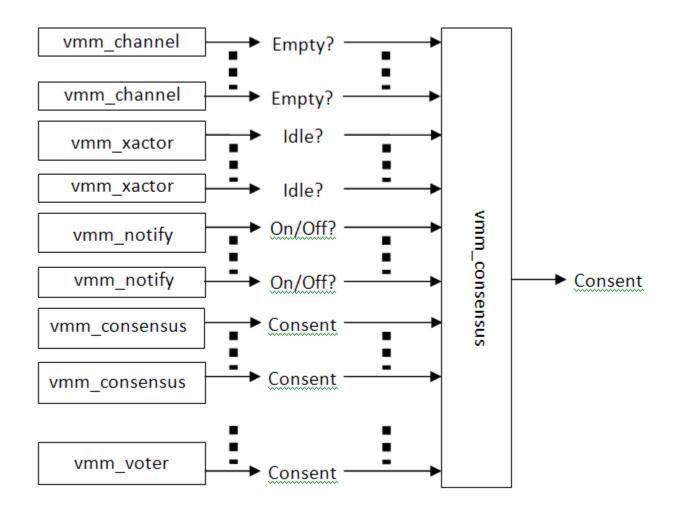

#### vmm\_consensus

The vmm\_consensus object offers a well-defined service for collaboration on deciding test completion and ending simulation.

For details, see Chapter 7, "Common Infrastructure and Services".

#### vmm\_subenv

The vmm\_subenv virtual base class is extended to create explicitlyphased sub-environments. All transactors and sub-environments instantiated in this environment must have their phase methods explicitly called at the appropriate time.

For details on vmm\_subenv, see Chapter 2, "Architecting Verification Environments".

#### vmm\_env

The vmm\_env virtual base class is extended to create explicitlyphased environments. This class includes a set of predefined methods that correspond to specific simulation phases. All transactors and sub-environments instantiated in this environment must have their phases methods explicitly called at the appropriate time. For details on vmm\_env, see Chapter 2, "Architecting Verification Environments".

#### **Enhanced Verification Performance and Flexibility**

VMM provides comprehensive ways of configuring transactors, components and verification environments which aid improving flexibility and performance.

#### vmm\_test

The vmm\_test class is extended to implement testcases. It is where tests add scenarios, override factories and modify connections. The vmm\_test class can be used for standalone tests or for concatenating multiple implicitly-phased tests within a simulation run to improve overall simulation efficiency.

For details, see Chapter 6, "Implementing Tests & Scenarios".

#### vmm\_opts

The vmm\_opts object allows to define and set configuration options. Options can be set from the simulator command line, file or within the code itself. These options can be set on a per-instance basis or globally by using regular expressions.

For details, see Chapter 7, "Common Infrastructure and Services".

# Debug and Analysis: Message Service Class and Transaction Debug

Transactors, scoreboards, assertions, environment and testcases use messages to report regular, debug, or error information.

#### vmm\_log [message service class]

The vmm\_opts object provides rich set of severity handling utilities and macros for comprehensive reporting, formatting and analysis.

For details, see Chapter 7, "Common Infrastructure and Services".

#### **Transaction and Environment Debug**

Transaction and components include built-in recording facility that enable transaction and environment debugging. The vmm\_data class members which are registered using shorthand macros are easily viewed on a waveform.

Additional notification status of various components are viewed on the waveform timeline. Additionally, it is possible to determine the level of debug information that is required to be shown.

For details, see Chapter 9, "Optimizing, Debugging and Customizing VMM".

#### What's New in VMM?

The latest VMM version incorporates new classes and features to enhance the functionality and flexibility in verification environment development.

Some highlights of the new features are,

- The class factory service supplements the existing factory usage and further enables faster stimulus configuration and reuse. It declares and overrides any kind of objects such as, transactions, scenarios, transactors and interfaces.

- The concepts of implicit phasing and timelines for enhanced flexibility and reuse of verification components have been implemented. This augments the current explicit phasing capabilities. Implicit phasing enables components to control their own status.

- Configuration options service including methods to control testbench functionality from the runtime command line, have been enhanced. It supports configuration database and configuration settings from a file. New RTL configuration support ensures alignment with testbench configuration. It supports randomized RTL configuration capabilities.

- Multiple name spaces and hierarchical naming are possible through a new common base class which provides a powerful search functionality.

- TLM-2.0 is now supported, it is complemented with channelbased connectivity and communication mechanisms.

- Extended parameterization features support many base classes in the standard library such as channels and generators.

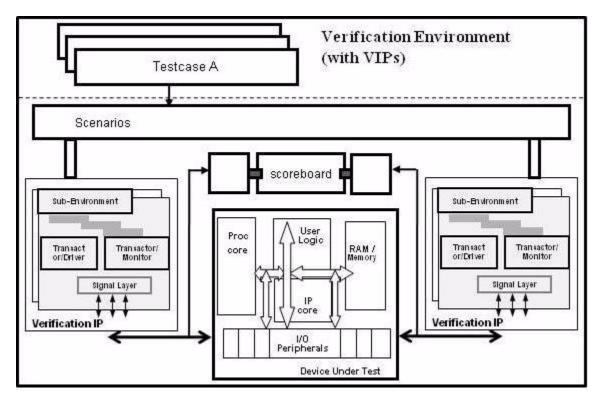

#### **UML** Diagram

The following diagram shows the relationship between the various VMM classes.

#### Resources

The following resources are available for VMM users:

VMM Central (<u>www.vmmcentral.org</u>) is an online community for VMM users to:

- Share information

- Exchange ideas

- Obtain VMM related news and updates

- Receive support on VMM related inquiries

- Learn new tricks and techniques from VMM users and experts

Note: VMM users are strongly encouraged to register as a member. Usage scenarios and recommendations of various VMM features are discussed in the following primers:

- Composing Environments

- Writing Command Layer Master Transactors

- Writing Command Layer Slave Transactors

- Writing Command Layer Monitor Transactors

- Using Command Layer Transactors

- Using the Register Abstraction Layer

- Using the Memory Allocation Manager

- Using the Data Stream Scoreboard

Applications are documented in the following user guides:

- VMM Register Abstraction Layer User Guide

- Verification Planner User Guide

- VMM Hardware Abstraction Layer User Guide

- VMM Scoreboarding User Guide

- VMM Performance Analyzer User Guide

VMM User Guide 1-20

# Architecting Verification Environments

This chapter contains the following sections:

- Overview

- Testbench Architecture

- Constructing and Controlling Environments

- Architecting Verification IP (VIP)

- Advanced Usage

#### **Overview**

The challenge in transitioning from a procedural language such as Verilog or VHDL, to a language like SystemVerilog is in making effective use of the object-oriented programming model. When properly used, these features can greatly enhance the reusability of testbench components.

This section covers the following topics:

- Guidelines to maximize the usage of features that create verification components and verification environment satisfying the needs of all the testcases applied to the DUT.

- Guidelines to model transactors with appropriate data sampling interfaces, verification sub-environments and environment.

- Guidelines to model test stimulus and response checking mechanisms.

The guidelines in this chapter are based on the VMM Standard Library specified in Appendix A, "Standard Library Classes (Part 1)". Though the methodology and approaches here can be implemented in a different class library, using a well-defined and openly accessible library guarantees interoperability of the various verification components.

#### **Testbench Architecture**

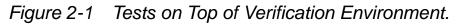

This section describes recommended testbench architecture. You implement testcases on top of a verification environment as shown in Figure 2-1. The verification environment implements the

abstraction and automation functions that help minimize the number and complexity of testcases written. You can reuse the verification environment without modifications with as many testcases as possible to minimize the amount of code required to verify the DUT.

For a given DUT, there might be several verification environments as you can observe in Figure 2-1. However, you should minimize the number of environments and build testcases on top of existing environments as far as possible.

Another important aspect of this methodology is to minimize the number of lines that are required to implement a testcase. Investing in a few or one verification environment to save even a single line in the thousands of potential testcases is worthwhile.

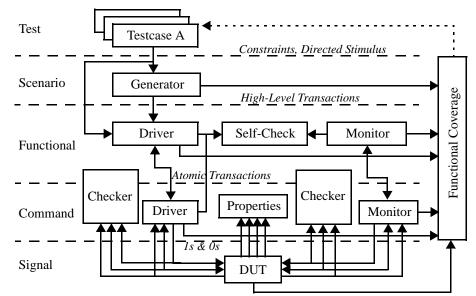

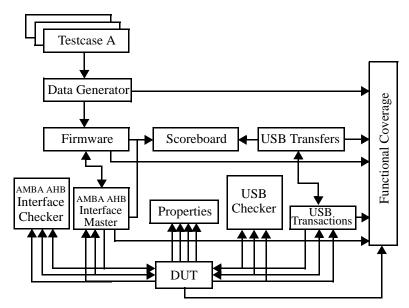

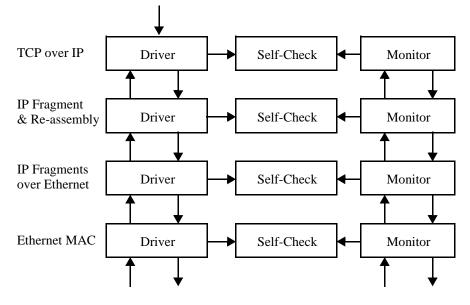

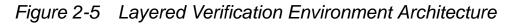

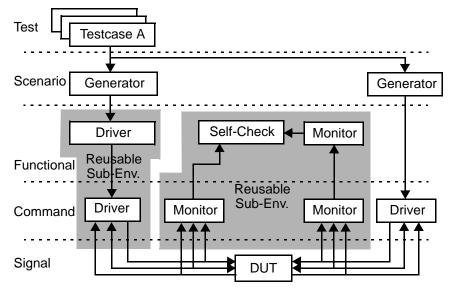

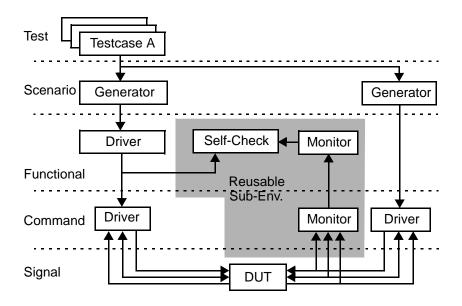

Verification environments are not monolithic. As shown in Figure 2-2, environments are composed of layers. As in Figure 2-3, they mirror the abstraction layers in the data processed by the design. You design them to meet the various requirements of testcases written for it. Each layer provides a set of services to the upper layers or testcases, while abstracting it from the lower-level details.

Figure 2-2 Layered Verification Environment Architecture

Figure 2-3 Application of Layered Testbench Architecture.

Though Figure 2-2 shows testcases interacting only with the upper layers of the verification environment, they can by-pass various layers to interact with various components of the environment or the DUT to accomplish their goals.

VMM User Guide

Testcases are a combination of additional constraints on generators, new random scenario definitions, synchronization mechanisms between transactors, error injection enablers, DUT state monitoring and directed stimulus.

A verification environment must enable support for all testcases required to verify the DUT without modification. Therefore, you must assemble it with carefully designed, reusable components.

You never implement complete verification environments in one pass. You do not deliver them to the testcase writers as a finished product that implements a complete set of specifications the verification architects provide.

Rather, they evolve to meet the increasingly complex requirements of the testcases being written and responses checked. A trivial directed testcase with no self-checking layers is added to evolve the verification environment into a full-fledged, self-checking, constrained-random one.

The methodology in this chapter allows this evolution to occur in a backward-compatible fashion to avoid breaking existing testcases. It describes enabling the vertical and diagonal reuse of test environments such as block-to-top reuse.

Layered architecture makes no assumption of the DUT model. It can be an RTL, gate-level model or transaction-level model. You can also simulate the DUT natively in the same simulator as the verification environment. Else, co-simulate it on a different simulator or emulate on a hardware platform. This top-level module contains the design portion of the simulation. Various elements of the signal layer or DUT are accessible via crossmodule references through the top-level module. It is unnecessary to instantiate the top-level module anywhere. For guidelines on implementing the signal layer, see "Signal Layer" on page 6.

The environment leverages generic functionality from a verification environment base class. It refers to the signal layer or various DUT elements via cross-module references into the top-level module.

Each testcase instantiates this environment. For guidelines on implementing the top-level environment class, see "Constructing and Controlling Environments" on page 28.

The vmm\_test describes the testcase procedure. For guidelines on implementing testcases, see Chapter 6, "Implementing Tests & Scenarios".

## **Signal Layer**

This layer provides signal-level connectivity to the DUT. Then the signal layer provides pin name abstraction enabling verification components that are used and unmodified with different DUTs or different implementation models of the same DUT. For example, consider an RTL description of the DUT using *interface* constructs and a gate-level description of the same DUT using individual bit I/O signals. This layer might abstract synchronization and timing of synchronous signals with respect to a reference signal.

The signal abstraction this layer provides is accessible. All layers and testcases above it might use it where signal-level access is required. However, you should implement verification environments and testcases in terms of the highest possible level services that lower layers provide and avoid accessing signals directly (unless imperative).

Command-layer transactors have a physical-level interface composed of individual signals. You bundle all signals pertaining to a physical protocol in a single *interface* construct hence allowing this interface to be virtual and easily bound to the DUT. For details, see Chapter 4, "Modeling Transactors and Timelines".

#### Example 2-1 Packaging of Interface Declaration

```

interface mii_if(...);

...

endinterface: mii_if;

...

class mii_phy_layer ...;

virtual mii_if.phy_layer sigs;

...

endclass: phy_layer

```

If an *interface* declaration already exists for the protocol signals as in RTL design code and it meets (or can be made to meet) all of the subsequent requirements outlined in this section, then you should physically move to the file packaging the transactors that use them. In most cases, different *interface* declarations will exist or you will require them.

To minimize the collisions between *interface* names and other identifiers in the global name space, they use a "likely-unique" prefix. That prefix is the same as various prefixes you use for related transactors. You use the name of the *package* that optionally contains the transactors that use the *interface* as the prefix to further document the association.

Verification components use the same interface constructs regardless of their perspective or role on the interface. Some components drive signals, others simply monitor their value.

Depending on the functionality of the verification component the signal being driven or monitored might be different. Example 2-2 shows how to use *interface* for bundling *inouts* to represent a physical interface signal regardless of the direction of the signal.

Example 2-2 Verification Interface Signal Declaration

```

interface mii_if();

inout tx_clk;

inout [3:0] txd;

inout [3:0] txd;

inout tx_en;

inout tx_err;

inout rx_clk;

inout [3:0] rxd;

inout [3:0] rxd;

inout rx_dv;

inout rx_err;

inout crs;

inout col;

...

endinterface: mii_if

```

Example 2-3 shows how to use clocking blocks for modeling synchronous interfaces. This approach avoids race conditions between a design and a verification environment and allows the environment to work with RTL and gate-level models of the DUT without modifications or timing violations.

You should use parameters to retain default values such as bus width, setup or hold. These values can be overridden when instantiating this interface.

Example 2-3 Synchronous Interface Signal Declaration

```

interface mii_if;

...

parameter setup_time = 5ns;

parameter hold_time = 3ns;

```

VMM User Guide

```

clocking mtx @(posedge tx_clk);

default input #setup_time output #hold_time;

output txd, tx_en, tx_err;

endclocking: tx

clocking mrx @(posedge rx_clk);

default input #setup_time output #hold_time;

input rxd, rx_dv, rx_err;

endclocking: rx

...

endinterface: mii_if

```

This implementation style allows changing the set-up and hold time on a per instance basis to meet the needs of the DUT without modifying the interface declaration itself. Modifying the interface declaration has global effects. However, you can specify parameters for each interface instance.

```

Example 2-4 Specifying Set-Up and Hold Times for Synchronous Signals

```

Different transactors might have different perspectives on a set of signals. One might be a master driver, another a reactive monitor or a slave driver and yet another a passive monitor. Certain interfaces have different types of proactive transactors such as arbiters and agents. You must declare a *modport* for each of their individual perspectives to ensure that each transactor uses the interface signals appropriately.

Example 2-5 Module Port Declarations

```

output col, ...);

modport passive(clocking ptx,

clocking mrx,

input crs,

input col, ...);

...

endinterface: mii_if

```

# You should implement transactors as separate *class* definitions.

This is described in Chapter 4, "Modeling Transactors and Timelines". They interface to the physical signals through *virtual modports*.

# You should not define transactions and transactors as *tasks* inside the *interface* declaration.

The *interface* declaration you share with the RTL design might contain such tasks. However, the verification environment uses them.

Note: The signals declared in the interface create a bundle of wires. The direction of information on the individual wires depends on the role of the agent you connect to those wires. For example, wires carrying address information are outputs for a bus master. However, they are inputs for a bus slave or bus monitor.

You should specify the direction of asynchronous signals directly in the *modport*, for you do not sample them via *clocking* blocks.

You should specify the direction of synchronous signals in the *clocking* block and include the entire clocking block in the *modport* port list.

Thus, synchronous signals are already visible and their directions are already enforced.

Transactors must enable delay of the driving or sampling of synchronous signals by an integer number of cycles. You can specify the number of cycles by referring to the *clocking* block that defines the synchronization of an interface, without knowing the details of the synchronization event specified in the *clocking* block declaration.

Because all signals in a *clocking* block are visible, adding the synchronous signals to the *modport* port list is redundant. Furthermore, referring to synchronous signals through their respective *clocking* blocks highlights their synchronous nature, associated sampling and driving semantics. Example 2-6 shows how to use *clocking* block positive edge for writing BFMs.

Example 2-6 Waiting for the Next Cycle on the tx Interface

```

foreach (bytes[i]) begin

...

@(this.sigs.mtx);

this.sigs.mtx.txd <= nibble;

...

@(this.sigs.mtx);

this.sigs.mtx.txd <= nibble;

...

end

```

You might have written verification components and the design using different *interface* declarations for the same physical signals. To connect the verification components to the design, it is necessary to map two separate *interface* instances to the same physical signals. This can be accomplished with continuous assignments for unidirectional signals and aliasing for bidirectional signals. Example 2-8 shows how to model a top-level module that contains multiple interfaces.

#### Example 2-7 Mapping Two Different Interface Instances to the Same Physical Signals

```

interface eth_tx_if; // RTL Design Interface

bit clk;

wire [3:0] d;

logic en;

logic err;

logic crs;

logic col;

endinterface: eth_tx_if

module tb_top;

bit tx_clk;

eth_tx_if mii_dut(); // Design Interface Instance

mii_if mii_xct(); // Transactor Interface Instance

assign mii_dut.clk = tx_clk; // Unidirectional

assign mii_xct.tx_clk = tx_clk;

alias mii_xct.txd = mii_dut.d; // Inout

...

endmodule: tb_top

```

Clock signals must be scheduled in the design regions. Therefore, you must generate them outside the verification environment in an *always* or *initial* block. You should not generate clock signals inside verification components or transactors because they need to be scheduled in the reactive region.

There are race conditions between initial scheduling of the *initial* and *always* blocks implementing the clock generators and those implementing the design.

Delaying the clock edges to a point in time until you have scheduled each *initial* and *always* block at least once, eliminates those race conditions.

It is a good practice to wait for the duration of a few periods of the slowest clock in the system before generating clock edges.

Example 2-8 Clock Generation in Top-Level Module

Using a two-state data type ensures that you initialize the clock signals to a known, valid value.

If a four-state logic type such as logic, is used to implement the clock signals, the initialization of those signals to 1'b0 might be considered as an active negative edge by some design components.

The alternative of leaving the clock signals at 1' bx while you delay the clock edges -- as in the previous rule might cause functional problems if you propagate these unknown values.

Clock signals can be synchronized with an asynchronous relationship inherently. This is required to simulate with a fixed initial phase and a common timing reference such as the internal simulation time. You should randomize the relationship of such clocks to ensure that problems related to asynchronous clock domains can surface during simulation.

Example 2-9 Randomizing Clock Offsets

```

integer tx_rx_offset; // 0-99% T lag

integer T = 100;

initial

```

```

begin

. . .

tx_rx_offset = {$random} % 100;

#20; // No clock edge at T=0

tx_clk = 0;

rx clk = 0;

. . .

fork

begin

#(T * (tx_rx_offset % 100) / 100.0);

forever begin

\#(T/2) rx_clk = 1;

\#(T/2) rx_clk = 0;

end

end

join_none

forever begin

#(T/2) tx_clk = 1;

#(T/2) tx_clk = 0;

end

end

```

To enable tests to control the random clock relationship values, you should randomize random clock relationship values to enable tests to control these values as part of the testcase configuration descriptor. You will then assign to the appropriate variable in the clock generation code, the randomized value in the extension of the explicit  $vmm\_env::reset\_dut()$  method or the implicit reset phase.

Note: It is possible to pass these values at run-time in the command line by using the vmm\_opts facility. For details, see Chapter 7, "Common Infrastructure and Services".

#### **Command Layer**

The command layer typically contains bus-functional models, physical-level drivers, monitors and checkers associated with the various interfaces and physical-level protocols present in the DUT.

Regardless of how you model the DUT, the command layer provides a consistent, low-level transaction interface to it. At this level, you define a transaction as an atomic data transfer or command operation on an interface such as a register write, transmission of an Ethernet frame or fetching of an instruction.

You typically define atomic operations using individual timing diagrams in interface specifications. Reading and writing registers is an example of an atomic operation. The command layer provides methods to access registers in the DUT. This layer has a mechanism that bypasses the physical interface to peek and poke the register values directly into the DUT model.

Note: The implementation of direct-access, register read/write driver is dependent upon the implementation of the DUT.

A driver actively supplies stimulus data to the DUT. A *proactive* driver is in control of the initiation and type of the transaction.

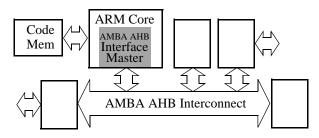

Whenever the higher layers of the verification environment supply a new transaction to a proactive driver, the transaction on the physical interface gets immediately executed. For example, a master busfunctional model for an AMBA AHB interface is a proactive driver. A *reactive* driver is not in control of the initiation or type of the transaction but might be in control of some aspect of the timing of its execution such as the introduction of wait states.

The DUT initiates the transaction and the reactive driver supplies the required data to successfully complete the transaction. For example, a program memory interface bus-functional model is a reactive driver. The DUT initiates read cycles to fetch the next instruction and the bus-functional model supplies new data in the form of an encoded instruction.

A monitor reports observed high-level transaction timing and data information. A *reactive* monitor includes elements to generate the low-level handshaking signals to terminate an interface and successfully complete a transaction.

Unlike a reactive driver, a reactive monitor does not generate transaction-level information. For example, a Utopia Level 1 receiver is a reactive monitor. It receives ATM cells without generating additional data. But it generates a cell to enable signal back to the DUT for flow control.

A *passive* monitor simply observes all signals involved in the transaction without any interference. A passive monitor is suitable for monitoring transactions on an interface between two DUT blocks in a system-level verification environment.

While interfacing with an RTL or gate-level model, the physical abstraction layer might translate transactions to or from signal assertions and transitions.

While interfacing with a transaction-level model, the physical abstraction layer becomes a pass-through layer.

In both cases, the transaction-level interface that is present in the higher layers remains the same. Thereby it allows the same verification environment and testcases to run on different models of the DUT at different levels of abstraction without any modifications.

The services the command layer provides might not be limited to atomic operations on external interfaces around the DUT. You can provide these services on internal interfaces for missing or temporarily removed design components.

For example, embedded memory acting as an elastic buffer for routed data packets can be replaced with a testbench component. This helps track and check packets in and out of the buffer rather than only at DUT endpoints. Or, an embedded code memory in a processor can be replaced with a reactive driver that allows on-thefly instruction generation instead of using pre-loaded static code. Alternatively, embedded processor can be replaced with a transactor allowing the testbench to control the read and write cycles of the processors, instead of indirectly through code execution.

When replacing DUT components with a transactor, you must take care that it is configured to an equivalent functionality. For example, if the transactor implements a superset of the transactions or timing compared to the DUT component then it should be configured to restrict its functionality to match that of the DUT component.

## **Functional Layer**

The functional layer provides the necessary abstraction layers to process application-level transactions and verify the correctness of the DUT.

Unlike interface-based transactions of the physical layer, the transactions in the functional layer might not have a one-to-one correspondence with an interface or physical transaction.

Functional transactions are abstractions of the higher-level operations performed by a major subset of the DUT or the entire DUT beyond the physical interface module.

A single functional transaction might require the execution of dozens of command-layer transactions on different interfaces. It depends on the completion status of some physical transactions to retry some transactions or delay others.

Functional layer transactors can be proactive, reactive or passive:

- A proactive transactor controls the initiation and the kind of transaction. It typically supplies some or all of the data the transaction requires.

- A reactive transactor neither controls the initiation nor kind of transaction. It is only responsible for terminating the transaction appropriately by supplying response data or handshaking. Reactive transactors report the observed transaction data they are reacting to.

- Passive transactors monitor transactions on an interface and simply report the observed transactions.

# You should sub-layer the functional layer according to the protocol structure.

For example, a functional layer for a TCP/IP over Ethernet device should contain a sub-layer to transmit and if necessary, retry an Ethernet frame. You must provide additional sub-layers to encapsulate IP fragments into Ethernet frames, fragment large IP frames into smaller IP fragments that fit into a single Ethernet frame and encapsulate a TCP packet into an IP frame.

The functional layer is also responsible for configuring the DUT according to a configuration descriptor. This layer includes a functional coverage model for the high-level stimulus and response transactions. It records the relevant information on all transactions this layer processes or creates.

Transactors are implemented using *vmm\_xactor*.

#### Example 2-10 Modeling Transactor

```

class mii_phy_layer extends vmm_xactor;

...

endclass: mii_phy_layer

...

class tb_env extends vmm_env;

```

```

mii_phy_layer phy;

mii_phy_layer phy;

...

virtual function void build();

...

this.phy = new(...);

...

endfunction: build

...

virtual task start();

...

this.phy.start_xactor();

...

endtask: start

endclass: tb_env

program test;

tb_env env = new;

...

endprogram

```

Though different labels are used to refer to stimulus transactors ((driver) from response transactors (monitor), they only differ in the direction of the information flow.

The interfaces on both sets of transactors are transaction-level interfaces. In all other aspects, drivers and monitors operate in the same way and you should implement using the same techniques and offer the same type of capabilities.

## **Scenario Layer**

This layer provides controllable and synchronizable data and transaction generators. By default, they initiate broad-spectrum stimulus to the DUT. You can use different generators or managers to supply data and transactions at the various sub-layers of the functional layer. This layer also contains a DUT configuration generator. VMM comes with a general purpose MSSG that aims at controlling, scheduling and randomizing multiple scenarios in parallel. MSSG is a superset of Atomic generators and Scenario Generators. For details, see "Multiple-Stream Scenarios" on page 6-29.

Atomic generation consists of randomizing individually constrained transactions. Atomic generators are suitable for generating stimulus where putting constraints on sequences of transactions is not necessary. They are suitable for quick randomization bring up and simulation performance.

For example, the configuration description generator is an atomic generator. For details, see "Modeling Scenarios" on page 24.

Scenarios are sequences of random transactions with certain relationships. Each scenario represents an interesting sequence of individual transactions to hit a particular functional corner case.

For example, a scenario in an Ethernet networking operation is a sequence of frames with a specified density i.e., a certain portion of the time the Ethernet line is busy sending/receiving.Otherwise, the line is idle.

MSSG generates scenarios in random order and sequence. It produces a stream of transactions that correspond to the generated scenarios. It initiates scenarios defined by and under the direction of a particular testcase. It produces a stream of transactions that correspond to the requested scenarios.

You might bypass this layer partially or completely by the test layer above it depending on the amount of directedness the testcase requires. Consequently, you must enable turning off generators either from the beginning or in the middle of a simulation to allow the injection of directed stimulus.

# You must enable the restarting of the generator to resume the generation of random stimulus after a directed stimulus sequence.

Typically, MSGG is a transactor with several transaction-level interfaces and possibly with input interfaces to create scenarios that can react to certain DUT conditions.

As in all other aspects, generators behave like transactors. You should implement them using the same techniques and offer the same type of capabilities.

## **Test Layer**

Testcases involve a combination of modifying constraints on generators, definition of new random scenarios, synchronization of different transactors and creation of random or directed stimulus.

This layer might provide additional testcase-specific self-checking that is not provided by the functional layer at the transaction level. For example, it checks where correctness will depend on timing with respect to a particular synchronization event introduced by the testcase.

The environment instantiates all necessary transactors and manages their execution. Therefore, the environment that encapsulates them should preferably be instantiated in a *program* block.

However, instantiation in *module* is still possible. As an added benefit, the *program* block implementing the testcase is able to access any required element of the verification environment. You instantiate the environment in a local variable to prevent initialization race conditions.

#### You should create test by extending the vmm\_test.

Example 2-11 shows a simple way of writing test. For details, see "Generating Stimulus" on page 2".

Example 2-11 Testcase Accessing Verification Environment Elements

```

program test;

...

tb_env env = new;

initial

begin

env.run();

end

endprogram: test

```

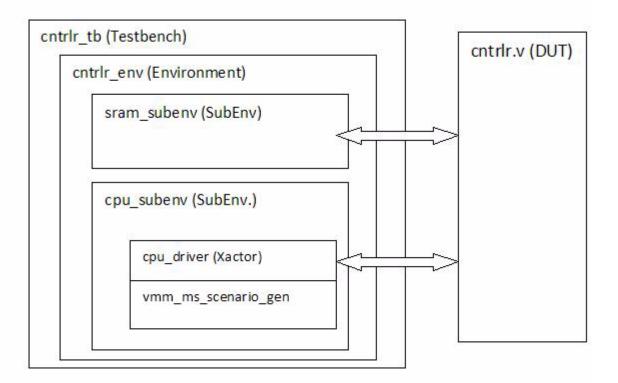

## Sub-environments

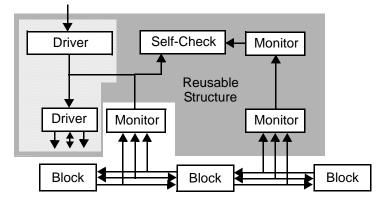

VMM promotes the design of transactors and self-checking structures so that you can reuse them in different environments. For example, you can construct system-level verification environments of the same basic components used to construct block-level environments.

When you construct a system-level environment using the same basic components used to construct block-level environments, VMM arranges, combines and connects these same basic components the same way. For example, a block-level self-checking structure complete with stimulus and response monitors, and scoreboard might be identical in the system-level environment. This occurs if the system-level, self-checking mechanism, consists of checking the behavior of the individual blocks which compose it.

Similarly, different block-level environments might need similar combinations of basic components. For example, a complete TCP/ IP stimulus stack.

You can minimize the overall effort and maintenance if you construct block and system-level environments by reusing complex testbench structures, which already provide a significant portion of the required functionality.

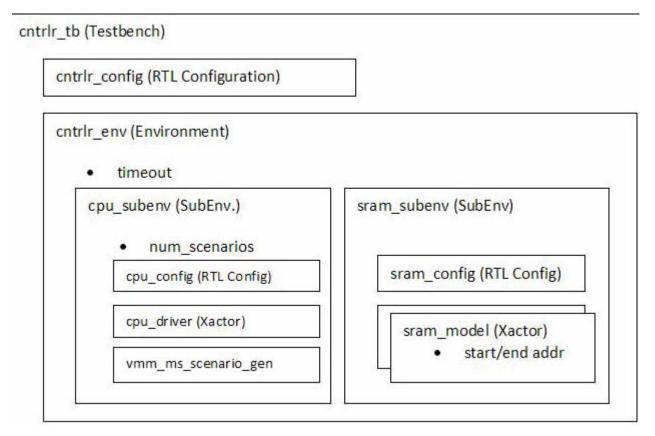

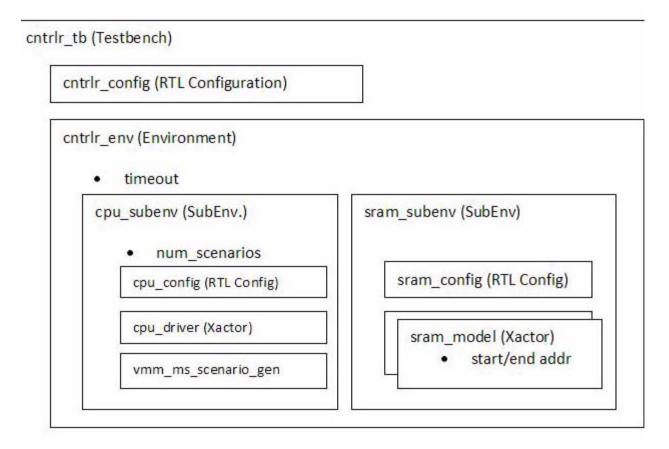

In this section, a "sub-environment" refers to a subset of a verification environment that is reusable in another verification environment. Sub-environments are not individual transactors. They are composed of two or more interconnected transactors potentially linked to additional elements such as, scoreboard, file I/O mechanism or response generator that implement a specific functionality.

You must identify and architect reusable sub-environments in the initial stages while designing and architecting a verification environment. You cannot reuse sub-environments if a verification environment is not designed to take advantage of it.

The remainder of this section provides some guidelines and hints to help identify the architect reusable sub-environments.