### Department of Electrical and Computer Engineering The University of Texas at Austin

EE 460N Spring 2015 Y. N. Patt, Instructor Ben Lin, Kishore Punniyamurthy, Will Hoenig TAs Final Exam May 15, 2015

Name:

| Problem 1 (10 points): |

|------------------------|

| Problem 2 (10 points): |

| Problem 3 (10 points): |

| Problem 4 (20 points): |

| Problem 5 (25 points): |

| Problem 6 (30 points): |

| Problem 7 (25 points): |

| Total (130 points):    |

Note: Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space provided.

Note: Please be sure your name is recorded on each sheet of the exam.

Please sign the following. I have not given nor received any unauthorized help on this exam.

Signature:\_\_\_\_\_

Name:\_\_\_\_\_

Problem 1 (10 points)

**Part a (5 points):** An application that is 96% parallelizable is executed on a single processor in 2.5 hours. If the application is allowed to run with an unlimited number of processors, what is the lower bound on its execution time?

**Part b** (**5 points**): We wish to use even parity to protect each single-byte value we transmit, by adding a ninth bit. If we wish to transmit 01010101, what nine bits should we transmit?

If we wish to transmit 00110111, what nine bits should we transmit?

# Problem 2 (10 points)

The following program fragment operates on 8-bit IEEE-like floating point format. Your job is to figure out how many bits for exponent, how many bits for fraction, and to complete the table below. BIAS (excess) is 4. Rounding is unbiased nearest.

```

float B;

float A = 5/16;

for(int i=0; i < 6; ++i)

{

B = A/(1<<i);

}

```

Note that (1<<i) is equal to  $2^i\,$  .

Each row of the table below specifies the **results** of one iteration of the for loop. Note that some iterations cause underflow and/or inexact exceptions, in addition to producing a value for B.

Hint: Some representations of B are subnormal.

| Iteration | <b>Binary Representation</b> | Floating point representation | Except    | ions    |

|-----------|------------------------------|-------------------------------|-----------|---------|

| (i)       | of B                         | of B                          | Underflow | Inexact |

| 0         |                              |                               | NO        | NO      |

| 1         |                              |                               | NO        | NO      |

| 2         |                              |                               | NO        | NO      |

| 3         |                              |                               | NO        | YES     |

| 4         |                              |                               |           |         |

| 5         |                              |                               |           |         |

# Problem 3 (10 points)

Consider a tightly coupled multiprocessor system with two processors (P1 and P2). Each processor has its own private data cache.

The Goodman "write-once" snoopy cache protocol we studied in class is used for maintaining cache coherence. On a cache miss, if another processor has the line in the modified state, its cache supplies the line to the processor having the cache miss.

The table shows the behavior of the system for eight consecutive data accesses, all to location A. Assume the caches are initially empty. Each access is performed by either P1 or P2. Your job: complete the entries in the table.

Note: In the last column, the entry "No one" means there is no need to supply the cache line because the private cache had a cache hit.

| Instance | P1 Executes a | P2 executes a | Bus Activity | Cache line  |

|----------|---------------|---------------|--------------|-------------|

|          | LOAD/STORE    | LOAD/STORE    |              | supplied by |

| 1        | LOAD A        |               |              |             |

| 2        |               |               | P2 READS A   | MEMORY      |

| 3        | STORE A       |               | P1 WRITES A  | NO ONE      |

| 4        |               |               |              | P1 CACHE    |

| 5        |               |               | P1 READS A   | P2 CACHE    |

| 6        |               | STORE A       |              |             |

| 7        |               | STORE A       |              |             |

| 8        | LOAD A        |               |              |             |

### Problem 4 (20 points)

Recall the Tomasulo problem on midterm two. The rules are very similar here.

Instructions are of the form ADD Rx,Ry,Rz and MUL Rx,Ry,Rz, as discussed in class. Each instruction requires a fetch cycle, a decode cycle, some number of execution cycles, and a final cycle to store the result into a register and/or a reservation station entry that is waiting for that result. A result is available to subsequent instructions after it is stored in a register or reservation station entry. Functional units not pipelined. Reservation stations are assigned from the top down. The top-most reservation station with both data entries valid is the next to be processed. Each instruction remains in its reservation station until its result is stored.

The only differences in the problem today are the following: There may be more than one adder and more than one multiplier. We have changed the number of execution cycles to 3 cycles for the adder and 4 cycles for the multiplier. All the adder(s) share three reservation stations. All the multiplier(s) likewise share three reservation stations. Finally, each instruction has two unique source registers; that is, for all instructions OP Rx,Ry,Rz,  $y \neq z$

A program fragment, consisting of five instructions, is executed on this machine. The first instruction is fetched in cycle 1. Part of your job: Complete the table below, i.e., the complete specification of the five instructions.

| Instruction | Opcode | DR | SR1 | SR2 |

|-------------|--------|----|-----|-----|

| 1           |        |    |     |     |

| 2           |        |    | R0  |     |

| 3           |        |    |     |     |

| 4           |        |    |     |     |

| 5           | ADD    |    |     | R3  |

Information on the next page will help you identify the five instructions executed.

The table below shows in what cycles the function units are executing. An  $\mathbf{E}$  in row ADD indicates that in that cycle at least one adder is executing. An  $\mathbf{E}$  in row MUL indicates that at least one multiplier is executing.

|     | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|-----|---|---|---|---|---|---|---|---|---|----|----|----|

| ADD |   |   |   |   |   | E | Е | E | E | Е  | Е  |    |

| MUL |   |   | E | E | E | E | E | E | E | Е  |    |    |

Initial values in the Register File are shown below:

| R0 | 1 | - | 7 |

|----|---|---|---|

| R1 | 1 | - | 4 |

| R2 | 1 | - | 5 |

| R3 | 1 | - | 9 |

|    |   |   |   |

The rest of your job is as follows: Provide the missing entries in the Register File and in the reservation stations for the adder(s) and multiplier(s) at the end of cycle X and at the end of cycle 10. Identify which cycle is X.

| $A G = G = 1 \cdot \mathbf{V}$ |  |

|--------------------------------|--|

| After Cycle X                  |  |

| Inter Cycle It                 |  |

Register File:

| R0 |   |   |   |

|----|---|---|---|

| R1 |   |   |   |

| R2 | 1 | - | 5 |

| R3 |   |   |   |

Reservation Stations for adder(s):

| α        |   |   |   | 1 |   |   |

|----------|---|---|---|---|---|---|

| $\beta$  | - | - | - | - | - | - |

| $\gamma$ | _ | _ | _ | _ | _ | _ |

Reservation Stations for multiplier(s):

| $\pi$    | 1 |   |   |   |   |   |

|----------|---|---|---|---|---|---|

| $\sigma$ | 1 | - | 5 |   |   |   |

| au       | _ | _ | _ | _ | - | _ |

Finally, how many adders and multipliers are there?

| Adders | Multipliers |  |

|--------|-------------|--|

|        |             |  |

### After Cycle 10

**Register File:**

| R0 | 1 | _ | 20 |

|----|---|---|----|

| R1 |   |   |    |

| R2 | 1 | I | 14 |

| R3 | 0 |   |    |

Reservation Stations for adder(s):

| $\alpha$ |   |   |   | 1 | _ | 5 |

|----------|---|---|---|---|---|---|

| $\beta$  | - | - | - | - |   | I |

| $\gamma$ | 1 |   |   |   |   |   |

Reservation Stations for multiplier(s):

| $\pi$    | - | I | _ | - | - | - |

|----------|---|---|---|---|---|---|

| $\sigma$ |   |   |   | 1 | - | 9 |

| $\tau$   | - | - | _ | - | - | - |

**Problem 5** (**25 points**): An LC-3b supporting VAX-style virtual memory has 16-bit virtual addresses, 11-bit physical addresses, and a 128-byte page size. User space occupies virtual memory locations 0x0000 to 0x7FFF; system space occupies locations 0x8000 to 0xFFFF.

Each PTE has the following format (Note: The PFN size is not given):

A user space TLB contains two entries, with perfect LRU replacement.

The computer executes the following three instructions:

LDW R0,R1,#0 ADD \_\_\_\_\_\_ STW R0,R2,#0

UBR:

You can assume no exceptions occur during their processing.

Before execution: The TLB contains one valid entry: Page x14, 10000110 PC: x4000 R2: x1278

Your job: Complete the table and fill in the four additional boxes.

| N | Virtual | Physical | Data    | TLB Hit      |

|---|---------|----------|---------|--------------|

| A | Address | Address  |         |              |

|   |         |          | x81     |              |

| х | x8880   |          |         |              |

|   |         | x200     |         |              |

|   |         |          |         |              |

|   |         |          | x88     |              |

| x | 3064    |          | xABCD   |              |

|   |         |          |         |              |

|   |         |          |         |              |

|   |         | x190     |         |              |

|   |         | x124     | x87     |              |

|   |         |          | xABCE   |              |

|   | SBR:    |          | Initial | value of R1: |

|   |         |          |         |              |

15

1 1

0

.

.

#### Problem 6 (30 points)

A 64KB byte-addressable memory is 4-way interleaved. The processor/memory bus is 16 bits wide, and each memory access takes 4 cycles. There is only 1 channel.

The address bits are specified as shown below:

| - | 15 11 | 10 3            | 2 1                       | 0           |

|---|-------|-----------------|---------------------------|-------------|

|   | Rank  | Chip<br>Address | Bank (Interleave)<br>Bits | Byte on Bus |

128 64-bit signed integers are stored in a 1024-byte array, starting at address x0000. We wish to know how many of these integers are negative.

The sign of a 64-bit signed integer is specified by its sign bit, i.e., the most significant bit of the most significant byte of the integer. Thus, to determine the signs of all 128 integers, we only need to load and examine 128 bytes from memory, as opposed to all 1024 bytes of the array.

Part a: What is the minimum number of cycles needed to read these 128 bytes from memory?

**Part b:** A smart engineer realized the time to read these 128 bytes from memory can be decreased if two bytes of padding were added to each array element (i.e. the entire array now requires 1280 bytes instead of 1024 bytes). What's the minimum number of cycles needed to read the 128 bytes from memory after padding has been added?

**Part c:** Assume our algorithm for determining the number of negative integers processes the 128 integers in sequential order. As previously stated, the algorithm only needs to access 1 byte per integer to determine its sign. The processor includes an initially empty 8KB, 4-way set associative data cache having a line size of 16 bytes. Compute the cache hit ratio when the algorithm processes 64-bit integers without padding.

Compute the cache hit ratio when the algorithm processes 64-bit integers with padding.

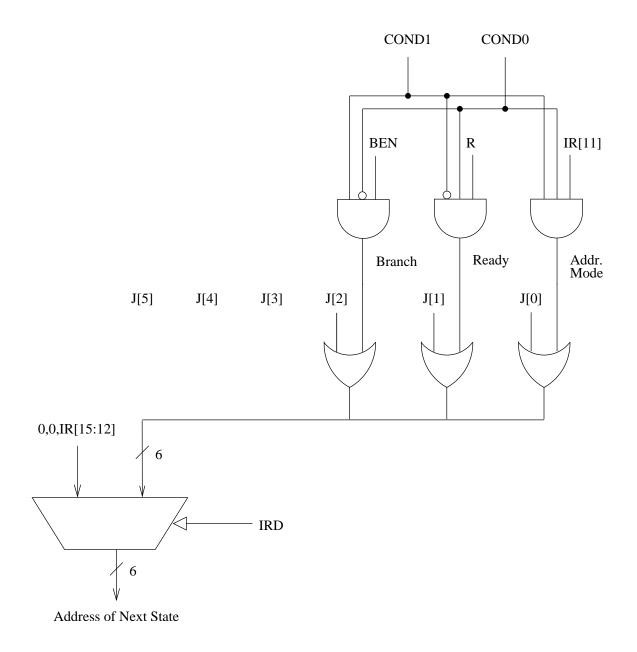

**Problem 7 (25 points):** We wish to augment the LC-3b with a new instruction LTA, which copies a linked list into a sequential array. (LTA: Linked To Array). The LTA instruction can be of either of the following two formats:

|     | 15 |   |   | 12 | 11  |    | 9 | 8   |      | 6 | 5 | 4   |    |    |             | 0 |

|-----|----|---|---|----|-----|----|---|-----|------|---|---|-----|----|----|-------------|---|

| LTA | 1  | 0 | 1 | 0  |     | DR |   |     | SR 1 |   | 1 |     | in | nm | 5           |   |

|     | 15 |   | 1 | 12 | .11 |    | 9 | . 8 |      | 6 | 5 | . 4 | 3  | 2  | 1           | 0 |

| LTA | 1  | 0 | 1 | 0  |     | DR | - |     | SR 1 |   | 0 | 0   | 0  |    | 8 <b>R2</b> |   |

An example may help explain what is going on:

|       |       |   |       |       |   | x6010 | x0001 |

|-------|-------|---|-------|-------|---|-------|-------|

| x4000 | x0001 |   | x5002 | x0004 |   |       | x0002 |

|       | x0002 |   |       | x0005 |   |       | x0003 |

| ·     | x0003 | - |       | x0006 | - |       | x0004 |

| ·     | x5002 |   |       | x0000 |   |       | x0005 |

| l     |       | ] |       |       |   |       | x0006 |

|       |       |   |       |       |   |       |       |

Linked list to be copied

Resulting sequential array

SR1 contains the memory address of the head of the linked list (x4000, in the above example). Each node in the linked list consists of n consecutive 16-bit words, followed by the pointer to the next node. SR2 or the immediate field contains the value for n (in the above example, n=3).

LTA copies the nodes into sequential locations of memory, starting with the location specified by DR (in the above example, x6010). Note: there is no need to copy the pointers, since the nodes are now stored in sequential memory locations.

Assume that DR, SR1, and SR2 (if SR2 is being used) all refer to different registers. Assume that all the linked list nodes and the destination array are aligned in memory and do not overlap.

Note: After processing the LTA instruction, SR1 contains the null pointer, since the linked list no longer exists; DR contains the address of the next location following the sequential array (in the above example x601C). The condition code will be set to Z.

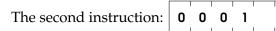

Part A. Implement the state machine.

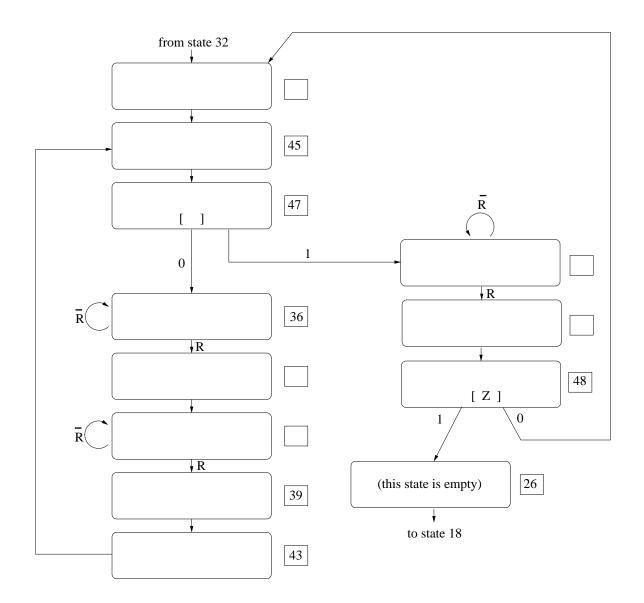

**Part B.** Complete the data path diagram by augmenting the DRMUX and adding any other necessary structures and control signals inside the provided box. Note: we have given you a counter which can be incremented or reset to 0. **Hint:** A **xor** A = 0

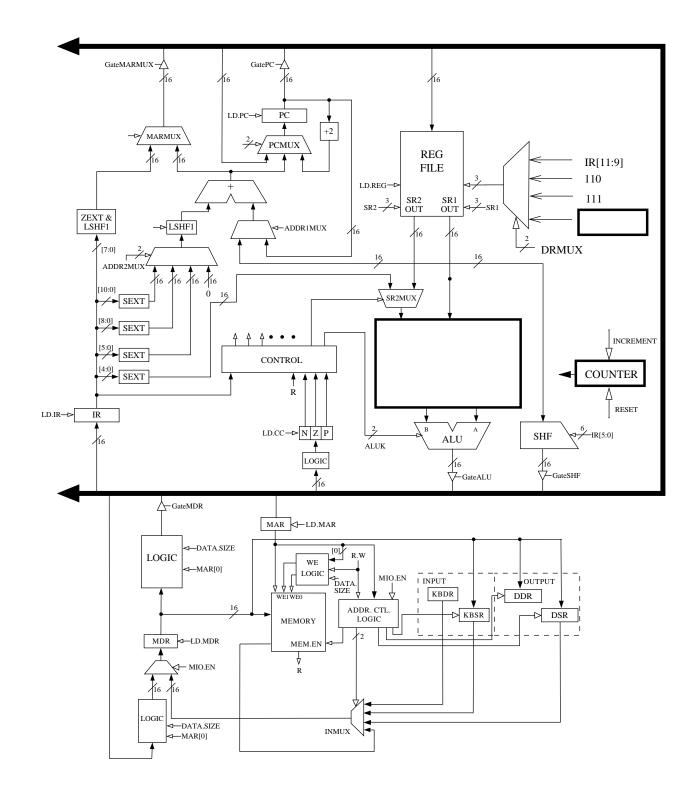

Part C. Complete the microsequencer. Hint: you will need to add one AND gate and one OR gate.

|                  | 15 | 14      | 13 | 12   | 11 | 10  | 9    | 8 | 7    | 6   | 5     | 4    | 3    | 2          | 1         | 0 |

|------------------|----|---------|----|------|----|-----|------|---|------|-----|-------|------|------|------------|-----------|---|

| ADD⁺             |    | 00      | 01 | I    |    | DR  |      |   | SR 1 |     | 0     |      | 0    |            | SR2       |   |

| ADD⁺             |    | 00      | 01 | I    |    | DR  | 1    |   | SR 1 |     | 1     |      |      | 'nm        |           |   |

| AND⁺             |    | 01      | 01 | I    |    | DR  |      |   | SR1  |     | 0     | 0    | 0    |            | SR2       |   |

| AND⁺             |    | 01      | 01 |      |    | DR  |      |   | SR 1 |     | 1     |      | ir   | nm         |           |   |

| BR               |    | 00      | 00 | I    | n  | z   | р    |   |      |     |       | offs |      |            |           |   |

| JMP              |    | 11      | 00 | I    |    | 000 |      | B | ase  |     |       | 1    | 000  | 000        | <br> <br> |   |

| JSR              |    | 1       | 00 | I    | 1  |     |      |   |      | PCo | offse | et11 |      | 1          |           |   |

| JSRR             |    | 01      | 00 |      | 0  | 0   | 0    | B | ase  | R   |       | 1    | nnn  | 000        |           |   |

| LDB⁺             |    | 1       | 10 | I    |    | DR  |      | B | ase  |     |       |      |      | set        |           |   |

| LDW <sup>+</sup> |    | 01      | 10 | 1    |    | DR  | 1    | В | ase  |     |       | I    | 1    | et6        |           |   |

| $LEA^{+}$        |    |         | 10 | 1    |    | DR  |      |   |      |     | PC    | offs | et9  |            |           |   |

| NOT⁺             |    |         | 01 | 1    |    | DR  | I    |   | SR   |     | 1     |      | 1    | <b>111</b> | 1         |   |

| RET              |    | 1       | 00 | 1    |    | 000 | 1    |   | 111  | 1   |       |      |      | 000        |           |   |

| RTI              |    | 10      | 00 | 1    |    | 1   |      |   | 000  |     |       | 000  |      | 1          |           |   |

| $LSHF^{+}$       |    | 1       |    | 1    |    | DR  |      |   | SR   |     | 0     | 0    |      | imo        | unt       | 4 |

| $RSHFL^{+}$      |    | 11      | 01 | 1    |    | DR  |      |   | SR   |     | 0     | 1    | C    |            | unt       | 4 |

| $RSHFA^{+}$      |    | ่<br>11 |    | 1    |    | DR  |      |   | SR   | 1   | 1     | 1    |      |            | unt       |   |

| STB              |    | 00      | 11 | 1    |    | SR  |      |   | ase  | R   |       | k    | off  | set        | 5<br>1    |   |

| STW              |    | 01      | 11 | 1    |    | SR  |      | B | ase  | R   |       |      | offs | et6        |           |   |

| TRAP             |    | 11      | 11 | 1    |    | 00  | 00   |   |      |     | tre   | apv  | ec   | t8         |           |   |

| XOR⁺             |    | 10      | 01 | <br> |    | DR  |      |   | SR1  |     | 0     | 0    | 0    |            | SR2       |   |

| XOR⁺             |    | 10      | 01 | <br> |    | DR  |      |   | SR   |     | 1     |      | i    | mm         | 5         |   |

| not used         |    | 10      | 10 | I    |    |     |      |   |      |     |       |      |      |            |           |   |

| not used         |    | 10      | 11 | 1    |    | ı   | <br> |   |      |     | I     |      |      | <br>       |           |   |

Figure 1: LC-3b Instruction Encodings

| Table 1: Data path control signals |                  |                                 |  |  |  |  |  |

|------------------------------------|------------------|---------------------------------|--|--|--|--|--|

| Signal Name                        | Signal Values    |                                 |  |  |  |  |  |

| LD.MAR/1:                          | NO(0), LOAD(     | 1)                              |  |  |  |  |  |

| LD.MDR/1:                          | NO(0), LOAD(1)   |                                 |  |  |  |  |  |

| LD.IR/1:                           | NO(0), LOAD(     | 1)                              |  |  |  |  |  |

| LD.BEN/1:                          | NO(0), LOAD(     | 1)                              |  |  |  |  |  |

| LD.REG/1:                          | NO(0), LOAD(     | 1)                              |  |  |  |  |  |

| LD.CC/1:                           | NO(0), LOAD(     |                                 |  |  |  |  |  |

| LD.PC/1:                           | NO(0), LOAD(     | 1)                              |  |  |  |  |  |

| GatePC/1:                          | NO(0), YES(1)    |                                 |  |  |  |  |  |

| GateMDR/1:                         | NO(0), YES(1)    |                                 |  |  |  |  |  |

| GateALU/1:                         | NO(0), YES(1)    |                                 |  |  |  |  |  |

| GateMARMUX/1:                      | NO(0), YES(1)    |                                 |  |  |  |  |  |

| GateSHF/1:                         | NO(0), YES(1)    |                                 |  |  |  |  |  |

| PCMUX/2:                           | PC+2(0)          | ;select pc+2                    |  |  |  |  |  |

|                                    | BUS(1)           | ;select value from bus          |  |  |  |  |  |

|                                    | ADDER(2)         | ;select output of address adder |  |  |  |  |  |

| DRMUX/1:                           | 11.9(0)          | ;destination IR[11:9]           |  |  |  |  |  |

|                                    | R7(1)            | ;destination R7                 |  |  |  |  |  |

| SR1MUX/1:                          | 11.9(0)          | ;source IR[11:9]                |  |  |  |  |  |

|                                    | 8.6(1)           | ;source IR[8:6]                 |  |  |  |  |  |

| ADDR1MUX/1:                        | PC(0), BaseR(1   |                                 |  |  |  |  |  |

|                                    |                  | ,                               |  |  |  |  |  |

| ADDR2MUX/2:                        | ZERO(0)          | ;select the value zero          |  |  |  |  |  |

|                                    | offset $6(1)$    | ;select SEXT[IR[5:0]]           |  |  |  |  |  |

|                                    | PCoffset9(2)     | ;select SEXT[IR[8:0]]           |  |  |  |  |  |

|                                    | PCoffset11(3)    | ;select SEXT[IR[10:0]]          |  |  |  |  |  |

| MARMUX/1:                          | 7.0(0)           | ;select LSHF(ZEXT[IR[7:0]],1)   |  |  |  |  |  |

|                                    | ADDER(1)         | ;select output of address adder |  |  |  |  |  |

| ALUK/2:                            | ADD(0), AND(     | (1), XOR(2), PASSA(3)           |  |  |  |  |  |

| MIO.EN/1:                          | NO(0), YES(1)    |                                 |  |  |  |  |  |

| <b>R.W</b> /1:                     | RD(0), WR(1)     |                                 |  |  |  |  |  |

| DATA.SIZE/1:                       | BYTE(0), WORD(1) |                                 |  |  |  |  |  |

| LSHF1/1:                           | NO(0), YES(1)    | NO(0), YES(1)                   |  |  |  |  |  |

Table 1. Data path control signals

| Table 2: Microsequencer control signals |                                                                                               |  |  |  |  |  |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Signal Values                           |                                                                                               |  |  |  |  |  |  |  |  |

|                                         |                                                                                               |  |  |  |  |  |  |  |  |

| $\text{COND}_0$                         | ;Unconditional                                                                                |  |  |  |  |  |  |  |  |

| $\text{COND}_1$                         | ;Memory Ready                                                                                 |  |  |  |  |  |  |  |  |

| $\operatorname{COND}_2$                 | ;Branch                                                                                       |  |  |  |  |  |  |  |  |

| $COND_3$                                | ;Addressing Mode                                                                              |  |  |  |  |  |  |  |  |

| NO, YES                                 |                                                                                               |  |  |  |  |  |  |  |  |

|                                         | Signal Va<br>COND <sub>0</sub><br>COND <sub>1</sub><br>COND <sub>2</sub><br>COND <sub>3</sub> |  |  |  |  |  |  |  |  |

Table 2: Microsequencer control signals

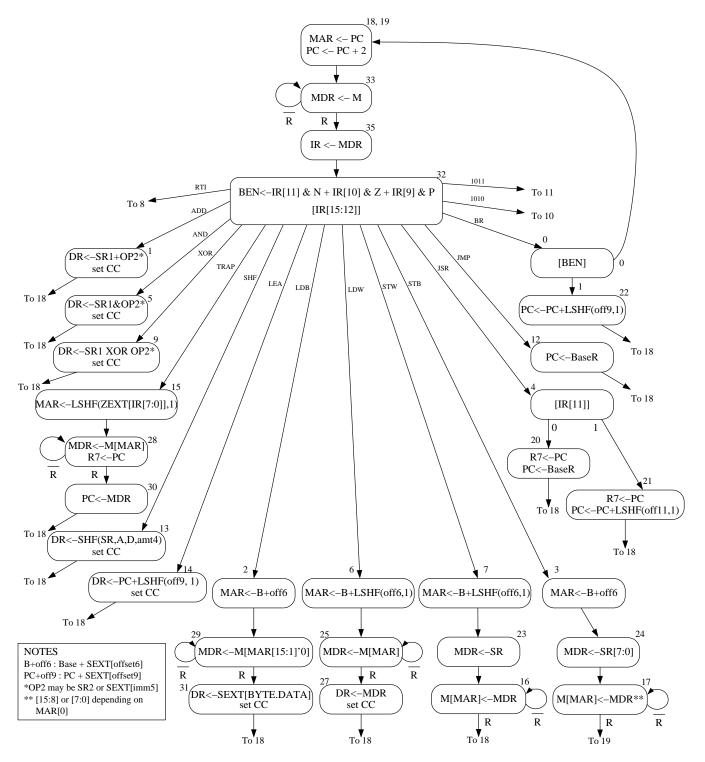

Figure 2: A state machine for the LC-3b

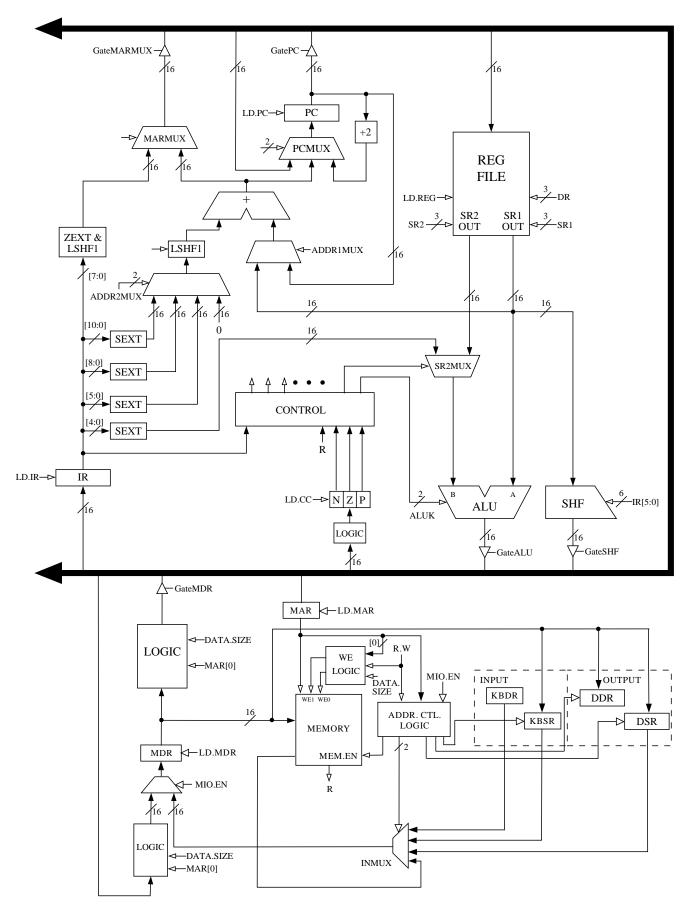

Figure 3: The LC-3b data path

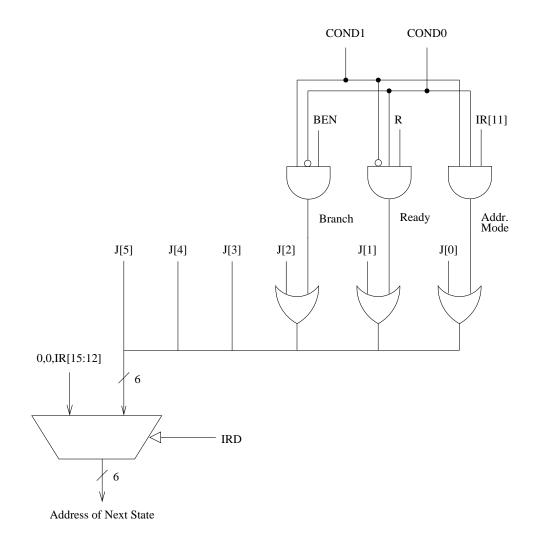

Figure 4: The microsequencer of the LC-3b base machine