# **DatasheetArchive.**....

#### **Request For Quotation**

Order the parts you need from our real-time inventory database. Simply complete a request for quotation form with your part information and a sales representative will respond to you with price and availability.

**Request For Quotation**

Your free datasheet starts on the next page.

More datasheets and data books are available from our homepage: http://www.datasheetarchive.com

June 1990

54FCT/74FCT374A Octal D Flip-Flop with TRI-STATE Outputs

## 54FCT/74FCT374A Octal D Flip-Flop with TRI-STATE® Outputs

### **General Description**

The 'FCT374A is a high-speed, low-power octal D-type flipflop featuring separate D-type inputs for each flip-flop and TRI-STATE outputs for bus-oriented applications. A buffered Clock (CP) and Output Enable ( $\overline{OE}$ ) are common to all flip-flops.

#### **Features**

- NSC 54/74FCT374A is pin and functionally equivalent to IDT 54/74FCT374A

- Buffered positive edge triggered clock

- TRI-STATE outputs for bus-oriented applications

- TTL input and output level compatible

- TTL inputs accept CMOS levels

- High current latch up immunity

- I<sub>OL</sub> = 48 mA (commercial) and 32 mA (military)

- Electrostatic discharge protection ≥ 2 kV

- Inherently radiation tolerant

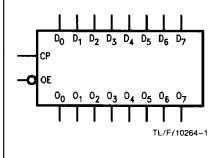

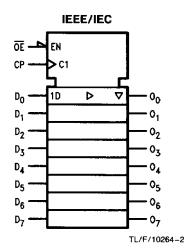

## **Logic Symbols**

**Pin Names**

$D_0 - D_7$

O<sub>0</sub>-O<sub>7</sub>

CP

OE

#### **Pin Assignment** for DIP, Flatpak and SOIC ŌĒ 20 ۰v<sub>cc</sub> 2 19 00 -07 3 Do 18 - D7 4 D₄ 17 - D<sub>6</sub> 5 -0<sub>6</sub> 0. 16 -0<sub>5</sub> 02. 6 15 - D<sub>5</sub> 7 $D_2$ 14 8 D3 • 13 - D₄ 03-9 -0₄ 12 GND 10 ·CP 11

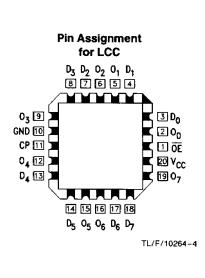

**Connection Diagrams**

TRI-STATE® is a registered trademark of National Semiconductor Corporation. FACT™ is a trademark of National Semiconductor Corporation.

Description

TRI-STATE Output Enable Input

Data inputs

Clock Pulse Input

**TRI-STATE Outputs**

TL/F/10264-3

### **Functional Description**

The 'FCT374A consists of eight edge-triggered flip-flops with individual D-type inputs and TRI-STATE outputs. The buffered clock and buffered Output Enable are common to all flip-flops. The eight flip-flops will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (CP) transition. With the Output Enable ( $\overline{OE}$ ) LOW, the contents of the eight flip-flops are available at the outputs. When the  $\overline{OE}$  is HIGH, the outputs go to the high impedance state. Operation of the  $\overline{OE}$  input does not affect the state of the flip-flops.

## **Truth Table**

|    | Outputs             |   |    |

|----|---------------------|---|----|

| Dn | D <sub>n</sub> CP Ō |   | On |

| н  |                     | L | Н  |

| L  |                     | L | L  |

| X  | X                   | н | Z  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial Z = High Impedance

- LOW-to-HIGH Transition

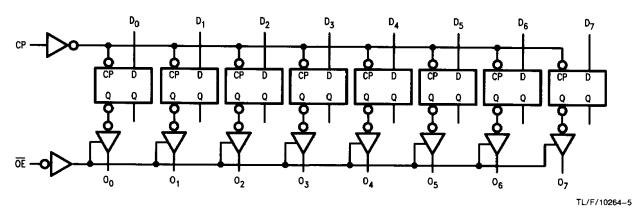

## Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Terminal Voltage                            |                          |

|---------------------------------------------|--------------------------|

| with Respect to GND (V <sub>TERM</sub> )    | <b>- - ·</b> · · - · · · |

| 54FCTA                                      | -0.5V to 7.0V            |

| 74FCTA                                      | -0.5V to 7.0V            |

| Temperature under Bias (T <sub>BIAS</sub> ) |                          |

| 74FCTA                                      | -55°C to +125°C          |

| 54FCTA                                      | -65°C to +135°C          |

| Storage Temperature (T <sub>STG</sub> )     |                          |

| 74FCTA                                      | -55°C to +125°C          |

| 54FCTA                                      | -65°C to +150°C          |

| Power Dissipation (P <sub>T</sub> )         | 0.5W                     |

| DC Output Current (I <sub>OUT</sub> )       | 120 mA                   |

| •• • • • • • • • • • • •                    |                          |

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. National does not recommend operation of FACT FCT circuits outside databook specifications.

#### **Recommended Operating Conditions**

| Supply Voltage (V <sub>CC</sub> )       |                       |

|-----------------------------------------|-----------------------|

| 54FCTA                                  | 4.5V to 5.5V          |

| 74FCTA                                  | 4.75V to 5.25V        |

| Input Voltage                           | $0V$ to $V_{CC}$      |

| Output Voltage                          | 0V to V <sub>CC</sub> |

| Operating Temperature (T <sub>A</sub> ) |                       |

| 54FCTA                                  | -55°C to +125°C       |

| 74FCTA                                  | 0°C to +70°C          |

| Junction Temperature (T <sub>J</sub> )  |                       |

| CDIP                                    | 175°C                 |

| PDIP                                    | 140°C                 |

#### **DC Characteristics for 'FCTA Family Devices**

Typical values are at  $V_{CC} = 5.0V$ , 25°C ambient and maximum loading. For test conditions shown as Max, use the value specified for the appropriate device type: Com:  $V_{CC} = 5.0V \pm 5\%$ ,  $T_A = 0$ °C to +70°C; Mil:  $V_{CC} = 5.0V \pm 10\%$ ,  $T_A = -55$ °C to +125°C,  $V_{HC} = V_{CC} - 0.2V$ .

| Symbol           | Parameter                                    | 54FCTA/74FCTA                        |                                      |                              | Units | Conditions                                                                                                                   |                                                                                                                                                             |

|------------------|----------------------------------------------|--------------------------------------|--------------------------------------|------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           |                                              | Min                                  | Тур                                  | Max                          | Units | Conditions                                                                                                                   |                                                                                                                                                             |

| VIH              | Minimum High Level<br>Input Voltage          | 2.0                                  |                                      |                              | v     |                                                                                                                              |                                                                                                                                                             |

| VIL              | Maximum Low Level<br>Input Voltage           |                                      |                                      | 0.8                          | v     |                                                                                                                              |                                                                                                                                                             |

| lін              | Input High Current                           |                                      |                                      | 5.0<br>5.0                   | μΑ    | V <sub>CC</sub> = Max                                                                                                        | $V_{I} = V_{CC}$ $V_{I} = 2.7V \text{ (Note 2)}$                                                                                                            |

| IIL              | Input Low Current                            |                                      |                                      | -5.0<br>-5.0                 | μΑ    | V <sub>CC</sub> = Max                                                                                                        | V <sub>I</sub> = 0.5V (Note 2)<br>V <sub>I</sub> = GND                                                                                                      |

| loz              | Maximum TRI-STATE Current                    |                                      |                                      | 10.0<br>10.0<br>10.0<br>10.0 | μΑ    | V <sub>CC</sub> = Max                                                                                                        | $V_{O} = V_{CC}$ $V_{O} = 2.7V \text{ (Note 2)}$ $V_{O} = 0.5V \text{ (Note 2)}$ $V_{O} = \text{GND}$                                                       |

| V <sub>IK</sub>  | Clamp Diode Voltage                          |                                      | -0.7                                 | -1.2                         | V     | $V_{CC} = Min; I_N = -18 \text{ mA}$                                                                                         |                                                                                                                                                             |

| los              | Short Circuit Current                        | -60                                  | -120                                 |                              | mA    | V <sub>CC</sub> = Max (Note 1); V <sub>O</sub> = GND                                                                         |                                                                                                                                                             |

| V <sub>OH</sub>  | Minimum High Level<br>Output Voltage         | 2.8<br>V <sub>HC</sub><br>2.4<br>2.4 | 3.0<br>V <sub>CC</sub><br>4.3<br>4.3 |                              | v     | $\label{eq:VCC} \begin{split} V_{CC} &= 3V; V_{IN} = 0.2V\\ V_{CC} &= Min\\ V_{IN} &= V_{IH} \text{ or } V_{IL} \end{split}$ | or V <sub>HC</sub> ; I <sub>OH</sub> = $-32 \mu A$<br>I <sub>OH</sub> = $-300 \mu A$<br>I <sub>OH</sub> = $-12 mA$ (Mil)<br>I <sub>OH</sub> = $-15 mA$ (Com |

| V <sub>OL</sub>  | Maximum Low Level<br>Output Voltage          |                                      | GND<br>GND<br>0.3<br>0.3             | 0.2<br>0.2<br>0.50<br>0.50   | v     | $\label{eq:VCC} \begin{split} V_{CC} &= 3V; V_{IN} = 0.2V\\ V_{CC} &= Min\\ V_{IN} &= V_{IH} \mbox{ or } V_{IL} \end{split}$ | or $V_{HC}$ ; $I_{OL} = 300 \ \mu A$<br>$I_{OL} = 300 \ \mu A$<br>$I_{OL} = 32 \ mA$ (Mil)<br>$I_{OL} = 48 \ mA$ (Com)                                      |

| Icc              | Maximum Quiescent<br>Supply Current          |                                      | 0.001                                | 1.5                          | mA    | $\label{eq:VCC} \begin{array}{l} V_{CC} = Max \\ V_{IN} \geq V_{HC}, V_{IN} \leq 0.2V \\ f_I = 0 \end{array}$                |                                                                                                                                                             |

| ΔI <sub>CC</sub> | Quiescent Supply Current;<br>TTL Inputs HIGH |                                      | 0.5                                  | 2.0                          | mA    | V <sub>CC</sub> = Max<br>V <sub>IN</sub> = 3.4V (Note 3)                                                                     |                                                                                                                                                             |

**DC Characteristics for 'FCTA Family Devices** (Continued) Typical values are at  $V_{CC} = 5.0V$ , 25°C ambient and maximum loading. For test conditions shown as Max, use the value specified for the appropriate device type: Com:  $V_{CC} = 5.0V \pm 5\%$ ,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ; Mil:  $V_{CC} = 5.0V \pm 10\%$ ,  $T_A = -55^{\circ}C$ to +125°C,  $V_{HC} = V_{CC} - 0.2V$ .

| Symbol | Parameter                                | 54FCTA/74FCTA |      |      | Units  | Conditions                                                                                       |                                                                                       |

|--------|------------------------------------------|---------------|------|------|--------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|        |                                          | Min           | Тур  | Max  | Units  | Conditions                                                                                       |                                                                                       |

| ICCD   | Dynamic Power<br>Supply Current (Note 4) |               | 0.15 | 0.25 | mA/MHz | $V_{CC} = Max$<br>Outputs Open<br>$\overline{OE} = GND$<br>One Input Toggling<br>50% Duty Cycle  | $V_{IN} \ge V_{HC}$ $V_{IN} \le 0.2V$                                                 |

| lc     | Total Power Supply<br>Current (Note 6)   |               | 1.5  | 4.0  |        | $V_{CC} = Max$<br>Outputs Open<br>$f_{CP} = 10 \text{ MHz}$<br>$\overline{OE} = GND$             | $\label{eq:VIN} \begin{array}{l} V_{IN} \geq V_{HC} \\ V_{IN} \leq 0.2 V \end{array}$ |

|        |                                          |               | 2.0  | 6.0  | mA     | f <sub>i</sub> = 5.0 MHz<br>One Bit Toggling<br>50% Duty Cycle                                   | $V_{IN} = 3.4V$<br>$V_{IN} = GND$                                                     |

|        |                                          |               | 3.75 | 7.8  |        | (Note 5)<br>$V_{CC} = Max$<br>Outputs Open<br>$f_{CP} = 10 \text{ MHz}$<br>$\overline{OE} = GND$ | $V_{IN} \ge V_{HC}$ $V_{IN} \le 0.2V$                                                 |

|        |                                          |               | 6.0  | 16.8 |        | f <sub>I</sub> = 2.5 MHz<br>Eight Bits Toggling<br>50% Duty Cycle                                | $V_{\rm IN} = 3.4V$<br>$V_{\rm IN} = GND$                                             |

| VH     | Input Hysteresis<br>on Clock Only        |               | 200  |      | mV     |                                                                                                  |                                                                                       |

Note 1: Maximum test duration not to exceed one second, not more than one output shorted at one time.

Note 2: This parameter guaranteed but not tested.

Note 3: Per TTL driven input ( $V_{IN} = 3.4V$ ); all other inputs at  $V_{CC}$  or GND.

Note 4: This parameter is not directly testable, but is derived for use in Total Power Supply calculations.

Note 5: Values for these conditions are examples of the I<sub>CC</sub> formula. These limits are guaranteed but not tested.

Note 6:  $I_C = I_{QUIESCENT} + I_{INPUTS} + I_{DYNAMIC}$

$I_{C} = I_{CC} + \Delta I_{CC} D_{H} N_{T} + I_{CCD} (f_{CP}/2 + f_{I} N_{I})$

I<sub>CC</sub> = Quiescent Current

$\Delta I_{CC}$  = Power Supply Current for a TTL High Input (V<sub>IN</sub> = 3.4V)

$D_{H} = Duty Cycle for TTL Inputs High$

N<sub>T</sub> = Number of Inputs at D<sub>H</sub>

I<sub>CCD</sub> = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

f<sub>CP</sub> = Clock Frequency for Register Devices (Zero for Non-Register Devices)

f<sub>1</sub> = Input Frequency

N<sub>I</sub> = Number of Inputs at f<sub>I</sub>

All currents are in milliamps and all frequencies are in megahertz.

|                                      |                                                             | 54FCTA/74FCTA                              | 74FCT/                                                                            | 4          | 54FCTA                                                            | 54FCTA |       |

|--------------------------------------|-------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|------------|-------------------------------------------------------------------|--------|-------|

| Symbol Paramo                        | Parameter                                                   | $T_{A} = +25^{\circ}C$ $V_{CC} = 5.0V$ Typ | T <sub>A</sub> , V <sub>CC</sub> =<br>R <sub>L</sub> = 500<br>C <sub>L</sub> = 50 | <b>0</b> Ω | $T_{A}, V_{CC} = Mil$ $R_{L} = 500\Omega$ $C_{L} = 50 \text{ pF}$ |        | Units |

|                                      |                                                             |                                            | Min (Note 1)                                                                      | Max        | Min (Note 1)                                                      | Max    | 1     |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>C <sub>P</sub> to O <sub>n</sub>       | 4.5                                        | 2.0                                                                               | 6.5        |                                                                   |        | ns    |

| tpzh<br>tpzL                         | Output Enable Time                                          | 5.5                                        | 1.5                                                                               | 6.5        |                                                                   |        | ns    |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Disable Time                                         | 4.0                                        | 1.5                                                                               | 5.5        |                                                                   | ·      | ns    |

| t <sub>SU</sub>                      | Set Up Time High or Low<br>D <sub>n</sub> to C <sub>P</sub> | 1.0                                        | 2.0                                                                               |            |                                                                   |        | ns    |

| t <sub>H</sub>                       | Hold Time High or Low<br>D <sub>n</sub> to C <sub>P</sub>   | 0.5                                        | 1.5                                                                               |            |                                                                   |        | ns    |

| t <sub>w</sub>                       | C <sub>P</sub> Pulse Width<br>High or Low                   | 4.0                                        | 5.0                                                                               |            |                                                                   |        | ns    |

Note 1: Minimum limits are guaranteed but not tested on propagation delays.

## Capacitance $T_A = +25^{\circ}C$ , f = 1.0 MHz

| Symbol | Parameter (Note)   | Тур | Max | Unit | Condition             |

|--------|--------------------|-----|-----|------|-----------------------|

| CIN    | Input Capacitance  | 6   | 10  | pF   | V <sub>IN</sub> = 0V  |

| COUT   | Output Capacitance | 8   | 12  | pF   | V <sub>OUT</sub> = 0V |

Note: This parameter is measured at characterization but not tested.

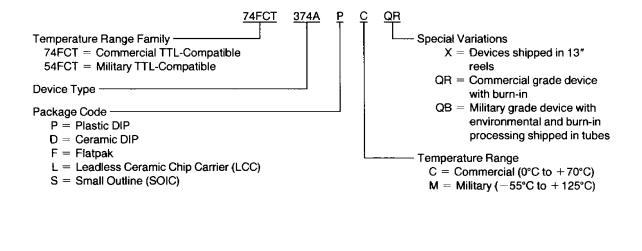

## **Ordering Information**

The device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as follows:

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959 TWX: (910) 339-9240

National Semiconductor GmbH lapan Ltd. industriestrasse 10 Sanseido Bldg. 5F D-8080 Furstenfeldbruck 4-15 Nishi Shinjuku West Germany Tel: (0-81-41) 103-0 Telex: 527-649 Shinjuku-Ku, Tokyo 160, Japan Tel: 3-299-7001 Fax: (08141) 103554 FAX: 3-299-7000

National Semiconductor National Semiconductor Hong Kong Ltd. Suite 513, 5th Floor Chinachem Golden Plaza 77 Mody Road, Tsimshatsui East, Kowloon, Hong Kong Tel: 3-7231290 Telex: 52996 NSSEA HX Fax: 3-3112536

National Semicondutores Do Brasil Ltda. Av. Brig. Faria Lima, 1363 6.0 Andor-Conj. 62 01451 Sao Paulo, SP. Brasil Tek (55/11) 212-5066 Fax: (55/11) 211-1161 NSBR BR

01.2671 🗹 🔤

National Semiconductor (Australia) PTY, Ltd. 1st Floor, 441 St. Kilda Fld. Melbourne, 3004 Victory, Australia Tel: (03) 267-5000 Fax: 61-3-2677458

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.