First:\_\_\_\_\_ Middle Initial: \_\_\_\_ Last:\_\_\_\_\_

# EE319K Final Exam

# Fall 2004

## Jonathan W. Valvano

This is a closed book exam. You must put your answers in these boxes only. You have 3 hours, so allocate your time accordingly. *Please read the entire exam before starting.*

| (5) Question 1. Precision in decimal digits |  |

|---------------------------------------------|--|

| (2) Part 2a. Choose A-E                     |  |

| (2) Part 2b. Choose A-E                     |  |

| (2) Part 2c. Choose A-E                     |  |

| (2) Part 2d. Choose A-E                     |  |

| (2) Part 2e. Choose A-E                     |  |

| (2) Part 3a. Specify RegB                   |  |

| (2) Part 3b. Specify 0 or 1                 |  |

| (1) Part 3c. Specify 0 or 1                 |  |

| (2) Part 4a. Give the value for <b>xxx</b>  |  |

| (3) Part 4b. Give the value for yyy         |  |

| (5) Question 5. Give the value for zzz      |  |

| (5) Question 6. Give the value              |  |

| (5) Question 7. Give the hexadecimal value  |  |

| (5) Question 8. Give the op code            |  |

(5) Question 9. Simplified memory cycles (you may or may not need all 5 entries)

| R/W | Addr | Data |

|-----|------|------|

|     |      |      |

|     |      |      |

|     |      |      |

|     |      |      |

|     |      |      |

|     |      |      |

(5) Question 10. Show the assembly code

### (10) Question 11. Hand assemble this program

| Address | Machine code |      | Sou  | rce code    |

|---------|--------------|------|------|-------------|

|         |              |      | org  | \$3900      |

|         |              | aa   | rmb  | 2           |

|         |              | bb   | rmb  | 1           |

|         |              | TCNT | equ  | \$0044      |

|         |              |      | org  | \$4300      |

|         |              |      | ldx  | TCNT        |

|         |              | loop | ldx  | #cc         |

|         |              |      | ldaa | 2, <b>x</b> |

|         |              |      | staa | bb          |

|         |              |      | bra  | loop        |

|         |              | cc   | fcb  | 0,1,2,3,4   |

### (15) Question 12. Show the assembly code

(20) Question 13. Show the assembly code

(5) Question 1. The measurement system range is 0 to 19.9 and a resolution of 0.1. What is the precision in decimal digits?

(10) Question 2. Place letter code for the best answer in the answer boxes

(2) Part a) Which direction does data flow on the data bus during a read cycle?

A) From 6812 to memory, or from 6812 to output device

B) From memory to 6812, or from input device to 6812

C) From input device to memory

D) From memory to output device

E) None of these answers is correct

(2) Part b) Which term best describes a computer system with a response time to external events that is short and bounded?

A) Real time

B) Dynamic

C) Busy-waiting

D) Nonintrusive

E) None of these answers is correct

(2) Part c) Which data structure has the following features? It can hold a variable number of fixed-size elements. It has two main operations, one to store data into itself, and a second operation to remove data. The data is removed in a "first come first served" order.

A) String

B) Binary tree

C) FIFO queue

D) MACQ

E) None of these answers is correct

(2) Part d) What is the difference between busy-waiting and gadfly synchronization?

A) Busy-waiting is used for I/O devices and gadfly is used for software events.

- B) Busy-waiting allows you to perform other operations (so you can be busy) while waiting for I/O devices and gadfly simply waits for the I/O device to be ready.

- C) The two terms describe exactly the same synchronization method.

D) Gadfly involves software loops, while busy-waiting involves hardware interrupts.

E) None of these answers is correct.

(2) Part e) What is drop out?

- A) Drop out is the error that occurs when the result of a calculation exceeds the range of the number system.

- B) Drop out is the error that occurs after a right shift or a divide, and the consequence is that an intermediate result looses its ability to represent all of the values.

C) Drop out is when both the Carry and the Overflow bits are set.

D) Drop out is data is lost when the software does not respond fast to an I/O event.

E) None of these answers is correct.

(5) Question 3. Consider the result of executing the following two 6812 assembly instructions.

#### ldab #170 addb #125

- (2) Part a) What will be the unsigned decimal value in Register B (0 to 255)?

- (2) Part b) What will be the value of the carry (C) bit?

- (1) Part c) What will be the value of the overflow (V) bit?

(5) Question 4. Consider the following assembly subroutine that creates two local variables, called  $\mathbf{p}$  and  $\mathbf{q}$ . The variable  $\mathbf{p}$  is 8 bits and initialized to 50. The variable  $\mathbf{q}$  is 16 bits and initialized to 500. The local variable binding is created using the **set** pseudo-ops.

```

; binding

set

XXX

р

yyy ; binding

; save red

set

q

; save register X

subl pshx

movb #50,1,-sp ; allocate and initialize p

movb #500,2,-sp ; allocate and initialize q

;... stuff

ldaa P,sp ; read from p

ldx Q,sp ; read from q

;... more stuff

leas 3,s ; deallocate p,q

; restore register X

pulx

rts

; return

```

(2) Part a) What value should you use in the **xxx** position to implement the binding of **p**?

(3) Part b) What value should you use in the yyy position to implement the binding of q?

(5) Question 5. Consider the following main program that calls an assembly subroutine using call by reference parameter passing on the stack. An address to an output port is pushed on the stack, and this subroutine will set bit 0 of that port. The subroutine uses Register X stack frame.

```

; binding

port set zzz

main lds

#$4000

ldd #PTT ; address to PTT

pshd

; pass 16-bit port parameter on stack

jsr Set0

leas 2, sp

stop

pshx ; save register X

tsx ; create Register X stack frame

leas -4,sp ; allocate locals

ldy port,x ; get port parameter

Set0 pshx

bset 0,y,#$01 ; set bit0 of the port

leas 4, sp ; deallocate locals

pulx

; restore register X

rts

; return

```

What value should you use in the **zzz** position to implement the binding of this parameter?

(5) Question 6. A signed 16-bit decimal fixed-point number system has a  $\Delta$  resolution of 1/100. What is the corresponding value of the number if the integer part stored in memory is \$C000? (5) Question 7. Assume RegX is initially \$4321, RegD is initially \$8765. What is resulting hexadecimal value in RegD after these instructions execute?

psha pshb pshx pula leas 2,s pulb (5) Question 8. Assume **PTT** is a signed 8-bit input and **PTM** is an output. The goal of this code is to clear **PTM** if **PPT** is larger than 100. Which op code should be used in the ??? position?

```

ldaa PTT

cmpa #100

??? skip

clr PTM

```

#### loop

(5) Question 9. Give the simplified memory cycles produced when the following one instruction is executed. Assume the PC contains \$4000, Register Y contains \$3900, each memory location from \$3800 to \$3FFF contains a value equal to the least significant byte of its address. I.e., \$3800 contains \$00, \$3801 contains \$01, etc. Just show R/W=Read or Write, Address, and Data for each cycle.

```

$4000 EE71 ldx 2,y+

```

(5) Question 10. Consider a table with 25 entries and 4 fields. Each entry has different values, but the same size and format. The assembly code for table entry number 5 is shown below

```

Entry5 fcb 100 8-bit count field

fdb 1000 16-bit time field

fcb "happy,",0,0,0 8-byte name field

fdb -50,300,-200 three 16-bit yaw,pitch,roll fields

```

Assume Register X is pointing to this entry

```

ldx #Entry5

```

Using Register X, write assembly code that reads the **pitch** value of **Entry5** into a register (10) Question 11 Hand assemble the program shown on the answer pages

(10) Question 11. Hand assemble the program shown on the answer pages

(15) Question 12. The SCISR1 register contains the TDRE and RDRF flags

|    |      | 7    | 6  | 5    | 4    | 3  | 2  | 1  | 0  |

|----|------|------|----|------|------|----|----|----|----|

|    | R    | TDRE | TC | RDRF | IDLE | OR | NF | FE | PF |

|    | W    |      |    |      |      |    |    |    |    |

| RE | SET: | 1    | 1  | 0    | 0    | 0  | 0  | 0  | 0  |

TDRE — Transmit Data Register Empty Flag

TDRE is set when the transmit shift register receives a byte from the SCI data register. When TDRE is 1, the transmit data register (SCIDRH/L) is empty and can receive a new value to transmit.Clear TDRE by reading SCI status register 1 (SCISR1), with TDRE set and then writing to SCI data register low (SCIDRL).

1 = Byte transferred to transmit shift register; transmit data register empty

0 = No byte transferred to transmit shift register

RDRF - Receive Data Register Full Flag

RDRF is set when the data in the receive shift register transfers to the SCI data register. Clear RDRF by reading SCI status register 1 (SCISR1) with RDRF set and then reading SCI data register low (SCIDRL).

1 = Received data available in SCI data register

0 = Data not available in SCI data register

The **SCIDRL** register serial input/output data. Write a subroutine that inputs one ASCII character from the serial port. Your subroutine should wait for new input using gadfly synchronization. The subroutine uses return by value parameter passing with RegB. You don't need to write the initialization ritual. COMMENTS WILL BE GRADED.

```

SCISR1equ $00CC ; SCI Status Register 1SCIDRLequ $00CF ; SCI Data Register Low

```

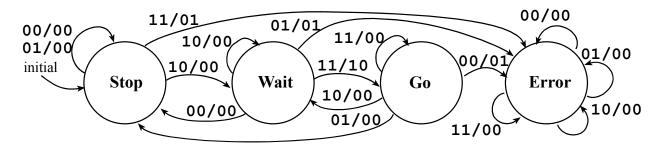

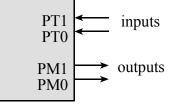

(20) Question 13. The objective of this problem is to implement the following two-input twooutput Mealy finite state machine. The state graph and ROM-based data structure are given. Your job is to write the entire main program, including reset vector, to run this machine. The FSM repeats over and over the following sequence

1) Input from PTT;

- 2) Output to PTM (depends on input and state);

- 3) Change states (depends on input and state).

The initial state is **Stop**.

You will use the following linked data structure (without copying it to the answer sheet)

|       | org | \$4000                     | Put in ROM  |

|-------|-----|----------------------------|-------------|

| Stop  | fcb | 0,0,0,1                    | Outputs     |

|       | fdb | Stop,Stop,Wait,Error       | Next states |

| Wait  | fcb | 0,1,0,2                    |             |

|       | fdb | Stop,Error,Wait,Go         |             |

| Go    | fcb | 1,0,0,0                    |             |

|       | fdb | Error,Stop,Wait,Go         |             |

| Error | fcb | 0,0,0,0                    |             |

|       | fdb | Error, Error, Error, Error | r           |

|       |     |                            |             |

The inputs are connected to PTT bits 1,0 and the outputs are connected to PTM bits 1,0.

You may use the following I/O port definitions (without copying them to the answer sheet)

DDRM equ \$0252 ; Port M Direction DDRT equ \$0242 ; Port T Direction PTM equ \$0250 ; Port M I/O Register PTT equ \$0240 ; Port T I/O Register

| postbyte,xb   | syntax | mode    | explanations                   | rr | register |

|---------------|--------|---------|--------------------------------|----|----------|

| rr000000      | ,r     | IDX     | 5-bit constant, n=0            | 00 | Х        |

| rr00nnnn      | n,r    | IDX     | 5-bit constant, $n=0$ to $+15$ | 01 | Y        |

| rr01nnnn      | -n,r   | IDX     | 5-bit constant, n=-16 to -1    | 10 | SP       |

| rr100nnn      | n,+r   | IDX     | pre-increment, n=1 to 8        | 11 | PC       |

| rr101nnn      | n,-r   | IDX     | pre-decrement, n=1 to 8        |    |          |

| rr110nnn      | n,r+   | IDX     | post-increment, n=1 to 8       |    |          |

| rrll1nnn      | n,r-   | IDX     | post-decrement, n=1 to 8       |    |          |

| 111rr100      | A,r    | IDX     | Reg A accumulator offset       |    |          |

| 111rr101      | B,r    | IDX     | Reg B accumulator offset       |    |          |

| 111rr110      | D,r    | IDX     | Reg D accumulator offset       |    |          |

| 111rr000 ff   | n,r    | IDX1    | 9-bit cons, n 16 to 255        |    |          |

| 111rr001 ff   | -n,r   | IDX1    | 9-bit const, n -256 to -16     |    |          |

| 111rr010 eeff | n,r    | IDX2    | 16-bit const, any 16-bit n     |    |          |

| 111rr111      | [D,r]  | [D,IDX] | Reg D offset, indirect         |    |          |

| 111rr011 eeff | [n,r]  | [IDX2]  | 16-bit constant, indirect      |    |          |

| Source Form | Address<br>Mode | Object Code |

|-------------|-----------------|-------------|

| BRA rel8    | REL             | 20 rr       |

## **LDX** Operation: $(M : M+1) \Rightarrow X$

Loads the most significant byte of index register X with the content of memory location M, and loads the least significant byte of X with the content of the next byte of memory at M+1.

| Source Form        | Address<br>Mode | Object Code |

|--------------------|-----------------|-------------|

| LDX #opr16i        | IMM             | СЕ јј КК    |

| LDX opr8a          | DIR             | DE dd       |

| LDX opr 16a        | EXT             | FE hh 11    |

| LDX oprx0_xysp     | IDX             | EE XD       |

| LDX oprx9, xysp    | IDX1            | EE XD ff    |

| LDX oprx16,xysp    | IDX2            | EE xb ee ff |

| LDX [D, xysp]      | [D, IDX]        | EE XD       |

| LDX [oprx16, xysp] | [IDX2]          | EE xb ee ff |

## **STAA** Operation: $(A) \Rightarrow M$

Stores the content of accumulator A in memory location M. The content of A is unchanged.

| Source Form        | Address<br>Mode | Object Code |

|--------------------|-----------------|-------------|

| STAA opr8a         | DIR             | 5A dd       |

| STAA opr16a        | EXT             | 7A hh 11    |

| STAA oprx0_xysp    | IDX             | 6A XD       |

| STAA oprx9,xysp    | IDX1            | 6A XD II    |

| STAA oprx16,xysp   | IDX2            | 6A XD ee ff |

| STAA [D,xysp]      | [D, IDX]        | 6A XD       |

| STAA [oprx16,xysp] | [IDX2]          | 6A XD ee ff |

### **LDAA** Operation: $(M) \Rightarrow A$

Loads the content of memory location M into accumulator A. The condition codes are set according to the data.

| Source Form        | Address<br>Mode | Object Code |

|--------------------|-----------------|-------------|

| LDAA #opr8i        | IMM             | B6 11       |

| LDAA opr8a         | DIR             | 96 didi     |

| LDAA opr16a        | EXT             | B6 hh 11    |

| LDAA oprx0_xysp    | IDX             | A6 XD       |

| LDAA oprx9,xysp    | IDX1            | A6 XD ff    |

| LDAA oprx16,xysp   | IDX2            | A6 Xb ee ff |

| LDAA [D,xysp]      | [D, IDX]        | A6 XD       |

| LDAA [oprx16,xysp] | [IDX2]          | A6 xb ee ff |

aba 8-bit add RegA=RegA+RegB aby unsigned add RegY=RegY+RegB adca 8-bit add with carry to RegA adca 8-bit add with carry to RegA adca 8-bit add with carry to RegA adca 8-bit add with carry to RegB adda 8-bit add to RegA adda 8-bit add to RegA adda 8-bit add to RegA adda 8-bit add to RegD adda 8-bit logical and to RegA adda 8-bit logical and to RegB andca 8-bit logical and to RegB asla/Islb 8-bit arith left shift Memory asla/Islb 8-bit arith left shift RegB asr 8-bit arith right shift asr 8-bit arith right shift memory asr 8-bit arith right shift to RegB bcc branch if carry clear bcg branch if carry clear bcg branch if result is zero (Z=1) bcs branch if signed ≥ bth 8-bit and th RegA, sets CCR blo branch if unsigned ≤ btb 8-bit and with RegA, sets CCR blo branch if unsigned ≤ btb 8-bit and with RegA, sets CCR blo branch if unsigned ≤ blob ble branch if signed ≤

bls long branch if unsigned ≤

bls branch if unsigned ≤

bls branch if signed ≤

bls branch if result is negative (N=1)

bne branch if result is norzero (2=0)

cond is overflow set

cond is overflow set

cond is overflow set

cond is overflow set

cond is overflow is result is norzero (2=0)

cond is overflow is result is norzero (2=0)

cond is overflow is result is norzero (2=0)

cond is overflow is result is norzero (2=0) branch if signed ≤ branch if unsigned < branch if unsigned ≤ branch if signed <

| pulx<br>puly<br>rev | pop 16 bits off stack into RegX<br>pop 16 bits off stack into RegY<br>Fuzzy logic rule evaluation |

|---------------------|---------------------------------------------------------------------------------------------------|

| revw                |                                                                                                   |

| rol                 | -                                                                                                 |

| rola                | 8-bit roll shift left RegA                                                                        |

|                     | 8-bit roll shift left RegB                                                                        |

|                     | 8-bit roll shift right Memory                                                                     |

|                     | 8-bit roll shift right RegA                                                                       |

|                     | 8-bit roll shift right RegB                                                                       |

| rtc                 | return sub in expanded memory                                                                     |

| rti                 | return from interrupt                                                                             |

| rts                 | return from subroutine                                                                            |

| sba                 | 8-bit subtract RegA=RegA-RegB                                                                     |

| sbca                | 8-bit sub with carry from RegA                                                                    |

| sbcb                | 8-bit sub with carry from RegB                                                                    |

| sec                 | set carry bit, C=1                                                                                |

| sei                 | set I=1, disable interrupts                                                                       |

| sev                 | set overflow bit, V=1                                                                             |

| sex                 | sign extend 8-bit to 16-bit reg                                                                   |

| staa                | 8-bit store memory from RegA                                                                      |

| stab                | 8-bit store memory from RegB                                                                      |

| std                 | 16-bit store memory from RegD                                                                     |

| sts                 | 16-bit store memory from SP                                                                       |

| stx                 | 16-bit store memory from RegX                                                                     |

| subb<br>subd<br>swi<br>tab<br>tap | <pre>16-bit store memory from RegY 8-bit sub from RegA 8-bit sub from RegB 16-bit sub from RegD software interrupt, trap transfer A to B transfer A to CC transfer B to A</pre> |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tbeq                              | test and branch if result=0                                                                                                                                                     |

| tbl                               | 8-bit look up and interpolation                                                                                                                                                 |

| tbne                              | test and branch if result≠0                                                                                                                                                     |

| tfr                               | transfer register to register                                                                                                                                                   |

| tpa                               | transfer CC to A                                                                                                                                                                |

|                                   | illegal op code, or software trap                                                                                                                                               |

|                                   | 8-bit compare memory with zero                                                                                                                                                  |

|                                   | 8-bit compare RegA with zero                                                                                                                                                    |

|                                   | 8-bit compare RegB with zero                                                                                                                                                    |

|                                   | transfer S+1 to X                                                                                                                                                               |

| tsy                               | transfer S+1 to Y                                                                                                                                                               |

|                                   | transfer X-1 to S                                                                                                                                                               |

|                                   | transfer Y-1 to S                                                                                                                                                               |

| wai                               | wait for interrupt                                                                                                                                                              |

| wav                               | weighted Fuzzy logic average                                                                                                                                                    |

| xgdx                              | exchange RegD with RegX                                                                                                                                                         |

| xgdy                              | exchange RegD with RegY                                                                                                                                                         |

| example           | addressing mode | Effective Address              |

|-------------------|-----------------|--------------------------------|

| ldaa #u           | immediate       | none                           |

| ldaa u            | direct          | EA is 8-bit address (0 to 255) |

| ldaa U            | extended        | EA is a 16-bit address         |

| ldaa m,r          | 5-bit index     | EA=r+m (-16 to 15)             |

| ldaa v,+r         | pre-increment   | r=r+v, EA=r (1 to 8)           |

| ldaa v,-r         | pre-decrement   | r=r-v, EA=r (1 to 8)           |

| ldaa v,r+         | post-increment  | EA=r, r=r+v (1 to 8)           |

| ldaa v,r-         | post-decrement  | EA=r, r=r-v (1 to 8)           |

| ldaa A,r          | Reg A offset    | EA=r+A, zero padded            |

| ldaa B,r          | Reg B offset    | EA=r+B, zero padded            |

| ldaa D,r          | Reg D offset    | EA=r+D                         |

| ldaa q <b>,</b> r | 9-bit index     | EA=r+q (-256 to 255)           |

| ldaa W,r          | 16-bit index    | EA=r+W (-32768 to 65535)       |

| ldaa [D,r]        | D indirect      | EA={r+D}                       |

| ldaa [W,r]        | indirect        | $EA=\{r+W\}$ (-32768 to 65535) |

Motorola 6812 addressing modes

| Pseudo op |        |       | meaning |                                                                 |  |  |  |  |  |  |  |  |  |

|-----------|--------|-------|---------|-----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| org       | rg org |       |         | Specific absolute address to put subsequent object code         |  |  |  |  |  |  |  |  |  |

| =         | equ    |       |         | Define a constant symbol                                        |  |  |  |  |  |  |  |  |  |

| set       |        |       |         | Define or redefine a constant symbol                            |  |  |  |  |  |  |  |  |  |

| dc.b      | db     | fcb   | byte    | Allocate byte(s) of storage with initialized values             |  |  |  |  |  |  |  |  |  |

| fcc       |        |       |         | Create an ASCII string (no termination character)               |  |  |  |  |  |  |  |  |  |

| dc.w      | dw     | fdb   | .word   | Allocate word(s) of storage with initialized values             |  |  |  |  |  |  |  |  |  |

| dc.l      | dl     | .long | J       | Allocate 32-bit long word(s) of storage with initialized values |  |  |  |  |  |  |  |  |  |

| ds d      | s.b    | rmb   | .blkb   | Allocate bytes of storage without initialization                |  |  |  |  |  |  |  |  |  |

| ds.w      |        | .blkw |         | Allocate bytes of storage without initialization                |  |  |  |  |  |  |  |  |  |

| ds.l      |        | blkl  |         | Allocate 32-bit words of storage without initialization         |  |  |  |  |  |  |  |  |  |

|              | _        |                                  |                   | _         |        | _         | _            |                     | _   |         | _        |             |                    | _  |                    | _              |              |            |             |                  |    |                  | _        |                  |           |              |                  |         |                    | _  |       | _        |             |                    |              |

|--------------|----------|----------------------------------|-------------------|-----------|--------|-----------|--------------|---------------------|-----|---------|----------|-------------|--------------------|----|--------------------|----------------|--------------|------------|-------------|------------------|----|------------------|----------|------------------|-----------|--------------|------------------|---------|--------------------|----|-------|----------|-------------|--------------------|--------------|

| F0<br>n,SP   | 9b const | F1<br>ce                         | 9b const          | F2        | n,SP   | 160 CONST | F3<br>1. 001 | 16b indr            | F4  | A,SP    | A offset | F5<br>P co  | B offset           | 8  | D offset           | t              | P/<br>[D,SP] | D indirect | F8<br>- Cr  | 9b const         | E9 | -n,PC            |          | n,PC             | 16b const | FB<br>In Dri | 16b indr         | Б.<br>Г | A offset           | G  | B,PC  | B offset | ьел<br>FE   | D offset           | EF<br>ID BC1 |

| E0<br>''X    | 9b const | E1<br>X                          | 9b const          | E2        | n,X    | 16b const | E3<br>6 55   | 16b indr            | E4  | XX<br>Y | A offset | E5<br>°     | B offset           | E6 | D official         |                | e/<br>[D,X]  | D indirect | E8          | 9b const         | E9 | -n,Y<br>Oh annot |          | n.Y              | 16b const | EB<br>6. VI  | 16b indr         | 2<br>23 | A,Y<br>Aoffset     | 8  | В,Ү   | B offset | E           | Doffset            | EF<br>DV1    |

| D0<br>-16,PC | 5b const | D1<br>14 PC                      | 5b const          | D2        | -14,PC | 5b const  | D3           | 5b const            | D4  | -12,PC  | 5D CONST | D5          | 3b const           | 9G | -10,PC             |                | D/<br>-9,PC  | 5b const   | 08<br>DB    | 5b const         | 60 | -7,PC            |          | -6.PC            | 5b const  | DB<br>E DC   | 5b const         | BC      | -4,PC<br>5b const  | 00 | -3,PC | 5b const | DE          | 5b const           | DF           |

| 0,PC         | 5b const | 01<br>1<br>1<br>1<br>1<br>1<br>1 | 5b const          | 8         | 2,PC   | 5b const  | ខ            | 3, P.C.<br>5b const | 2   | 4,PC    | 5D CONST | S<br>S      | 5b const           | 8  | 6,PC<br>5h const   |                | C7<br>7,PC   | 5b const   | св<br>св    | 5b const         | C9 | 9,PC             |          | 10.PC            | 5b const  | CB<br>       | 5b const         | 8       | 12, PC<br>Sb const | 8  | 13,PC | 5b const | CE<br>Trave | 5b const           | CF<br>48 BC  |

| B0<br>1,SP+  | post-inc | B1<br>3 cpt                      | post-inc          | <u>B2</u> | 3,SP+  | post-inc  | B3           | 4,SP+<br>post-inc   | 84  | 5,SP+   | post-inc | B5<br>2 cou | post-inc           | 8  | 7,SP+<br>met-inc   | and the second | B/<br>8,SP+  | post-inc   | B8<br>° c D | post-dec         | B9 | 7,SP-            | huaran   | 6.8 <sup>-</sup> | post-dec  | 88<br>       | post-dec         | BC      | 4,SP-<br>post-dec  | D8 | 3,SP- | post-dec | BE          | post-dec           | BF<br>1 cp   |

| AD<br>1,+SP  | pre-inc  | A1<br>9.46D                      | pre-inc           | A2        | 3,+SP  | pre-inc   | A3           | 4,+SP<br>pre-Inc    | A4  | 5,+SP   | pre-inc  | A5<br>      | pre-inc            | A6 | 7,+SP<br>nre-inc   | 2 2            | A7<br>8,+SP  | pre-inc    | A8<br>AB    | pre-dec          | 6A | 7,-SP            | non-or   | <br>6SP          | pre-dec   | AB<br>, cn   | pre-dec          | AC.     | 4,-SP<br>pre-dec   | Q  | 3,-SP | pre-dec  | AE<br>2 CD  | pre-dec            | AF<br>1 ep   |

| 90<br>-16,SP | 5b const | 91<br>15 ep                      | 5b const          | 92        | -14,SP | 5b const  | 93           | -13,SP<br>5b const  | 707 | -12,SP  | 5b const | 95<br>11 cn | Bb const           | 96 | -10,SP<br>Sh const |                | 97<br>-9,SP  | 5b const   | 85          | 5b const         | 66 | -7,SP            |          | an<br>-6.SP      | 5b const  | 9B<br>7 A A  | 5b const         | 90      | 5b const           | D6 | -3,5P | 5b const | 36          | 5b const           | 9F<br>_1 sp  |

| 80<br>0,SP   | 5b const | 81<br>1 cp                       | 5b const          | 82        | 2,SP   | 5b const  | 83           | 3,SP<br>5b const    | 84  | 4,SP    | 5b const | 85<br>r en  | 5b const           | 86 | 6,SP<br>5h const   |                | 87<br>7,SP   | 5b const   | 88          | 5b const         | 68 | 9,SP             |          | 00<br>10.SP      | 5b const  | 88           | 5b const         | 8       | 12,SP<br>Sb const  | 08 | 13,SP | Sb const | 38          | 5b const           | 8F<br>15 CD  |

| 70           | post-inc | 71                               | 2, 17<br>post-inc | 72        | 3,Y+   | post-inc  | 73           | 4,Y+<br>post-inc    | 74  | 5,4+    | post-inc | 75          | a, Y +<br>post-inc | 78 | 7,Y+<br>most-inc   | -              | 77<br>8,Y+   | post-inc   | 78          | 8,Y-<br>post-dec | 79 | -7,7             | posr-dec | 6.Y-             | post-dec  | 78           | o,r-<br>post-dec | 70      | 4, Y-<br>post-dec  | 62 | 3, Y- | post-dec | 7E          | z, T -<br>post-dec | 75           |

|              | _        |                                  | _                 | 1         |        | _         |              |                     |     |         |          |             |                    | -  |                    | +              |              |            |             |                  |    |                  |          |                  |           |              |                  |         |                    |    |       |          |             |                    |              |

₹ŝ

pre-inc

-12,Y 5b const

4,Y 5b const

post-inc

pre-inc

5b const

4,X 5b const

÷.

5;<del>,</del>X

3

4

켨

24

2

3

÷

-13,Y 5b const

3,Y 5b const

post-inc

pre-inc

3

\$3

g

g

3

8

4,<del>,</del>

-13,X 5b const -12,X

3,X 5b const

ore-inc

7÷3

鉛

8

45

約

22

ŝ

8

ore-inc

-11,Y Sb const

5,Y 5b const

post-inc

pre-inc

-11,X Sb const

5,X 5b const

÷,

8,+X

ž

ore-inc

-10,Y Sb const

6,Y 5b const

7,X+ post-inc

X+'.

pre-inc

-10,X Sb const

6,X 5b const

88

48

器

38

99

8

,+,8

pre-inc

-9,Y 5b const

7,Y 5b const

8,X+ post-inc

8,+X

pre-inc

const × 8

X<sub>6</sub>-

7,X 5b const

ß

5

ß

27

₽ 6

07

2 2

ž

8,Y 5b const

8,X-post-dec

8,-X

ore-dec

5b const

5b cons ×8

5b const

88

8

8

38

83

8

8

re-dec 2

ž

8

3

8

8

କ୍ଷ

0

8

ore-inc

-16,Y 5b const

0,Y 5b const

1,X+ post-inc

ž

pre-inc

-16,X 5b const

0,X 5b const

₹ 5

-15,Y 5b const

1,Y 5b const

×, post-inc 3,×

2,+X

pre-inc

-15,X 5b const

1,X 5b const

Ξ

5

Ξ

₹.

-14,Y 5b const

2,Y 5b const

post-inc 4,¥

3,+X pre-inc

-14,X 5b const

2,X 5b const

23

42

33

ន

2

03

[D, PC] indirect

[D,Y] Indirect

-1,PC 5b const

15,PC 5b const

post-dec 1,SP. 뚭

1,-SP pre-dec

-1,SP 5b const

15,SP 5b const

1,Y-post-dec

1,-Y pre-dec

-1,Y const

15,Y 5b const

1,X-post-dec

1,-X pre-dec

-1,X 5b const

15,X 5b const

2,-7

ᇥ

В

Å,

끮

2

ш

pre-dec

-2,Y 5b const

14,Y 5b const

post-dec

pre-dec

-2,X 5b const

14,X 5b const

2,×

2,-X

ĥ

넁 8

4

똜

片

벁

붱

3,-Y

,≺ ,≺ 5b const

13,Y 5b const

post-dec

pre-dec

5b const

13,X const

З,×

3,-X

-3,X

8

9

ê

6

କ୍ଷ

ē

8 6 빙

pre-dec

4

pre-dec

-4,Y 5b const

12,Y Sb const

post-dec

pre-dec

Å,

4,-X

5b const

12,X Sb const

S

Ş

õ

8

õ

g

5-7

re-de(

-5,Y 5b const

11,Y 5b const

post-dec

ore-dec

-5,X 5b const

11,X 5b const

÷ S

5,-X

Ę,

Ϋ́

10, Y 5b const

Ϋ́θ 3Å

8,-X

χġ 5b const

10,X 5b const

Z

₹

≤

₹

5b const Ş

8

ŝ

38

38

₿

8

post-dec

ore-dec

9-090

e-dec

-7,Y 5b const

9,Y 5b const

7,X-post-dec

7,-X

pre-dec

-7,X 5b const

9,X 5b const

83

ŝ

8

Ø.

19

æ

Ш ō