(4) Question 1. We can hear sounds from about 20 to 20 kHz, thus we say the frequency components of sound exist from 20 to 20 kHz. The Nyquist Theorem requires you to sample at a rate strictly larger than twice the maximum frequency components of the signal. Thus in this case, we must sample larger than 400 Hz. Recall in lab the distance signal was 0 to 2 Hz, and we sampled at 5 Hz.

(4) Question 2. E) The motor will not spin at all because we did not wait in between each output to the motor.

(4) Question 3. Write a subroutine to sample ADC channel 5 of the 9S12DP512.

```

ADC_In movb #$85,ATD0CTL5 ;start ADC channel 5

```

```

brclr ATD0STAT0,#$80,adcwait ; wait for SCF

```

```

ldy ATD0DR0

```

rts

(8) Question 4. 0 maps to 0 and 4095 maps to 4000. When Vin is 4 V, the ADC is 4095, software converts 4095 into 4000. Multiply by 4000, then divide by 4095

```

ldy #4000

emul

ldx #4095

ediv

```

(4) Question 5. The trick is the sty instruction overwrites the data saved on the stack by the stx instruction. RegX will be \$3455

(4) Question 6. The order is D) 1,6,3,2,5,4,7

1) There is data in the receive data register and the hardware sets the flag bit (e.g., RDRF=1)

6) The CCR, A, B, X, Y, PC are pushed on the stack

- 3) The I bit in the CCR is set by hardware

- 2) The SCI vector address is loaded into the PC

- 5) The software reads **SCI1SR1**

- 4) The software reads **SCI1DRL**

- 7) The software executes rti

(10) Question 7. Write software that increments a 16-bit global variable every 2 msec.

```

org $0800

```

```

Count

rmb

2

; incremented every 2 msec

$4000

orq

lds

main

#$4000

movw #0,Count

movb #$80,TSCR1

;enable TCNT

bset TIOS,#$08

;activate output compare

bset TIE,#$08

;arm OC3

ldd TCNT

addd #50

;first interrupt right away

std TC3

cli

bra

*

OC3han movb #$08,TFLG1 ;ack

ldd TC3

addd #16000

;2ms=16000*125ns

std TC3

;next interrupt

ldx Count

```

inx

stx Count

rti

org \$FFE8

fdb OC3han

org \$FFFE

fdb main

t -1 0 100 200 300 400 500 600 700 800 900 1000 1100 1200 us (5) Question 9. Transmits 1 to 2, then 2 to 1 taking a total of 2 ms.

(4) Question 10. The most common mistake was to think  $V_{out}$  is 5V when the digital output was 111. Let n=4b<sub>2</sub>+2b<sub>1</sub>+b<sub>0</sub> be the 3-bit number on PT2,PT1,PT0. The voltage on PT2 is 5\*b<sub>2</sub>. The voltage on PT1 is 5\*b<sub>1</sub>. The voltage on PT0 is 5\*b<sub>0</sub>. We will define all currents going from left to right. The current through the 10k $\Omega$  is (5\*b<sub>2</sub>-V<sub>out</sub>)/10k $\Omega$ . The current through the 20k $\Omega$  is (5\*b<sub>1</sub>-V<sub>out</sub>)/20k $\Omega$ . The current through the left 40k $\Omega$  is (5\*b<sub>0</sub>-V<sub>out</sub>)/40k $\Omega$ . The current through the right 40k $\Omega$  is V<sub>out</sub>/40k $\Omega$ . Adding the currents up we get

$(5*b_2-V_{out})/10k\Omega + (5*b_1-V_{out})/20k\Omega + (5*b_0-V_{out})/40k\Omega = V_{out}/40k\Omega.$

Multiply by  $40k\Omega$

$$4(5*b_2-V_{out}) + 2(5*b_1-V_{out}) + (5*b_0-V_{out}) = V_{out}$$

Solving for V<sub>out</sub>

$4*5*b_2+2*5*b_1+5*b_0=8*V_{out} \label{eq:Vout}$  Substituting the definition of n

$V_{out} = 5*n/8$

| PT2 | PT1 | PT0 | Vout (V) |

|-----|-----|-----|----------|

| 0   | 0   | 0   | 0.000    |

| 0   | 0   | 1   | 0.625    |

| 0   | 1   | 0   | 1.250    |

| 0   | 1   | 1   | 1.875    |

| 1   | 0   | 0   | 2.500    |

| 1   | 0   | 1   | 3.125    |

| 1   | 1   | 0   | 3.750    |

| 1   | 1   | 1   | 4.375    |

(8) Question 11. You will be execute one instruction and answering questions.

Part a) 07 is the machine code for **bsr**

Part b) The return address is \$4005, which is pushed on the stack. To push, first decrement SP then store. The order in this table does not matter. In fact, the 9S12 will store the \$4005 as a 16-bit value in one bus cycle

| Address | Data |

|---------|------|

| \$3FFD  | \$05 |

| \$3FFC  | \$40 |

Part c) The SP points to valid data on top of the stack, SP = \$3FFC

Part d) The PC is incremented after each fetch (PC=\$4005), then the PC relative value of \$02 is added to the PC to get the target address of the subroutine, PC = \$4007

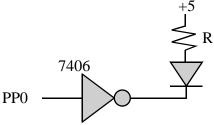

(5) Question 12.  $R = (5-V_d-V_{OL})/I_d = (5-1.5-0.5)/0.03 = 3V/0.03A = 100 \Omega$ .

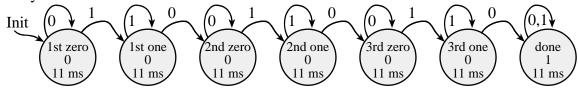

(10) Question 13. Basically, we wait for the input to be 1, wait for it to be zero, wait for the input to be 1, wait for it to be zero, wait for the input to be 1, then wait for it to be zero. To debounce we run the FSM at any time between 10 and 100 ms.

## (10) Question 14.

Part a) Hand execute and draw a stack picture

## Pt set 4 ;16-bit pointer to 8-bit data

## L1 set -1 ;8-bit local variable

Part b) A pointer is on the stack, so we need an indirection to get the data

```

ldaa [Pt,x]

```

We could have performed the indirection in multiple instructions

```

ldy Pt,x

```

```

ldaa 0,y

```

(15) Question 15. The FIFO is full when Cnt is 8.

```

Fifo_Put ldab Cnt

;number of elements currently saved, 0 to 8

cmpb #8

bhs

full

;full if Cnt is 8

ldx

#Fifo

NotFull

ldab PutI

;RegB is 0 to 7

staa b,x

;save in Fifo

inc

Cnt

;one more saved

incb

;next place to put

andb #$07

;0 to 7

stab PutI

ldab #1

;success

bra

done

full

clrb

;failure

done

rts

```