| First:                                                                                                                                                                                                                | Middle Initial: Last:                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This is a closed book exam. You must hours, so allocate your time accordingly. <i>Please</i>                                                                                                                          | t put your answers in the space provided. You have 3                                                                                                                                                                                 |

| Please read and affirm our honor code:  "The core values of The University of Texas at leadership, individual opportunity, and response expected to uphold these values through integrit toward peers and community." | Austin are learning, discovery, freedom, ibility. Each member of the university is                                                                                                                                                   |

| Signed:                                                                                                                                                                                                               | December 12, 2008                                                                                                                                                                                                                    |

| system range is -2 to +2 m. The frequency com                                                                                                                                                                         | a 12-bit ADC to measure a distance. The measurement apponents of the distance signal can vary from DC (0 Hz) compare interrupt to sample the ADC. What rate (in Hz) to the distance of the distance of the distance of the distance. |

| ISR the four-bit motor output is set to 5, 6, 1 following four instructions occur during each IS movb #\$05,PTT movb #\$06,PTT movb #\$0A,PTT movb #\$09,PTT  There are 200 steps per rotation of the motor. W        | re interrupt is used to spin a stepper motor. During each 0, then 9. The stepper is interfaced to PT3-0, and the SR, without any delay between these instructions.                                                                   |

| A) The motor will not spin at all B) The motor will spin at 20 rps = (4 step/ms)*(C) The motor will spin at 1000 rps = (1 rot/ms) D) The motor will spin at 4000 rps = (4 rot/ms)                                     | (1000ms/s)*(1 rot/200steps)<br>*(1000ms/s)                                                                                                                                                                                           |

| E) The motor will spin at 5 rps = $(1 \text{ step/ms})*(1 \text{ step/ms})$                                                                                                                                           | `                                                                                                                                                                                                                                    |

**(4) Question 3.** Write a subroutine to sample ADC channel 4 of the 9S12DP512. Assume the ADC initialized for a 10-bit sample, sequence length is 1, and the ADC clock is 2 MHz. Implement right-justified conversions, and return the result in RegX.

(8) Question 4. Assume you have an 11-bit ADC with a range of 0 to +10 V (not the 9S12). Write a subroutine that converts the ADC sample into a fixed-point number with a resolution of 0.01 V. The input parameter is call by value in RegD containing the right-justified ADC sample (0 to 2047). Minimize errors due to dropout and overflow. Return by value the integer part of the fixed-point number in RegY. E.g., if the input voltage is 7.5 V then RegY is returned as 750.

(4) Question 5. Assume RegA = \$55, RegX=\$1234 and RegY = \$5678. What is the value in RegX after executing these instructions?

```

psha

stx 2,-sp

sty 2,sp-

leas 2,sp

pula

pulx

```

- (4) Question 6. These seven events all occur during each RDRF interrupt.

- 1) There is data in the receive data register and the hardware sets the flag bit (e.g., RDRF=1)

- 2) The SCI vector address is loaded into the PC

- 3) The I bit in the CCR is set by hardware

- 4) The software reads **SCI1DRL**

- 5) The software reads **SCI1SR1**

- 6) The CCR, A, B, X, Y, PC are pushed on the stack

- 7) The software executes rti

Which of the following sequences could be possible? Pick one answer A-F (only one is correct)

```

A) 1,3,6,2,4,5,7

```

B) 1,6,3,2,5,4,7

C) 5,1,3,4,2,6,7

D) 1,2,5,3,4,6,7

E) 1,6,3,2,4,5,7

F) None of the above sequences are possible

(10) Question 7. Write software that increments a 16-bit global variable every 1 msec using output compare 2. Show the complete main program, the OC2 ISR, the interrupt vector, and the reset vector. After initialization the main program executes a do-nothing loop. Write code as friendly as possible. Assume the E clock is 8 MHz. To make it easier for me to grade, leave TSCR2 equal to 0.

org \$0800 Count rmb 2 ;incremented every 1 msec org \$4000

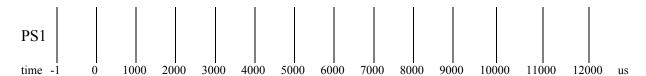

(5) Question 8. Consider a serial port operating with a baud rate of 1000 bits per second. Draw the waveform occurring at the PS1 output (voltage levels are +5 and 0) when the ASCII 'T' (\$54) is transmitted on SCI0. The protocol is 1 start, 8 data and 1 stop bit. The SCI0 is initially idle, and the software writes the \$54 to SCI0DRL at time=0. Show the PS1 line before and after the frame, assuming the channel is idle before and after the frame.

(5) Question 9. Consider a computer network where two 9S12s are connected via their SCI0 ports, using a 3-wire cable similar to Lab 7. The transmitter of computer 1 is connected to the receiver of computer 2, and the transmitter of computer 2 is connected to the receiver of computer 1. Initially, both SCI0 ports are idle. The baud rate on both computers is initialized to 1000 bits/sec, with 1 start, 8 data and 1 stop bit. Both computers have their RDRF flags armed and enabled. The transmitters are active, but not armed for interrupts. The I bit is clear in both computers. At time 0, computer 1 reads SCI0SR1 then writes to SCI0DRL. The RDRF ISR in computer 2 will read its SCI1DRL then write to its SCI1DRL (echo the data back). Approximately how long after computer 1 writes to SCI1DRL will an RDRF interrupt occur back in computer 1? Assume the software execution time is fast compared to the I/O transmission time.

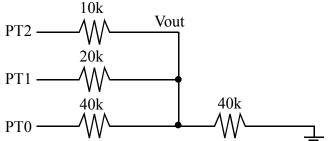

(4) Question 10. Consider the following three-bit DAC connected to Port T. Fill in the expected response table assuming  $V_{OH}$  is 5 V and  $V_{OL}$  is 0 V.

| PT2 | PT1 | PT0 | Vout (V) |

|-----|-----|-----|----------|

| 0   | 0   | 0   |          |

| 0   | 0   | 1   |          |

| 0   | 1   | 0   |          |

| 0   | 1   | 1   |          |

| 1   | 0   | 0   |          |

| 1   | 0   | 1   |          |

| 1   | 1   | 0   |          |

| 1   | 1   | 1   |          |

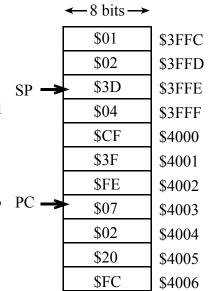

**(8) Question 11.** Assume the PC equals \$4003, and the SP equals \$3FFE. Initially, memory contains data as shown in the figure. You will be executing one instruction and answering questions about executing that one instruction.

Part a) Given the initial conditions in this figure, what instruction will be executed next?

\$3B

\$4007

Part b) As you execute that one instruction, two bytes are stored into PC -> memory? Give the addresses and the 8-bit data values that are stored.

| Data |

|------|

|      |

|      |

|      |

|      |

|      |

Part c) What is the SP after the one instruction is executed?

Part d) What is the PC after the one instruction is executed?

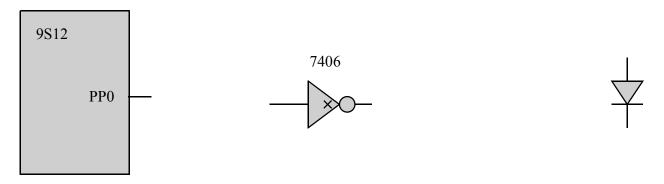

(5) Question 12. You are given an LED with a (2 V, 10 mA) operating point. Interface this LED to the 9S12 using a 7406, such that the LED is on when PP0 is high and the LED is off when PP0 is low. The  $V_{OL}$  of the 7406 is 0.5 V. Label all resistor values. No software is required.

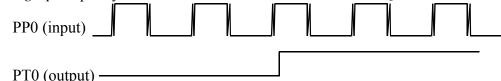

- (10) Question 13. A positive logic switch is connected to PPO and a positive logic LED is connected to PTO. Design a Moore finite state machine that counts the number of times the switch is pressed and released, so that the LED is turned on if the switch is pressed 3 or more times. The LED should come on after the switch is touched the third time. Switch bounce causes the input to toggle low/high/low/high every time the switch is touched, and to toggle high/low/high/low every time the switch is released. This bounce is typically less than 1 ms. You may assume the switch input is high for at least 100 ms when touched and low for at least 100 ms when released. In other words, the maximum rate at which the operator will push the switch is 5 times/sec. To eliminate switch bounce, you will read the input at a rate slower than every 10 ms, but faster than every 100 ms. The FSM controller will repeat this sequence in the foreground over and over

- 1) Output to the LED, as defined by the state

- 2) Wait a prescribed amount of time, as defined by the state

- 3) Input from the switch

- 4) Go to the next state, as defined by the state and by the input

Draw the FSM graph. Specify the initial state. NO SOFTWARE IS REQUIRED.

(10) Question 14. In this question, the subroutine implements a call by reference parameter passed on the stack. There are no return parameters. Call by reference means an address to the data is pushed on the stack. A typical calling sequence is

```

orq

$4000

Data fcb

100

;8-bit information

Main lds #$4000

movw #Data,2,-sp ;pointer to the Data is pushed

jsr Subroutine

leas 2,sp

;discard parameter

The subroutine allocates one 8-bit local variable, L1, and uses RegY frame pointer addressing to

access the local variable and parameter. The binding for these three are

Pt set ??? ;16-bit pointer to 8-bit data

L1 set ??? ;8-bit local variable

Subroutine

leas -1,sp ;allocate L1

pshy

; save old stack frame pointer

establish new stack frame pointer;

tsy

;-----start of body-----

ldaa ????? ;Reg A = value of the parameter

staa L1,y ;save parameter into local L1

;----end of body-----

puly

leas 1,sp ;deallocate

rts

```

Part a) Show the binding for the ??? parameters in the above program.

| Pt | set |  |

|----|-----|--|

|    |     |  |

| L1 | set |  |

Part b) Show the operand for the ????? in the above program. In particular, you must use Register Y stack frame addressing, Pt binding, and bring the value of the parameter into Register A. It can be done in one instruction, but for partial credit you can use two instructions.

(15) Question 15. This FIFO queue has 8 allocated locations and can hold up to eight 8-bit data values. The picture shows it currently holding three values (shaded). The FIFO and its three variables are defined in RAM. When the counter is zero the FIFO is empty.

| org \$3900                                                      | Address Contents Index                   |

|-----------------------------------------------------------------|------------------------------------------|

| Fifo rmb 8 ;allocates 8 bytes                                   | \$3900 0                                 |

| GetI rmb 1 ;index where to find oldest data                     | \$3901 1                                 |

| PutI rmb 1 ;index where to put next data                        | \$39022                                  |

| Cnt rmb 1 ;number of elements stored in fifo                    | \$39033                                  |

| This function initializes the FIFO                              | \$3904 <u>\$56 <del>← 4</del> Oldest</u> |

|                                                                 | \$3905   \$78   5                        |

| Fifo_Init clr Cnt ;no data in Fifo                              | \$3906 \$34 <del>← 6</del> Newest        |

| <pre>clr GetI ;Get next from Fifo[GetI]</pre>                   | \$3907 7                                 |

| <pre>clr PutI ;Put next into Fifo[PutI]</pre>                   | Cnt = 3                                  |

| rts                                                             | GetI = 4                                 |

| Write an assembly subroutine, Fifo_Put, that implements the put | PutI = 7                                 |

Write an assembly subroutine, **Fifo\_Put**, that implements the put operation. The input parameter contains the data to put as call by value

in RegB, and a result code is returned in RegA. If RegA=1, then the input data was successfully stored. If RegA=0, the data could not be saved in the FIFO because it was previously full at the time of the call.

```

;input: RegB, Output: RegA=success

Fifo_Put

```

| aba         | 8-bit add RegA=RegA+RegB                                      | des          | 16-bit decrement RegSP                             |

|-------------|---------------------------------------------------------------|--------------|----------------------------------------------------|

| abx         | unsigned add RegX=RegX+RegB                                   | dex          | 16-bit decrement RegX                              |

| aby         | unsigned add RegY=RegY+RegB                                   | dey          | 16-bit decrement RegY                              |

| adca        | 8-bit add with carry to RegA                                  | _            | RegY=(Y:D)/RegX, unsigned divide                   |

| adcb        | 8-bit add with carry to RegB                                  |              | RegY=(Y:D)/RegX, signed divide                     |

| adda        | 8-bit add to RegA                                             |              | 16 by 16 signed multiply, 32-bit add               |

| addb        | 8-bit add to RegB                                             |              | 16-bit unsigned maximum in RegD                    |

| addd        | 16-bit add to RegD                                            |              | 16-bit unsigned maximum in memory                  |

| anda        | 8-bit logical and to RegA                                     |              | 16-bit unsigned minimum in RegD                    |

| andb        | 8-bit logical and to RegB                                     | eminm        | 16-bit unsigned minimum in memory                  |

| andcc       | 8-bit logical and to RegCC                                    | emul         | RegY:D=RegY*RegD unsigned multiply                 |

| asl/l       | s1 8-bit left shift Memory                                    | emuls        | RegY:D=RegY*RegD signed multiply                   |

|             | lsla 8-bit left shift RegA                                    |              | 8-bit logical exclusive or to RegA                 |

|             | lslb 8-bit arith left shift RegB                              |              | 8-bit logical exclusive or to RegB                 |

| asld/       | lsld 16-bit left shift RegD                                   | etbl         | 16-bit look up and interpolation                   |

| asr         | 8-bit arith right shift Memory                                | exg          | exchange register contents exg X, Y                |

| asra        | 8-bit arith right shift to RegA                               | fdiv         | unsigned fract div, X=(65536*D)/X                  |

| asrb        | 8-bit arith right shift to RegB                               | _            | increment and branch if result=0 ibeq Y,loop       |

| bcc         | branch if carry clear                                         | ibne         | increment and branch if result ≠ 0 ibne A, loop    |

| bclr        | bit clear in memory bclr PTT, #\$01                           |              | 16-bit unsigned div, X=D/X, D=remainder            |

| bcs         | branch if carry set                                           |              | 16-bit signed divide, X=D/X, D= remainder          |

| beq         | branch if result is zero (Z=1)                                | inc          | 8-bit increment memory                             |

| bge         | branch if signed ≥ enter background debug mode                | inca         | 8-bit increment RegA<br>8-bit increment RegB       |

| bgnd<br>bat | branch if signed >                                            | incb<br>ins  | 16-bit increment RegSP                             |

| bgt<br>bhi  | branch if unsigned >                                          | inx          | 16-bit increment RegX                              |

| bhs         | branch if unsigned ≥                                          | iny          | 16-bit increment RegY                              |

| bita        | 8-bit and with RegA, sets CCR                                 | jmp          | jump always                                        |

| bitb        | 8-bit and with RegB, sets CCR                                 | jsr          | jump to subroutine                                 |

| ble         | branch if signed ≤                                            | lbcc         | long branch if carry clear                         |

| blo         | branch if unsigned <                                          | lbcs         | long branch if carry set                           |

| bls         | branch if unsigned ≤                                          | lbeq         | long branch if result is zero                      |

| blt         | branch if signed <                                            | lbge         | long branch if signed ≥                            |

| bmi         | branch if result is negative (N=1)                            | lbgt         | long branch if signed >                            |

| bne         | branch if result is nonzero (Z=0)                             | lbhi         | long branch if unsigned >                          |

| bpl         | branch if result is positive (N=0)                            | lbhs         | long branch if unsigned $\geq$                     |

| bra         | branch always                                                 | lble         | long branch if signed $\leq$                       |

| brclr       | branch if bits are clear brclr PTT, #\$01, loop               | lblo         | long branch if unsigned <                          |

| brn         | branch never                                                  | lbls         | long branch if unsigned $\leq$                     |

|             | branch if bits are set brset PTT, #\$01, loop                 | lblt         | long branch if signed <                            |

| bset        | bit set clear in memory bset PTT, #\$04                       | lbmi         | long branch if result is negative                  |

| bsr         | branch to subroutine                                          | lbne         | long branch if result is nonzero                   |

| bvc         | branch if overflow clear                                      | lbpl         | long branch if result is positive                  |

| bvs         | branch if overflow set                                        | lbra         | long branch always                                 |

| call        | subroutine in expanded memory<br>8-bit compare RegA with RegB | lbrn<br>lbvc | long branch never<br>long branch if overflow clear |

| cba<br>clc  | clear carry bit, C=0                                          | lbvs         | long branch if overflow set                        |

| cli         | clear I=0, enable interrupts                                  | ldaa         | 8-bit load memory into RegA                        |

| clr         | 8-bit memory clear                                            | ldab         | 8-bit load memory into RegB                        |

| clra        | RegA clear                                                    | ldd          | 16-bit load memory into RegD                       |

| clrb        | RegB clear                                                    | lds          | 16-bit load memory into RegSP                      |

| clv         | clear overflow bit, V=0                                       | ldx          | 16-bit load memory into RegX                       |

| cmpa        | 8-bit compare RegA with memory                                | ldy          | 16-bit load memory into RegY                       |

| cmpb        | 8-bit compare RegB with memory                                | leas         | 16-bit load effective addr to SP leas 2, sp        |

| com         | 8-bit logical complement to memory                            | leax         | 16-bit load effective addr to X leax 2,x           |

| coma        | 8-bit logical complement to RegA                              | leay         | 16-bit load effective addr to Y leay 2, y          |

| comb        | 8-bit logical complement to RegB                              | lsr          | 8-bit logical right shift memory                   |

| cpd         | 16-bit compare RegD with memory                               | lsra         | 8-bit logical right shift RegA                     |

| срх         | 16-bit compare RegX with memory                               | lsrb         | 8-bit logical right shift RegB                     |

| сру         | 16-bit compare RegY with memory                               | lsrd         | 16-bit logical right shift RegD                    |

| daa         | 8-bit decimal adjust accumulator                              | maxa         | 8-bit unsigned maximum in RegA                     |

| dbeq        | decrement and branch if result=0 dbeq Y, loop                 | maxm         | 8-bit unsigned maximum in memory                   |

| dbne        | decrement and branch if result ≠0 dbne A, loop                | mem          | determine the membership grade                     |

| dec         | 8-bit decrement memory                                        | mina         | 8-bit unsigned minimum in RegA                     |

| deca        | 8-bit decrement RegA                                          | minm         | 8-bit unsigned minimum in memory                   |

| decb        | 8-bit decrement RegB                                          | movb         | 8-bit move memory to memory movb #100,PTT          |

| movw                                                                                                                 | 16-bit move memory to memory movw #13, SCIBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | wai wait for in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                                                                                                                                                                                                          |                                                                                                                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| mul                                                                                                                  | RegD=RegA*RegB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fuzzy logic average                                                                                                                                                                                                        |                                                                                                                                                                                              |  |

| neg                                                                                                                  | 8-bit 2's complement negate memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | xgdx exchange RegD with RegX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                              |  |

| nega                                                                                                                 | 8-bit 2's complement negate RegA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xgdy exchange RegD with RegY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                              |  |

| negb                                                                                                                 | 8-bit 2's complement negate RegB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |                                                                                                                                                                                              |  |

| oraa                                                                                                                 | 8-bit logical or to RegA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mode                                                                                                                                                                                                                       | Effective Address                                                                                                                                                                            |  |

| orab                                                                                                                 | 8-bit logical or to RegB<br>8-bit logical or to RegCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ldaa #u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | immediate                                                                                                                                                                                                                  | No EA                                                                                                                                                                                        |  |

| orcc<br>psha                                                                                                         | push 8-bit RegA onto stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ldaa u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | direct                                                                                                                                                                                                                     | EA is 8-bit address                                                                                                                                                                          |  |

| psha                                                                                                                 | push 8-bit RegB onto stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ldaa U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | extended                                                                                                                                                                                                                   | EA is a 16-bit address                                                                                                                                                                       |  |

| pshc                                                                                                                 | push 8-bit RegCC onto stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |                                                                                                                                                                                              |  |

| pshd                                                                                                                 | push 16-bit RegD onto stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ldaa m,r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-bit index                                                                                                                                                                                                                | EA=r+m (-16 to 15)                                                                                                                                                                           |  |

| pshx                                                                                                                 | push 16-bit RegX onto stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ldaa v,+r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | pre-incr                                                                                                                                                                                                                   | r=r+v, EA=r (1 to 8)                                                                                                                                                                         |  |

| pshy                                                                                                                 | push 16-bit RegY onto stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ldaa v,-r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | pre-dec                                                                                                                                                                                                                    | r=r-v, EA=r (1 to 8)                                                                                                                                                                         |  |

| pula                                                                                                                 | pop 8 bits off stack into RegA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ldaa v,r+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | post-inc                                                                                                                                                                                                                   | EA=r, r=r+v (1 to 8)                                                                                                                                                                         |  |

| pulb                                                                                                                 | pop 8 bits off stack into RegB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ldaa v,r-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | post-dec                                                                                                                                                                                                                   | EA=r, r=r-v (1 to 8)                                                                                                                                                                         |  |