First: Last: Last: This is a closed book exam. You must put your answers on pages 1,2,3,4 only. You have 50 minutes, so allocate your time accordingly. Show your work, and put your answers in the boxes. *Please read the entire quiz before starting.* (4) Question 1. Digital logic currently uses binary because it is fast, low power, and very small. In the future, an EE319K student invents ternary logic that is faster, smaller and lower power than binary. This means each ternary bit can be 0, 1, or 2. Ternary means base 3 in the same way binary means base 2. What is the value of the unsigned four-digit ternary number 1201? Give your answer as a decimal number.

| (3) Question 2. Answer true/false for each of the following three statements<br>Part a) Flash EEPROM memory on the LM3S1968 is volatile  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|--|

| Part b) I add three 32-bit numbers by executing ADD twice. The order in which I add the numbers affects the final value of the carry bit |  |

| Part c) Dropout error can occur on a logical right shift (e.g., LSR)                                                                     |  |

(4) Question 3. Consider the following 8-bit subtraction (assume registers are 8 bits wide)

Load -100 into R1 Load +50 into R2 Subtract R3 = R1-R2

What will be the value of the overflow (V) bit?

What will be the value of the carry (C) bit?

(4) Question 4. What is the binary representation of 8-bit signed number -10?

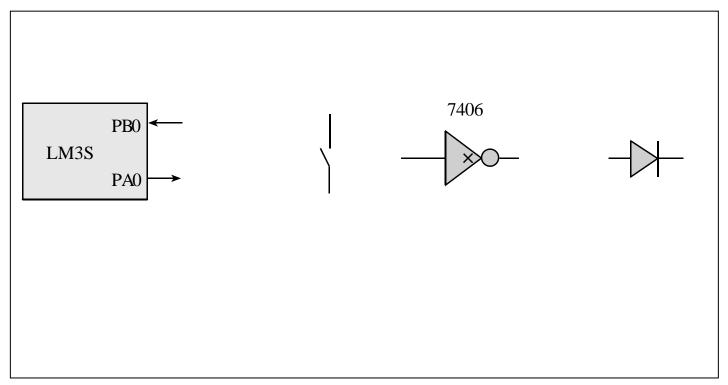

(20) Question 5. Interface the LED to PA0. The desired LED operating point is 2.0V at 25 mA. At 25 mA you can assume the  $V_{OL}$  of the 7406 will be 0.5 V. Interface the switch to PB0 using positive logic. No software is required in this question, and you may assume PA0 is an output and PB0 an input. Your bag of parts includes the switch, the 7406, the LED, and one resistor each of the values  $\{1\Omega, 10\Omega, 100\Omega, 1k\Omega, 100k\Omega, 100k\Omega \text{ and } 1M\Omega\}$ . Pick the best resistors to use (you will not need them all.)

(5) Question 6. Assume PC is \$5200, and Register X is \$1234. You may assume all RAM locations are initially 0. Show the simplified bus cycles occurring when the **stx** instruction is executed. In the "changes" column, specify which registers get modified during that cycle, and the corresponding new values. Do not worry about changes to the CCR. *Just show the one instruction*. **\$5200 stx \$2000**

For questions 7 8, and 9, don't worry about establishing the reset vector, creating a main program, or initializing the stack pointer. You may use RAM-based global variables. Include comments. You may use the following definitions

```

GPIO_PORTA_DATA_R EQU 0x40004080

GPIO_PORTA_DIR_R EQU 0x40004400

GPIO_PORTA_AFSEL_R EQU 0x40004420

GPIO_PORTA_DEN_R EQU 0x4000451C

SYSCTL_RCGC2_R EQU 0x400FE108

SYSCTL_RCGC2_GPIOA EQU 0x0000001 ; port A Clock Gating Control

```

(20) Question 7. Assume seven positive logic switches are connected to PA6-PA0, and one LED is connected to PA7. Assume the direction register is properly initialized. Write an assembly language subroutine that sets PA7=1, if PA0=1, PA2=0, and PA6=0, regardless of the other 4 switches. For all other patterns of input switches, do not change the PA7 output.

(20) Question 8. Write an assembly language subroutine that adds two unsigned 32-bit numbers. The two inputs are passed in Register R0 and Register R1, and the result is returned in Register R0. Implement ceiling, such that if the sum is too big for 32 bits, return 0xFFFFFFF.

(20) Question 9. Write an assembly language subroutine that counts the number of binary bits that are zero in a 32-bit number. The 32-bit input parameter is passed in Register R0 and the result is returned in Register R1. For example, if Register R0 = 0x00000001, return Register R1=31 because there are 31 binary zeros. If Register R0 = 0xFF0F0FFF, return Register R1 =8 because there are 8 binary zeros.

```

Memory access instructions

```

| TDD                  | ·                 |         |                                                                              | . 1  | load 22 hit number at [Dal to Dd                                |  |

|----------------------|-------------------|---------|------------------------------------------------------------------------------|------|-----------------------------------------------------------------|--|

| LDF                  |                   | d, [Rn  | -                                                                            |      | load 32-bit number at [Rn] to Rd                                |  |

|                      |                   |         |                                                                              |      | load 32-bit number at [Rn+off] to Rd                            |  |

|                      |                   | d, =va  |                                                                              |      | set Rd equal to any 32-bit value (PC rel)                       |  |

|                      |                   | 1, [Rn  |                                                                              |      | load unsigned 16-bit at [Rn] to Rd                              |  |

|                      |                   |         |                                                                              |      | load unsigned 16-bit at [Rn+off] to Rd                          |  |

|                      |                   | l, [Rn  | -                                                                            |      | load signed 16-bit at [Rn] to Rd                                |  |

| LDF                  |                   | . –     |                                                                              | ; 1  | load signed 16-bit at [Rn+off] to Rd                            |  |

| LDF                  |                   | d, [Rn  |                                                                              |      | load unsigned 8-bit at [Rn] to Rd                               |  |

| LDF                  | RB R              | d, [Rn  | ,#off]                                                                       | ; 1  | load unsigned 8-bit at [Rn+off] to Rd                           |  |

| LDF                  | RSB R             | l, [Rn  | ]                                                                            | ; 1  | load signed 8-bit at [Rn] to Rd                                 |  |

| LDF                  | RSB R             | d, [Rn  | ,#off]                                                                       | ; 1  | load signed 8-bit at [Rn+off] to Rd                             |  |

| STF                  | R R               | t, [Rn  | ]                                                                            | ; s  | store 32-bit Rt to [Rn]                                         |  |

| STF                  | R R               | t, [Rn  | ,#off]                                                                       | ; s  | store 32-bit Rt to [Rn+off]                                     |  |

| STF                  |                   | t, [Rn  |                                                                              |      | store least sig. 16-bit Rt to [Rn]                              |  |

|                      |                   |         |                                                                              |      | store least sig. 16-bit Rt to [Rn+off]                          |  |

|                      |                   | t, [Rn  |                                                                              |      | store least sig. 8-bit Rt to [Rn]                               |  |

|                      |                   |         |                                                                              |      | store least sig. 8-bit Rt to [Rn+off]                           |  |

|                      |                   | Rt}     | , "OII]                                                                      |      | push 32-bit Rt onto stack                                       |  |

| POE                  | -                 | Rd}     |                                                                              | -    | pop 32-bit number from stack into Rd                            |  |

| ADF                  |                   |         | el                                                                           | _    | set Rd equal to the address at label                            |  |

|                      |                   |         |                                                                              |      | set Rd equal to op2                                             |  |

|                      |                   |         |                                                                              |      | set Rd equal to op2<br>set Rd equal to im16, im16 is 0 to 65535 |  |

| MOV                  |                   |         |                                                                              |      |                                                                 |  |

|                      |                   | -       | 2>                                                                           | ; s  | set Rd equal to -op2                                            |  |

| Branch               |                   |         |                                                                              |      |                                                                 |  |

| В                    |                   |         | branch                                                                       |      | -                                                               |  |

| BEÇ                  | -                 |         | branch                                                                       |      |                                                                 |  |

| BNE                  |                   |         | branch                                                                       |      |                                                                 |  |

| BCS                  | S lab             | el ;    | branch                                                                       | if   | $C == 1$ Higher or same, unsigned $\geq$                        |  |

| BHS                  | S lab             |         |                                                                              |      | C == 1 Higher or same, unsigned $\geq$                          |  |

| BCC                  | lab               | el ;    | branch                                                                       | if   | C == 0 Lower, unsigned <                                        |  |

| BLC                  | ) lab             | el ;    | branch                                                                       | if   | C == 0 Lower, unsigned <                                        |  |

| BMI                  | I lab             | el ;    | branch                                                                       | if : | N == 1 Negative                                                 |  |

| BPI                  | lab               | el ;    | branch                                                                       | if : | N == 0 Positive or zero                                         |  |

| BVS                  | 3 lab             | el ;    | branch                                                                       | if ' | V == 1 Overflow                                                 |  |

| BVC                  | lab               | el ;    | branch                                                                       | if ' | V == 0 No overflow                                              |  |

| BHI                  | lab               | el ;    | branch                                                                       | if   | C == 1 and $Z == 0$ Higher, unsigned >                          |  |

| BLS                  |                   |         |                                                                              |      | $C == 0$ or $Z == 1$ Lower or same, unsigned $\leq$             |  |

| BGE                  |                   |         |                                                                              |      | $N == V$ Greater than or equal, signed $\geq$                   |  |

| BLI                  |                   |         |                                                                              |      | N != V Less than, signed <                                      |  |

| BGI                  |                   |         |                                                                              |      | Z==0 and N==V Greater than, signed >                            |  |

| BLE                  |                   |         |                                                                              |      | $Z=1$ and N!=V Less than or equal, signed $\leq$                |  |

| BX                   |                   |         |                                                                              |      | direct to location specified by Rm                              |  |

| BL                   |                   |         |                                                                              |      | subroutine at label                                             |  |

| BLX                  |                   |         |                                                                              |      | subroutine at label<br>subroutine indirect specified by Rm      |  |

|                      |                   |         | branch                                                                       | 20   | subiditine indifect specified by Kin                            |  |

| Interru              | pi msiri<br>SIE I | cuons   |                                                                              |      | anchla intermenta (T-0)                                         |  |

|                      |                   |         |                                                                              |      | enable interrupts (I=0)                                         |  |

| CPS                  | SID I             |         |                                                                              | ;    | disable interrupts (I=1)                                        |  |

| Logical instructions |                   |         |                                                                              |      |                                                                 |  |

| 0                    |                   |         |                                                                              |      | Dd-Datana (and is 20 hits)                                      |  |

|                      |                   |         |                                                                              |      | Rd=Rn&op2 (op2 is 32 bits)                                      |  |

|                      |                   |         |                                                                              |      | Rd=Rn op2 (op2 is 32 bits)                                      |  |

|                      |                   |         |                                                                              |      | Rd=Rn^op2 (op2 is 32 bits)                                      |  |

|                      |                   |         |                                                                              |      | Rd=Rn&(~op2) (op2 is 32 bits)                                   |  |

| ORN                  | N{S} {            | κα, } R | n, <op23< td=""><td>&gt;;</td><td>Rd=Rn (~op2) (op2 is 32 bits)</td></op23<> | >;   | Rd=Rn (~op2) (op2 is 32 bits)                                   |  |

Page 6

; logical shift right Rd=Rm>>Rs LSR{S} Rd, Rm, Rs (unsigned) LSR{S} Rd, Rm, #n ; logical shift right Rd=Rm>>n (unsigned) ; arithmetic shift right Rd=Rm>>Rs (signed) ASR{S} Rd, Rm, Rs ; arithmetic shift right Rd=Rm>>n (signed) ASR{S} Rd, Rm, #n LSL{S} Rd, Rm, Rs ; shift left Rd=Rm<<Rs (signed, unsigned) LSL{S} Rd, Rm, #n ; shift left Rd=Rm<<n (signed, unsigned)</pre> **Arithmetic instructions** ADD{S} {Rd,} Rn,  $\langle op2 \rangle$ ; Rd = Rn + op2ADD{S} {Rd,} Rn, #im12; Rd = Rn + im12, im12 is 0 to 4095  $SUB{S} {Rd}, Rn, <op2>; Rd = Rn - op2$ SUB{S} {Rd,} Rn, #im12 ; Rd = Rn - im12, im12 is 0 to 4095  $RSB{S} {Rd_{1}} Rn_{1} < op2 > ; Rd = op2 - Rn$  $RSB{S} {Rd_{,}} Rn_{,} \#im12 ; Rd = im12 - Rn$ CMP Rn, <op2> ; Rn - op2 sets the NZVC bits CMN Rn, <op2>; Rn - (-op2) sets the NZVC bits ; Rd = Rn \* Rmsigned or unsigned  $MUL{S} {Rd}, Rn, Rm$ MLA Rd, Rn, Rm, Ra ; Rd = Ra + Rn\*Rm signed or unsigned MT.S Rd, Rn, Rm, Ra ; Rd = Ra - Rn\*Rmsigned or unsigned UDIV {Rd,} Rn, Rm ; Rd = Rn/Rmunsigned SDIV {Rd,} Rn, Rm ; Rd = Rn/Rmsigned Notes Ra Rd Rm Rn Rt represent 32-bit registers any 32-bit value: signed, unsigned, or address value {S} if S is present, instruction will set condition codes #im12 any value from 0 to 4095 #im16 any value from 0 to 65535 if Rd is present Rd is destination, otherwise Rn {Rd, } any value from 0 to 31 #n any value from -255 to 4095 #off label any address within the ROM of the microcontroller the value generated by <op2> op2 Examples of flexible operand <op2> creating the 32-bit number. E.g., Rd = Rn+op2 ; op2 = RmADD Rd, Rn, Rm ADD Rd, Rn, Rm, LSL #n ; op2 = Rm<<n Rm is signed, unsigned ADD Rd, Rn, Rm, LSR #n ; op2 = Rm>>n Rm is unsigned ADD Rd, Rn, Rm, ASR #n ; op2 = Rm>>n Rm is signed ADD Rd, Rn, #constant ; op2 = constant, where X and Y are hexadecimal digits: produced by shifting an 8-bit unsigned value left by any number of bits • in the form **0x00XY00XY** in the form **0xXY00XY00** in the form **0xXYXYXYX** R0 0x0000.0000 R1 256k Flash R2 ROM 0x0003.FFFF **Condition code bits** R3 N negative **R**4 0x2000.0000 64k RAM General R5 Z zero purpose -R6 V signed overflow 0x2000.FFFF registers R7 C carry or R8 0x4000.0000 R9 unsigned overflow I/O ports R10 0x41FF.FFFF R11 R12 0xE000.0000 Stack pointer R13 (MSP) Internal I/O Link register R14 (LR) 0xE004.0FFF PPB Program counter R15 (PC)