| First:                                          | Last:                                              |

|-------------------------------------------------|----------------------------------------------------|

| This is a closed book exam. You must            | put your answers on this piece of paper only. You  |

| have 50 minutes, so allocate your time accordin | ngly. Please read the entire quiz before starting. |

|                                                 |                                                    |

| (5) Question 1. Answer A,B,C,D,E            |                                    |

|---------------------------------------------|------------------------------------|

| (5) Question 2. Answer \$00 to \$FF         |                                    |

| (4) Part 3a. Specify RegB                   |                                    |

| (2) Part 3b. Specify 0 or 1                 |                                    |

| (2) Part 3c. Specify 0 or 1                 |                                    |

| (2) Part 3d. Specify 0 or 1                 |                                    |

| (2) Part 3e. Specify 0 or 1                 |                                    |

| (10) Question 4. Specify <b>D</b>           |                                    |

| (10) Question 5. Show the machine code      |                                    |

| (10) Question 6. What value is pushed       |                                    |

| (10) Question 7 Simplified memory cycles (v | (an max and not need all 5 antina) |

## (10) Question 7. Simplified memory cycles (you may or may not need all 5 entries)

| R/W | Addr | Data | changes |

|-----|------|------|---------|

|     |      |      |         |

|     |      |      |         |

|     |      |      |         |

|     |      |      |         |

|     |      |      |         |

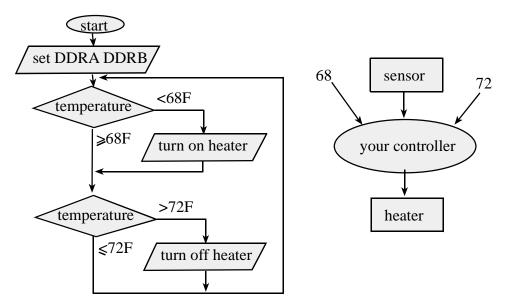

| (40) Ques | tion 8. | Write the assembly language program that implements a thermostat. |

|-----------|---------|-------------------------------------------------------------------|

| PORTA     | equ     | \$0000                                                            |

| PORTB     | equ     | \$0001                                                            |

| DDRA      | equ     | \$0002                                                            |

| DDRB      | equ     | \$0003                                                            |

| These two tables interpret indexed-mode machine codes | de machine codes |

|-------------------------------------------------------|------------------|

|-------------------------------------------------------|------------------|

| rr | register |

|----|----------|

| 00 | Х        |

| 01 | Y        |

| 10 | SP       |

| 11 | PC       |

| postbyte, xb  | syntax | mode    | explanations                |

|---------------|--------|---------|-----------------------------|

| rr000000      | ,r     | IDX     | 5-bit constant, n=0         |

| rr00nnnn      | n,r    | IDX     | 5-bit constant, n=0 to +15  |

| rr01nnnn      | -n,r   | IDX     | 5-bit constant, n=-16 to -1 |

| rr100nnn      | n,+r   | IDX     | pre-increment, n=1 to 8     |

| rr101nnn      | n,-r   | IDX     | pre-decrement, n=1 to 8     |

| rr110nnn      | n,r+   | IDX     | post-increment, n=1 to 8    |

| rr111nnn      | n,r-   | IDX     | post-decrement, n=1 to 8    |

| 111rr100      | A,r    | IDX     | Reg A accumulator offset    |

| 111rr101      | B,r    | IDX     | Reg B accumulator offset    |

| 111rr110      | D,r    | IDX     | Reg D accumulator offset    |

| 111rr000 ff   | n,r    | IDX1    | 9-bit cons, n 16 to 255     |

| 111rr001 ff   | -n,r   | IDX1    | 9-bit const, n -256 to -16  |

| 111rr010 eeff | n,r    | IDX2    | 16-bit const, any 16-bit n  |

| 111rr111      | [D,r]  | [D,IDX] | Reg D offset, indirect      |

| 111rr011 eeff | [n,r]  | [IDX2]  | 16-bit constant, indirect   |

|               |        |         |                             |

ORAB

Inclusive OR B

Operation:  $(B) + (M) \Rightarrow B$

Description: Performs bitwise logical inclusive OR between the content of accumulator B and the content of memory location M. The result is placed in B. Each bit of B after the operation is the logical inclusive OR of the corre-

sponding bits of M and of B before the operation.

Condition Codes and Boolean Formulas:

| s     | х | н | 1 | Ν | Ζ | ۷ | С |

|-------|---|---|---|---|---|---|---|

| (etc) | Ŧ | - | - | Δ | Δ | 0 | + |

N: Set if MSB of result is set; cleared otherwise.

Z: Set if result is \$00; cleared otherwise.

| Source Form        | Address Mode | Object Code | Cycles | Access Detail |

|--------------------|--------------|-------------|--------|---------------|

| ORAB #opr8i        | IMM          | CA ii       | 1      | P             |

| ORAB opr8a         | DIR          | DA dd       | 3      | rfP           |

| ORAB opr16a        | EXT          | FA hh 11    | 3      | rOP           |

| ORAB oprx0_xysp    | IDX          | EA xb       | 3      | rfP           |

| ORAB oprx9,xysp    | IDX1         | EA xb ff    | 3      | rPO           |

| ORAB oprx16,xysp   | IDX2         | EA xb ee ff | 4      | frPP          |

| ORAB [D, xysp]     | [D,IDX]      | EA xb       | 6      | fIfrfP        |

| ORAB [oprx16,xysp] | [IDX2]       | EA xb ee ff | 6      | fIPrfP        |

V. 0. Cleared

aba 8-bit add RegA+RegB unsigned add RegX+RegB abx unsigned add RegY+RegB aby adca 8-bit add with carry to RegA adcb 8-bit add with carry to RegB adda 8-bit add to RegA addb 8-bit add to RegB addd 16-bit add to RegD anda 8-bit logical and to RegA andb 8-bit logical and to RegB andcc 8-bit logical and to RegCC asl/lsl 8-bit left shift Memory asla/lsla 8-bit left shift RegA aslb/lslb 8-bit arith left shift RegB asld/lsld 16-bit left shift RegD 8-bit arith right shift Memory asr asra 8-bit arith right shift asrb 8-bit arith right shift to RegB bcc branch if carry clear bclr clear bits in memory branch if carry set bcs branch if result is zero (Z=1) beq branch if signed = bge bynd enter background debug mode bgt branch if signed > branch if unsigned > bhi bhs branch if unsigned = 8-bit and with RegA, sets CCR bita bitb 8-bit and with RegB, sets CCR ble branch if signed = branch if unsigned < blo bls branch if unsigned = branch if signed < blt branch if result is negative (N=1) bmi branch if result is nonzero (Z=O) bne bpl branch if result is positive (N=0) branch always bra brclr branch if bits are clear, branch never brn brset branch if bits are set bset set bits in memory bsr branch to subroutin branch to subroutine bsr branch if overflow clear bvc branch if overflow set bvs call subroutine in expanded memory 8-bit compare RegA with RegB cba clc clear carry bit, C=0 cli clear I=0, enable interrupts 8-bit Memory clear clr clra RegA clear clrb RegB clear ClipRegB clearmaxaclvclear overflow bit, V=0maxmcmpa8-bit compare RegA with memorymemcmpb8-bit compare RegB with memoryminacom8-bit logical complement to Memoryminmcoma8-bit logical complement to RegAmovbcomb8-bit logical complement to RegBmovbcomb8-bit logical complement to RegBmovbcpd16-bit compare RegD with memorymulcpx16-bit compare RegZ with memorynegcpy16-bit compare RegY with memorynegdaa8-bit decimal adjust accumulatornegb clear overflow bit, V=0 daa 8-bit decimal adjust accumulator dbeq decrement and branch if result=0 dbne decrement and branch if result?0 8-bit decrement memory dec deca 8-bit decrement RegA decb 8-bit decrement RegB 16-bit decrement RegSP des 16-bit decrement RegX dex dey 16-bit decrement RegY ediv RegY=(Y:D)/RegX, unsigned divide edivs RegY=(Y:D)/RegX, signed divide emacs 16 by 16 signed mult, 32-bit add emaxd 16-bit unsigned maximum in RegD emaxm16-bitunsigned maximum in memorypuldpop 16bitsoffstackinto RegDeminm16-bitunsigned minimum in RegDpulxpop 16bitsoffstackinto RegXeminm16-bitunsigned minimum in memorypulypop 16bitsoffstackinto RegX

emul RegY:D=RegY\*RegD unsigned mult emuls ReqY:D=ReqY\*ReqD signed mult emuls Regivernegt Regimented eora 8-bit logical exclusive or to Reg eorb 8-bit logical exclusive or to Reg etbl 16-bit look up and interpolation exg exchange register contents fdiv 16-bit unsigned fractional divide ibeq increment and branch if result=0 8-bit logical exclusive or to RegA 8-bit logical exclusive or to RegB 16-bit unsigned fractional divide ibeq increment and branch if recu-ibne increment and branch if recu-idiv 16-bit unsigned divide idivs 16-bit by 16-bit signed divide inc 8-bit increment memory inca 8-bit increment RegA incb 8-bit increment RegB ins 16-bit increment RegSP inx 16-bit increment RegY iny 16-bit increment RegY jmp jump always jsr jump to subroutine lbcc long branch if carry clear 'bes long branch if carry set in' if result is zero increment and branch if result?0 lbeq long branch if result is zero long branch if signed = lbge lbgt long branch if signed > lbhi long branch if unsigned > lbhs long branch if unsigned = lble lblo long branch if signed = long branch if unsigned < lbls long branch if unsigned = lblt long branch if signed < lbmi long branch if result is negative lbne long branch if result is nonzero lbpl long branch if result is positive lbra lbra lbrn lbvc lbra long branch always long branch never long branch if overflow clear lbvs long branch if overflow set 8-bit load memory into RegA 8-bit load memory into RegB ldaa Idab 8-bit load memory into RegB Idd 16-bit load memory into RegD Ids 16-bit load memory into RegSP Idx 16-bit load memory into RegX Idy 16-bit load memory into RegY leas 16-bit load effective addr to SP leax 16-bit load effective addr to X leay 16-bit load effective addr to Y lear 6-bit load effective addr to Y ldab lsr 8-bit logical right shift memory lsra lsrb 8-bit logical right shift RegA 8-bit logical right shift RegB lsrd 16-bit logical right shift RegD maxa 8-bit unsigned maximum in RegA maxm 8-bit unsigned maximum in memory determine the membership grade mina 8-bit unsigned minimum in RegA 8-bit unsigned minimum in memory minm movb 8-bit move memory to memory mov~ movw 16-bit move memory to memory mul RegD=RegA\*RegB 8-bit 2's complement negate memory 8-bit 2's complement negate RegA nega negb 8-bit 2's complement negate RegB 8-bit logical or to RegA oraa orab 8-bit logical or to RegB 8-bit logical or to RegCC orcc psha push 8-bit RegA onto stack pshb push 8-bit RegB onto stack pshc push 8-bit RegCC onto stack pshd push 16-bit RegD onto stack pshx push 16-bit RegX onto stack push 16-bit RegY onto stack pshy pula pop 8 bits off stack into RegA pulb pop 8 bits off stack into RegA pulc pop 8 bits off stack into RegCC

| subb  | 8-bit sub from RegB             |

|-------|---------------------------------|

| subd  | 3                               |

| swi   |                                 |

| tab   | transfer A to B                 |

|       | transfer A to CC                |

| t.ba  |                                 |

|       | test and branch if result=0     |

| tbl   | 8-bit look up and interpolation |

| t.bne |                                 |

| tfr   | transfer register to register   |

| tpa   | transfer CC to A                |

| trap  |                                 |

| trap  |                                 |

| tst   |                                 |

| tsta  |                                 |

| tstb  |                                 |

| tsx   |                                 |

|       | transfer S+1 to Y               |

| -     | transfer X-1 to S               |

|       | transfer Y-1 to S               |

| wai   | wait for interrupt              |

| wav   | weighted Fuzzy logic average    |

| xqdx  |                                 |

| xqdy  | exchange ReqD with ReqY         |

| example    | addressing mode | Effective Address              |

|------------|-----------------|--------------------------------|

| ldaa #u    | immediate       | EA is 8-bit address (0 to 255) |

| ldaa u     | direct          | EA is 8-bit address (0 to 255) |

| ldaa U     | extended        | EA is a 16-bit address         |

| ldaa m,r   | 5-bit index     | EA=r+m (-16 to 15)             |

| ldaa v,+r  | pre-increment   | r=r+v, EA=r (1 to 8)           |

| ldaa v,-r  | pre-decrement   | r=r-v, EA=r (1 to 8)           |

| ldaa v,r+  | post-increment  | EA=r, r=r+v (1 to 8)           |

| ldaa v,r-  | post-decrement  | EA=r, r=r-v (1 to 8)           |

| ldaa A,r   | Reg A offset    | EA=r+A, zero padded            |

| ldaa B,r   | Reg B offset    | EA=r+B, zero padded            |

| ldaa D,r   | Reg D offset    | EA=r+D                         |

| ldaa q,r   | 9-bit index     | EA=r+q (-256 to 255)           |

| ldaa W,r   | 16-bit index    | EA=r+W (-32768 to 65535)       |

| ldaa [D,r] | D indirect      | EA={r+D}                       |

| ldaa [W,r] | indirect        | $EA=\{r+W\}$ (-32768 to 65535) |

Motorola 6812 addressing modes

(5) **Question 1.** Which term best describes a memory that retains its information when power is removed and restored?

A) nonvolatile B) volatile C) memory mapped D) friendly E) none of these

(5) Question 2. What is the 8-bit unsigned hexadecimal representation of the number 171?

Question 3. Consider the result of executing the following two 6812 assembly instructions.

## ldab #101 subb #110

(4) **Part a**) What is the value in Register B after these two instructions are executed? Give your answer in unsigned decimal (0 to 255).

(2) Part b) What will be the value of the carry (C) bit?

(2) Part c) What will be the value of the overflow (V) bit?

(2) Part d) What will be the value of the zero (Z) bit?

(2) Part e) What will be the value of the negative (N) bit?

(10) Question 4. The range of values spans 0 to 0.255 (2.55e-1), and you will use an 8-bit unsigned decimal fixed-point format. What resolution **D** would be best?

(10) Question 5. Show the machine code generated by the instruction

|         | OI        | cab -  | 20,у          |                    |            |         |                                      |

|---------|-----------|--------|---------------|--------------------|------------|---------|--------------------------------------|

| (10) Qu | estion 6. | When t | he <b>bsr</b> | <b>sub</b> instruc | ction is e | xecuted | , what value is pushed on the stack? |

| \$F120  | CF0C00    | ] [    | 2](           | 0){OP              | }main      | lds     | #\$0C00                              |

| \$F123  | 87        | [      | 1](           | 2){0               | }          | clra    |                                      |

| \$F124  | 0766      | [      | 4](           | 3){PPPS            | }loop      | bsr     | sub                                  |

| \$F126  | 20FC      | [      | 3](           | 7){PPP             | }          | bra     | loop                                 |

|         |           |        |               |                    | ; Pu       | rpose   | : increment a number                 |

|         |           |        |               |                    | ; Inj      | put:    | RegA, range 0 to 255                 |

|         |           |        |               |                    | ; Ou       | tput:   | RegA=Input+1                         |

|         |           |        |               |                    | ; Er:      | rors:   | overflow if 255                      |

| \$F18C  |           |        |               | 10){O              | }sub       | inca    |                                      |

| \$F18D  | 3D        | [      | 5](           | 11){Ufppp          | <b>P</b> } | rts     |                                      |

| \$FFFE  |           |        |               |                    |            | org     | \$fffe                               |

| \$FFFE  | F120      |        |               |                    |            | fdb 1   | main                                 |

| (10) 0  |           | ~.     |               | 11.01 1            |            |         |                                      |

(10) Question 7. Give the simplified memory cycles produced when the following one instruction is executed. Assume the PC contains \$F129, Reg Y equals \$0980, Reg B is 0, and each memory location from \$0900 to \$09FF contains a value equal to the least significant byte of its address. I.e., \$0900 contains \$00, \$0901 contains \$01, \$0902 contains \$02 etc. Show changes during the cycle they occur to the memory, PC, Y, B, IR, and EAR. Ignore changes to the CCR.

\$F129 EA4A [ 3](3){rfP } orab 10,y

(40) Question 8. Write the assembly language program that implements a thermostat. PORTB is an 8bit output that controls the heater to the room. If you set PORTB to \$00, the heater will go off. If you set PORTB to \$FF, then the heater will turn on. PORTA is an 8-bit input containing the current temperature in unsigned binary fixed-point format with a resolution of  $2^{-1}$ °F. The range is 0°F to 127.5°F. For example, if the room temperature is 70°F, then reading PORTA will return 140 (decimal). If the temperature goes below 68°F, turn the heater on. If it goes above 72°F, turn the heater off.

| <u> </u>        |                   |                 |                  |                 |                   |                                         |                  |                  |                    | 1                |                    |                  | 1 - 11                                  |                   |                          |

|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------------------------------|------------------|------------------|--------------------|------------------|--------------------|------------------|-----------------------------------------|-------------------|--------------------------|

| 00              | 10                | 20              | 30               | 40              | 50                | 60                                      | 70               | 80               | 90                 | A0               | BO                 | CO               | D0                                      | E0                | F0                       |

| 0,X             | -16,X             | 1,+X            | 1,X+             | 0.Y             | -16,Y             | 1,+Y                                    | 1,Y+             | 0,SP             | -16,SP             | 1,+SP            | 1,SP+              | 0,PC             | -16,PC                                  | n,X<br>9b const   | n,SP<br>9b const         |

| 5b const        | 5b const          | pre-inc         | post-inc         | 5b const        | 5b const          | pre-inc                                 | post-inc         | 5b const         | 5b const           | pre-inc          | post-inc           | 5b const         | 5b const                                |                   | 1. And the second second |

| 01              | 11                | 21              | 31               | 41              | 51                | 61                                      | 71               | 81               | 91                 | A1               | B1                 | C1               | D1                                      | E1                | F1                       |

| 1,X             | -15,X             | 2,+X            | 2,X+             | 1,Y             | -15,Y             | 2,+Y                                    | 2,Y+             | 1,SP             | -15,SP             | 2,+SP            | 2,SP+              | 1,PC<br>5b const | -15,PC<br>5b const                      | -n,X<br>9b const  | -n,SP<br>9b const        |

| 5b const        | 5b const          | pre-inc         | post-inc         | 5b const        | 5b const          | pre-inc                                 | post-inc         | 5b const         | 5b const           | pre-inc          | post-inc           |                  |                                         |                   |                          |

| 02              | 12                | 22              | 32               | 42              | 52                | 62                                      | 72               | 82               | 92                 | A2               | B2                 | C2               | D2                                      | E2                | F2                       |

| 2,X             | -14,X             | 3,+X            | 3,X+             | 2,Y             | -14,Y             | 3,+Y                                    | 3,Y+             | 2,SP             | -14,SP<br>5b const | 3,+SP<br>pre-inc | 3,SP+<br>post-inc  | 2,PC<br>5b const | -14,PC<br>5b const                      | n,X<br>16b const  | n,SP<br>16b const        |

| 5b const        | 5b const          | pre-inc         | post-inc         | 5b const        | 5b const          | pre-inc                                 | post-inc         | 5b const         |                    |                  | 1                  |                  |                                         |                   |                          |

| 03              | 13                | 23              | 33               | 43              | 53                | 63                                      | 73               | 83               | 93                 | A3               | B3                 | C3               | D3                                      | E3                | F3                       |

| 3,X             | -13,X             | 4,+X            | 4,X+             | 3,Y             | -13,Y             | 4,+Y                                    | 4,Y+<br>post-inc | 3,SP<br>5b const | -13,SP<br>5b const | 4,+SP<br>pre-inc | 4,SP+<br>post-inc  | 3,PC<br>5b const | -13,PC<br>5b const                      | [n,X]<br>16b indr | [n,SP]<br>16b indr       |

| 5b const        | 5b canst          | pre-inc         | post-inc         | 5b const        | 5b canst          | pre-inc                                 |                  |                  |                    | -                | Part of Carton and |                  |                                         | 1 Marsh 6 6 6 6 7 | F4                       |

| 04              | 14                | 24              | 34               | 44              | 54                | 64                                      | 74               | 84               | 94                 | A                | B4                 | C4<br>4.PC       | D4<br>-12.PC                            | E4<br>AX          | A.SP                     |

| 4,X             | -12,X             | 5,+X            | 5,X+             | 4.Y<br>Sp const | -12,Y<br>5b const | 5,+Y<br>pre-inc                         | 5,Y+<br>post-inc | 4,SP<br>5b const | -12,SP<br>5b const | 5,+SP<br>pre-inc | 5,SP+<br>post-inc  | 5 const          | 5b canst                                | A offset          | A offset                 |

| 5b const        | 5b canst          | pre-inc         | post-inc         |                 | - 212/09/21/2010  | *                                       |                  |                  |                    |                  |                    | and the set      |                                         |                   |                          |

| 05              | 15                | 25              | 35               | 45              | 55                | 65                                      | 75               | 85               | 95                 | AS               | 85<br>6.SP+        | C5<br>5.PC       | D5<br>-11,PC                            | E5<br>B.X         | F5<br>B.SP               |

| 5,X             | -11,X             | 6,+X<br>pre-inc | 6,X+<br>post-inc | 5,Y<br>5b const | -11,Y<br>5b const | 6,+Y<br>pre-inc                         | 6,Y+<br>post-inc | 5,SP<br>5b const | -11,SP<br>5b const | 6,+SP<br>pre-inc | post-inc           | 5b const         | 5b const                                | B offset          | B offset                 |

| 5b const        | 5b const          |                 |                  |                 |                   | P                                       |                  |                  |                    | -                | 8                  | 100000000000000  | 100000000000000000000000000000000000000 |                   |                          |

| 06              | 16                | 26              | 36               | 46              | 56                | 66                                      | 76               | 86               | 96<br>-10.SP       | A6<br>7.+SP      | 86<br>7.SP+        | 06<br>6.PC       | D6<br>-10.PC                            | E6<br>DX          | F6<br>D.SP               |

| 6,X<br>5b const | -10,X<br>5b const | 7,+X<br>pre-inc | 7,X+<br>post-inc | 6,Y<br>5b const | -10,Y<br>5b const | 7,+Y                                    | 7,Y+<br>post-inc | 6,SP<br>5b const | 5b const           | pre-inc          | post-inc           | 5b const         | 5b const                                | Doffset           | D offset                 |

|                 |                   |                 |                  |                 |                   |                                         |                  |                  | -                  |                  | 5                  |                  |                                         | E7                | F7                       |

| 07              | 17                | 27              | 37               | 47              | 57                | 67                                      | 77<br>8.Y+       | 87<br>7.SP       | 97<br>-9.SP        | A7<br>8.+SP      | 87<br>8.SP+        | C7<br>7.PC       | D7<br>-9.PC                             | ID,XI             | F7<br>[D.SP]             |

| 7,X<br>5b const | -0,X<br>5b const  | 8,+X<br>pre-inc | 8,X+<br>post-inc | 7,Y<br>5b const | -0,Y<br>5b const  | 8,+Y<br>pre-inc                         | post-inc         | 5b const         | 5b const           | pre-inc          | post-inc           | 5b const         | 5b const                                | D indirect        | D indirect               |

| Sec. 2011. 1920 |                   | 1               |                  |                 |                   | 1                                       | 78               | 88               |                    | A8               | B8                 | C8               | D8                                      | E8                | F8                       |

| 08              | 18                | 28              | 38               | 48              | 58<br>-8.Y        | 68<br>8Y                                | 78<br>8.Y-       | 88<br>8.SP       | 98<br>8,SP         | A8<br>8SP        | 8.SP-              | 8.PC             | -8.PC                                   | LO n.Y            | n.PC                     |

| 8,X<br>5b const | -8,X<br>5b const  | 8,-X<br>pre-dec | 8,X-<br>post-dec | 8,Y<br>5b const | 5b const          | pre-dec                                 | post-dec         | 5b const         | 5b const           | pre-dec          | post-dec           | 5b const         | 5b const                                | 9b const          | 9b const                 |

|                 |                   |                 | 39               | 49              | 59                | 69                                      | 79               | 89               | 99                 | A9               | B9                 | C9               | D9                                      | E9                | F9                       |

| 09<br>9,X       | 19<br>-7,X        | 29<br>7X        | 39<br>7.X-       | 99 9.Y          | 59<br>-7.Y        | 09<br>7Y                                | 7.Y-             | 9.SP             | -7.SP              | 7SP              | 7.SP-              | 9.PC             | -7.PC                                   | -n.Y              | -n.PC                    |

| 5b const        | 5b const          | pre-dec         | post-dec         | 5b const        | 5b const          | pre-dec                                 | post-dec         | 5b const         | 5b const           | pre-dec          | post-dec           | 5b const         | 5b const                                | 9b const          | 9b const                 |

| 0A              | 1A                | 2A              | 34               | 4A              | 5A                | 6A                                      | 7A               | 8A               | 9A                 | AA               | BA                 | CA               | DA                                      | EA                | FA                       |

| 10.X            | -6.X              | 6X              | 6.X-             | 10.Y            | -6.Y              | 6Y                                      | 6.Y-             | 10.SP            | -6.SP              | 6,-SP            | 6.SP-              | 10.PC            | -6.PC                                   | n.Y               | n.PC                     |

| 5b const        | 5b const          | pre-dec         | post-dec         | 5b const        | 5b const          | pre-dec                                 | post-dec         | 5b const         | 5b const           | pre-dec          | post-dec           | 5b const         | 5b const                                | 16b const         | 16b const                |

| 08              | 1B                | 28              | 38               | 4B              | 58                | 6B                                      | 7B               | 8B               | 98                 | AB               | BB                 | CB               | DB                                      | EB                | FB                       |

| 11.X            | -5.X              | 5X              | 5.X-             | 4D 11.Y         | -5.Y              | 5Y                                      | 5.Y-             | 11.SP            | -5.SP              | 5SP              | 5.SP-              | 11.PC            | -5.PC                                   | [n,Y]             | In.PCI                   |

| 5b const        | 5b const          | pre-dec         | post-dec         | 5b const        | 5b const          | pre-dec                                 | post-dec         | 5b const         | 5b const           | pre-dec          | post-dec           | 5b const         | 5b const                                | 16b indr          | 16b indr                 |

| 0C              | 1C                | 2C              | 30               | 4C              | 50                | 6C                                      | 70               | 8C               | 90                 | AC               | BC                 | CC               | DC                                      | EC                | FC                       |

| 12.X            | -4X               | 4X              | 4.X-             | 12,Y            | -4.Y              | 4Y                                      | 4.Y-             | 12.SP            | -4.SP              | 4SP              | 4.SP-              | 12.PC            | -4.PC                                   | A,Y               | A,PC                     |

| 5b const        | 5b const          | pre-dec         | post-dec         | 5b const        | 5b const          | pre-dec                                 | post-dec         | 5b const         | 5b const           | pre-dec          | post-dec           | 5b const         | 5b const                                | Aoffset           | A offset                 |

| 0D              | 1D                | 2D              | 3D               | 4D              | 5D                | 6D                                      | 7D               | 8D               | 9D                 | AD               | BD                 | CD               | DD                                      | ED                | FD                       |

| 13,X            | -3,X              | 3X              | 3,X-             | 13,Y            | -3,Y              | 3,-Y                                    | 3,Y-             | 13,SP            | -3,SP              | 3,-SP            | 3.SP-              | 13,PC            | -3,PC                                   | B,Y               | B,PC                     |

| 5b const        | 5b const          | pre-dec         | post-dec         | 5b const        | 5b const          | pre-dec                                 | post-dec         | 5b const         | 5b const           | pre-dec          | post-dec           | 5b const         | 5b const                                | B offset          | B offset                 |

| 0E              | 1E                | 2E              | 3E               | 4E              | 5E                | 6E                                      | 7E               | 8E               | 9E                 | AE               | BE                 | CE               | DE                                      | EE                | FE                       |

| 14.X            | -2,X              | 2-X             | 2,X-             | 14,Y            | -2,Y              | 2-Y                                     | 2.Y-             | 14,SP            | -2,SP              | 2,-SP            | 2,SP-              | 14,PC            | -2,PC                                   | D,Y               | D,PC                     |

| 5b const        | 5b const          | pre-dec         | post-dec         | 5b const        | 5b const          | pre-dec                                 | post-dec         | 5b const         | 5b const           | pre-dec          | post-dec           | 5b const         | 5b const                                | D offset          | D offset                 |

| 0F              | 1F                | 2F              | 3F               | 4F              | 5F                | 6F                                      | 7F               | 8F               | 9F                 | AF               | BF                 | CF               | DF                                      | EF                | FF                       |

|                 |                   |                 |                  | 15.Y            | -1.Y              | 1,-Y                                    | 1.Y-             | 15.SP            | -1.SP              | 1SP              | 1.SP-              | 15.PC            | -1.PC                                   | [D,Y]             | [D.PC]                   |

| 15,X            | -1,X              | 1,-X            | 1,X-             | 13, 1           | -1.1              | 1. A | 1,1-             | 10,01            | -1,51              | 1, WI            | 1,00               | 10,00            | -1,-0                                   | 10.0              |                          |

Table A-3 Indexed Addressing Mode Postbyte Encoding (xb)