First:\_\_\_\_\_ Last:\_\_\_\_\_

This is a closed book exam. You must put your answers on this piece of paper only. You have 50 minutes, so allocate your time accordingly. *Please read the entire quiz before starting.*

| (5) Question 1. Give the hex value    |                  |

|---------------------------------------|------------------|

| (5) Question 2. Specify 0 or 1        |                  |

| (5) Question 3. Specify 0 or 1        |                  |

| (5) Question 4. Specify A-H           |                  |

| (5) Question 5. Show the equation     |                  |

| (5) Question 6. Show the machine code |                  |

| (5) Question 7. How many binary bits? |                  |

| (5) Question 8. Specify values        | RegA =<br>RegX = |

## (10) Question 9. Simplified memory cycles (you may or may not need all 5 entries)

| R/W | Addr | Data | Changes to A,B,X,Y,S,PC,IR,EAR |

|-----|------|------|--------------------------------|

|     |      |      |                                |

|     |      |      |                                |

|     |      |      |                                |

|     |      |      |                                |

|     |      |      |                                |

```

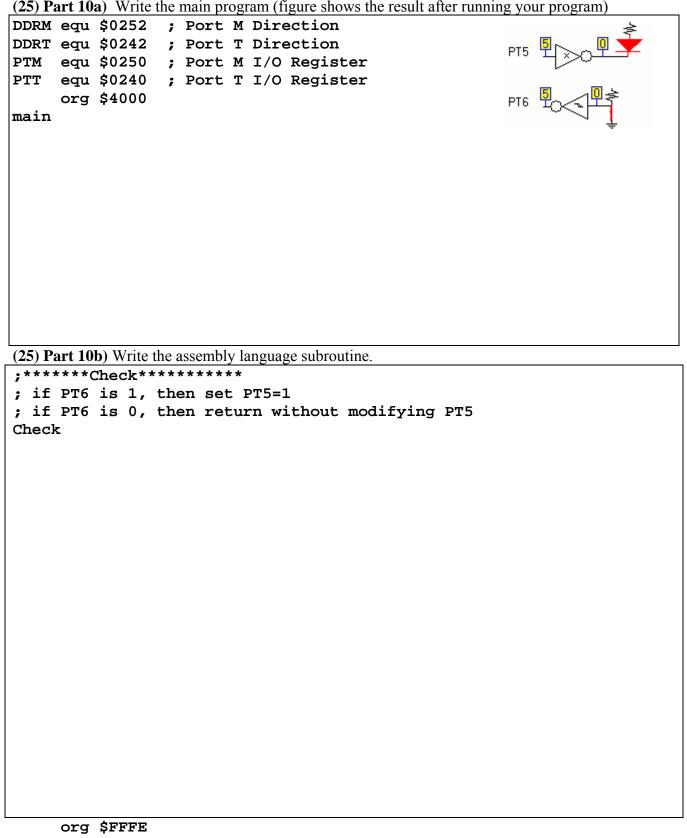

(25) Part 10a) Write the main program (figure shows the result after running your program)

```

fdb main

aba 8-bit add RegA+RegB abx unsigned add RegX+RegB abv unsigned add RegY+RegB adca 8-bit add with carry to RegA adcb 8-bit add with carry to RegB adda 8-bit add to RegA addb 8-bit add to RegB addd 16-bit add to RegD branch if unsigned > bhs branch if unsigned ≥ bita 8-bit and with RegA, sets CCR bitb 8-bit and with RegB, sets CCR ble branch if signed ≤ blo branch if unsigned < bls branch if unsigned ≤ blt branch if signed < blsbranch if unsigned >bltbranch if signed <</td>bmibranch if result is negative (N=1)bmebranch if result is nonzero (Z=0)bnebranch if result is positive (N=0)bplbranch if result is positive (N=0)brabranch alwaysbrclrbranch if bits are clear,brabranch if overflow clearbrabranch neverbrabranch if overflow setbrabrabrabranch if overflow set brnbranch neverlbvslong branch if overflow setbrsetbranch if bits are setlda8-bit load memory into RegAbsetset bits in memoryldab8-bit load memory into RegBbsrbranch to subroutineldd16-bit load memory into RegDbvcbranch if overflow clearlds16-bit load memory into RegSPbvsbranch if overflow setldx16-bit load memory into RegXcallsubroutine in expanded memoryldy16-bit load memory into RegYcba8-bit compare RegA with RegBleas16-bit load effective addr to SPclcclear carry bit, C=0leax16-bit load effective addr to Xcliclear I=0, enable interruptsleay16-bit load effective addr to Yclr8-bit Memory clearlsr8-bit logical right shift memoryclraRegA clearlsra8-bit logical right shift RegA deca8-bit decrement RegAorab8-bit logical or to RegBdecb8-bit decrement RegBorcc8-bit logical or to RegCCdes16-bit decrement RegSPpshapush 8-bit RegA onto stackdex16-bit decrement RegYpshbpush 8-bit RegB onto stackdey16-bit decrement RegYpshcpush 8-bit RegC onto stackedivRegY=(Y:D)/RegX, unsigned dividepshcpush 16-bit RegD onto stackemacs16 by 16 signed mult, 32-bit addpshypush 16-bit RegY onto stackemaxm16-bit unsigned maximum in memorypulbpop 8 bits off stack into RegB

emind 16-bit unsigned minimum in RegD eminm 16-bit unsigned minimum in memory emul RegY:D=RegY\*RegD unsigned mult emuls RegY:D=RegY\*RegD signed mult eora 8-bit logical exclusive or to RegA eorb 8-bit logical exclusive or to RegB addb8-bit add to RegBevento-nut logical exclusive or to RegBaddd16-bit add to RegDetbl16-bit look up and interpolationanda8-bit logical and to RegAfdivunsigned fract div, X=(65536\*D)/Xandb8-bit logical and to RegBibeqincrement and branch if result=0andc8-bit logical and to RegCCibneincrement and branch if result≠0asla/lsla8-bit left shift RegAidiv16-bit unsigned divide, X=D/X, D=remasla/lsla8-bit arith left shift RegBinc8-bit increment RegAasr8-bit arith right shiftinc8-bit increment RegBasr8-bit arith right shiftins16-bit increment RegBasr8-bit arith right shiftins16-bit increment RegSPasr8-bit arith right shift to RegBinx16-bit increment RegSPbccbranch if carry cleariny16-bit increment RegYbcllclear bits in memoryjmpjump alwaysbcsbranch if signed ≥lbcslong branch if carry clearbgbranch if signed >lbcslong branch if carry setbglong branch if signed >lbglong branch if signed ≥bhibranch if unsigned >lbglong branch if signed >bhibranch if unsigned ≥lbglong branch if signed > etbl 16-bit look up and interpolation lbgt long branch if signed > lbhi long branch if unsigned > lbhs long branch if unsigned ≥ lble long branch if signed ≤

lblo long branch if unsigned <</pre> lbls long branch if unsigned ≤

lblt long branch if signed <

lbmi long branch if result is negative</pre> cli clear I=0, enable interrupts clr 8-bit Memory clear clra RegA clear clrb RegB clear clv clear overflow bit, V=0 cmpa 8-bit compare RegA with memory com 8-bit logical complement to Memory com 8-bit logical complement to RegA comb 8-bit logical complement to RegA cmb 8-bit logical complement to RegB cmb 8-bit logical compare RegV with memory cpy 16-bit compare RegY with memory dbag decrement and branch if result=0 dbae decrement and branch if result≠0 dbae decrement memory chit decrement memory chit decrement memory chit decrement RegA chit decrement RegA chit decrement RegA chit decrement RegA orab 8-bit logical or to RegB

| pulc<br>puld<br>pulx<br>puly<br>revw<br>rol<br>rola<br>rolb<br>ror<br>rora<br>rorb<br>rtc<br>rti<br>rts<br>sba<br>sbca | Fuzzy logic rule evaluation<br>weighted Fuzzy rule evaluation<br>8-bit roll shift left Memory<br>8-bit roll shift left RegA<br>8-bit roll shift left RegB<br>8-bit roll shift right Memory<br>8-bit roll shift right RegB<br>return sub in expanded memory<br>return from interrupt<br>return from subroutine<br>8-bit subtract RegA-RegB<br>8-bit sub with carry from RegA |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sbca<br>sbcb                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                             |

| sec                                                                                                                    | set carry bit, C=1                                                                                                                                                                                                                                                                                                                                                          |

| sei                                                                                                                    | set I=1, disable interrupts                                                                                                                                                                                                                                                                                                                                                 |

| sev                                                                                                                    | set overflow bit, V=1                                                                                                                                                                                                                                                                                                                                                       |

| sex<br>staa                                                                                                            | sign extend 8-bit to 16-bit reg<br>8-bit store memory from RegA                                                                                                                                                                                                                                                                                                             |

| stab                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                             |

| std                                                                                                                    | 16-bit store memory from RegD                                                                                                                                                                                                                                                                                                                                               |

| sts                                                                                                                    | 16-bit store memory from SP                                                                                                                                                                                                                                                                                                                                                 |

| stx                                                                                                                    | 16-bit store memory from RegX                                                                                                                                                                                                                                                                                                                                               |

```

sty

16-bit store memory from RegY

8-bit sub from RegA

suba

subb 8-bit sub from RegB

subd 16-bit sub from RegD

swi software interrupt, trap

tab transfer A to B

tap transfer A to CC

transfer B to A

tba

tbeq test and branch if result=0

tbl 8-bit look up and interpolation

tbne test and branch if result≠0

tfr transfer register to register

tpa

transfer CC to A

trap illegal instruction interrupt

trap illegal op code, or software trap

tst

8-bit compare memory with zero

tsta 8-bit compare RegA with zero

tstb 8-bit compare RegB with zero

tsx transfer S+1 to X

tsy transfer S+1 to Y

txs

transfer X-1 to S

tys transfer Y-1 to S

wai wait for interrupt

wav weighted Fuzzy logic average

xgdx exchange RegD with RegX

xgdy exchange RegD with RegY

```

INC

## **Increment Memory**

**Operation:** (M) +  $01 \rightarrow M$

| Source Form       | Address Mode | Object Code | HCS12 Access Detail |

|-------------------|--------------|-------------|---------------------|

| INC opr16a        | EXT          | 72 hh 11    | rPwO                |

| INC oprx0_xysp    | IDX          | 62 xb       | rPw                 |

| INC oprx9,xysp    | IDX1         | 62 xb ff    | rPwO                |

| INC oprx16,xysp   | IDX2         | 62 xb ee ff | frPwP               |

| INC [D,xysp]      | [D,IDX]      | 62 xb       | fIfrPw              |

| INC [oprx16,xysp] | [IDX2]       | 62 xb ee ff | fIPrPw              |

| example    | addressing mode | Effective Address              |

|------------|-----------------|--------------------------------|

| ldaa #u    | immediate       | No EA                          |

| ldaa u     | direct          | EA is 8-bit address (0 to 255) |

| ldaa U     | extended        | EA is a 16-bit address         |

| ldaa m,r   | 5-bit index     | EA=r+m (-16 to 15)             |

| ldaa v,+r  | pre-increment   | r=r+v, EA=r (1 to 8)           |

| ldaa v,-r  | pre-decrement   | r=r-v, EA=r (1 to 8)           |

| ldaa v,r+  | post-increment  | EA=r, r=r+v (1 to 8)           |

| ldaa v,r-  | post-decrement  | EA=r, r=r-v (1 to 8)           |

| ldaa A,r   | Reg A offset    | EA=r+A, zero padded            |

| ldaa B,r   | Reg B offset    | EA=r+B, zero padded            |

| ldaa D,r   | Reg D offset    | EA=r+D                         |

| ldaa q,r   | 9-bit index     | EA=r+q (-256 to 255)           |

| ldaa W,r   | 16-bit index    | EA=r+W (-32768 to 65535)       |

| ldaa [D,r] | D indirect      | EA={r+D}                       |

| ldaa [W,r] | indirect        | $EA=\{r+W\}$ (-32768 to 65535) |

| E 1 (010   | 11 · 1 ·        |                                |

Freescale 6812 addressing modes r is X, Y, SP, or PC

| 20 30 40                                                                                                                | 30 . 40                                                           | 8                                               | 89<br>(8)                          | Г                               | 50       |                    |    | 80                | 06                 | dat i<br>ØV      | B0                  | 00                | D0                 | Э                       | F0<br>en             |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|------------------------------------|---------------------------------|----------|--------------------|----|-------------------|--------------------|------------------|---------------------|-------------------|--------------------|-------------------------|----------------------|

| 5b const pre-inc post-inc 5b const 5b const pre-inc post-inc                                                            | post-inc 5b const 5b const pre-inc                                | 5b const 5b const pre-inc                       | 5b const pre-inc                   | pre-inc                         |          | post-              |    | 0, sP<br>5b const | 5b const           |                  |                     | 5b const          | 5b const           | 9b const                | 9b const             |

| 21 31 41 51 61 71                                                                                                       | 31 41 51 61 71                                                    | 41 51 61 71                                     | 51 61 71                           | 61 71                           | 71       | 71                 |    | 81<br>1 en        | 91<br>45 en        | ۲۹ ten           | B1<br>2 cn.         | сі<br>,           | D1                 | E1                      | F1                   |

| -15,X 2,+X 2,X+ 1,Y -15,Y 2,+Y 2,Y+<br>5b const pre-inc post-inc 5b const 5b const pre-inc post-inc                     | post-inc 5b const 5b const pre-inc                                | 5b const 5b const pre-inc                       | 5b const pre-inc                   | Z,+Y<br>pre-inc                 |          | z, Y+<br>post-inc  |    | 5b const          | 5b const           | pre-inc          | 2, SHT<br>post-inc  | 5b const          | 5b const           | 9b const                | 9b const             |

| 22 32 42 52 62 72                                                                                                       | 32 42 52 62 72                                                    | 42 52 62 72                                     | 52 62 72                           | 62 72                           | 72       | 72                 |    | 82                | 92                 | A2<br>2.00       | 82<br>2 cn.         | 3                 | D2                 | E2                      | F2<br>~ en           |

| -14,X 3,+X 3,X+ 2,Y -14,T 3,TT 3,TT 3,TT 55 const pre-inc post-inc post-inc post-inc                                    | post-inc 5b const 5b const pre-inc post                           | 5b const 5b const pre-inc pos                   | 5b const pre-inc pos               | pre-inc pos                     | ğ        | post-inc           |    | 5b const          | 5b const           | pre-inc          | post-inc            | 5b const          | 5b const           | 16b const               | 16b const            |

| 23 33 43 53 63 73                                                                                                       | 33 43 53 63 73                                                    | 43 53 63 73                                     | 53 63 73                           | 63 73                           | 73       |                    | Г  | 83                | 93                 | A3               | B3                  | ឌ                 | D3                 | E3                      | F3                   |

| -13,X 4,+X 4,X+ 3,Y -13,Y 4,+Y 4,Y+<br>5b const pre-inc post-inc 5b const pre-inc post-inc                              | post-inc 5b const 5b const pre-inc post                           | 3,Y -13,Y 4,+Y<br>5b const 5b const pre-inc pos | -13,Y 4,+Y<br>5b const pre-inc pos | -13,Y 4,+Y<br>const pre-inc pos | ă<br>V   | 4,Y+<br>post-inc   |    | 3,SP<br>5b const  | -13,SP<br>5b const | 4,+SP<br>pre-inc | 4,SP+<br>post-inc   | 3, PC<br>5b const | -13,PC<br>5b const | [n,X]<br>16b indr       | [n,SP]<br>16b indr   |

| 24 34 44 54 64 74                                                                                                       | 34 44 54 64 74                                                    | 44 54 64 74                                     | 54 64 74                           | 64 74                           | 74       |                    |    | 84                | 94                 | A4               | B4                  | 5                 | D4                 | E4                      | F4                   |

| -12,X 5,+X 5,X+ 4,Y -12,Y 5,+Y 5,Y+<br>5b const pre-inc post-inc 5b const pre-inc post-inc                              | ( 5,X+ 4,Y -12,Y 5,+Y<br>post-linc 5b const pre-inc               | 4,Y -12,Y 5,+Y<br>5b const 5b const pre-inc     | -12,Y 5,+Y<br>5b const pre-inc     | 5,+Y<br>pre-inc                 |          | 5,Y+<br>post-inc   |    | 4,SP<br>5b const  | -12,SP<br>5b const | 5,+SP<br>pre-inc | 5,SP+<br>post-inc   | 4, PC<br>5b const | -12,PC<br>5b const | A,X<br>A offset         | A offset             |

| 25 35 45 55 65                                                                                                          | 35 45 55 65                                                       | 45 55 65                                        | 55 65                              | . 65                            |          | 75                 |    | 85                | 96                 | A5               | B5                  | 8                 | D5                 | E5                      | F5                   |

| -11,X 6,+X 6,X+ 5,Y -11,Y 6,+Y 6,Y+<br>5b const pre-inc post-inc 5b const 5b const pre-inc post-inc post-inc            | K 6,X+ 5,Y -11,Y 6,+Y<br>post-line 5b const 5b const pre-line pos | 5,Y -11,Y 6,+Y<br>5b const 5b const pre-inc pos | -11,Y 6,+Y<br>Sb const pre-inc pos | -11,Y 6,+Y<br>const pre-inc po: | ă        | 6,Y+<br>post-inc   |    | 5,SP<br>5b const  | -11,SP<br>Sb const | 6,+SP<br>pre-inc | 6,SP+<br>post-inc   | 5, PC<br>5b const | -11,PC<br>Bb const | B,X<br>B offset         | B offset             |

| 26 38 46 56                                                                                                             | 36 46 56 66                                                       | 46 56 66                                        | 99                                 | 99                              |          | 8                  |    | 86                | 96<br>96           | A6               | 8                   | 8                 | D6                 | E6                      | F6                   |

| -10,X 7,+X 7,X+ 6,Y -10,Y 7,+Y 7,Y+<br>3b const pre-inc post-inc 5b const 3b const pre-inc post-inc                     | K 7,X+ 6,Y -10,Y 7,+Y<br>post-inc 5b const 5b const pre-inc pos   | 5b const 5b const pre-inc pos                   | 5b const pre-inc pos               | -10,Y /,+Y<br>const pre-inc pos | 800      | post-inc           |    | 5b const          | Eb const           | 7,+SP<br>pre-inc | post-inc            | 5b const          | 5b const           | D offiset               | D offset             |

| 27 37 47 57 67 77                                                                                                       | 37 47 57 67 77                                                    | 47 57 67 77                                     | 57 67 77                           | 67 77                           | "        |                    |    | 87                | 26                 | A7               | B7                  | C7                | D7                 | E7                      | F7<br>m on t         |

| -9,X 8,+X 8,X+ 7,Y -9,Y 8,+Y 8,Y+<br>5b const pre-inc post-inc 5b const pre-inc post-inc post-inc                       | ( 8,X+ 7,Y -9,Y 8,+Y<br>post-inc 5b const 5b const pre-inc pos    | 5b const pre-inc pos                            | -9,Y 8,+Y<br>5b const pre-inc pos  | 8,+Y<br>pre-inc pos             | 90<br>20 | 8,Y+<br>post-inc   |    | 7,SP<br>5b const  | -9,SP<br>5b const  | 8,+SP<br>pre-inc | 8,SP+<br>post-inc   | 7,PC<br>5b const  | 5b const           | D indirect              | D indirect           |

| 28 38 48                                                                                                                | 28 48 58 68 78                                                    | 48 58 68 78                                     | 58 68 78                           | 68 78<br>50 78                  | ° 78     | 78 。 、             |    | 88<br>een         | 98<br>° e n        | A8<br>e_cp       | B8<br>s c D_        | C8<br>8 DC        | D8<br>BD           | E8<br>,                 | F8<br>PC             |

| 5b const 5b const pre-dec pos                                                                                           | post-dec 5b const 5b const pre-dec                                | 5b const 5b const pre-dec                       | 5b const pre-dec                   | pre-dec                         |          | post-dec           |    | 5b const          | 5b const           | pre-dec          | post-dec            | 5b const          | 5b const           | 9b const                | 9b const             |

| 29 39 49<br>7X 7.X- 9.Y                                                                                                 | 7X 39 49 59 69 79                                                 | 7.X- 49 59 69 79                                | 59 69 79<br>9.Y -7.Y 7Y 79         | 69 79<br>7Y                     | 79<br>77 | -7.5<br>7.Y-       |    | 89<br>9,SP        | 99<br>-7,SP        | A9<br>7SP        | B9<br>7,SP-         | C9<br>9,PC        | D9<br>-7,PC        | Е9<br>-n,Y              | F9<br>-n,PC          |

| post-dec 5b const 5b const pre-dec pos                                                                                  | posi-dec 5b const 5b const pre-dec                                | 5b const 5b const pre-dec                       | 5b const pre-dec                   | pre-dec                         |          | post-dec           |    | 5b const          | 5b const           | pre-dec          | post-dec            | 5b const          | 5b const           | 9b const                | 9b const             |

| 2A 3A 4A 5A 6A 6A - Y 5A 6A 6-Y                                                                                         | 3A 4A 5A 6A 6A 6A                                                 | 6X- 4A 5A 6A 6A<br>6X- 10,Y 5A 6A               | 5A 6A 6A                           | -6,Y 6A                         | 6Y       | 7A<br>6,Y-         |    | 8A<br>10,SP       | 9A<br>6,SP         | AA<br>6,-SP      | BA<br>6,SP-         | CA<br>10,PC       | DA<br>-6,PC        | EA<br>n,Y               | FA<br>n,PC           |

| const pre-dec post-dec 50 const 50 const pre-dec                                                                        | post-dec 50 const 50 const pre-dec                                | Faec 50 const 50 const pre-aec                  | pep-aud 18000 00                   | const pre-dec                   | 080-     | post-dec           | Т  | 15U COURT         | 1500000            | pre-oec          | post-dec            | 20 00USI          | 1500 000           | TDD CONSI               |                      |

| 2B 3B 4B 5B 5B 5F 71,Y 55,Y 75, 77 55,-Y 75, 77 55,-Y 75, 77 55,-Y 75, 77 55,-Y 75, 75, 75, 75, 75, 75, 75, 75, 75, 75, | 5,-X 5,X- 4B 5B 6B 77 7<br>5,-X 5,X- 11,Y -5,Y 6,-Y 7             | 5X- 48 58 68 7                                  | 58 68<br>-5,Y 5,-Y                 | -5.Y 618<br>-5.Y                | 5,-7     | 78<br>5,Y-         |    | 88<br>11,SP       | 9B<br>-5,SP        | AB<br>5,-SP      | 5,SP-               | CB<br>11,PC       | -5,PC              | EB<br>[n,Y]<br>4eh inde | In, PC)              |

| 0 const pre-dec post-dec 30 const 30 const pre-dec                                                                      | post-dec 30 const 30 const pre-dec                                | SFORC 30 COMSI 30 COMSI DIREGRAC                | 20 COTISE pre-dec                  | ocorrist pre-dec                | ,        | post-der           |    | 20 COTISI         | 20 00/181          | pre-aec          | post-dec            | 20 000181         |                    |                         |                      |

| 10 ZC 30 40 90 10 10 10 10 10 10 10 10 10 10 10 10 10                                                                   | 4X 4.X- 12.Y -4.Y 4Y                                              | 4.X- 42.Y 5C 8C 7C                              | 12,Y =4,Y =4,-Y /C                 | -4,Y 6C /C                      | 4,-Y 7C  | ,4,4               |    | 8C<br>12,SP       | ыс<br>†            | AC<br>4,-SP      | 4,SP-               | 12, PC            | -4,PC              | ۲,<br>۲,                | APC<br>2             |

| t pre-dec post-dec 5b const 5b const pre-dec poi                                                                        | post-dec 5b const 5b const pre-dec                                | 5b const 5b const pre-dec                       | const 5b const pre-dec             | pre-dec                         |          | post-dec           |    | 5b const          | 5b const           | pre-dec          | post-dec            | Sb const          | 5b const           | A offset                | A offset             |

| 20 3D 4D 5D 6D 7D                                                                                                       | 3D 4D 5D 6D 7D                                                    | 4D 5D 6D 7D                                     | 50 60 70                           | C2 C8                           | 5        | 5<br>2             |    | 08<br>00 07       | 06 U               | uu u             | BD<br>, cn          | 00 00             | 00                 | ~°<br>Ш                 | E<br>2.22            |

| -3,X 3,-X 3,X- 13,Y -3,Y 3,Y 3,Y 3,Y                                                                                    | Dost-dec 5b const 5b const pre-dec                                | 5b const 5b const pre-dec                       | 5b const pre-dec                   | 3,-Y<br>Dre-dec                 |          | 3, Y-<br>post-dec  |    | 50 const          | 5b const           | u-ur<br>pre-dec  | o, ser-<br>post-dec | 3b const          | 5b const           | Boffset                 | Boffset              |

| 2E 3E 4E 5E 6E                                                                                                          | 3E 4E 5E 6E                                                       | 4E 5E 6E                                        | 5E 6E                              | 96                              | ſ        | 7E                 | Г  | 8E                | 9E                 | AE               | BE                  | ы                 | DE                 | Ш                       | E.                   |

| -2,X 2,-X 2,X- 14,Y -2,Y 2,-Y 2,Y-<br>5b const bee-dec post-dec 5b const 5b const bre-dec post-dec post-dec             | C 2,X- 14,Y -2,Y 2,-Y<br>post-dec 5b const 5b const pre-dec       | 14,Y -2,Y 2,-Y<br>5b const 5b const pre-dec     | -2,Y 2,-Y<br>5b const pre-dec      | 2,-Y<br>Dre-dec                 |          | 2, Y -<br>post-dec |    | 14,SP<br>5b const | -2,SP<br>5b const  | 2,-SP<br>Dre-dec | 2,SP-<br>post-dec   | 14,PC<br>5b const | -2,PC<br>5b const  | Doffset                 | D offset             |

| 2F 3F 4F 5F 6F                                                                                                          | 3F 4F 5F 6F                                                       | 4F 5F 6F                                        | 5F 6F                              | 6F                              |          | 7F                 | Г  | 8F                | 9F                 | AF               | Γ                   | ц.                | DF                 | EF                      | LL<br>LL             |

| 1,-X                                                                                                                    | 1,X- 15,Y -1,Y 1,-Y<br>most day 6th const file const mandar       | 15,Y -1,Y 1,-Y<br>Showet Showet median          | -1,Y 1,-Y<br>Shoonet median        | 1,-Y<br>Managara                |          | 1,Y-               |    | 15,SP<br>5h minet | -1,SP<br>Shoonet   | 1,-SP<br>meder   | 1,SP-<br>not-der    | 15,PC             | -1,PC<br>5b const  | [D,Y]<br>D indirect     | [D,PC]<br>D indirect |

| Annaud warman warman warmand annaud                                                                                     | non-aid veillan an teillan an ann-tend                            |                                                 |                                    | Anna Aud                        |          | man mound          | ٦. |                   |                    | nnn nud          | T                   |                   |                    |                         |                      |

(5) Question 1. What is the 8-bit hexadecimal representation (\$00 to \$FF) for decimal value -90?

- (5) Question 2. What will be the value of the carry (C) bit after executing the following?

- ldab #50

- subb #210

(5) Question 3. What will be the value of the overflow (V) bit after executing the following?

ldaa #50

adda #-60

(5) Question 4. A software variable can take on the following specific values -5.0, -4.9, -4.8, ..., 4.8, 4.9, 5.0. Which fixed-point format should be used for this variable? If more than one format could be used to solve the problem, choose the most space-efficient format. Enter the correct letter A-H.

**A**) 8-bit signed fixed-point,  $\Delta = 0.1$

- **E**) 16-bit signed fixed-point,  $\Delta = 0.1$

- **B**) 16-bit signed fixed-point,  $\Delta = 0.01$

- **F**) 8-bit unsigned fixed-point,  $\Delta = 0.1$ **G**) 32-bit floating point

- C) 8-bit signed fixed-point,  $\Delta = 0.01$ D) 16-bit unsigned fixed-point,  $\Delta = 0.001$

- **H**) fixed-point is not needed

(5) Question 5. Rewrite the following equation using fixed-point math, assuming X,Y,Z are integers. Basically, your equation should perform this operation using integer add, subtract, multiply and divide, minimizing the error caused by dropout. Don't worry about overflow.

Z = 0.123 \* X - 0.66 \* Y + 0.5

(5) Question 6. Show the machine code generated by the instruction

inc 1,y+

(5) Question 7. You are asked to measure a parameter to  $3\frac{1}{2}$  decimal digits. What is the approximate precision in binary bits?

(5) **Question 8.** Assume the SP has been properly initialized. What will be the contents of RegA and RegX after the following six instructions are executed? Hint: draw stack pictures.

| ldaa | <b>#\$12</b> |

|------|--------------|

| ldx  | #\$3456      |

| pshx |              |

| psha |              |

| pulx |              |

| pula |              |

(10) Question 9. Assume RegX is \$3800, RegY is \$3810, the PC is \$4123, and Ram locations \$3800 to \$38FF are initially \$00, 01,...FF respectively. E.g., location \$3856 contains \$56. Show the simplified bus cycles occurring when the **inc** 10,**x** instruction is executed. In the "changes" column, specify which registers get modified during that cycle, and the corresponding new values. Do not worry about changes to the CCR. Just show the one instruction.

## \$4123 620A inc 10,x

**Question 10.** Write a **main** program and a subroutine **Check** that inputs from Port T bit 6 and outputs to Port T bit 5. The software system will continuously check the status of the input signal, setting the output high if the input ever becomes high. The system never sets the output low. Full credit will be given to the code that is friendly.

(25) Part a) Write the assembly language **main** program that first initializes the stack. Next it should make Port T bit 6 an input and Port T bit 5 an output. The body of the **main** program should call the part b) subroutine, **Check**, over and over without stopping.

(25) Part b) Write the assembly language subroutine called **Check**, which first reads Port T bit 6. If Port T bit 6 is 1, then set Port T bit 5 equal to 1. If Port T bit 6 is 0, then Port T bit 5 is not changed.