\_\_\_\_\_ Middle Initial: \_\_\_\_\_ Last:\_\_ First: This is a closed book exam. You must put your answers on this piece of paper only. You have 50 minutes, so allocate your time accordingly. Please read the entire quiz before starting. (5) Question 1. (5) Question 2. (5) Question 3. (5) Question 4. (5) Question 5. (5) Question 6. (5) Question 7. (5) Question 8. (5) Question 9. (10) **Question 10.** Pulse bset PTT,#1 ; send pulse on PT0 bclr PTT,#1 rts

| (15) Question 11. | Convert |                    |

|-------------------|---------|--------------------|

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

|                   |         |                    |

| (5) Question 12.  |         |                    |

|                   | calc    | ;short calc(void){ |

| (15) Question 13. |         |                    |

|                   |         | ;short sum,n;      |

|                   |         |                    |

|                   |         |                    |

|                   |         | ;n = 100;          |

|                   |         | <u>_</u>           |

|                   |         | ;sum = 0;          |

|                   |         |                    |

|                   |         | ;do{ sum = sum+n;  |

|                   |         |                    |

|                   |         |                    |

;} while(--n);

;return(sum);}

This Fifo queue can hold up to eight 8-bit data values, and the Address Contents picture shows it currently is holding three values (shaded).

(5) **Ouestion 1.** What value is returned if we were to call Fifo Get at this point?

(5) Question 2. Next, assume we call Fifo\_Put. What will be the new PutPt after we call Fifo Put?

| •                        | volve the following assembly program \$3907 \$66   |

|--------------------------|----------------------------------------------------|

| involving a stack frame. |                                                    |

| main lds #\$4000         |                                                    |

| ldaa #100                |                                                    |

| psha                     | ; pass 8-bit <b>in</b> parameter on stack          |

| jsr sub2                 |                                                    |

| leas 1,s                 | ; balance stack                                    |

| here bra here            |                                                    |

| data set xxx             | ; binding of 8-bit local variable                  |

| <b>in</b> set <b>yyy</b> | ; binding of 8-bit input parameter                 |

| sub2 pshx                | ; save register X                                  |

| des                      | ; allocate 8-bit local variable called <b>data</b> |

| tsx                      | ; RegX stack frame                                 |

| ;****body of the         | subroutine                                         |

| ldab <b>in,</b> x        | ; get a copy of <b>in</b> parameter                |

| stab <b>data,</b> x      | ; store into local variable <b>data</b>            |

| ;****end of body         |                                                    |

| ins                      | ; deallocate <b>data</b>                           |

| pulx                     | ; restore register X                               |

| rts                      | ; return                                           |

|                          |                                                    |

(5) Question 3. What value should you use in the **xxx** position to implement the binding of the local variable, **data**?

(5) Question 4. What value should you use in the yyy position to implement the binding of the parameter, **in**?

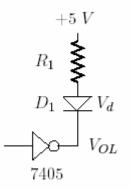

(5) Question 5. Specify the resistor value for  $R_1$ , assuming LED current  $I_d$  is 1 mA, the LED voltage  $V_d$  is 2.5 V, and the gate output voltage  $V_{OL}$  is 0.5 V.

(5) Question 6. Which three events cause an interrupt to occur? Specify three letters in any order.

A) The software disarms the interrupt (e.g., RTIE=0)

B) The I bit in the CCR is set

C) The I bit in the CCR is clear

D) The software arms the interrupt (e.g., RTIE=1)

E) The software acknowledges the interrupt, clearing the flag (e.g., RTIF=0)

F) The software sets the flag bit (e.g., RTIF=1)

G) The hardware sets the flag bit (e.g., RTIF=1)

H) The hardware acknowledges the interrupt, clearing the flag (e.g., RTIF=0)

\$12

\$56

\$78

\$34

- GetPt

- PutPt

\$3904

\$3905 \$3906 (5) Question 7. Consider a 10-bit ADC with a range of -10 to +10V. What is the approximate resolution of this ADC? Give units.

(5) **Question 8.** The 0 to 5V 10-bit ADC on the 9S12C32 uses the successive approximation conversion technique. This technique involves a series of guesses. Which will be the first guess?

A) 0 V B) 5V/1024 = 5mV C) 5V/256 = 20mV D) 1.25 V E) 2.5 V F) 3.75 V G) 5 V

```

sei

rti

org $FFF0

```

```

fdb RTIhandler

```

A) Register A is altered by the ISR, so the main program will be confused.

B) The sei instruction disables interrupts, so no more interrupts will occur

C) This ISR did not acknowledge the interrupt (clear RTIF), so it will interrupt over and over continuously.

D) This ISR did not acknowledge the interrupt (clear RTIF) so no more interrupts will occur.

E) The stack is unbalanced, so it will crash.

F) The ISR didn't need to set the I bit with the **sei**, because the **rti** instruction will automatically set the I bit when the handler returns.

(15) Question 10. A complicated software system includes this subroutine

Pulse bset PTT,#1 ; send pulse on PT0 bclr PTT,#1 rts

Design a minimally intrusive debugging instrument that will allow you to measure how many times this subroutine has been called. You may assume that this subroutine is called less than 1000 times. Include global variable definitions, an initialization subroutine and the instrument added to **Pulse** that counts. No comments required for this question.

(15) Question 11. Write a subroutine that converts a 10-bit ADC sample into a position. The input parameter is passed call by reference in Reg Y, meaning Reg Y contains a pointer to the input 16-bit input data. The output parameter should be returned by value in RegD, meaning Reg D itself contains the result. The conversion is a linear function (Output = 2.5\*Input+100). The range of input values is 0 to 1023. The output range is 100 to 2556. The following main program illustrates how data is passed into and out of your subroutine. *Comments are required*.

|                                                                                   | org  | \$3800   |       |         |        |      | 2.5*65536=163840          |

|-----------------------------------------------------------------------------------|------|----------|-------|---------|--------|------|---------------------------|

| Result                                                                            | rmb  | 2        |       |         |        |      | 2.5/65536 = 0.00003814697 |

|                                                                                   | org  | \$4000   |       |         |        |      | 65536/2.5=26214           |

| Data                                                                              | fdb  | 1000     |       |         |        |      | 3.5*65536=229376          |

| main                                                                              | lds  | #\$4000  |       |         |        |      | 3.5/65536=0.00005340576   |

|                                                                                   | ldy  | #Data    | ; Reg | Y point | ts to  | data | 65536/3.5=18725           |

|                                                                                   | jsr  | Convert  | ; you | r subro | outine | e    |                           |

|                                                                                   | std  | Result   | ; sav | e resu  | lt     |      |                           |

| The following table shows some example data. (don't worry about rounding the LSB) |      |          |       |         |        |      |                           |

| Input                                                                             | 2.5* | Input Ou | tput  | Meaniı  | ng     |      |                           |

| 0                                                                                 |      | 0        | 100   | 1.00    | cm     |      |                           |

| 100                                                                               | 25   | 0        | 350   | 3.50    | cm     |      |                           |

| 1000                                                                              | 250  | 0 2      | 600   | 26.00   | cm     |      |                           |

1022 26.55 cm 2555 2655 (hint: you can solve this problem one of two ways. First, you could use the fdiv instruction. Second, you could rewrite the formula as Output = 2\*Input + Input/2 + 100.

(5) Question 12. A serial port will be used to transfer 2000 bytes of information per second. The protocol is 1 start bit, 8 data bits, and 2 stop bits. What is the slowest baud rate that can handle this serial transfer?

(20) Question 13. Translate explicitly (line by line) the following C program to assembly. Both variables (**n** sum) must be stored on the stack, including symbolic binding. For each line of C, fetch necessary values off the stack, operate, and store back to the stack as appropriate. For example, **sum** = **sum+n**; should be implemented as read **sum** from stack, read **n** from stack, add, write result back to stack. The output parameter should be returned by value in Reg D. No additional comments required for this question.

```

short calc(void){

short sum,n; // two 16-bit signed variables

n = 100;

sum = 0;

do\{ sum = sum+n;

} while(--n); // means decrement and branch back if not zero

return(sum); } // return a 16-bit result in Reg D

```

ble branch if signed ≤ blo branch if unsigned < bls branch if unsigned ≤

blo

blanch if unsigned ≤

lbdq

long branch if result is

bls

branch if unsigned ≤

lbge

long branch if signed ≥

blt

branch if signed <</td>

lbgt

long branch if signed ≥

bmi

branch if result is negative (N=1)

lbhi

long branch if unsigned >

bne

branch if result is nonzero (Z=0)

lbhs

long branch if unsigned ≥

bpl

branch always

lblo

long branch if unsigned ≤

dbeq Y,loop dbeq Y,loopmovb #100,PTTdbnedecrement and branch if result≠0movw16-bit move memory to memory dbne A,loop dec 8-bit decrement memory deca 8-bit decrement RegA decb 8-bit decrement RegB des 16-bit decrement RegSP dex 16-bit decrement RegX dey 16-bit decrement ReqY

aba 8-bit add RegA=RegA+RegB abx unsigned add RegY=RegX+RegB aby unsigned add RegY=RegX+RegB adca 8-bit add with carry to RegA adca 8-bit add with carry to RegA adca 8-bit add with carry to RegB adca 8-bit add with carry to RegB adca 8-bit add to RegA adda 8-bit add to RegD addb 8-bit add to RegD addb 8-bit logical and to RegA andcc 8-bit logical and to RegA andcc 8-bit logical and to RegB asla/lsl 8-bit left shift RegD asla/lsl 8-bit left shift RegD asr 8-bit arith right shift to RegB asl/lsl 8-bit arith right shift RegB asla/lsl 16-bit left shift RegD are 8-bit arith right shift to RegB asl/lsl 8-bit arith right shift to RegB asla/lsl 6-bit arith right shift to RegB asr 8-bit arith right shift to RegB bcc branch if carry clear bclr bit clear in memory bclr bit clear in memory bclr bit clear in memory bclr bit signed ≥ bdt branch if signed ≥ bdt branch if signed ≥ bdt branch if signed ≤ bdt branch if nusigned ≤ bdt 8-bit and with RegA, sets CCR bls branch if unsigned ≤ blt 8-bit and with RegS, sets CCR bls branch if unsigned ≤ blt 8-bit and with RegS, sets CCR bls branch if unsigned ≤ blt 8-bit and with RegS, sets CCR bls branch if unsigned ≤ blt 8-bit and with RegS, sets CCR bls branch if unsigned ≤ blt branch if ingiged ≤ blt branch if ingiged ≤ blt branch if unsigned ≤ blt branch if signed ≤ blt branch if unsigned ≤ blt branch if signed ≤ blt bra DotDranch if result is positive (N=0)DisDing branch if signed ≤brabranch if bits are clearlbllong branch if unsigned ≤brclr PTT,#\$01,looplbllong branch if unsigned ≤branch neverlbllong branch if result is negativebranch if bits are setlbllong branch if result is nozerobrset branch if outringlbllong branch if result is nozerobst PTT,#\$01,looplbllong branch if result is nozerobst PTT,#\$01,looplbllong branch if result is nozerobst pranch if overflow clearlbrlong branch if overflow clearbvs branch if overflow setlda8-bit load memory into RegAcla8-bit compare RegA with RegBldd16-bit load memory into RegDclic clear carry bit, C=0lds16-bit load memory into RegSPclir RegA clearleas16-bit load effective addr to SPclr RegA clearleas16-bit load effective addr to SPclr RegB clearlsr 8-bit logical right shift RegAcom 8-bit logical complement to RegAlsr 8-bit logical right shift RegAcom 8-bit logical complement to RegAlsr 8-bit logical right shift RegDcom 8-bit logical complement to RegAlsr 8-bit unsigned maximum in RegAcom 8-bit logical complement to RegAlsr 16-bit unsigned maximum in RegAcom 8-bit logical complement to RegBmaxa 8-bit unsigned maximum in RegAcom 8-bit logical complement to RegBmaxa 8-bit unsigned maximum in RegAcom 8-bit logical complement to RegBmaxa 8-bit unsigned maximum i movb #100,PTT movw #13,SCIBD mul RegD=RegA\*RegB neg 8-bit 2's complement negate memor nega 8-bit 2's complement negate RegA negb 8-bit 2's complement negate RegB oraa 8-bit logical or to RegA 8-bit 2's complement negate memory oraa 8-bit logical or to RegA orab 8-bit logical or to RegB 8-bit logical or to RegA

| orcc<br>psha<br>pshb<br>pshc<br>pshd<br>pshy<br>pula<br>pulb<br>pulc<br>puld<br>pulx<br>puly<br>rev<br>revw<br>rol<br>rola<br>rolb<br>ror<br>rora<br>rorb<br>rtc<br>rti<br>rts | 8-bit logical or to RegCC<br>push 8-bit RegA onto stack<br>push 8-bit RegB onto stack<br>push 8-bit RegC onto stack<br>push 16-bit RegD onto stack<br>push 16-bit RegY onto stack<br>push 16-bit RegY onto stack<br>pop 8 bits off stack into RegA<br>pop 8 bits off stack into RegB<br>pop 8 bits off stack into RegCC<br>pop 16 bits off stack into RegY<br>pop 16 bits off stack into RegY<br>Fuzzy logic rule evaluation<br>%-bit roll shift left Memory<br>8-bit roll shift left RegB<br>8-bit roll shift left RegB<br>8-bit roll shift right RegA<br>8-bit roll shift right RegB<br>return sub in expanded memory<br>return from subroutine |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sba<br>sbca                                                                                                                                                                    | 8-bit subtract RegA-RegB<br>8-bit sub with carry from RegA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| sbcb                                                                                                                                                                           | 8-bit sub with carry from RegB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| sec                                                                                                                                                                            | set carry bit, C=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| sei                                                                                                                                                                            | set I=1, disable interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| sev                                                                                                                                                                            | set overflow bit, V=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| sex                                                                                                                                                                            | sign extend 8-bit to 16-bit reg sex B,D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| staa                                                                                                                                                                           | 8-bit store memory from RegA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| stab<br>std |                                                    |

|-------------|----------------------------------------------------|

| sts         | 16-bit store memory from SP                        |

| stx         | 16-bit store memory from ReqX                      |

| sty         | 16-bit store memory from RegY                      |

| suba        | 8-bit sub from RegA                                |

| subb        | 8-bit sub from RegB                                |

| subd        | 16-bit sub from RegD                               |

| swi         | software interrupt, trap                           |

| tab         | transfer A to B                                    |

| tap         | transfer A to CC                                   |

| tba         | transfer B to A                                    |

| tbeq        | test and branch if result=0                        |

|             | tbeq Y,loop                                        |

| tbl         | 8-bit look up and interpolation                    |

| tbne        | test and branch if result≠0                        |

|             | tbne A,loop                                        |

| tfr         | transfer register to register                      |

|             | tfr X,Y                                            |

| tpa         | transfer CC to A                                   |

| trap        | illegal instruction interrupt                      |

| trap        | illegal op code, or software trap                  |

| tst         | 8-bit compare memory with zero                     |

| tsta        | 1 5                                                |

| tstb        | 1 2                                                |

| tsx         | transfer S to X                                    |

| tsy         | transfer S to Y                                    |

| txs         |                                                    |

| tys         | transfer Y to S                                    |

| wai         | wait for interrupt                                 |

|             | weighted Fuzzy logic average                       |

| wadw        |                                                    |

|             | exchange RegD with RegX<br>exchange RegD with RegY |

| example    | addressing mode | Effective Address              |

|------------|-----------------|--------------------------------|

| ldaa #u    | immediate       | none                           |

| ldaa u     | direct          | EA is 8-bit address (0 to 255) |

| ldaa U     | extended        | EA is a 16-bit address         |

| ldaa m,r   | 5-bit index     | EA=r+m (-16 to 15)             |

| ldaa v,+r  | pre-increment   | r=r+v, EA=r (1 to 8)           |

| ldaa v,-r  | pre-decrement   | r=r-v, EA=r (1 to 8)           |

| ldaa v,r+  | post-increment  | EA=r, r=r+v (1 to 8)           |

| ldaa v,r-  | post-decrement  | EA=r, r=r-v (1 to 8)           |

| ldaa A,r   | Reg A offset    | EA=r+A, zero padded            |

| ldaa B,r   | Reg B offset    | EA=r+B, zero padded            |

| ldaa D,r   | Reg D offset    | EA=r+D                         |

| ldaa q,r   | 9-bit index     | EA=r+q (-256 to 255)           |

| ldaa W,r   | 16-bit index    | EA=r+W (-32768 to 65535)       |

| ldaa [D,r] | D indirect      | EA={r+D}                       |

| ldaa [W,r] | indirect        | $EA=\{r+W\}$ (-32768 to 65535) |

## Freescale 6812 addressing modes

| Pseudo op |       | n     | meaning |                                                                 |  |  |  |  |

|-----------|-------|-------|---------|-----------------------------------------------------------------|--|--|--|--|

| org       |       |       |         | Specific absolute address to put subsequent object code         |  |  |  |  |

| =         | = equ |       |         | Define a constant symbol                                        |  |  |  |  |

| set       |       |       |         | Define or redefine a constant symbol                            |  |  |  |  |

| dc.b      | db    | fcb   | .byte   | Allocate byte(s) of storage with initialized values             |  |  |  |  |

| fcc       |       |       |         | Create an ASCII string (no termination character)               |  |  |  |  |

| dc.w      | dw    | fdb   | .word   | Allocate word(s) of storage with initialized values             |  |  |  |  |

| dc.l      | dl    |       | .long   | Allocate 32-bit long word(s) of storage with initialized values |  |  |  |  |

| ds        | ds.   | b rmb | .blkb   | Allocate bytes of storage without initialization                |  |  |  |  |

| ds.w      |       |       | .blkw   | Allocate bytes of storage without initialization                |  |  |  |  |

| ds.l      |       |       | .blkl   | Allocate 32-bit words of storage without initialization         |  |  |  |  |

|           |       |       |         |                                                                 |  |  |  |  |

FDIV

## FDIV

## Fractional Divide

Operation:

$(D) + (X) \Rightarrow X; Remainder \Rightarrow D$

Description: Divides an unsigned 16-bit numerator in double accumulator D by an unsigned 16-bit denominator in index register X, producing an unsigned 16-bit quotient in X and an unsigned 16-bit remainder in D. If both the numerator and the denominator are assumed to have radix points in the same positions, the radix point of the quotient is to the left of bit 15. The numerator must be less than the denominator. In the case of overflow (denominator is less than or equal to the numerator) or division by zero, the quotient is set to \$FFFF, and the remainder is indeterminate.

FDIV is equivalent to multiplying the numerator by 2<sup>16</sup> and then performing 32 by 16-bit integer division. The result is interpreted as a binary-weighted fraction, which resulted from the division of a 16-bit integer by a larger 16-bit integer. A result of \$0001 corresponds to 0.000015, and \$FFFF corresponds to 0.9998. The remainder of an IDIV instruction can be resolved into a binary-weighted fraction by an FDIV instruction. The remainder of an FDIV instruction can be resolved into the next 16 bits of binary-weighted fraction by another FDIV instruction.

| CCR Details: | s |   |   |   | Ν | - | • | С |  |

|--------------|---|---|---|---|---|---|---|---|--|

| CCR Details. | - | - | - | - | - | Δ | Δ | Δ |  |

- Z: Set if quotient is \$0000; cleared otherwise

- V: 1 if X ≤ D Set if the denominator was less than or equal to the numerator; cleared otherwise

- C: X15 X14 X13 X12 •... X3 X2 X1 X0 Set if denominator was \$0000; cleared otherwise