## **Final Exam Solutions**

**Date:** December 19, 2018

Printed Name: \_

Last,

First

Your signature is your promise that you have not cheated and will not cheat on this exam, nor will you help others to cheat on this exam. <u>You will not reveal the contents of this exam to others who are taking the makeup thereby giving them an undue advantage</u>:

Signature:

## **Instructions:**

- Write your UT EID on all pages (at the top) and circle your instructor's name at the bottom.

- Closed book and closed notes. No books, no papers, no data sheets (other than the last four pages of this Exam)

- No devices other than pencil, pen, eraser (no calculators, no electronic devices), please turn cell phones off.

- Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space (boxes) provided. *Anything outside the boxes will be ignored in grading*.

- You have 180 minutes, so allocate your time accordingly.

- For all questions, unless otherwise stated, find the most efficient (time, resources) solution.

- Unless otherwise stated, make all I/O accesses friendly.

- Please read the entire exam before starting. See supplement pages for Device I/O registers.

| Problem 1  | 10  |  |

|------------|-----|--|

| Problem 2  | 5   |  |

| Problem 3  | 10  |  |

| Problem 4  | 5   |  |

| Problem 5  | 15  |  |

| Problem 6  | 10  |  |

| Problem 7  | 5   |  |

| Problem 8  | 10  |  |

| Problem 9  | 10  |  |

| Problem 10 | 20  |  |

| Total      | 100 |  |

(10) Problem 1. Give a one to three word answer for each question.

| (1) Part a) What data structure do you use to stream data from an ISR to the main program given the situation where data arrives into the ISR bursts but is processed one byte at a time in the main?                                                                                                                   | FIFO                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| (1) Part b) With UART transmission we send one start bit, 8 data bits and one stop bit. What term do we use to define these 10 bits?                                                                                                                                                                                    | Frame                 |

| (1) Part c) What qualifier do we add to an otherwise local variable (scope within a function) so that the variable is defined in permanently in RAM?                                                                                                                                                                    | <mark>static</mark>   |

| (1) Part d) What qualifier do we add to an otherwise global variable so that the scope is restricted to software located within that same file?                                                                                                                                                                         | static                |

| (1) Part e) What graphical structure describes the modularity of a system, such that circles and rectangles are modules and arrows represent information passes from one module to another?                                                                                                                             | Data flow<br>graph    |

| (1) Part f) What term is used to describe the smallest difference in input voltage that an ADC can reliably distinguish?                                                                                                                                                                                                | Resolution            |

| (1) Part g) What are the units of electrical power? Give as a one-word answer, and not as a combination of other units.                                                                                                                                                                                                 | watts                 |

| (1) Part h) In a real-time system, it is important to respond to critical events. What is the term used to describe the delay between the time a critical event occurs and the time the event is processed? For example, the time between touching a switch and the time the software recognizes the switch is touched. | Latency               |

| (1) Part i) A number system where the value 4.125 is represented with the integer 264?                                                                                                                                                                                                                                  | Binary fixed<br>point |

| (1) Part j) What is the debugging term used to store important information into arrays? This debugging technique can be used to replace printing (printf) information while the program is running                                                                                                                      | Dump                  |

(5) Problem 2. Consider the sampling rate chosen for the ADC in Lab 8. Give the relationship for the slowest possible sampling rate ( $f_s$ , in Hz), given these parameters: ADC range (V, in volts), number of ADC bits (n, in bits, e.g., 12 bits) and rate at which one moves the slide pot (r, in oscillations per sec).

| Nyquist f <sub>s</sub> > 2r |  |  |  |

|-----------------------------|--|--|--|

|                             |  |  |  |

|                             |  |  |  |

|                             |  |  |  |

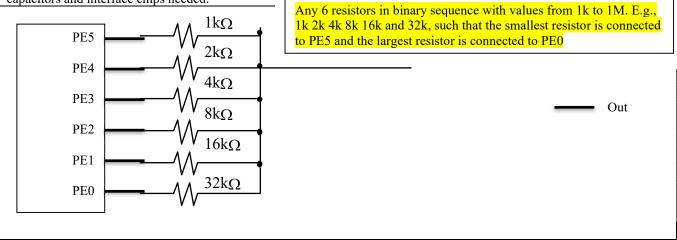

(10) Problem 3: Design a 6-bit DAC connected to Port E using PE5 to PE0. Show the circuit and label all resistors, capacitors and interface chips needed.

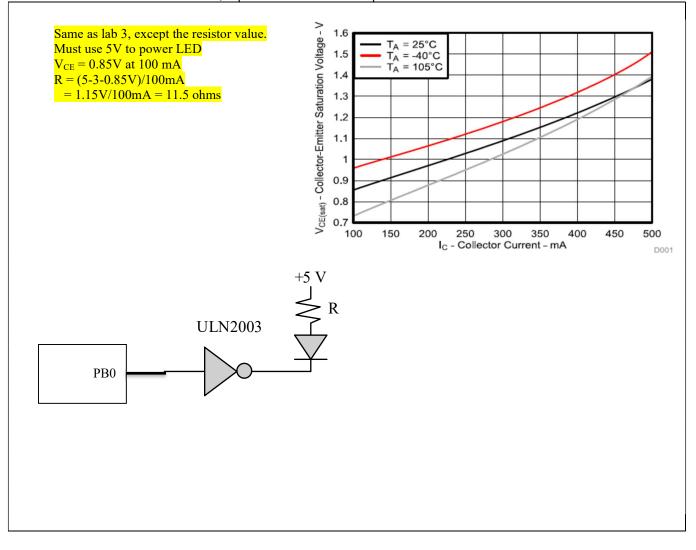

(5) Problem 4. Interface an LED to Port B bit 0 using positive logic. The desired operating point of the LED is 3V and 100 mA. Assume the ULN2003B has an output voltage that depends on the collector current according to this graph at 25 C. Show the circuit and label all resistors, capacitors and interface chips needed.

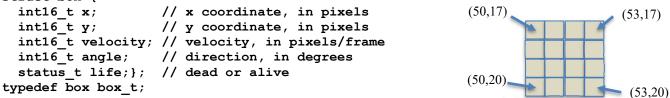

(15) Problem 5. Consider a game that has up to 50 boxes. There is an array specifying the current status of each box. Each box is 4 by 4 pixels, and has an (x,y) coordinate, a velocity, a direction, and a life parameter. You may assume the Box array has been populated with data. The figure on the right shows one example box at (x,y)=(50,20)

```

typedef enum {dead,alive} status_t;

struct box {

```

Each box has 16 pixels in the game world, occupying the square space from (x,y) to (x+3, y-3). Write a C function that searches to see if two alive boxes are overlapping (the location of any of the 16 pixels of one box is equal to any of the 16 pixels of another box). If two boxes are occupying the same space, set the life parameter of both boxes to 0. Do not worry about 3 or more boxes occupying the same space.

```

void Search(box t box[]) { // 50 elements

int i,j;

int16 t dx; // x distance between boxes

int16_t dy; // y distance between boxed

for(i=0;i<49;i++) {</pre>

if((box[i].life == alive){

for(j=i+1;j<50;j++) {</pre>

if(box[j].life == alive) {

dx = box[i].x - box[j].x;

dy = box[i].y - box[j].y; // calculate distances

if((dx>-4)\&\&(dx<+4)\&\&(dy>-4)\&\&(dy<+4))

box[i].life = dead;

box[j].life = dead;

۲

۲

۲

}

```

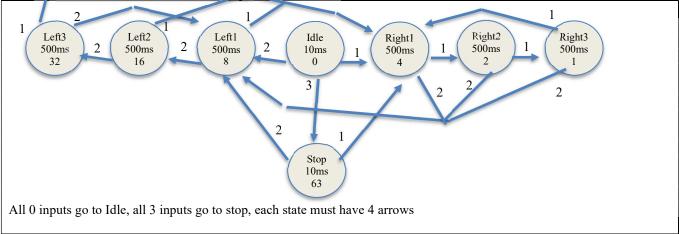

(10) Problem 6. Draw the state transition graph for a Moore FSM used to control 6 tail lights on a car. There are two inputs and 6 outputs. If the input is 0 the output is 0. If the input is 1 (turn right), the output cycles through the values 4 2 1 every ½ second. If the input is 2 (turn left), the output cycles through the values 8,16,32 every ½ second. If the input is 3 (brake) the output is 63. Each state has a name, output, dwell time, and multiple arrows to next states.

(5) Problem 7. Assume the UART0 has been initialized. Use busy-wait synchronization to implement a C function with the following steps

- 1) Wait for new serial port input

- 2) Read the new 8-bit ASCII character data

- 3) Echo the data by transmitting the same 8-bit data just received

- 4) Return by value the one character received.

Show what you would place in the .h file

```

//-----UART_InCharEcho------

// Wait for new serial port input

// Echo received data to transmitter

// Input: none

// Output: ASCII code for character just received

char UART InCharEcho(void);

```

```

Show what you would place in the .c file

```

```

char UART_InCharEcho(void) { char data;

while((UART0_FR_R&0x00000010) != 0); // UART Receive FIFO Empty

data = UART0_DR_R;

while((UART0_FR_R&0x00000020) != 0); // UART Transmit FIFO Full (optional)

UART0_DR_R = data;

return data;

}

```

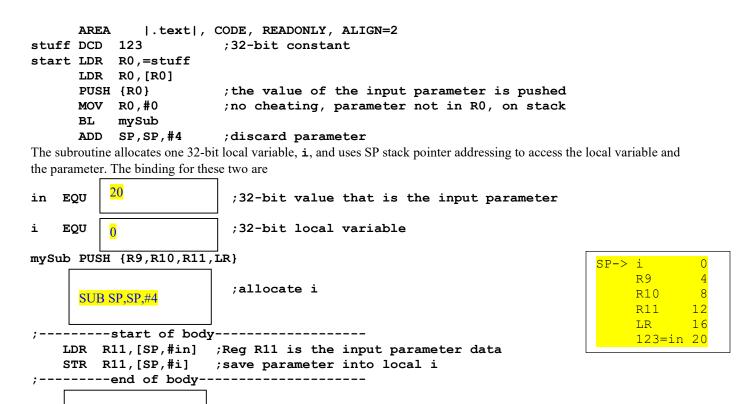

(10) Question 8. The subroutine mySub uses a call by value parameter passed on the stack. There are no return parameters. Call by value means the data itself is pushed on the stack. This is not AAPCS compliant. A typical calling sequence is

```

POP {R9,R10,R11,PC}

```

ADD SP,SP,#4

In the boxes provided, show the binding for in, the binding for the local variable i, the assembly instruction(s) to allocate i, and the assembly instructions to deallocate i.

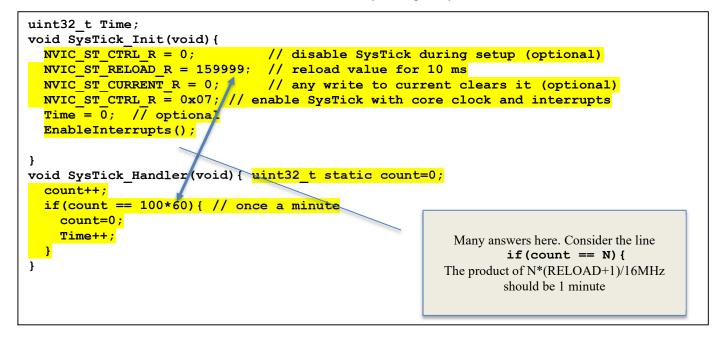

(10) Question 9: Write C code to maintain the elapsed time in minutes. I.e., increment the global variable **Time** once a minute. Include both the initialization and the ISR. Do not worry about priority. Assume bus clock is 16 MHz.

;deallocate i

(20) Question 10: You are asked to implement a simple postfix calculator as a subroutine in assembly language. The input (call by reference in R0) to your function is a null-terminated character string with the following 12 valid characters 0,1,2,3,4,5,6,7,8,9,+,and\*. You may assume all strings are valid and calculate exactly one 32-bit output value. For example

| "5"                        | returns 5                                                                   |

|----------------------------|-----------------------------------------------------------------------------|

| "79+"                      | returns $7+9 = 16$                                                          |

| "58*1+"                    | returns $(5*8)+1 = 41$                                                      |

| "92*7+4*52+*"              | returns $(((9*2)+7)*4)*(5+2)) = ((18+7)*4)*7) = ((25*4)*7) = (100*7) = 700$ |

| The basic idea is to fetch | a character from the string.                                                |

The basic idea is to fetch a character from the string:

- if it is a + or \* operator, pop two numbers from the stack, unsigned 32-bit operate, and push the result

- if it is a digit, convert ASCII to value, push the value (0 to 9) of the digit as a 32-bit value onto the stack

- if it is the null termination, pop one 32-bit value from the stack and return that value in R0

|                                                                                                                                                                                                                                                   | LDRB R1, [R0] ; characters are one byte; could have used signed LDRSB<br>ADD R0,R0,#1 ; next<br>CMP R1,#0<br>BEQ done<br>CMP R1,#'+'<br>BNE nPls<br>plus POP {R2,R3}<br>ADD R2,R3 ; add top two elements<br>PUSH {R2}<br>B Calc<br>nPls CMP R1,#'*'<br>BNE nMul<br>mult POP {R2,R3}<br>MUL R2,R3 ; multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0} | LDRB R1, [R0] ; characters are one byte; could have used signed LDRSB<br>ADD R0,R0,#1 ; next<br>CMP R1,#0<br>BEQ done<br>CMP R1,#'+'<br>BNE nPls<br>plus POP {R2,R3}<br>ADD R2,R3 ; add top two elements<br>PUSH {R2}<br>B Calc<br>nPls CMP R1,#'*'<br>BNE nMul<br>mult POP {R2,R3}<br>MUL R2,R3 ;multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0} | -    | put: I                           | ) points to the string to process<br>RO contains the value determined by the calculator |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|-----------------------------------------------------------------------------------------|

| <pre>plus POP {R2,R3} ADD R2,R3 ;add top two elements PUSH {R2} B Calc nPls CMP R1,#'*' BNE nMul mult POP {R2,R3} MUL R2,R3 ;multiply top two elements PUSH {R2} B Calc nMul SUB R1,#'0' PUSH {R1} ; push digit 0 to 9 B Calc done POP {R0}</pre> | <pre>plus POP {R2,R3}<br/>ADD R2,R3 ;add top two elements<br/>PUSH {R2}<br/>B Calc<br/>nPls CMP R1,#'*'<br/>BNE nMul<br/>mult POP {R2,R3}<br/>MUL R2,R3 ;multiply top two elements<br/>PUSH {R2}<br/>B Calc<br/>nMul SUB R1,#'0'<br/>PUSH {R1} ; push digit 0 to 9<br/>B Calc<br/>done POP {R0}</pre>                                                                                                                               | <pre>plus POP {R2,R3}<br/>ADD R2,R3 ;add top two elements<br/>PUSH {R2}<br/>B Calc<br/>nPls CMP R1,#'*'<br/>BNE nMul<br/>mult POP {R2,R3}<br/>MUL R2,R3 ;multiply top two elements<br/>PUSH {R2}<br/>B Calc<br/>nMul SUB R1,#'0'<br/>PUSH {R1} ; push digit 0 to 9<br/>B Calc<br/>done POP {R0}</pre>                                                                                                                              | luit | LDRB<br>ADD<br>CMP<br>BEQ<br>CMP | R0,R0,#1 ; next<br>R1,#0<br>done<br>R1,#'+'                                             |

| BNE nMul<br>mult POP {R2,R3}<br>MUL R2,R3 ;multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                       | BNE nMul<br>mult POP {R2,R3}<br>MUL R2,R3 ;multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                                                                                                                                                                         | BNE nMul<br>mult POP {R2,R3}<br>MUL R2,R3 ;multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                                                                                                                                                                        | plus | POP<br>ADD<br>PUSH               | <pre>{R2,R3} R2,R3 ;add top two elements {R2}</pre>                                     |

| MUL R2,R3 ;multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                       | MUL R2,R3 ;multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                                                                                                                                                                                                         | MUL R2,R3 ;multiply top two elements<br>PUSH {R2}<br>B Calc<br>nMul SUB R1,#'0'<br>PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                                                                                                                                                                                                        | nPls |                                  |                                                                                         |

| PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                                                                                                          | PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                                                                                                                                                                                                                                                                                            | PUSH {R1} ; push digit 0 to 9<br>B Calc<br>done POP {R0}                                                                                                                                                                                                                                                                                                                                                                           | mult | MUL<br>PUSH                      | R2,R3 ;multiply top two elements<br>{R2}                                                |

| done POP {R0}                                                                                                                                                                                                                                     | done POP {R0}                                                                                                                                                                                                                                                                                                                                                                                                                       | done POP {R0}                                                                                                                                                                                                                                                                                                                                                                                                                      | nMul | PUSH                             | <pre>{R1} ; push digit 0 to 9</pre>                                                     |

|                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    | done | POP                              | {R0}                                                                                    |

Memory access instructions

|       | •         |          | tructions                                                                           |     |                                                 |

|-------|-----------|----------|-------------------------------------------------------------------------------------|-----|-------------------------------------------------|

| I     | LDR       |          | [Rn]                                                                                |     | load 32-bit number at [Rn] to Rd                |

| I     | DR        | Rd,      | [Rn,#off]                                                                           | ;   | load 32-bit number at [Rn+off] to Rd            |

| I     | DR        | Rd,      | =value                                                                              | ;   | set Rd equal to any 32-bit value (PC rel)       |

| I     | DRH       | Rd,      | [Rn]                                                                                | ;   | load unsigned 16-bit at [Rn] to Rd              |

| I     | DRH       | Rd,      | [Rn,#off]                                                                           | ;   | load unsigned 16-bit at [Rn+off] to Rd          |

| I     | DRSH      | Rd.      | [Rn]                                                                                | ;   | load signed 16-bit at [Rn] to Rd                |

|       | DRSH      | '        |                                                                                     |     | load signed 16-bit at [Rn+off] to Rd            |

|       | LDRB      | -        | [Rn]                                                                                |     | load unsigned 8-bit at [Rn] to Rd               |

|       |           |          |                                                                                     |     | load unsigned 8-bit at [Rn+off] to Rd           |

|       | LDRB      |          |                                                                                     |     | -                                               |

|       |           | Rd,      |                                                                                     |     | load signed 8-bit at [Rn] to Rd                 |

| I     | LDRSB     | Rd,      | [Rn,#off]                                                                           |     | load signed 8-bit at [Rn+off] to Rd             |

| S     | STR       | Rt,      | [Rn]                                                                                | ;   | store 32-bit Rt to [Rn]                         |

| S     | STR       | Rt,      | [Rn,#off]                                                                           | ;   | store 32-bit Rt to [Rn+off]                     |

| s     | STRH      | Rt,      | [Rn]                                                                                | ;   | store least sig. 16-bit Rt to [Rn]              |

| s     | STRH      | Rt,      | [Rn,#off]                                                                           | ;   | store least sig. 16-bit Rt to [Rn+off]          |

|       | STRB      |          | [Rn]                                                                                |     | store least sig. 8-bit Rt to [Rn]               |

|       | STRB      |          |                                                                                     |     | store least sig. 8-bit Rt to [Rn+off]           |

|       | PUSH      | {Rt]     |                                                                                     |     | push 32-bit Rt onto stack                       |

|       |           |          | -                                                                                   |     |                                                 |

|       | POP       | {Rd]     | -                                                                                   | -   | pop 32-bit number from stack into Rd            |

|       | ADR .     |          | label                                                                               |     | set Rd equal to the address at label            |

| M     | 40V{S}    |          | -                                                                                   |     | set Rd equal to op2                             |

| M     | 10V       | Rd,      | #im16                                                                               | ;   | set Rd equal to im16, im16 is 0 to 65535        |

| M     | IVN {S}   | } Rd,    | <op2></op2>                                                                         | ;   | set Rd equal to -op2                            |

| Bran  | ch inst   | ruction  | IS                                                                                  |     |                                                 |

| Е     | 3 ]       | label    | ; branch                                                                            | to  | label Always                                    |

| Е     |           | label    |                                                                                     | if  | -                                               |

|       |           | label    |                                                                                     |     | -                                               |

|       |           |          |                                                                                     |     | •                                               |

|       |           | label    | -                                                                                   |     |                                                 |

|       | -         | label    | ,                                                                                   |     |                                                 |

| E     |           |          | ; branch                                                                            |     |                                                 |

| E     | BLO ]     | label    | ; branch                                                                            | if  | C == 0 Lower, unsigned <                        |

| E     | BMI ]     | label    | ; branch                                                                            | if  | N == 1 Negative                                 |

| Е     | 3PL ]     | label    | ; branch                                                                            | if  | N == 0 Positive or zero                         |

| Е     | svs 1     | label    | ; branch                                                                            | if  | V == 1 Overflow                                 |

| Е     |           | label    |                                                                                     |     |                                                 |

|       |           | label    |                                                                                     |     | C==1 and Z==0 Higher, unsigned >                |

|       |           | label    |                                                                                     |     | $C==0$ or $Z==1$ Lower or same, unsigned $\leq$ |

|       |           |          |                                                                                     |     |                                                 |

|       | -         |          | ; branch                                                                            |     |                                                 |

|       |           | label    | ,                                                                                   |     | , 2                                             |

|       |           | label    |                                                                                     |     | Z==0 and N==V Greater than, signed >            |

| E     | BLE ]     | label    | ; branch                                                                            | if  | Z==1 or N!=V Less than or equal, signed $\leq$  |

| E     | SX E      | Rm       | ; branch                                                                            | in  | direct to location specified by Rm              |

| E     | 3L ]      | label    | ; branch                                                                            | to  | subroutine at label                             |

| Е     | BLX B     | Rm       | ; branch                                                                            | to  | subroutine indirect specified by Rm             |

| Inter | runt in   | structio |                                                                                     |     | <b>· ·</b>                                      |

|       | CPSIE     | I        | 0115                                                                                |     | enable interrupts (I=0)                         |

|       | CPSID     | ī        |                                                                                     |     | disable interrupts (I=1)                        |

|       |           |          | ~                                                                                   | '   | disable interrupts (1-1)                        |

|       |           | ruction  |                                                                                     |     |                                                 |

|       |           |          |                                                                                     |     | Rd=Rn&op2 (op2 is 32 bits)                      |

|       |           |          |                                                                                     |     | Rd=Rn op2 (op2 is 32 bits)                      |

|       |           |          |                                                                                     |     | Rd=Rn^op2 (op2 is 32 bits)                      |

| E     | BIC{S     | } {Rd    | ,} Rn, <op2< td=""><td>&gt; ;</td><td>Rd=Rn&amp;(~op2) (op2 is 32 bits)</td></op2<> | > ; | Rd=Rn&(~op2) (op2 is 32 bits)                   |

| С     | DRN { S } | } {Rd    | ,} Rn, <op2< td=""><td>&gt; ;</td><td>Rd=Rn (~op2) (op2 is 32 bits)</td></op2<>     | > ; | Rd=Rn (~op2) (op2 is 32 bits)                   |

|       |           |          | Rm, Rs                                                                              |     | logical shift right Rd=Rm>>Rs (unsigned)        |

|       |           |          | Rm, #n                                                                              |     | logical shift right Rd=Rm>>n (unsigned)         |

|       |           |          | Rm, Rs                                                                              |     | arithmetic shift right Rd=Rm>>Rs (signed)       |

| -     |           | ,,       | , 100                                                                               | ,   |                                                 |

```

ASR{S} Rd, Rm, #n

; arithmetic shift right Rd=Rm>>n (signed)

LSL{S} Rd, Rm, Rs

; shift left Rd=Rm<<Rs (signed, unsigned)</pre>

; shift left Rd=Rm<<n (signed, unsigned)</pre>

LSL{S} Rd, Rm, #n

Arithmetic instructions

ADD{S} {Rd,} Rn, \langle op2 \rangle; Rd = Rn + op2

ADD{S} {Rd,} Rn, #im12 ; Rd = Rn + im12, im12 is 0 to 4095

SUB{S} {Rd}, Rn, <op2>; Rd = Rn - op2

SUB{S} {Rd,} Rn, #im12 ; Rd = Rn - im12, im12 is 0 to 4095

RSB{S} {Rd}, Rn, <op2>; Rd = op2 - Rn

RSB{S} {Rd_{,}} Rn_{,} \#im12 ; Rd = im12 - Rn

CMP

Rn, <op2>

; Rn - op2

sets the NZVC bits

CMN

Rn, <op2>

; Rn - (-op2)

sets the NZVC bits

MUL{S} {Rd}, Rn, Rm; Rd = Rn * Rm

signed or unsigned

MLA

Rd, Rn, Rm, Ra ; Rd = Ra + Rn*Rm signed or unsigned

MLS

Rd, Rn, Rm, Ra; Rd = Ra - Rn*Rm

signed or unsigned

UDIV

{Rd,} Rn, Rm

; Rd = Rn/Rm

unsigned

SDIV

{Rd,} Rn, Rm

; Rd = Rn/Rm

signed

Notes Ra Rd Rm Rn Rt represent 32-bit registers

value

any 32-bit value: signed, unsigned, or address

{S}

if S is present, instruction will set condition codes

any value from 0 to 4095

#im12

#im16

any value from 0 to 65535

{Rd,}

if Rd is present Rd is destination, otherwise Rn

any value from 0 to 31

#n

any value from -255 to 4095

#off

label

any address within the ROM of the microcontroller

the value generated by <op2>

op2

Examples of flexible operand <op2> creating the 32-bit number. E.g., Rd = Rn+op2

ADD Rd, Rn, Rm

; op2 = Rm

ADD Rd, Rn, Rm, LSL #n ; op2 = Rm<<n Rm is signed, unsigned

ADD Rd, Rn, Rm, LSR #n ; op2 = Rm>>n Rm is unsigned

ADD Rd, Rn, Rm, ASR #n ; op2 = Rm>>n Rm is signed

ADD Rd, Rn, #constant ; op2 = constant, where X and Y are hexadecimal digits:

produced by shifting an 8-bit unsigned value left by any number of bits

in the form 0x00XY00XY

0x0000.0000

256k Flash

in the form 0xXY00XY00

ROM

in the form 0xXXXXXXX

0x0003.FFFF

R0

R1

0x2000.0000

32k RAM

R2

Condition code bits

R3

0x2000.7FFF

N negative

R4

General

R5

Z zero

0x4000.0000

R6

purpose -

I/O ports

V signed overflow

R7

registers

C carry or

R8

0x400F.FFFF

unsigned overflow

R9

R10

0xE000.0000

Internal I/O

R11

R12

PPB

0xE004.1FFF

Stack pointer R13 (MSP)

Link register R14 (LR)

Program counter

R15 (PC)

DCB

1,2,3 ; allocates three 8-bit byte(s)

1,2,3 ; allocates three 16-bit halfwords

DCW

1,2,3 ; allocates three 32-bit words

DCD

SPACE 4 ; reserves 4 bytes

```

| Address     | 7    | 6    | 5     | 4     | 3     | 2     | 1     | 0     | Name               |

|-------------|------|------|-------|-------|-------|-------|-------|-------|--------------------|

| \$400F.E608 |      |      | GPIOF | GPIOE | GPIOD | GPIOC | GPIOB | GPIOA | SYSCTL_RCGCGPIO_R  |

| \$4000.53FC | DATA | DATA | DATA  | DATA  | DATA  | DATA  | DATA  | DATA  | GPIO_PORTB_DATA_R  |

| \$4000.5400 | DIR  | DIR  | DIR   | DIR   | DIR   | DIR   | DIR   | DIR   | GPIO PORTB DIR R   |

| \$4000.5420 | SEL  | SEL  | SEL   | SEL   | SEL   | SEL   | SEL   | SEL   | GPIO PORTB AFSEL R |

| \$4000.551C | DEN  | DEN  | DEN   | DEN   | DEN   | DEN   | DEN   | DEN   | GPIO_PORTB_DEN_R   |

Table 4.5. TM4C123 Port B parallel ports. Each register is 32 bits wide. Bits 31 – 8 are zero.

|     | Address    |      | 31 | 30                                 | 29-7     | 6       | 5          | 4     | 3         | 2   | 1        |        | 0     | Name       |

|-----|------------|------|----|------------------------------------|----------|---------|------------|-------|-----------|-----|----------|--------|-------|------------|

|     | 0xE000E100 | 0    |    | F                                  |          | UART1   | UART0      | Е     | D         | С   | В        |        | А     | NVIC_EN0_R |

|     |            |      |    |                                    |          |         |            |       |           |     |          |        |       |            |

| Ac  | ldress     | 31-2 | 24 | 23-17 16 15-3 2 1                  |          |         |            | 0     |           | Nan | ne       |        |       |            |

| \$E | 000E010    | 0    |    | 0 COUNT 0 CLK SRC INTEN ENABLE     |          |         |            |       | BLE       | NV  | IC_ST    | CTRL_R |       |            |

| \$E | 000E014    | 0    |    | 24-bit RELOAD value NVIC ST RELOAD |          |         |            |       |           |     | RELOAD_R |        |       |            |

| \$E | 000E018    | 0    |    |                                    | 24-bit ( | CURRENT | value of S | vsTic | ck counte | er  |          | NV     | IC ST | CURRENT R  |

| Address    | 31-29   | 28-24 | 23-21  | 20-8 | 7-5   | 4-0 | Name            |

|------------|---------|-------|--------|------|-------|-----|-----------------|

| \$E000ED20 | SYSTICK | 0     | PENDSV | 0    | DEBUG | 0   | NVIC_SYS_PRI3_R |

Table 9.6. SysTick registers.

Table 9.6 shows the SysTick registers used to create a periodic interrupt. SysTick has a 24-bit counter that decrements at the bus clock frequency. Let  $f_{BUS}$  be the frequency of the bus clock, and let *n* be the value of the **RELOAD** register. The frequency of the periodic interrupt will be  $f_{BUS}/(n+1)$ . First, we clear the **ENABLE** bit to turn off SysTick during initialization. Second, we set the **RELOAD** register. Third, we write to the **NVIC\_ST\_CURRENT\_R** value to clear the counter. Lastly, we write the desired mode to the control register, **NVIC\_ST\_CTRL\_R**. To turn on the SysTick, we set the **ENABLE** bit. We must set **CLK\_SRC=1**, because **CLK\_SRC=0** external clock mode is not implemented. We set **INTEN** to arm SysTick interrupts. The standard name for the SysTick ISR is **SysTick\_Handler**.

| Address     | 31-2     |       |       |     |       | 1     |       | 0     | Name             |  |  |

|-------------|----------|-------|-------|-----|-------|-------|-------|-------|------------------|--|--|

| \$400F.E638 |          |       |       |     |       | ADC1  |       | ADC0  | SYSCTL RCGCADC R |  |  |

|             |          |       |       |     |       |       |       |       |                  |  |  |

| -           | 31-14    | 13-12 | 11-10 | 9-8 | 7-6   | 5-4   | 3-2   | 1-0   |                  |  |  |

| \$4003.8020 |          | SS3   |       | SS2 |       | SS1   |       | SS0   | ADC0_SSPRI_R     |  |  |

|             |          |       |       |     |       |       |       |       |                  |  |  |

|             |          | 31    | -16   |     | 15-12 | 11-8  | 7-4   | 3-0   |                  |  |  |

| \$4003.8014 |          |       |       |     | EM3   | EM2   | EM1   | EM0   | ADC0_EMUX_R      |  |  |

|             |          |       |       |     |       |       |       |       |                  |  |  |

|             |          | 31    | -4    |     | 3     | 2     | 1     | 0     |                  |  |  |

| \$4003.8000 |          |       |       |     | ASEN3 | ASEN2 | ASEN1 | ASEN0 | ADC0_ACTSS_R     |  |  |

| \$4003.80A0 |          |       |       |     |       | MU    | X0    |       | ADC0_SSMUX3_R    |  |  |

| \$4003.80A4 |          |       |       |     | TS0   | IE0   | END0  | D0    | ADC0_SSCTL3_R    |  |  |

| \$4003.8028 |          |       |       |     | SS3   | SS2   | SS1   | SS0   | ADC0 PSSI R      |  |  |

| \$4003.8004 |          |       |       |     | INR3  | INR2  | INR1  | INR0  | ADC0_RIS_R       |  |  |

| \$4003.8008 |          |       |       |     | MASK3 | MASK2 | MASK1 | MASK0 | ADC0 IM R        |  |  |

| \$4003.8FC4 | 003.8FC4 |       |       |     |       |       | Speed |       |                  |  |  |

|             |          |       |       |     | •     |       |       |       | ·                |  |  |

|             |          | 31    | -12   |     |       | 11-   | -0    |       |                  |  |  |

| \$4003.80A8 |          |       |       |     |       | DA    | ГА    |       | ADC0 SSFIFO3 R   |  |  |

Table 10.3. The TM4C ADC registers. Each register is 32 bits wide.

Set Speed to 0001 for slow speed operation. The ADC has four sequencers, but we will use only sequencer 3. We set the ADC\_SSPRI\_R register to 0x3210 to make sequencer 3 the lowest priority. Because we are using just one sequencer, we just need to make sure each sequencer has a unique priority. We set bits 15–12 (EM3) in the ADC\_EMUX\_R register to specify how the ADC will be triggered. If we specify software start (EM3=0x0), then the software writes an 8 (SS3) to the ADC\_PSSI\_R to initiate a conversion on sequencer 3. Bit 3 (INR3) in the ADC\_RIS\_R register will be set when the conversion is complete. We can enable and disable the sequencers using the ADC\_ACTSS\_R register. Which channel we sample is configured by writing to the ADC\_SSMUX3\_R register. The ADC\_SSCTL3\_R register specifies the mode of the ADC sample. Clear TS0. We set IE0 so that the INR3 bit is set on ADC conversion, and clear it when no flags are needed. We will set IE0 for both interrupt and busy-wait synchronization. When using sequencer 3, there is only one sample, so END0 will always be set, signifying this sample is the end of the sequence. Clear the D0 bit. The ADC\_RIS\_R

register has flags that are set when the conversion is complete, assuming the IE0 bit is set. Do not set bits in the ADC\_IM\_R register because we do not want interrupts. Write one to ADC\_ISC\_R to clear the corresponding bit in the ADC\_RIS\_R register.

UARTO pins are on PA1 (transmit) and PA0 (receive). The UARTO\_IBRD\_R and UARTO\_FBRD\_R registers specify the baud rate. The baud rate divider is a 22-bit binary fixed-point value with a resolution of 2<sup>-6</sup>. The Baud16 clock is created from the system bus clock, with a frequency of (Bus clock frequency)/divider. The baud rate is

**Baud rate = Baud16/16 =** (Bus clock frequency)/(16\*divider) We set bit 4 of the UARTO\_LCRH\_R to enable the hardware FIFOs. We set both bits 5 and 6 of the UARTO\_LCRH\_R to establish an 8-bit data frame. The **RTRIS** is set on a receiver timeout, which is when the receiver FIFO is not empty and no incoming frames have occurred in a 32-bit time period. The arm bits are in the UARTO\_IM\_R register. To acknowledge an interrupt (make the trigger flag become zero), software writes a 1 to the corresponding bit in the UARTO\_IC\_R register. We set bit 0 of the UARTO\_CTL\_R to enable the UART. Writing to UARTO\_DR\_R register will output on the UART. This data is placed in a 16-deep transmit hardware FIFO. Data are transmitted first come first serve. Received data are place in a 16-deep receive hardware FIFO. Reading from UARTO\_DR\_R register will get one data from the receive hardware FIFO. The status of the two FIFOs can be seen in the UARTO\_FR\_R register (FF is FIFO full, FE is FIFO empty). The standard name for the UARTO ISR is UARTO\_Handler. RXIFLSEL specifies the receive FIFO level that causes an interrupt (010 means interrupt on  $\geq \frac{1}{2}$  full, or 7 to 8 characters). TXIFLSEL specifies the transmit FIFO level that causes an interrupt (010 means interrupt on  $\leq \frac{1}{2}$  full, or 9 to 8 characters).

|             | 31-12    | 11    | 10    | 9       | 8           |       | 7–0   |               | Name          |

|-------------|----------|-------|-------|---------|-------------|-------|-------|---------------|---------------|

| \$4000.C000 |          | OE    | BE    | PE      | FE          |       | DATA  | 1             | UART0_DR_R    |

|             |          | 31-   | _3    |         | 3           | 2     | 1     | 0             |               |

| \$4000.C004 |          | 51    | 5     |         | OE          | BE    | PE    | FE            | UARTO RSR R   |

|             |          |       |       |         |             |       |       | •             |               |

|             | 31-8     | 7     | 6     | 5       | 4           | 3     |       | 2-0           | _             |

| \$4000.C018 |          | TXFE  | RXFF  | TXFF    | RXFE        | BUSY  |       |               | UARTO FR R    |

|             | 31–16    |       |       |         | 15–0        |       |       |               |               |

| \$4000.C024 | 51-10    |       |       |         | DIVIN       | [     |       |               | UART0_IBRD_R  |

|             |          |       |       |         |             | -     |       |               |               |

|             |          | 31-   | -6    |         |             |       | 5-0   |               | _             |

| \$4000.C028 | 000.C028 |       |       |         |             | DIV   | /FRAC |               | UART0_FBRD_R  |

|             | 31-8     | 7     | 6-5   | 4       | 3           | 2     | 1     | 0             |               |

| \$4000.C02C | 51-0     | SPS   | WPEN  | FEN     | STP2        | EPS   | PEN   | BRK           | UART0_LCRH_R  |

| \$1000.0020 |          | 515   | WILI  | 1 121 ( | 5112        | LIS   | 1 111 | Ditt          | Lenal_ic      |

|             | 31-10    | 9     | 8     | 7       | 6–3         | 2     | 1     | 0             |               |

| \$4000.C030 |          | RXE   | TXE   | LBE     |             | SIRLP | SIREN | UARTEN        | UART0_CTL_R   |

|             |          |       |       |         | _           |       |       | •             |               |

| \$4000.C034 |          | 31-   | -6    |         | 5-<br>RXIFI |       | TV    | 2-0<br>IFLSEL | LIADTO JELC D |

| \$4000.C034 |          |       |       |         | KAIFI       | LSEL  | 17    | IFLSEL        | UART0_IFLS_R  |

|             | 31-11    | 10    | 9     | 8       | 7           | 6     | 5     | 4             |               |

| \$4000.C038 |          | OEIM  | BEIM  | PEIM    | FEIM        | RTIM  | TXIM  | RXIM          | UARTO IM R    |

| \$4000.C03C |          | OERIS | BERIS | PERIS   | FERIS       | RTRIS | TXRIS | RXRIS         | UART0_RIS_R   |

| \$4000.C040 |          | OEMIS | BEMIS | PEMIS   | FEMIS       | RTMIS | TXMIS | RXMIS         | UART0_MIS_R   |

| \$4000.C044 |          | OEIC  | BEIC  | PEIC    | FEIC        | RTIC  | TXIC  | RXIC          | UART0_IC_R    |

|             |          |       |       |         |             | -     |       |               |               |

Table 11.2. UART0 registers. Each register is 32 bits wide. Shaded bits are zero.