## Exam 1 Fun Times

**Date:** October 5, 2012

| Printed Name: |       |       |  |

|---------------|-------|-------|--|

|               | Last, | First |  |

|               |       |       |  |

Your signature is your promise that you have not cheated and will not cheat on this exam, nor will you help others to cheat on this exam:

Signature:

## **Instructions:**

- Closed book and closed notes.

- No calculators or any electronic devices (turn cell phones off).

- You must put your answers on pages 2-6 only.

- You have 50 minutes, so allocate your time accordingly.

- Show your work, and put your answers in the boxes.

- Please read the entire quiz before starting.

(3) Question 1. Which of the following statements is most true? If we wished to reduce the power consumption used by our microcontroller

A) we could increase the operating voltage?

B) we could decrease the frequency of the bus clock?

C) we could set bits in the DEN register for unused pins?

D) none of A B or C is correct

E) A B and C are all correct

(4) Question 2. Digital logic currently uses binary because it is fast, low power, and very small. In the future, an EE319K student invents ternary logic that is faster, smaller and lower power than binary. This means each ternary digit can be 0, 1, or 2. Ternary means base 3 in the same way binary means base 2. What are the four **basis** elements of unsigned four-digit ternary number? Give your answers as a decimal numbers.

(3) Question 3. Consider the following 8-bit subtraction (assume registers are 8 bits wide) Load 0x32 into R1 Load 0x9C into R2 Subtract R3 = R1-R2 What will be the 8-bit result in Register R3? ------

What will be the value of the overflow (V) bit? -----

What will be the value of the carry (C) bit? -----

## EE319K Fall 2012 Exam 1A Modified

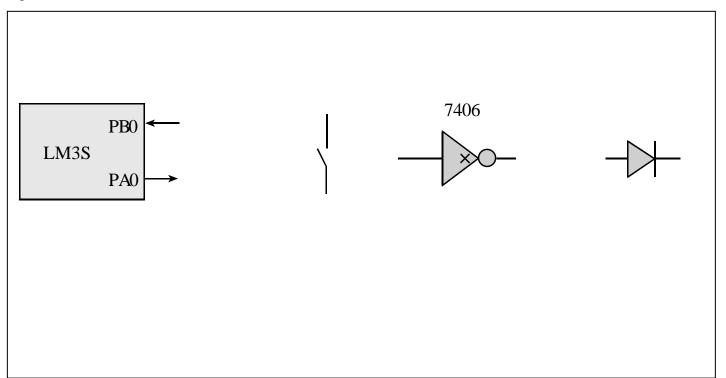

(20) Question 4. Interface the LED to PA0 in positive logic. The desired LED operating point is 1.0V at 2 mA. At 2 mA you can assume the  $V_{OL}$  of the 7406 will be 0.5 V. Assume the output high voltage of the microcontroller is 3.2 V and the output low voltage is 0.1V. Interface the switch to PB0 using positive logic. No software is required in this question, and you may assume PA0 is an output and PB0 an input. Assume the pull-down feature of PB0 will be activated by software. Your bag of parts includes the switch, the 7406, the LED, and resistors (you specify the values). Pick the fewest components to use (you may or may not need them all.) You may also use 3.3V, 5V power and ground.

(15) Question 5. Write an assembly subroutine that selects bit 8. The input to the subroutine is a 32-bit number in R0. The output in R0 is 0 if the input bit 8 is 0, and the output is 1 if the input bit 8 is 1.

(5) **Question 6.** Write C function that selects bit 8. The input to the function is an unsigned 32-bit number. The output of the function is 0 if the input bit 8 is 0, and the output is 1 if the input bit 8 is 1.

For questions 7 and 8, don't worry about establishing the reset vector, creating a main program, or initializing the stack pointer. You may use RAM-based global variables. Bit-specific addressing is allowed but not required. You may use the following definitions GPIO\_PORTB\_DATA\_R EQU 0x400053FC

GPIO\_PORTB\_DATA\_R EQU 0x400053FC GPIO\_PORTB\_DIR\_R EQU 0x40005400 GPIO\_PORTB\_AFSEL\_R EQU 0x40005420 GPIO\_PORTB\_DEN\_R EQU 0x4000551C SYSCTL\_RCGCGPIO\_R EQU 0x400FE608 SYSCTL\_RCGCGPIO\_GPIOB EQU 0x00000002 ; port B Clock Gating Control

(10) Question 7. Fill in the boxes with hexadecimal numbers that initialize Port B. Bits 0, 1, and 2 are input. Bits 3 and 5 are output.

PortB Init LDR R1, =SYSCTL RCGCGPIO R LDR R0, [R1] ORR R0, R0, #-----STR R0, [R1] NOP NOP LDR R1, =GPIO PORTB DIR R LDR R0, [R1] ORR R0, R0, #-----/ BIC R0, R0, #-----\ STR R0, [R1] LDR R1, =GPIO PORTB AFSEL R LDR R0, [R1] BIC R0, R0, #-----\_\_\_\_\_ STR R0, [R1] LDR R1, =GPIO\_PORTB\_DEN\_R LDR R0, [R1] ORR R0, R0, #-----STR R0, [R1] BX LR

(30) Question 8. Write an assembly language main program that first calls the initialization and then performs steps 2, 3, and 4 over and over infinitely.

1) execute **PortB\_Init** defined in Question 7.

2) read the inputs;

3) if all three inputs are equal to each other (inputs are 000 or 111) then toggle output bit 3,

4) otherwise (inputs are 001, 010, 011, 100, 101, or 110) toggle output bit 5.

Write friendly code. Comments are allowed but not needed.

(10) Question 9. Write a C language main program that first calls the initialization and then performs steps 2, 3, and 4 over and over infinitely.

1) execute **PortB Init()**; defined in Question 7.

2) read the inputs;

3) if all three inputs are equal to each other (inputs are 000 or 111) then toggle output bit 3,

4) otherwise (inputs are 001, 010, 011, 100, 101, or 110) toggle output bit 5.

Write friendly code. Comments are allowed but not needed. With this definition #define PORTB (\*((volatile uint32 t \*)0x400053FC))

You will be able to read and write to Port B. For example

| n = PORTB;   | // reads | all 8 | 8 bits | of Port 1 | 3 into | variable n  |

|--------------|----------|-------|--------|-----------|--------|-------------|

| PORTB = $m;$ | // write | all 8 | 8 bits | of Port 1 | 3 with | data from m |

## Memory access instructions

| Memory access man actions                                                             |                                                                          |  |  |  |  |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|--|

| LDR Rd, [Rn]                                                                          | ; load 32-bit number at [Rn] to Rd                                       |  |  |  |  |

| LDR Rd, [Rn,#off]                                                                     | ; load 32-bit number at [Rn+off] to Rd                                   |  |  |  |  |

| LDR Rd, =value                                                                        | ; set Rd equal to any 32-bit value (PC rel)                              |  |  |  |  |

| LDRH Rd, [Rn]                                                                         | ; load unsigned 16-bit at [Rn] to Rd                                     |  |  |  |  |

| LDRH Rd, [Rn,#off]                                                                    | ; load unsigned 16-bit at [Rn+off] to Rd                                 |  |  |  |  |

| LDRSH Rd, [Rn]                                                                        | ; load signed 16-bit at [Rn] to Rd                                       |  |  |  |  |

| LDRSH Rd, [Rn,#off]                                                                   | ; load signed 16-bit at [Rn+off] to Rd                                   |  |  |  |  |

| LDRB Rd, [Rn]                                                                         | ; load unsigned 8-bit at [Rn] to Rd                                      |  |  |  |  |

| ,                                                                                     | ; load unsigned 8-bit at [Rn+off] to Rd                                  |  |  |  |  |

| LDRSB Rd, [Rn]                                                                        | ; load signed 8-bit at [Rn] to Rd                                        |  |  |  |  |

| ,                                                                                     | ; load signed 8-bit at [Rn+off] to Rd                                    |  |  |  |  |

| STR Rt, [Rn]                                                                          | ; store 32-bit Rt to [Rn]                                                |  |  |  |  |

| , <u> </u>                                                                            | ; store 32-bit Rt to [Rn+off]                                            |  |  |  |  |

|                                                                                       |                                                                          |  |  |  |  |

|                                                                                       | ; store least sig. 16-bit Rt to [Rn]                                     |  |  |  |  |

|                                                                                       | ; store least sig. 16-bit Rt to [Rn+off]                                 |  |  |  |  |

|                                                                                       | ; store least sig. 8-bit Rt to [Rn]                                      |  |  |  |  |

|                                                                                       | ; store least sig. 8-bit Rt to [Rn+off]                                  |  |  |  |  |

| PUSH {Rt}                                                                             | ; push 32-bit Rt onto stack                                              |  |  |  |  |

| POP {Rd}                                                                              | ; pop 32-bit number from stack into Rd                                   |  |  |  |  |

| ADR Rd, label                                                                         | ; set Rd equal to the address at label                                   |  |  |  |  |

| $MOV{S} Rd, $                                                                         | ; set Rd equal to op2                                                    |  |  |  |  |

| MOV Rd, #im16                                                                         | ; set Rd equal to im16, im16 is 0 to 65535                               |  |  |  |  |

| $MVN{S} Rd, $                                                                         | ; set Rd equal to -op2                                                   |  |  |  |  |

| Branch instructions                                                                   |                                                                          |  |  |  |  |

| B label ; branch                                                                      | to label Always                                                          |  |  |  |  |

| BEQ label ; branch                                                                    | if Z == 1 Equal                                                          |  |  |  |  |

| BNE label ; branch                                                                    | if Z == 0 Not equal                                                      |  |  |  |  |

| BCS label ; branch                                                                    | if C == 1 Higher or same, unsigned $\geq$                                |  |  |  |  |

| BHS label ; branch                                                                    | if C == 1 Higher or same, unsigned $\geq$                                |  |  |  |  |

| BCC label ; branch                                                                    | if C == 0 Lower, unsigned <                                              |  |  |  |  |

| BLO label ; branch                                                                    | if C == 0 Lower, unsigned <                                              |  |  |  |  |

| BMI label ; branch                                                                    | if N == 1 Negative                                                       |  |  |  |  |

| BPL label ; branch                                                                    | if N == 0 Positive or zero                                               |  |  |  |  |

|                                                                                       | if V == 1 Overflow                                                       |  |  |  |  |

|                                                                                       | if V == 0 No overflow                                                    |  |  |  |  |

| ,,                                                                                    | if C==1 and Z==0 Higher, unsigned >                                      |  |  |  |  |

| BLS label ; branch                                                                    |                                                                          |  |  |  |  |

| ,                                                                                     | if N == V Greater than or equal, signed $\geq$                           |  |  |  |  |

|                                                                                       | 1 / 5                                                                    |  |  |  |  |

|                                                                                       | if N != V Less than, signed <<br>if Z==0 and N==V Greater than, signed > |  |  |  |  |

|                                                                                       | if $Z=1$ or N!=V Less than or equal, signed $\leq$                       |  |  |  |  |

|                                                                                       |                                                                          |  |  |  |  |

|                                                                                       | indirect to location specified by Rm                                     |  |  |  |  |

|                                                                                       | to subroutine at label                                                   |  |  |  |  |

|                                                                                       | to subroutine indirect specified by Rm                                   |  |  |  |  |

| Interrupt instructions                                                                |                                                                          |  |  |  |  |

| CPSIE I                                                                               | ; enable interrupts (I=0)                                                |  |  |  |  |

| CPSID I                                                                               | ; disable interrupts (I=1)                                               |  |  |  |  |

|                                                                                       |                                                                          |  |  |  |  |

| Logical instructions                                                                  |                                                                          |  |  |  |  |

| $AND{S} {Rd}, Rn, $                                                                   |                                                                          |  |  |  |  |

| $ORR{S} {Rd}, Rn, < op2$                                                              |                                                                          |  |  |  |  |

| $EOR{S} {Rd}, Rn, < op2$                                                              |                                                                          |  |  |  |  |

| BIC{S} {Rd,} Rn, <op2< td=""><td>&gt; ; Rd=Rn&amp;(~op2) (op2 is 32 bits)</td></op2<> | > ; Rd=Rn&(~op2) (op2 is 32 bits)                                        |  |  |  |  |

| $ORN{S} {Rd}, Rn, < op2$                                                              | > ; Rd=Rn (~op2) (op2 is 32 bits)                                        |  |  |  |  |

|                                                                                       |                                                                          |  |  |  |  |

Program counter

R15 (PC)

```

LSR{S} Rd, Rm, Rs

; logical shift right Rd=Rm>>Rs (unsigned)

LSR{S} Rd, Rm, #n

; logical shift right Rd=Rm>>n

(unsigned)

; arithmetic shift right Rd=Rm>>Rs (signed)

ASR{S} Rd, Rm, Rs

; arithmetic shift right Rd=Rm>>n (signed)

ASR{S} Rd, Rm, #n

LSL{S} Rd, Rm, Rs

; shift left Rd=Rm<<Rs (signed, unsigned)

LSL{S} Rd, Rm, #n

; shift left Rd=Rm<<n (signed, unsigned)</pre>

Arithmetic instructions

ADD{S} {Rd,} Rn, \langle op2 \rangle; Rd = Rn + op2

ADD{S} {Rd,} Rn, \#im12; Rd = Rn + im12, im12 is 0 to 4095

SUB{S} {Rd}, Rd, Rn, <op2>; Rd = Rn - op2

SUB{S} {Rd,} Rn, #im12 ; Rd = Rn - im12, im12 is 0 to 4095

RSB{S} {Rd_{1}} Rn_{1} < op2 > ; Rd = op2 - Rn

RSB{S} {Rd_{,}} Rn_{,} \#im12 ; Rd = im12 - Rn

; Rn - op2

CMP

Rn, <op2>

sets the NZVC bits

CMN

Rn, <op2>

; Rn - (-op2)

sets the NZVC bits

; Rd = Rn * Rm

signed or unsigned

MUL{S} {Rd}, Rn, Rm

MLA

Rd, Rn, Rm, Ra ; Rd = Ra + Rn*Rm

signed or unsigned

MT.S

Rd, Rn, Rm, Ra ; Rd = Ra - Rn*Rm

signed or unsigned

UDIV

{Rd,} Rn, Rm

; Rd = Rn/Rm

unsigned

SDIV

{Rd,} Rn, Rm

; Rd = Rn/Rm

signed

Notes Ra Rd Rm Rn Rt represent 32-bit registers

any 32-bit value: signed, unsigned, or address

value

if S is present, instruction will set condition codes

{S}

#im12

any value from 0 to 4095

#im16

any value from 0 to 65535

if Rd is present Rd is destination, otherwise Rn

{Rd, }

any value from 0 to 31

#n

any value from -255 to 4095

#off

any address within the ROM of the microcontroller

label

op2

the value generated by <op2>

Examples of flexible operand <op2> creating the 32-bit number. E.g., Rd = Rn+op2

; op2 = Rm

ADD Rd, Rn, Rm

ADD Rd, Rn, Rm, LSL #n ; op2 = Rm<<n Rm is signed, unsigned

ADD Rd, Rn, Rm, LSR #n ; op2 = Rm>>n Rm is unsigned

ADD Rd, Rn, Rm, ASR #n ; op2 = Rm>>n Rm is signed

ADD Rd, Rn, #constant ; op2 = constant, where X and Y are hexadecimal digits:

produced by shifting an 8-bit unsigned value left by any number of bits

•

in the form 0x00XY00XY

in the form 0xXY00XY00

in the form 0xXYXYXYX

R0

0x0000.0000

R1

256k Flash

R2

ROM

0x0003.FFFF

Condition code bits

R3

N negative

R4

0x2000.0000

64k RAM

General

R5

Z zero

purpose -

R6

0x2000.FFFF

V signed overflow

registers

R7

C carry or

R8

0x4000.0000

R9

unsigned overflow

I/O ports

R10

0x41FF.FFFF

R11

R12

0xE000.0000

Stack pointer

R13 (MSP)

Internal I/O

Link register

R14 (LR)

PPB

0xE004.0FFF

```