Copyright

by

Yeong Foong Choo

2018

The Report committee for Yeong Foong Choo Certifies that this is the approved version of the following report:

# Complex Block Floating-Point Format with Box Encoding in Communication Systems

# APPROVED BY SUPERVISING COMMITTEE:

Brian L. Evans, Supervisor

Earl E. Swartzlander Jr.

# Complex Block Floating-Point Format with Box Encoding in Communication Systems

by

# Yeong Foong Choo

# Report

Presented to the Faculty of the Graduate School of the University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

# Master of Science in Engineering

The University of Texas at Austin May 2018 This report is dedicated to my wife, Mun and my newborn daughter, Grace.

### Acknowledgments

I would like to take this opportunity to thank Professor Brian L. Evans for allowing me to conduct this research topic in communication systems design. I am also thankful for the idea generation from Dr. Alan Gatherer at Huawei Labs. With the guidance of Dr. Gatherer and Dr. Evans, I had the opportunity of presenting my first publication at 2017 Asilomar Conference on Signals, Systems, and Computers. I would also like to offer my appreciation to Professor Earl E. Swartzlander Jr. for his willingness to be the reader of this report and for his detailed attention in suggesting improvement on this report.

My experience in pursuing the graduate degree of Electrical and Computer Engineering (ECE) is enriched by participating in all research-oriented networking events within the Embedded Signal Processing Lab (ESPL) and the Wireless Networking Communications Group (WNCG). The feedback that I received from Jinseok Choi, Junmo Sung, Faris Mismar, Matthew Koenig, and other remote ESPL members over the duration of my research project have been very valuable and ensuring the quality of my research presentation. At the Texas Wireless Summit 2017 and WNCG Open House 2018, Dr. Amine Mezghani was a consistent visitor at my poster presentation who offered valuable feedback at potential improvement of this project.

# Complex Block Floating-Point Format with Box Encoding in Communication Systems

by

Yeong Foong Choo, MSE The University of Texas at Austin, 2018 Supervisor: Brian L. Evans

This research project entails an efficient numeric digital representation in communication systems design. A complex block floating-point format with box encoding is proposed to encode an array of complex numbers that has better numeric resolution than its IEEE-754 counterpart when the same number of bits are allocated to the dominant value in the array. It is estimated that at least 10% of bit savings could be achieved by the new complex block representation on a quad-precision IEEE-754 format. A further bits savings of up to 18% could potentially be achieved for complex blocks at half-precision and single-precision IEEE-754 representation.

The implementation cost of the proposed block floating-point format is evaluated in terms of memory usage, design of arithmetic units, and memory input/output rates for communications system modeling and block diagrams. Further analysis is performed on the limitation and quantization effects of this complex block format relative to complex IEEE-754 format. The coverage of the arithmetic units design include complex block adder and complex block multiplier. The appropriate systems that would be required to perform algorithms such as the fast Fourier transform (forward and inverse) are designed using the proposed complex block format in multistages complex block multiply-adder.

The proposed block floating-point format is simulated as a new numeric class defined and implemented in MATLAB simulation environment. The MATLAB simulation is divided into two major parts. The first part of MATLAB simulation targets the simulation of complex block addition and complex block multiplication units for arbitrary size of complex samples per input block. The reference output values of complex block arithmetic are those computed with similar precision in IEEE-754 format. The second part of MATLAB simulation is performed on the system model of the single-carrier modulation-based and multi-carrier modulation-based communication systems. The quadrature amplitude modulation (QAM) is the baseband modulation type targeted in this work. The specification identified in the system model is relevant to those specified in the Long-Term Evolution (LTE) Standards for Base Station, Release 12.

# Table of Contents

| Lis      | st of Tables xi |              |                                                |      |  |  |  |

|----------|-----------------|--------------|------------------------------------------------|------|--|--|--|

| Lis      | st of           | Figure       | es 2                                           | xiii |  |  |  |

| 1        | Imp             | lemen        | lementation of Digital Communication Systems 1 |      |  |  |  |

|          | 1.1             | Digital      | Communication Systems Brief                    | 1    |  |  |  |

|          | 1.2             | Hardw        | are Design Constraints and Tradeoffs           | 3    |  |  |  |

|          | 1.3             | Digital      | l Signal Processor Architecture                | 4    |  |  |  |

|          | 1.4             | Data (       | Converter Architecture                         | 5    |  |  |  |

|          | 1.5             | Organization |                                                |      |  |  |  |

| <b>2</b> | Nur             | nber S       | ystems                                         | 7    |  |  |  |

|          | 2.1             | IEEE-        | 754 Floating-Point Format                      | 7    |  |  |  |

|          |                 | 2.1.1        | Binary Numeric Representation                  | 7    |  |  |  |

|          |                 | 2.1.2        | Implementation Complexity                      | 9    |  |  |  |

|          |                 | 2.1.3        | Complex-valued Representation                  | 11   |  |  |  |

|          | 2.2             | Compl        | ex Block Floating-Point Format                 | 11   |  |  |  |

|          |                 | 2.2.1        | Common Exponent Encoding                       | 13   |  |  |  |

|          |                 | 2.2.2        | Conversion with Two Parallel ADCs              | 19   |  |  |  |

|          |                 | 2.2.3        | Conversion with Single ADC                     | 20   |  |  |  |

| 3 | Pro                                        | posed Complex Block Floating-Point Representation 2                     |                                                                                                                                                                                                                                                                                                  |                                                                                                                        |  |  |

|---|--------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

|   | 3.1                                        | Expon                                                                   | ent Box Encoding Technique                                                                                                                                                                                                                                                                       | 21                                                                                                                     |  |  |

|   | 3.2                                        | Vector Arithmetic Subsystem Modeling                                    |                                                                                                                                                                                                                                                                                                  | 24                                                                                                                     |  |  |

|   |                                            | 3.2.1                                                                   | Complex Block Addition                                                                                                                                                                                                                                                                           | 24                                                                                                                     |  |  |

|   |                                            | 3.2.2                                                                   | Complex Block Multiplication                                                                                                                                                                                                                                                                     | 26                                                                                                                     |  |  |

|   | 3.3                                        | Algorit                                                                 | thms Modeling                                                                                                                                                                                                                                                                                    | 28                                                                                                                     |  |  |

|   |                                            | 3.3.1                                                                   | Fast Fourier Transform (Radix-2)                                                                                                                                                                                                                                                                 | 28                                                                                                                     |  |  |

|   |                                            | 3.3.2                                                                   | Fast Fourier Transform (Radix-4)                                                                                                                                                                                                                                                                 | 32                                                                                                                     |  |  |

|   | 3.4                                        | Analys                                                                  | sis and Limitation                                                                                                                                                                                                                                                                               | 34                                                                                                                     |  |  |

|   |                                            | 3.4.1                                                                   | Phase Resolution                                                                                                                                                                                                                                                                                 | 34                                                                                                                     |  |  |

|   |                                            | 3.4.2                                                                   | Block Wordlength Analysis                                                                                                                                                                                                                                                                        | 35                                                                                                                     |  |  |

|   | 3.4.3 Block Arithmetic Complexity Analysis |                                                                         |                                                                                                                                                                                                                                                                                                  |                                                                                                                        |  |  |

|   |                                            |                                                                         |                                                                                                                                                                                                                                                                                                  |                                                                                                                        |  |  |

| 4 | Syst                                       | tem M                                                                   | odel of Baseband Transceivers Design                                                                                                                                                                                                                                                             | 37                                                                                                                     |  |  |

| 4 | <b>Syst</b><br>4.1                         |                                                                         | odel of Baseband Transceivers Design<br>carrier Modulation System                                                                                                                                                                                                                                |                                                                                                                        |  |  |

| 4 | Ţ                                          |                                                                         |                                                                                                                                                                                                                                                                                                  | 37                                                                                                                     |  |  |

| 4 | Ţ                                          | Single-                                                                 | carrier Modulation System                                                                                                                                                                                                                                                                        | 37<br>38                                                                                                               |  |  |

| 4 | Ţ                                          | Single-<br>4.1.1                                                        | carrier Modulation System<br>Discrete-time Complex Baseband QAM Transmitter                                                                                                                                                                                                                      | 37<br>38<br>39                                                                                                         |  |  |

| 4 | Ţ                                          | Single-<br>4.1.1<br>4.1.2                                               | Carrier Modulation System<br>Discrete-time Complex Baseband QAM Transmitter<br>Discrete-time Complex Baseband QAM Receiver                                                                                                                                                                       | 37<br>38<br>39<br>41                                                                                                   |  |  |

| 4 | 4.1                                        | Single-<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                             | carrier Modulation System<br>Discrete-time Complex Baseband QAM Transmitter<br>Discrete-time Complex Baseband QAM Receiver<br>Channel Model and Assumptions                                                                                                                                      | <ul> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>41</li> </ul>                                                 |  |  |

| 4 | 4.1                                        | Single-<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                             | carrier Modulation System<br>Discrete-time Complex Baseband QAM Transmitter<br>Discrete-time Complex Baseband QAM Receiver<br>Channel Model and Assumptions<br>LTE Specifications and Requirements                                                                                               | <ul> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>41</li> <li>42</li> </ul>                                     |  |  |

| 4 | 4.1                                        | Single-<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Multi-                   | carrier Modulation System<br>Discrete-time Complex Baseband QAM Transmitter<br>Discrete-time Complex Baseband QAM Receiver<br>Channel Model and Assumptions<br>LTE Specifications and Requirements<br>carrier Modulation System                                                                  | <ol> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>41</li> <li>42</li> <li>43</li> </ol>                         |  |  |

| 4 | 4.1                                        | Single-<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Multi-<br>4.2.1          | carrier Modulation System<br>Discrete-time Complex Baseband QAM Transmitter<br>Discrete-time Complex Baseband QAM Receiver<br>Channel Model and Assumptions<br>LTE Specifications and Requirements<br>carrier Modulation System<br>Discrete-time OFDM Transmitter                                | <ol> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>41</li> <li>42</li> <li>43</li> <li>45</li> </ol>             |  |  |

| 4 | 4.1                                        | Single-<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Multi-<br>4.2.1<br>4.2.2 | carrier Modulation System<br>Discrete-time Complex Baseband QAM Transmitter<br>Discrete-time Complex Baseband QAM Receiver<br>Channel Model and Assumptions<br>LTE Specifications and Requirements<br>carrier Modulation System<br>Discrete-time OFDM Transmitter<br>Discrete-time OFDM Receiver | <ol> <li>37</li> <li>38</li> <li>39</li> <li>41</li> <li>41</li> <li>42</li> <li>43</li> <li>45</li> <li>45</li> </ol> |  |  |

|              | 5.1             | Signals Generation                                   | 47 |  |

|--------------|-----------------|------------------------------------------------------|----|--|

|              | 5.2             | MATLAB: Vector Arithmetic Unit                       | 48 |  |

|              | 5.3             | MATLAB: Algorithms Modeling Unit                     | 51 |  |

| 6            | Con             | clusion                                              | 54 |  |

|              | 6.1             | Summary                                              | 54 |  |

|              | 6.2             | Future Work                                          | 55 |  |

|              |                 |                                                      |    |  |

| A            | open            | dices                                                | 58 |  |

| $\mathbf{A}$ | Max             | ximum Exponent Difference for Low Quantization Error | 58 |  |

| в            | Pha             | se Resolution in Common Exponent Encoding            | 59 |  |

| $\mathbf{C}$ | Bloo            | ck Diagrams for Complex Block Arithmetic             | 60 |  |

| Bi           | Bibliography 64 |                                                      |    |  |

# List of Tables

| 2.1 | Table of IEEE-754 Format                                                  | 7  |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Table of Common Exponent                                                  | 15 |

| 2.3 | Table of Bit Savings in Common Exponent Format (64 Complex Samples)       | 17 |

| 3.1 | Table of Exponent Box Format                                              | 21 |

| 3.2 | Table of Bit Savings in Exponent Box Format (64 Complex Samples) $\ldots$ | 23 |

| 3.3 | Table of Exponent Box Shift Effect on Complex Mantissa Addition           | 26 |

| 3.4 | Table of Real Intermediate Mantissa in Multiplication                     | 28 |

| 3.5 | Table of Imaginary Intermediate Mantissa in Multiplication                | 28 |

| 3.6 | Table of Phase Resolution of Complex Block Format                         | 34 |

| 3.7 | Table of Wordlength Requirement for Complex Block Format                  | 35 |

| 3.8 | Table of Hardware Operations for Complex Block Addition                   | 36 |

| 3.9 | Table of Hardware Operations for Complex Block Multiplication             | 36 |

| 4.1 | Table of Complexity Analysis of Complex Baseband QAM Transmitter          | 39 |

| 4.2 | Table of Complexity Analysis of Complex Baseband QAM Receiver             | 40 |

| 4.3 | Table of QAM Specification                                                | 41 |

| 4.4 | Table of Digital Transceiver Specifications                               | 42 |

| 4.5 | Table of EVM Requirement of LTE Base Station Transmitter                  | 42 |

| 4.6 | Table of ACLR Requirement of LTE Base Station Transmitter                 | 42 |

| 4.7 | Table of Complexity Analysis of OFDM Transmitter                          | 44 |

| 4.8 | Table of Complexity Analysis of OFDM Receiver                 | 45 |

|-----|---------------------------------------------------------------|----|

| 4.9 | Table of EVM Window Length Requirement of Digital Transmitter | 46 |

# List of Figures

| 1.1  | Block Diagram of Simple Communication Systems                 | 1  |

|------|---------------------------------------------------------------|----|

| 1.2  | Block Diagram of Transmitter Baseband Processing              | 2  |

| 1.3  | Block Diagram of Receiver Baseband Processing                 | 3  |

| 2.1  | Bit Packing of IEEE-754                                       | 7  |

| 2.2  | Bit Packing of Complex IEEE-754 Extension                     | 11 |

| 2.3  | Bit Packing of Complex Block IEEE-754 Extension               | 12 |

| 2.4  | Plot of Phase-Magnitude Coherence                             | 13 |

| 2.5  | Plots of IQ Waveform and Upsampled Waveform of 64-QAM Symbols | 14 |

| 2.6  | Bit Packing of Common Exponent Format                         | 16 |

| 2.7  | Algorithm for Conversion to Common Exponent Format            | 17 |

| 2.8  | Plot of Common Exponent Format Effective Encoding Region      | 18 |

| 2.9  | Data Converter Architecture with Two Parallel ADCs            | 19 |

| 2.10 | Data Converter Architecture with One ADC                      | 20 |

| 3.1  | Bit Packing of Exponent Box Format                            | 22 |

| 3.2  | Algorithms for Conversion to Exponent Box Format              | 22 |

| 3.3  | Plot of Exponent Box Format Effective Encoding Region         | 23 |

| 3.4  | Interface of 2-to-1 Complex Block Arithmetic Subsystems       | 24 |

| 3.5  | Interface of 2-to-1 Complex Block Addition Subsystems         | 25 |

| 3.6  | Interface of 2-to-1 Complex Block Multiplication Subsystems   | 27 |

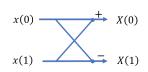

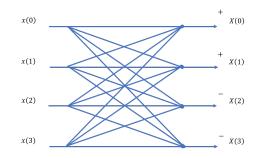

| Block Diagram of Radix-2 2-point FFT                                                                               | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

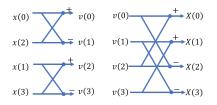

| Block Diagram of Radix-2 4-point FFT                                                                               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bit Packing of Radix-2 4-point FFT                                                                                 | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Block Diagram of Radix-4 4-point FFT                                                                               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

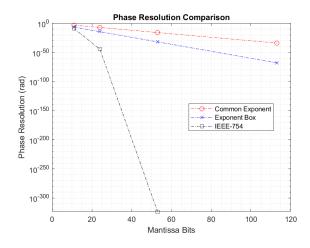

| Plot of Phase Resolution                                                                                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

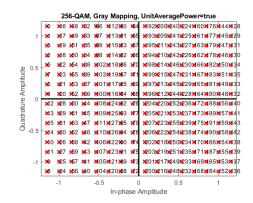

| Plot of 256-QAM Normalized Constellation                                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

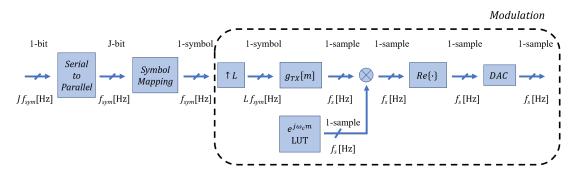

| Block Diagram of Complex Baseband QAM Transmitter                                                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Block Diagram of Complex Baseband QAM Receiver                                                                     | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

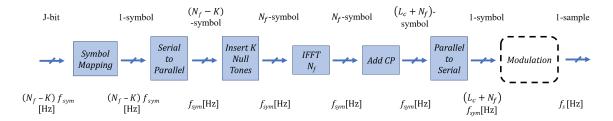

| Block Diagram of OFDM Transmitter                                                                                  | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

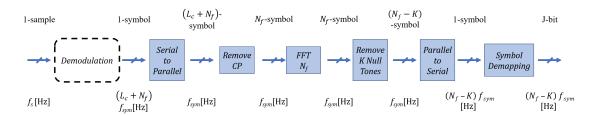

| Block Diagram of OFDM Receiver                                                                                     | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

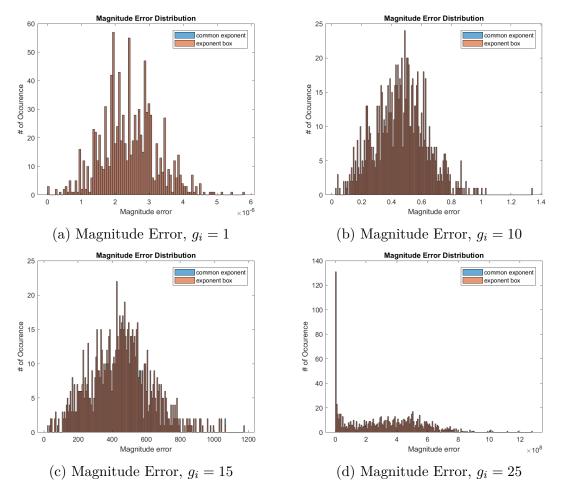

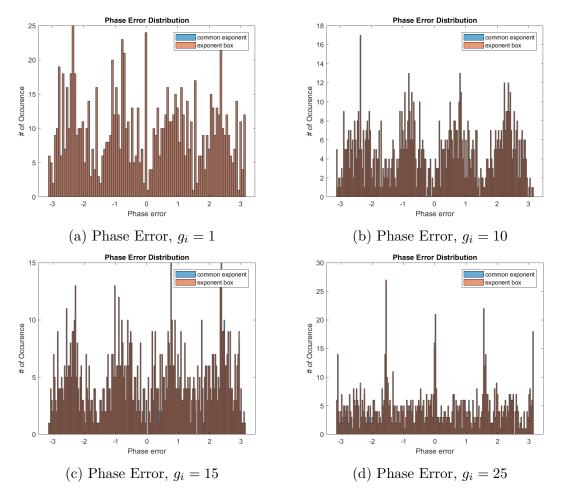

| Plots of Magnitude Error Distribution of Complex Block Multiply                                                    | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Plots of Phase Error Distribution of Complex Block Multiply                                                        | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

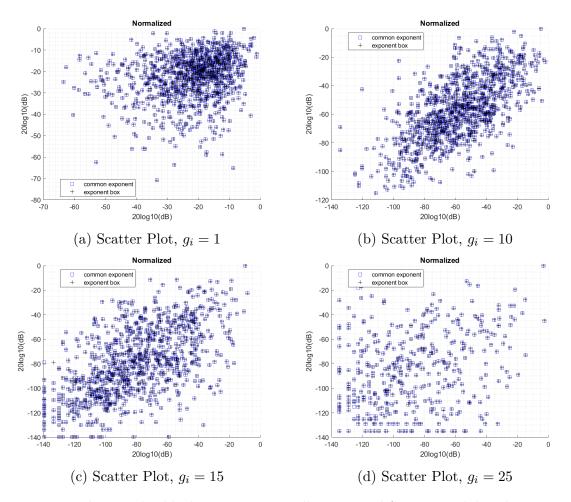

| Scatter Plots of Complex Block Multiply Output                                                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

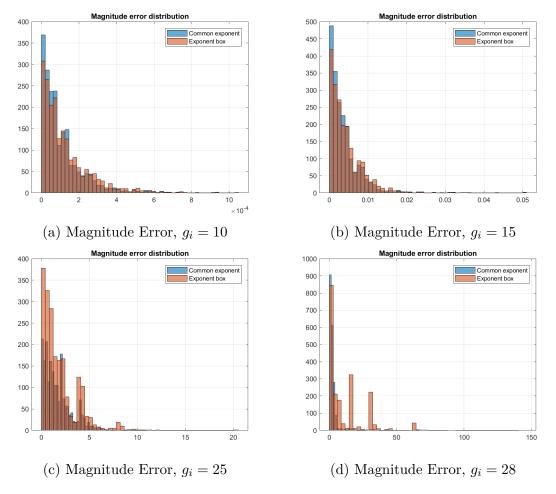

| Plots of Magnitude Error Distribution of 4-point FFT                                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

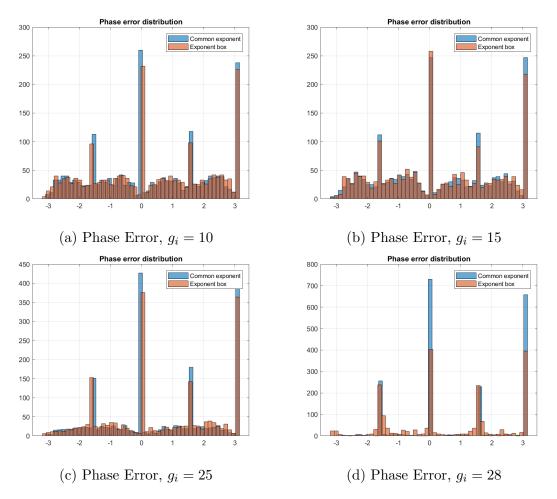

| Plots of Phase Error Distribution of 4-point FFT                                                                   | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Complete Plash Addition Plash Dismon (i) Pash Output                                                               | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

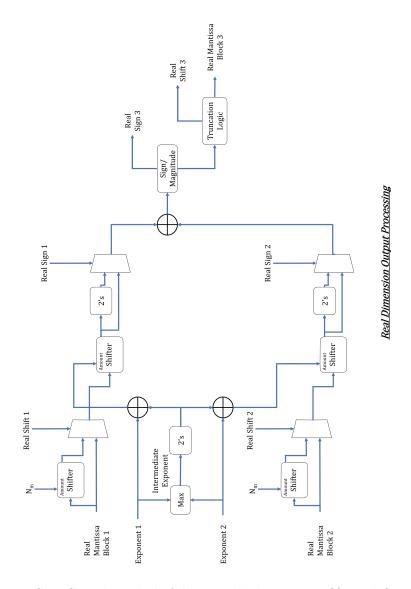

| Complex Block Addition Block Diagram (i) Real Output                                                               | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

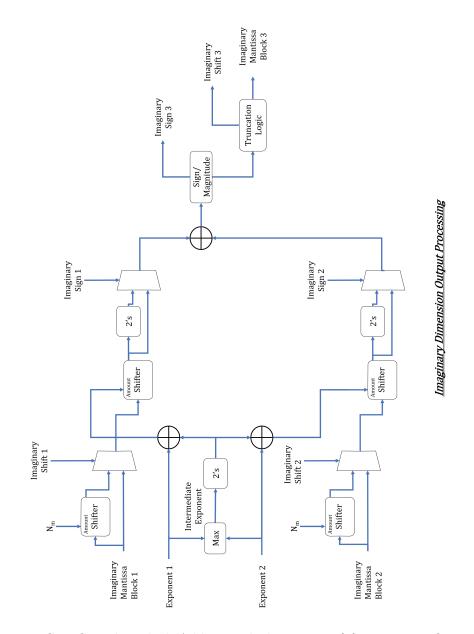

| Complex Block Addition Block Diagram (i) Real Output<br>Complex Block Addition Block Diagram (ii) Imaginary Output | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

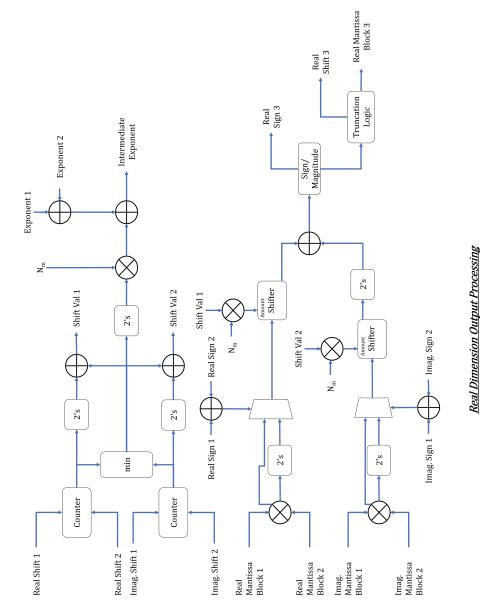

|                                                                                                                    | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

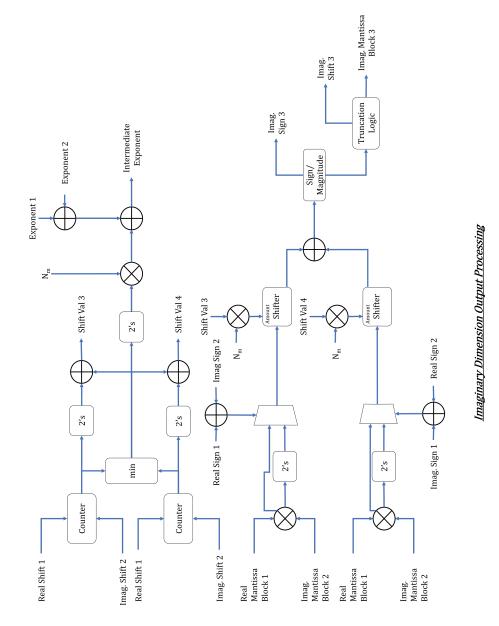

|                                                                                                                    | Block Diagram of Radix-2 4-point FFT         Bit Packing of Radix-2 4-point FFT         Block Diagram of Radix-4 4-point FFT         Plot of Phase Resolution         Plot of Phase Resolution         Plot of 256-QAM Normalized Constellation         Block Diagram of Complex Baseband QAM Transmitter         Block Diagram of Complex Baseband QAM Receiver         Block Diagram of OFDM Transmitter         Block Diagram of OFDM Receiver         Block Diagram of OFDM Receiver         Slock Diagram of OFDM Receiver         Stater Plots of Magnitude Error Distribution of Complex Block Multiply         Scatter Plots of Complex Block Multiply Output         Plots of Magnitude Error Distribution of 4-point FFT         Plots of Phase Error Distribution of 4-point FFT         Plots of Magnitude Error Distribution of 4-point FFT |

### Chapter 1

# Implementation of Digital Communication Systems

### 1.1 Digital Communication Systems Brief

The digital communication systems take various forms. The basic unit of information is a logical bit of a "0" or "1" and the rate of information transfer is measured in terms of bits/s. Multiple fixed-length bits are grouped into a symbol. Each symbol is mapped to a unique symbol amplitude and the symbol amplitudes are converted into a continuous-time analog baseband (low frequency) signal. The baseband signal is then upconverted to a carrier frequency for bandpass transmission. Figure 1.1 shows the block diagram for simple communication systems with abstraction on transmitter baseband processing (TX BB), upconversion unit, channel model, downconversion unit, and receiver baseband processing (RX BB).

Figure 1.1: Block Diagram of Simple Communication Systems

Any communication system would be restricted to occupying finite bandwidth for information transfer. The modulating signal has its fundamental frequency at the center of the transmission frequency band. Baseband modulation allows onedimension baseband symbol be modulated on the modulating signal. Amplitude modulation allows information be encoded as symbols with varying amplitude. Phase shift keying allows symbols to be encoded in the phase of a carrier signal. The combination of amplitude and phase modulation is a common way to use the transmission frequency band efficiently. The combination of amplitude and phase modulation leads to the study of complex baseband modulation or quadrature amplitude modulation (QAM).

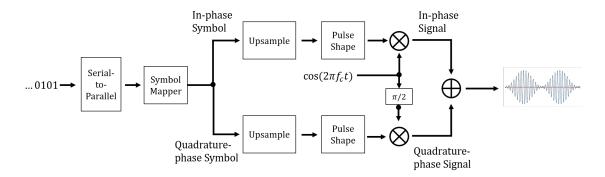

Figure 1.2 shows the block diagram of transmitter baseband signal processing for quadrature amplitude modulation (QAM). QAM is preferred for high data rates since it effectively increases the data rate by 2x for the same transmission bandwidth and signal-to-noise ratio (SNR) condition. Information is carried independently on two parallel streams of amplitude symbols known as In-phase and Quadrature-phase signals. Both In-phase and Quadrature-phase signals share a common oscillator circuitry and therefore sharing the same transmission band centered at the intermediate frequency,  $f_{im}$ , but the Quadrature-phase signals have phase offset of  $\frac{\pi}{2}$  relative to the In-phase signals. The pair of In-phase and Quadrature-phase signals is commonly known as complex IQ signals.

Figure 1.2: Block Diagram of Transmitter Baseband Processing

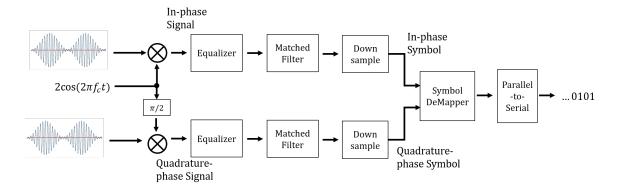

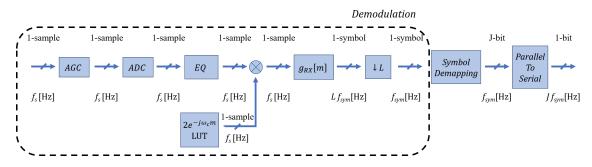

Figure 1.3 shows the block diagram of receiver baseband signal processing for quadrature amplitude modulation (QAM). The channel effect introduces signal distortion and degradation to the received signals and requires additional recovery work performed at the receiver. Often, the receiver would perform higher than Nyquist sampling rate to provide additional samples for running phase and timing offset correction algorithm. Furthermore, the channel equalization algorithm requires that the received data samples be available in a block for processing and higher throughput.

Figure 1.3: Block Diagram of Receiver Baseband Processing

The channel behavior determines the selection of modulation type. Singlecarrier modulation refers to shifting the baseband (low frequency) signal to be centered at a carrier frequency,  $f_c$ . Multi-carrier modulation refers to the composition of several narrowband signals in the baseband frequency region that each of them carries baseband symbol (Narrowband means that the transmission bandwidth is much smaller than the carrier frequency). More details on transmitter and receiver design in signal-carrier modulation and multi-carrier modulation are described in Section 4.1 and Section 4.2. For frequency flat fading channels, the receiver design would favor a simpler single-carrier modulation. For frequency selective channels, the receiver design would prefer multi-carrier modulation as the channel equalization can be performed on each subcarrier.

# 1.2 Hardware Design Constraints and Tradeoffs

Energy-efficient data representation in application specific baseband transceiver hardware are in demand resulting from energy costs involved in baseband signal processing [1]. In macrocell base stations, about ten percent of energy cost comes from digital signal processing (DSP) modules while power amplification and cooling processes consume more than 70% of total energy [2]. The energy consumption by DSP modules relative to power amplification and cooling will increase in future designs of small cell systems because low-powered cellular radio access nodes handle a shorter radio range [2]. The design of an energy-efficient number representation will reduce overall energy consumption in base stations.

The design choices for the digital radio transceiver subsystems are often made between the tradeoffs of hardware resources and system performance. The hardware resources may include the power, timing and memory requirement, while the system performance could be judged by quantitative measures such as power consumption, clocking frequency, processing bandwidth, supported numeric data types, processing delay, etc.

### **1.3 Digital Signal Processor Architecture**

One of the techniques for keeping the power consumption low is by limiting the clock frequencies. However, limiting the clock frequencies may not be the optimal tradeoff to make against the system performance. The clock frequencies are needed to provide sufficient sampling operations demanded by the software applications. Therefore, the power requirement correlates with the required clock frequencies and sampling frequencies at the analog-to-digital converters (ADC) and digital-toanalog converters (DAC).

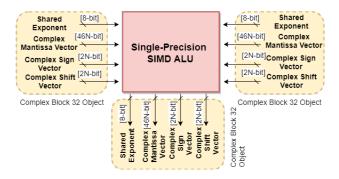

Several processor architectures such as SIMD and VLIW parallelism have been proposed to increase overall system performance at the cost of higher power consumption. With VLIW parallelism, several functional units could be initiated to operate on arithmetic operations, logic operations, or memory accesses independently to increase system throughput. With SIMD parallelism, the instruction overheads could be reduced by executing operation on a group of data of similar type. A slightly lower power consumption could be achieved by individually optimizing each of the frequently used functional units.

The floating-point processing unit is included to speed up the processing of scalar/vector floating-point data. The floating-point unit could occupy up to 40% - 50% of the total core area and could consume up to 50% - 60% of the available core power [3].

### **1.4 Data Converter Architecture**

The processor clock rate (cycle per second) is limiting the processor while memory bandwidth (bits per second) is limiting the interaction between processor, memory banks, and arithmetic processing module. Analog-to-digital converters (ADCs) generate discrete and quantized bits to represent the signal magnitude. Oversampling above the Nyquist rate at the data converter is often needed to ensure fidelity of the data signal. The resampling operation will often be needed and performed on the raw data bits when the processor runs on limited resources.

The main design choices of data converter would affect the power consumption, signal bandwidth, and effective number of bits. These parameters are tied together by a general measure of power efficiency of the data converter, namely the figure of merit (FoM). The Walden FoM measures the above quantities and generalizes the energy needed for each conversion step of least significant bit, [4]. The Schreier FoM includes the term dynamic range of the data converter, which is affected by the variable in-band noise power [5]. Extensive consideration of the ADC selection will require some insight on the impact of system design such as placement of anti-aliasing filter, out-of-band signal transmission, and signal leakage [6].

Suppose the passband waveform occupies bandwidth, W, centered at carrier frequency,  $f_c$ . The data converter unit would require sampling frequency to be at least,  $f_s > W$  since the baseband bandwidth is  $B = \frac{W}{2}$  and the Nyquist sampling criterion requires  $f_s \ge 2B$ .

# 1.5 Organization

This report is organized in the following format. Chapter 2 reviews the binary floating-point number format most commonly implemented in modern processor. The discussion of complex valued floating-point number format is natural extension that relates to modified floating-point format in prior arts.

Chapter 3 describes the main contribution of this work which focuses on proposed complex block floating-point representation that has acceptable implementation complexity and reduced error in complex block multiplication-based arithmetic. The proposed representation is shown to apply to implementation of fast Fourier transform algorithm in radix-2 and radix-4 format.

Chapter 4 focuses on the system model of communication systems design that features the proposed representation. The particular modulation systems in discussion are single-carrier and multi-carrier amplitude-based modulation which are commonly used in communication technology.

Chapter 5 shows the simulation results obtained from computations of complex block arithmetic and algorithms modeling. Chapter 6 draws on the conclusion and future work based on the design approach and simulation results of the proposed complex block floating-point representation.

# Chapter 2

#### Number Systems

# 2.1 IEEE-754 Floating-Point Format

#### 2.1.1 Binary Numeric Representation

The IEEE-754 Standards [7] specify a normalized number format that provides better numeric precision and larger range than a fixed-point number systems. Table 2.1 lists a number of supported floating-point number representation in the IEEE-754 Standards. Each supported wordlength is even integer multiple of a byte (8-bit).  $N_w$ -bit is defined as the wordlength of scalar floating-point number,  $N_s$  as the 1-bit Sign,  $N_e$  as the Exponent bit width, and  $N_m$  as the Mantissa bit width. The possible value of  $N_w$  is the sum of  $N_s + N_e + N_m$ . Figure 2.1 shows the bit packing of  $N_w$ -bit IEEE-754 real-valued number that would be in memory or in floating-point register.

| Components | Definition | Bit Widths, B         |

|------------|------------|-----------------------|

| Wordlength | $N_w$      | $\{16, 32, 64, 128\}$ |

| Sign       | $N_s$      | $\{1, 1, 1, 1\}$      |

| Exponent   | $N_e$      | $\{5, 8, 11, 15\}$    |

| Mantissa   | $N_m$      | $\{10, 23, 52, 112\}$ |

Table 2.1: Definition & bit widths of IEEE-754 Format [7] listing half-precision (16-bit), single-precision (32-bit), double precision (64-bit), and quad precision (128-bit). The wordlength is obtained by summing the sign, exponent, and mantissa bits.

| Bits | N <sub>s</sub> | N <sub>e</sub> | N <sub>m</sub> |  |

|------|----------------|----------------|----------------|--|

|      | Sign           | Exponent       | Mantissa       |  |

Figure 2.1: Typical bit packing of IEEE-754 format.

The Mantissa bits are interpreted as the fractional value  $(1.0000 \le x < 2.0000)$ and represent the most significant figures of a number. The IEEE-754 Standards require the normalized result to have a leading bit of 1. The leading bit of 1 is not coded and would be located before the radix-2 point of the Mantissa bits. The Exponent bits are adjusted in the process of normalization and serve as a Base-2 integer/fractional multiplier that controls the magnitude of a number.

To represent numbers that are out of range, the IEEE-754 Standards have specified a few unique sequence. With the Exponent bits set to all ones and the Mantissa bits set to all zeros, the  $+\infty$  and  $-\infty$  are represented depending on the Sign bit. With the Exponent bits set to all ones and the Mantissa bits set to any non-zeros, Not a Number (NaN) is represented. To represent an exact 0.0, the Exponent bits are set to all zeros and the Mantissa bits are set to all zeros. The Sign bit of 0 determines +0.0 and the Sign bit of 1 determines -0.0.

There are several quantitative measures that determine the effectiveness and show the limitation of this number format. The numeric range is defined as the most negative and the most positive values that can be represented. The numeric precision is defined as the smallest mantissa increment that affects the resultant mantissa value in addition/subtraction with a value of 1.0. The effective dynamic range, D, is calculated as the ratio of numeric range to numeric precision,  $D = 20log(\frac{numeric \ range}{precision})$ . With a specific signal-to-noise ratio requirement in an application, the effective dynamic range would be a useful metric to compare and select from the IEEE-754 format and non-IEEE-754 format.

## 2.1.2 Implementation Complexity

The IEEE-754 Standards also specify the exception handling requirement of invalid operation, division by zero, overflow and underflow. Algorithms that consist of heavy multiplication and addition operations of two large numbers or two small numbers are likely to incur overflow or underflow exceptions. To conform with the standards, additional circuitry is needed to perform exception handling.

The two common arithmetic operations involved in signal processing are addition and multiplication. All arithmetic operations that operate on two floating-point numbers require internal rescaling of mantissa and exponent bits.

For the addition operation, the Exponent bits must be compared and the leading hidden bit of one before the Mantissa bit is recovered. If the Exponent bits are not equal, then the smaller Exponent value would be increased by one and the Mantissa value would be divided by two. This process repeats until both Exponent values are equal. Fixed-point addition is applied on the Mantissa bits to give an intermediate Mantissa. There will be tradeoff made between the delay and gate cost involved in the fixed-point addition algorithm. For example, with a carry skip adder algorithm, the delay of the Mantissa bits addition result can be reduced to  $O(\sqrt{N_m + 1})$  at the gate cost of  $O(N_m)$ . The intermediate Mantissa bits would be normalized to give a leading bit of one, increasing/decreasing the value of Exponent bits in the process.

For the multiplication operation, the pre-processing of Exponent and Mantissa bits is less complex. The leading 1s of Mantissa bits are first recovered. Fixed-point multiplication is applied to the Mantissa bits and fixed-point addition is applied to the Exponent bits. For example, with the Dadda reduction technique, the complexity of the Mantissa bits multiplication operation can be reduced to approximately  $O(log_{1.45}(N_m+1))$  stages to use  $O(2(N_m))$  carry lookahead adder,  $O(N_m^2)$  full adders, and  $O(N^{1.5})$  half adders. The delay would account for  $O(log_{1.45}(N_m))$  stages of full adder delays and  $O(log_r(N_m))$  carry lookahead adder delay. For example, with carry skip adder algorithm, the delay of the Exponent bits addition result can be reduced to  $O(\sqrt{N_e})$  at the gate cost of  $O(N_e)$ . The intermediate Mantissa bits would also undergo normalization process to give leading bit of one and affect the value of the Exponent.

Both floating-point addition and multiplication require normalization of the intermediate Mantissa and Exponent to produce the final result. The floating-point addition requires two pre-scaling of input Mantissa and Exponent bits, but only involves one fixed-point addition of the Mantissas. Floating-point multiplication does not require pre-scaling of input Mantissa or Exponent bits, but this involves two operations: one fixed-point addition of Exponents and one fixed-point multiplication of Mantissas.

The selection of addition and multiplication algorithms will depend on the actual bit width of  $N_e$  for arithmetic on the Exponents and  $N_m$  for arithmetic on the Mantissas. That is because certain algorithms may provide speedup for particular bit widths, i.e., root of a number, even numbers, or odd numbers. With the IEEE-754 Standard, the half-precision format has an odd number of Exponent bits and (Mantissa + 1) bits, the single-precision format has an even number of Exponent bits and (Mantissa + 1) bits, the double-precision format has an odd number of Exponent bits and (Mantissa + 1) bits, the double-precision format has an odd number of Exponent bits and (Mantissa + 1) bits, the double-precision format has an odd number of Exponent bits and (Mantissa + 1) bits, and the quad-precision format has an odd number of a gorithms are not optimized based on the number of input bits, then the input bits are not fully utilized in the arithmetic operations.

In any arithmetic operations that potentially change the output values of Mantissas, the Mantissas of the result will undergo a stage of re-normalization and the Exponent will increment or decrement correspondingly.

#### 2.1.3 Complex-valued Representation

Each complex number can be thought of as two orthogonal real numbers in a Cartesian coordinate system. The arithmetic operations are defined in complex number domain. Each complex number addition can be realized by performing two real number additions. Each complex number multiplication can be realized by performing four real number multiplications and two real number additions. With simple extension of IEEE-754 format from one real value dimension to two real values dimension, a complex floating-point number can be simply coded as a pair of floating-point numbers with similar bit widths and precision. This would allow hardware reuse or easy replication of hardware units. Figure 2.2 shows the bit packing of a complex IEEE-754 number that would require  $2N_w$ -bits in memory or in floating-point register where  $N_w$  is the scalar floating-point bit width.

| Bits  | N <sub>s</sub> | N <sub>e</sub> | N <sub>m</sub> |

|-------|----------------|----------------|----------------|

| Real  | Sign           | Exponent       | Mantissa       |

| Imag. | Sign           | Exponent       | Mantissa       |

Figure 2.2: Typical bit packing of complex floating-point in IEEE-754 precision. Each real/imaginary dimension has the IEEE-754 precision.

#### 2.2 Complex Block Floating-Point Format

While information is rarely contained in just a scalar real/complex number, the IEEE-754 numeric representation is often used to represent an array of real/complex

numbers. Suppose  $N_v$  is the number of complex samples in an array, Figure 2.3 shows the bit packing of an array of complex IEEE-754 numbers that would require  $2N_vN_w$ -bits in memory or in vector floating-point register.

| N <sub>v</sub>         | N <sub>s</sub> | N <sub>e</sub> | N <sub>m</sub> |

|------------------------|----------------|----------------|----------------|

| 1 <sup>st</sup> Real   | Sign           | Exponent       | Mantissa       |

| 1 <sup>st</sup> Imag.  | Sign           | Exponent       | Mantissa       |

| 2 <sup>nd</sup> Real   | Sign           | Exponent       | Mantissa       |

| $2^{nd}$ Imag.         | Sign           | Exponent       | Mantissa       |

|                        |                |                |                |

| $(N_v - 1)^{th}$ Real  | Sign           | Exponent       | Mantissa       |

| $(N_v - 1)^{th}$ Imag. | Sign           | Exponent       | Mantissa       |

| $N_{v}^{th}$ Real      | Sign           | Exponent       | Mantissa       |

| $N_v^{th}$ Imag.       | Sign           | Exponent       | Mantissa       |

Figure 2.3: Typical vector form bit packing of IEEE-754 complex block. Each complex sample has twice the IEEE-754 precision.

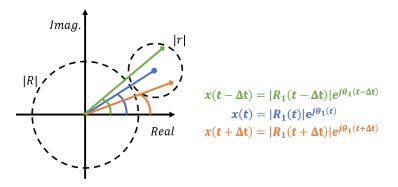

The complex block floating-point format is preferred for the purpose of improving both the throughput and latency of obtaining the block arithmetic results and reducing the area and implementation complexity of block arithmetic units. Suppose the information encoded in a complex block has continuity in magnitude/phase, a complex block floating-point format can be designed that reduces the wordlength requirements. The idea of coherence in magnitude or phase is shown in Figure 2.4.

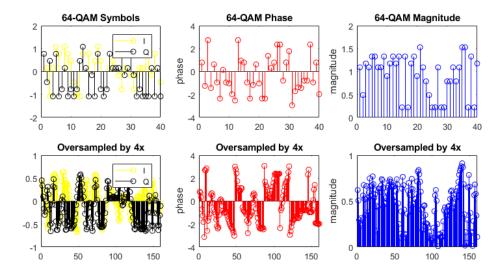

The discrete samples within in a time window may locate within a region or boundary on a complex value plane. A practical example that shows coherence in magnitude and phase is the randomly generated 64-QAM symbols oversampled by 4x above the Nyquist rate in Figure 2.5. With oversampling condition, this shows that any time-delayed samples generated by the same data converter source would have the characteristic of coherence in magnitude and phase.

The tradeoff associated with reducing the wordlength maybe the reduced mag-

Figure 2.4: Multiple discrete-time complex samples on the scatter plot of real/imaginary dimension. The smaller dotted circle enclosed complex samples that may have coherence in both magnitude and phase due to high sampling rate.

nitude/phase resolution in the polar representation. A more memory efficient complex block format could be designed such that the bits allocation are used to encode the magnitude or phase difference in a complex block floating-point number instead of the absolute magnitude/phase value of each complex number in the block.

In hardware design, the data converter converts continuous-time input signals and generates digital amplitude representations at uniformly spaced time intervals. Data converter design on this complex block floating-point format will be described in detail.

## 2.2.1 Common Exponent Encoding

The concept of common exponent encoding is shown in scalar complex floatingpoint representation in [8] and block floating-point representation in [9]. The authors in [8] target an improvement on IEEE-754 16-bit half-precision and show a complex floating-point representation that requires 29-bits and achieves 3-bit effective savings. The 3-bit savings is achieved by saving one of the 5-bit Exponent ( $N_e$ )-bit while reusing 2-bits for explicitly encoding the leading bit of "1" or "0" for re-normalized

Figure 2.5: [Top row, from the left to right] The in-phase/quadrature-phase (IQ) waveform consists of 64-QAM symbols in 40 symbols length. The phase and magnitude plots of the IQ waveform of 64-QAM symbols show little phase coherence and more magnitude coherence. [Bottom row, from the left to right] The 4x oversampled waveform of the 64-QAM symbols in 160 samples length. The phase and magnitude plots of the upsampled waveform show the most phase and magnitude coherence.

numbers. The Mantissas are 11-bit  $(N_m+1)$ -bit and all coded. The authors also report ASIC silicon footprint of arithmetic units (adder, multiplier) are larger by 10% and registers and memories footprint are smaller by 10% in its VLSI implementation. The performance loss reported varies between 0.2 dB in low SNR and 2 dB in high SNR cases.

The authors in [9] emulate the block floating-point algorithm on a fixed-point digital signal processor for a fast Fourier Transform arithmetic unit. The authors implement a 64-point FFT through radix-4 1st stage and radix-2 subsequent stages in the block floating-point format. The authors report an error measurement better than fixed-point FFT, which is expected. However, the more helpful piece of error measurement should be documented relative to purely floating-point FFT output accuracy. There is no mention of floating-point precision nor IEEE-754 relevance.

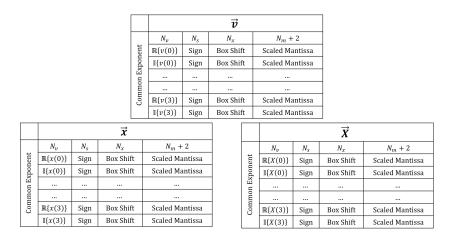

Table 2.2 shows the wordlength required for  $N_v$  complex samples per block in common exponent encoding method. Figure 2.6 shows the bit packing of  $N_v$ complex samples in an array that is in memory or in vector floating-point register. The behavior of the common exponent encoding in a complex block format would have a somewhat similar behavior as polar representation of complex number encoding, although not exactly, in terms of bit allocation. The most significant sample in terms of magnitude, either the real part or the imaginary part would get the full bit representation,  $(N_m + 1 + 2^{N_e})$ -bits in fixed-point equivalent precision, without any quantization loss relative to the IEEE-754 format. All other samples would only get partial bit representation,  $(N_m + 1 - 2^{\Delta N_e})$ -bits in fixed-point equivalent precision. The smaller complex values in the block reduces the mantissa precision since the process of re-normalizing to a common exponent in the block introduces more leading zero bits.

| Components      | Definition | Bit Widths, B                                        |

|-----------------|------------|------------------------------------------------------|

| Wordlength      | $N_w$      | $\{5, 8, 11, 15\} + (2 * N_v) * \{12, 25, 54, 114\}$ |

| Common Exponent | $N_e$      | $\{5, 8, 11, 15\}$                                   |

| Sign            | $N_s$      | $\{1, 1, 1, 1\}$                                     |

| Mantissa        | $N_m$      | $\{11, 24, 53, 113\}$                                |

Table 2.2: Definition & bit widths of common exponent encoding assuming block size of  $N_v$  complex samples per block. The wordlength is obtained by summing a common exponent,  $2N_v$  times sign and mantissa bits. The mantissa bit is one bit wider than IEEE-754 format to ensure the dominant value has same IEEE-754 precision.

Figure 2.7 describes the algorithm used in conversion of complex block format, assuming that IEEE-754 format is first available. Essentially, the common exponent encoding technique applied to complex block floating-point format allows sharing of the common exponent in a block of complex-valued data. The mantissa pairs are re-normalized to the value of the common exponent after the leading bit is recovered.

| N <sub>e</sub>     | Nv                     | N <sub>s</sub> | $N_m + 1$       |

|--------------------|------------------------|----------------|-----------------|

|                    | 1 <sup>st</sup> Real   | Sign           | Scaled Mantissa |

|                    | 1 <sup>st</sup> Imag.  | Sign           | Scaled Mantissa |

|                    | 2 <sup>nd</sup> Real   | Sign           | Scaled Mantissa |

| ~                  | 2 <sup>nd</sup> Imag.  | Sign           | Scaled Mantissa |

| Common<br>Exponent |                        |                |                 |

| Exponent           | $(N_v - 1)^{th}$ Real  | Sign           | Scaled Mantissa |

|                    | $(N_v - 1)^{th}$ Imag. | Sign           | Scaled Mantissa |

|                    | $N_{v}^{th}$ Real      | Sign           | Scaled Mantissa |

|                    | $N_v^{th}$ Imag.       | Sign           | Scaled Mantissa |

Figure 2.6: Typical vector form bit packing of common exponent format complex block. The common exponent applies to all complex samples in the block.

Each of the complex pair would trade the exponent bits with 1-bit leading bit for more memory storage space. Although being memory efficient, the digital representation would have weaker encoding of phase resolution in each of the complex pair in the block. The maximum allowed exponent difference without huge quantization error under the common exponent encoding is derived in Appendix A. The mantissas of either the real part or the imaginary part could be reduced to zeros as a result of large phase difference in a complex sample. It is also possible that the mantissas of smaller value complex samples in a block be reduced to all zeros as a result of large magnitude difference across multiple complex samples.

The amount of bit savings in terms of percentage depends on the number of bits per floating-point number and the block size. Common exponent encoding would achieve the highest amount of savings for half-precision floating-point number and smallest amount of savings for quad-precision floating-point number. This is due to the averaging effect by the exponentially growing word size in the IEEE-754 table. Table 2.3 lists the expected bit savings for varying IEEE-754 precision numbers with 64 complex samples per block.

#### **Conversion to Common Exponent Encoding**

| Step 1: | $E_{common} = \max\{Real(\vec{E}), Imag(\vec{E})\}$                               |

|---------|-----------------------------------------------------------------------------------|

| Step 2: | $\Delta \operatorname{Real}(\vec{E}) = E_{common} - \operatorname{Real}(\vec{E})$ |

|         | $\Delta Imag(\vec{E}) = E_{common} - Imag(\vec{E})$                               |

| Step 3: | $Real(\vec{M}) = Real(1, \vec{M}) \gg \Delta Real(\vec{E})$                       |

|         | $Imag(\vec{M}) = Imag(1, \vec{M}) \gg \Delta Imag(\vec{E})$                       |

| Step 4: | Done                                                                              |

Figure 2.7: The algorithm assumes IEEE-754 format is first available and consists of four main steps. Step 1 identifies the common exponent. Step 2 identifies the amount of right shifting on the mantissa which is the difference between common exponent and original real/imaginary exponents. Step 3 recovers the leading 1 bit of real/imaginary mantissa and performs appropriate right shifting. Step 4 completes the conversion.

| IEEE-754 | # of Exponent Saved | # of Traded | # Overall Saved Per Block / $\%$ |

|----------|---------------------|-------------|----------------------------------|

| 16-bit   | 5-bit               | 2-bit       | (3+8*63)-bit / 24.76%            |

| 32-bit   | 8-bit               | 2-bit       | (6+14*63)-bit / 21.68%           |

| 64-bit   | 11-bit              | 2-bit       | (9+20*63)-bit / 15.49%           |

| 128-bit  | 15-bit              | 2-bit       | (13+28*63)-bit / $10.85%$        |

Table 2.3: The expected bit savings in memory and register for common exponent format. With block size of 64 complex samples per block, the bit savings range between 10.85% and 24.76% depending on the chosen IEEE-754 precision.

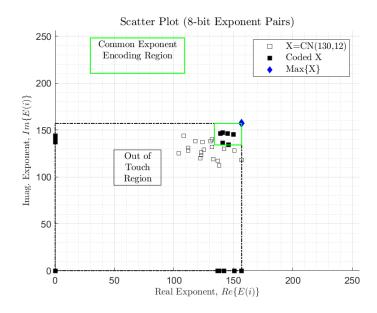

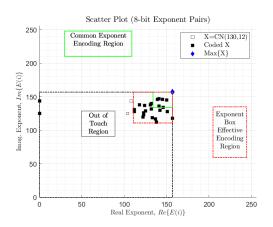

The effective encoding region is defined as a square of size  $(N_m \times N_m)$  with the chosen common exponent at the top right corner. The out of touch region floats next to the effective encoding region and bounded by the real-axis and imaginary axis. The out of touch region contains all complex exponent pairs in which the corresponding IEEE-754 mantissa are potentially zeroed as a result of aggressive rescaling. The union of the effective encoding region and the out of touch region forms a subset of the entire encoding space  $(2^{N_m} \times 2^{N_m})$  of the IEEE-754 format as shown in Figure 2.8.

The effective encoding region is labeled  $(\Box)$  in Figure 2.8 and encloses only

Figure 2.8: The unfilled rectangle symbols indicate the original real/imaginary exponent pairs. The dark rectangle symbols indicate coded exponent pairs. The largest exponent value is selected to be the common exponent at the top right corner of the effective encoding region. The size of effective encoding region is the square of the mantissa bit width,  $N_m + 1$ . Any complex exponent pairs that fall outside the effective encoding region will have the corresponding mantissa values coded as zeroes. The possible locations of coded exponent pairs are within the effective encoding region, on the x-axis, y-axis, and at the origin.

a fraction of the 25 normally distributed complex valued exponent pairs with mean of 130 and variance of 12. The empty rectangular white box symbols indicate complex exponent pairs in separate exponents encoding. The solid rectangular filled box symbols indicate complex exponent pairs in common exponent encoding. The coded complex exponent pairs that fall on either y-axis, x-axis, or origin imply that one or both of real/imaginary mantissa values are coded as zeros.

The accuracy of the complex block arithmetic (adder, multiplier, matrix operations) would rely on each mantissa values in the complex block format. The common exponent encoding is expected to have higher quantization error in the complex block format and block arithmetic output since the performance of the complex block representation is data dependent.

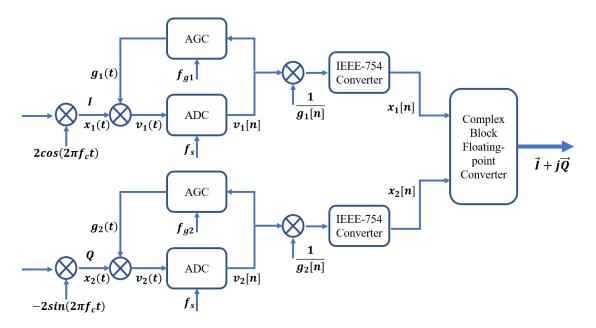

# 2.2.2 Conversion with Two Parallel ADCs

Figure 2.9 describes a block diagram with two parallel data converters that are assumed to sample in time and provide digital representation of two stream of numbers in fixed-point format, namely the real and imaginary dimension of complex numbers. The automatic gain control applies gain on the analog inputs prior to the data converter with the feedback information on the quantized output of the data converter. The data converter output passes fixed-point number to convert into higher precision floating-point number. The parallel stream of real and imaginary floating-point numbers are combined to generate complex floating-point number in a block. To benefit from memory efficient storage such as common exponent encoding, a 2nd stage of number conversion is needed.

Figure 2.9: Two analog-to-digital converters (ADCs) running in parallel generate the inphase/quadrature-phase waveforms. To convert to floating-point format, both ADCs work with separate automatic gain control (AGC) to maximize signal-to-quantization-noise ratio (SQNR). In this architecture, there is a need of second stage conversion to complex block floating-point format which applies the algorithm in Figure 2.7.

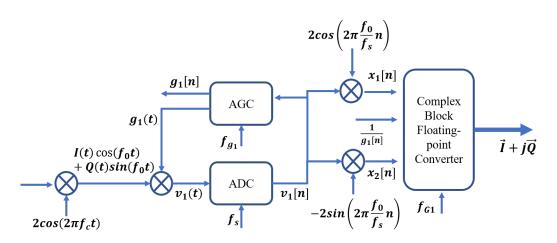

#### 2.2.3 Conversion with Single ADC