Copyright

by

Yousof Mortazavi

2015

# The Dissertation Committee for Yousof Mortazavi certifies that this is the approved version of the following dissertation:

## Analog-to-Digital Converter Circuit and System Design to Improve with CMOS Scaling

| Committee:                    |

|-------------------------------|

|                               |

| Brian L. Evans, Supervisor    |

| Arjang Hassibi, Co-Supervisor |

| Todd E. Humphreys             |

| Earl E. Swartzlander Jr.      |

| Ahmed H. Tewfik               |

## Analog-to-Digital Converter Circuit and System Design to Improve with CMOS Scaling

by

Yousof Mortazavi, B.S.; M.S.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2015$

## Acknowledgments

I wish to thank many people who have been a source of knowledge and inspiration to me through the years.

First and foremost, I would like to express my deepest gratitude to my advisor Prof. Brian L. Evans, who encouraged me to pursue post-graduate studies under his supervision, and guided and mentored me for my entire time at The University of Texas at Austin. Without his kindness and patience, I would not have been able to succeed.

Second, I would like to sincerely thank Dr. Arjang Hassibi, who gave me a chance to collaborate with him and his former student Dr. Woo Young Jung, and inspired us both to achieve something new, by thinking outside the box, across analog/digital boundaries.

I am also grateful to my committee members and professors: Prof. Todd E. Humphreys, Prof. Earl E. Swartzlander, and Prof. Ahmed H. Tewfik. In their classes, they have all taught me advanced topics and concepts that have directly or indirectly guided me throughout this dissertation. Their guidance and role on my doctoral committee is deeply appreciated.

As the person who first taught me about  $\Delta\Sigma$  ADCs, I am deeply indebted to Eric J. Swanson, who caught my interest in the field of  $\Delta\Sigma$  ADCs, gave me a deep understanding of such ADCs, and even mentored and supported me while he was at Cirrus Logic, Inc.. May he rest in peace.

I wish to express my gratitude to both my loving parents, who always supported and motivated me, as well as pushed me to limits I didn't know I could achieve. And finally, many thanks and appreciation to my wife Sebar, who has been very patient, loving, and understanding throughout the final years of my studies.

Analog-to-Digital Converter Circuit and System Design

to Improve with CMOS Scaling

Yousof Mortazavi, Ph.D.

The University of Texas at Austin, 2015

Supervisor:

Brian L. Evans

Co-Supervisor:

Arjang Hassibi

There is a need to rethink the design of analog/mixed-signal circuits to

be viable in state-of-the-art nanometer-scale CMOS processes due to the hos-

tile environment they create for analog circuits. Reduced supply voltages and

smaller capacitances are beneficial to circuit speed and digital circuit power

efficiency; however, these changes along with smaller dimensions and close

coupling of fast-switching digital circuits have made high-accuracy voltage-

domain analog processing increasingly difficult. In this work, techniques to

improve analog-to-digital converters (ADC) for nanometer-scale processes are

explored.

First, I propose a mostly-digital time-based oversampling delta-sigma

$(\Delta\Sigma)$  ADC architecture. This system uses time, rather than voltage, as the

analog variable for its quantizer, where the noise shaping process is realized

by modulating the width of a variable-width digital "pulse." The merits of

vii

this architecture render it not only viable to scaling, but also enable improved circuit performance with ever-increasing time resolution of scaled CMOS processes. This is in contrast to traditional voltage-based analog circuit design, whose performance generally decreases with scaling due to increasingly higher voltage uncertainty due to supply voltage reduction and short-channel effects.

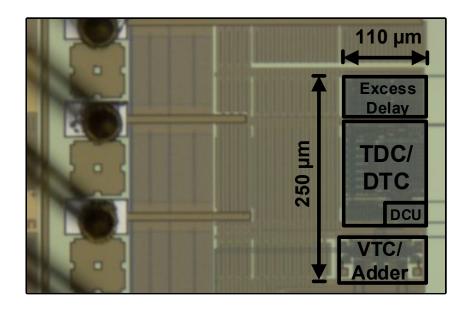

In conjunction with Dr. Woo Young Jung while he was a Ph.D. student at The University of Texas at Austin, two prototype implementations of the proposed architecture were designed and fabricated in TSMC 180 nm CMOS and IBM 45 nm Silicon-On-Insulator (SOI) process. The prototype ADCs demonstrate that the architecture can achieve bandwidths of 5-20 MHz and  $\sim$ 50 dB SNR with very small area. The first generation ADC core occupies an area of only 0.0275 mm<sup>2</sup>, while the second generation ADC core occupies 0.0192 mm<sup>2</sup>. The two prototypes can be categorized as some of the smallest-area modulators in the literature.

Second, I analyze the measured results of the prototype ADC chips, and determine the source for the harmonic distortion. I then demonstrate a digital calibration algorithm that sufficiently mitigates the distortion. This calibration approach falls in the general philosophy of digitally-assisted analog systems. In this philosophy, digital calibration and post-correction are favored over traditional analog solutions, in which there is a high cost to the analog solution either in complexity, power, or area.

## **Table of Contents**

| Ackno   | wledgments                                       | V   |

|---------|--------------------------------------------------|-----|

| Abstra  | act                                              | vi  |

| List of | Figures                                          | xii |

| Chapte  | er 1. Introduction                               | 1   |

| 1.1     | ADC Circuits Suited for Scaling                  | 4   |

|         | 1.1.1 Spectral Error Shaping                     | 4   |

|         | 1.1.2 Digitally-Enhanced Analog                  | 5   |

|         | 1.1.3 Time-Based Methods                         | 5   |

| 1.2     | Proposed Contributions                           | 6   |

| 1.3     | Organization                                     | 8   |

| 1.4     | Abbreviations                                    | S   |

| Chapte  | er 2. Background and Prior Work                  | 10  |

| 2.1     | Analog-to-Digital Conversion                     | 10  |

|         | 2.1.1 Sampling Theory                            | 11  |

|         | 2.1.2 Quantization                               | 12  |

| 2.2     | Delta-Sigma Modulation                           | 15  |

| 2.3     | Time-Based Signal Processing                     | 17  |

| 2.4     | Time-Based Delta Sigma ADCs                      | 20  |

| 2.5     | Summary                                          | 22  |

| Chapte  |                                                  | 23  |

| 3.1     | Introduction                                     | 23  |

| 3.2     | Time-Based $\Delta\Sigma$ Modulator Architecture | 24  |

|         | 3.2.1 Pulse Width Information Encoding           | 24  |

|         | 3.2.2 Time-Domain Addition and Subtraction       | 27  |

|        | 3.2.3  | Modulator Topology and System Modeling 29               |

|--------|--------|---------------------------------------------------------|

|        | 3.2.4  | Voltage-to-Time Converter/Adder                         |

|        | 3.2.5  | Time-to-Digital Converter/Digital-to-Time Converter 35  |

|        | 3.2.6  | Delay Control Unit                                      |

| 3.3    | Sumn   | nary                                                    |

| Chapte | er 4.  | Behavioral Modeling of Time-Based $\Delta\Sigma$ ADC 41 |

| 4.1    | Funct  | ional Model                                             |

|        | 4.1.1  | VTC/Adder Model                                         |

|        | 4.1.2  | Phase Detector Model                                    |

|        | 4.1.3  | TDC/DTC Model                                           |

|        | 4.1.4  | Excess Delay Model                                      |

|        | 4.1.5  | Simulation Results                                      |

| 4.2    | Mode   | ling Sources of Nonlinearity                            |

|        | 4.2.1  | Modeling DTC Element Mismatch                           |

|        | 4.2.2  | Modeling TDC Element Mismatch                           |

|        | 4.2.3  | Modeling VTC/Adder Nonlinearity                         |

| 4.3    | Sumn   | nary                                                    |

| Chapte | er 5.  | First Generation Chip 60                                |

| 5.1    | Introd | duction                                                 |

| 5.2    | Circu  | it Implementation                                       |

|        | 5.2.1  | VTC/Adder                                               |

|        | 5.2.2  | TDC/DTC                                                 |

|        | 5.2.3  | Delay Control Unit (DCU) 64                             |

|        | 5.2.4  | Complete ADC System                                     |

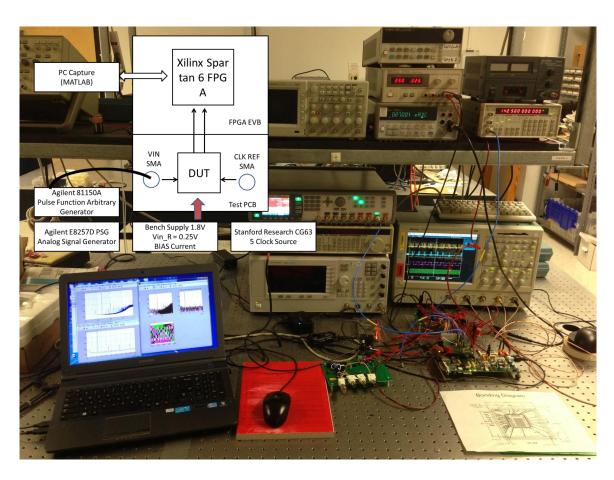

| 5.3    | Test a | and Measurement                                         |

|        | 5.3.1  | Test Methodology                                        |

|        | 5.3.2  | Die Photo                                               |

|        | 5.3.3  | Experimental Results                                    |

| 5.4    | Sumn   | 70                                                      |

| Chapter 6. |        | Second Generation Chip                   | 77  |

|------------|--------|------------------------------------------|-----|

| 6.1        | Intro  | duction                                  | 77  |

| 6.2        | Circu  | it Implementation                        | 77  |

|            | 6.2.1  | VTC/Adder                                | 78  |

|            | 6.2.2  | TDC/DTC                                  | 79  |

|            | 6.2.3  | Delay Control Unit (DCU)                 | 81  |

|            | 6.2.4  | Complete ADC System                      | 82  |

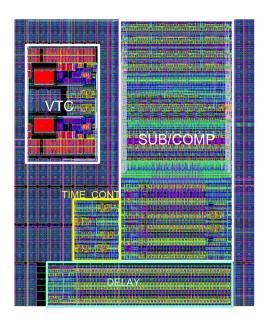

|            | 6.2.5  | Chip Layout                              | 82  |

| 6.3        | Test a | and Measurement                          | 84  |

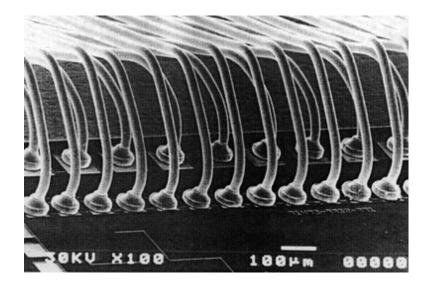

|            | 6.3.1  | Package Assembly and Wire Bonding        | 84  |

|            | 6.3.2  | Capture Printed Circuit Board Design     | 86  |

|            | 6.3.3  | Experimental Results                     | 88  |

| 6.4        | Sumn   | nary                                     | 93  |

| Chapt      | er 7.  | Nonlinear Circuit Linearization          | 94  |

| 7.1        | Intro  | duction                                  | 94  |

| 7.2        | DTC    | Mismatch Calibration                     | 95  |

|            | 7.2.1  | Calibration of the First Generation ADC  | 98  |

|            | 7.2.2  | Calibration of the Second Generation ADC | 105 |

| 7.3        | Impro  | oved Design For TDC/DTC                  | 105 |

| 7.4        | Sumn   | nary                                     | 109 |

| Chapt      | er 8.  | Conclusions and Future Work              | 110 |

| 8.1        | Sumn   | nary                                     | 110 |

| 8.2        | Contr  | ributions                                | 110 |

| 8.3        | Futur  | e Work                                   | 112 |

| Bibliog    | graphy | y                                        | 114 |

| Vita       |        |                                          | 121 |

## List of Figures

| 1.1 | A classification of techniques to improve scaling of analog integrated circuits in nanometer-scale CMOS processes                                                                                          | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Block diagram of a typical analog-to-digital converter                                                                                                                                                     | 11 |

| 2.2 | N=2-bit uniform quantizer function                                                                                                                                                                         | 12 |

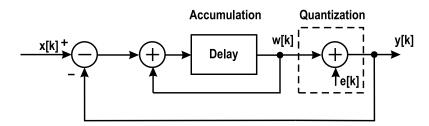

| 2.3 | First-order delta-sigma analog-to-digital converter                                                                                                                                                        | 14 |

| 2.4 | Sampled-data linear model of the analog portion of the first-order delta-sigma analog-to-digital converter shown in Fig. 2.3                                                                               | 14 |

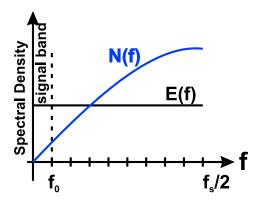

| 2.5 | Spectral density of noise from delta-sigma quantization                                                                                                                                                    | 16 |

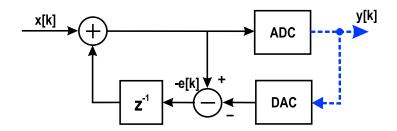

| 2.6 | Error feedback only delta-sigma modulator                                                                                                                                                                  | 17 |

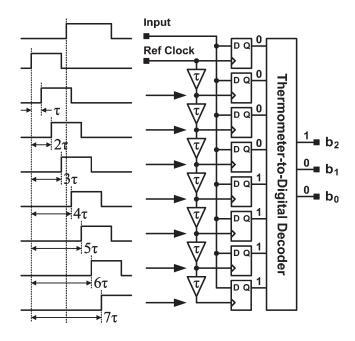

| 2.7 | A 3-bit flash time-to-digital converter                                                                                                                                                                    | 19 |

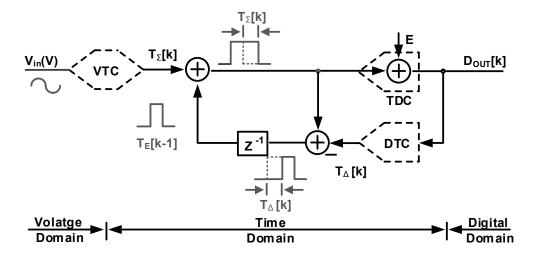

| 3.1 | $\Delta\Sigma$ modulator model showing boundaries of voltage/time/digital domain processing. VTC = voltage-to-time converter, TDC = time-to-digital converter, DTC = digital-to-time converter             | 25 |

| 3.2 | Definition of pulse and pseudo-differential (conceptual) pulse .                                                                                                                                           | 26 |

| 3.3 | (a) Addition and (b) subtraction in time-domain using pulse widths                                                                                                                                         | 28 |

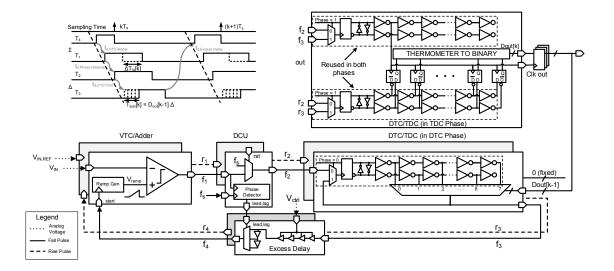

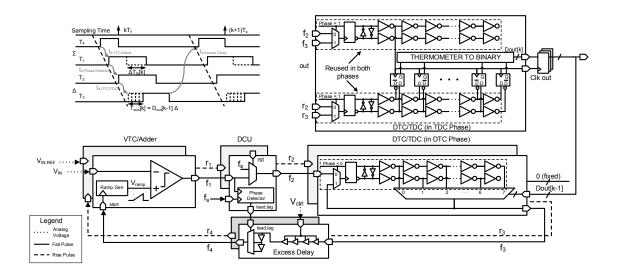

| 3.4 | (a) Architecture and (b) timing diagram of the time-based $\Delta\Sigma$ ADC. VTC = voltage-to-time converter, DCU = delay control unit, TDC = time-to-digital converter, DTC = digital-to-time converter. | 30 |

| 3.5 | Functional block diagram and timing diagram of the VTC/Adder.                                                                                                                                              |    |

|     |                                                                                                                                                                                                            | 33 |

| 3.6 | Functional block diagram of the TDC/DTC                                                                                                                                                                    | 35 |

| 4.1 | Top-Level Simulink Model of the proposed time-based $\Delta\Sigma$ ADC                                                                                                                                     | 42 |

| 4.2 | Simulink model for the VTC/Adder block of the proposed time-based $\Delta\Sigma$ ADC                                                                                                                       | 43 |

| 4.3 | Simulink model for the Phase Detector block of the proposed time-based $\Delta\Sigma$ ADC                                                                                                                  | 44 |

| 4.4  | Simulink model for the TDC/DTC block of the proposed time-based $\Delta\Sigma$ ADC                                                                                             | 45 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5  | Simulink model for the Excess Delay block of the proposed time-based $\Delta\Sigma$ ADC                                                                                        | 46 |

| 4.6  | Averaged FFT Spectrum of the behavioral model with DCU disabled. Odd harmonics are due to input-dependent modulation of sampling interval when the DCU is disabled             | 47 |

| 4.7  | Averaged FFT Spectrum of behavioral model with DCU enabled.                                                                                                                    | 48 |

| 4.8  | Waveforms for different signals in the behavioral model of the proposed time-based $\Delta\Sigma$ ADC                                                                          | 49 |

| 4.9  | Histograms for $\Delta T = t(f_{\text{out, phase detector}}) - k \cdot T_s$ showing the deviation from ideal sampling times $k \cdot T_s$ when the DCU is disabled/enabled     | 50 |

| 4.10 | Histogram for $\Delta T = t(f_{\text{out, phase detector}}) - k \cdot T_s$ showing the deviation from ideal sampling times $k \cdot T_s$ when the DCU is enabled               | 51 |

| 4.11 | Simulink model for TDC/DTC including the element mismatch for DTC/TDC phases                                                                                                   | 53 |

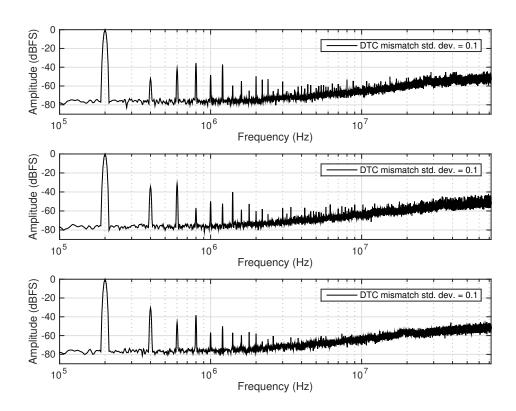

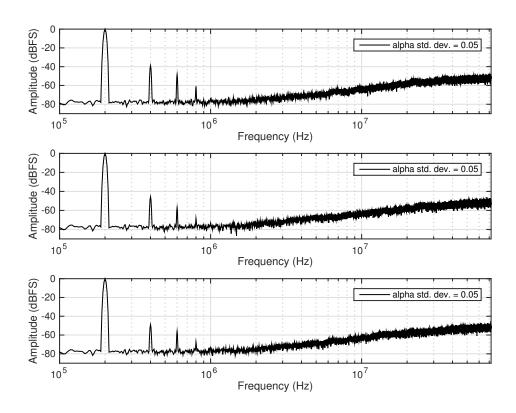

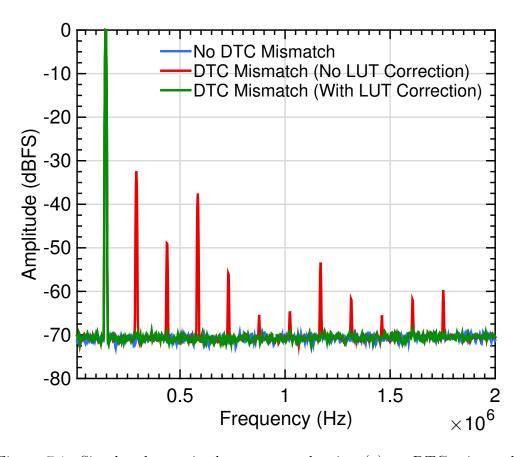

| 4.12 | Output spectrum showing the effect of DTC element mismatch with $\sigma=10\%$ for 3 different random mismatch vectors                                                          | 54 |

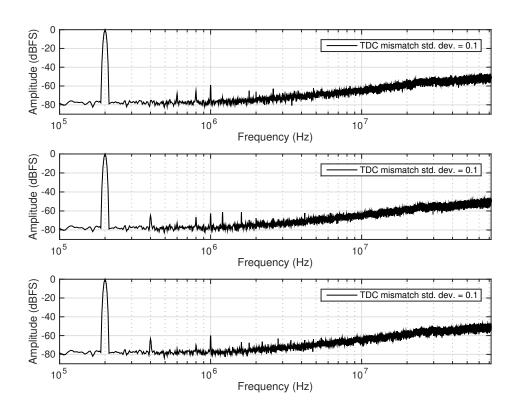

| 4.13 | Output spectrum showing the effect of TDC element mismatch with $\sigma=10\%$ for 3 different random mismatch vectors                                                          | 56 |

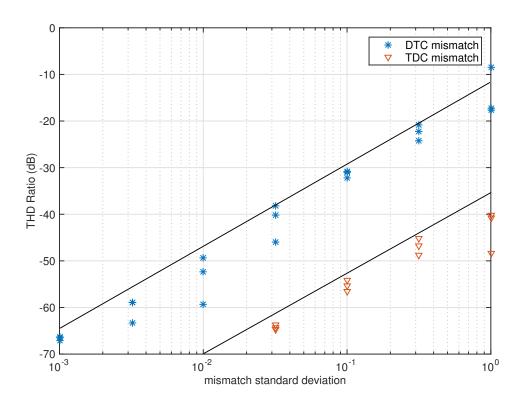

| 4.14 | Total Harmonic Distortion vs. $\sigma$ of DTC and TDC element mismatch. Note DTC mismatch results in more than 20 dB higher THD relative to TDC mismatch with comparable stan- |    |

|      | dard deviation                                                                                                                                                                 | 57 |

| 4.15 | Output spectrum showing the effect of VTC/Adder nonlinearity for 3 different random nonlinearity coefficient ( $\alpha$ ) vectors                                              | 58 |

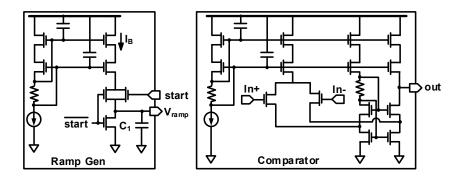

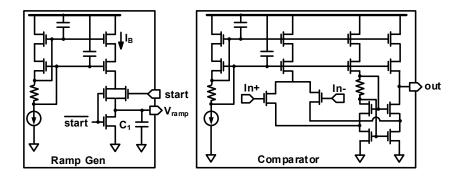

| 5.1  | VTC/Adder circuit showing ramp generator and comparator .                                                                                                                      | 62 |

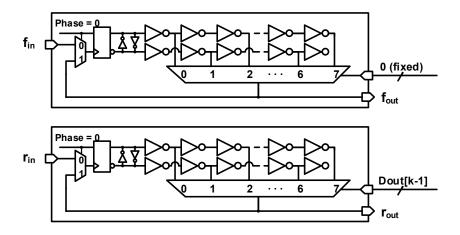

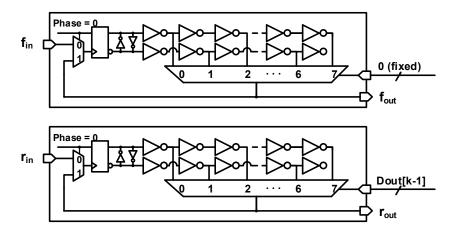

| 5.2  | Digital-to-time converter (DTC) phase (phase 0) of the DTC/TDC circuit. Output pulse is recirculated through the block a second time for the TDC operation (phase 1)           | 62 |

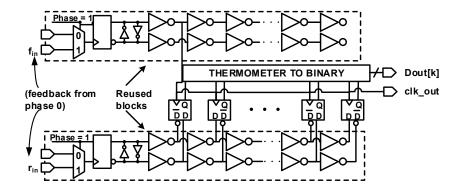

| 5.3  | Time-to-digital converter (TDC) phase (phase 1) of the DTC/TDC circuit. Note the reuse of the unit delay elements from the previous phase (DTC)                                | 64 |

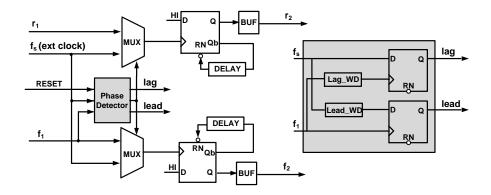

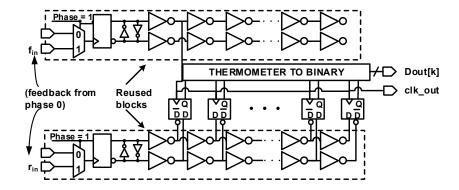

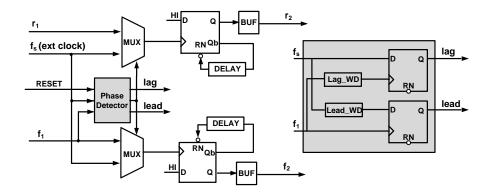

| 5.4  | Delay Control Unit, including phase detector                                                                                                                                   | 65 |

| 5.5  | Complete PWM-based $\Delta\Sigma$ ADC System                                                                                                                                   | 66 |

| J. J | Complete I fill bubba <u>—</u> I II C Dybtom                                                                                                                                   | 00 |

| 5.6  | Photo of the test setup                                                                                                                                              | 68 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.7  | Die photo of the first-generation prototype ADC                                                                                                                      | 69 |

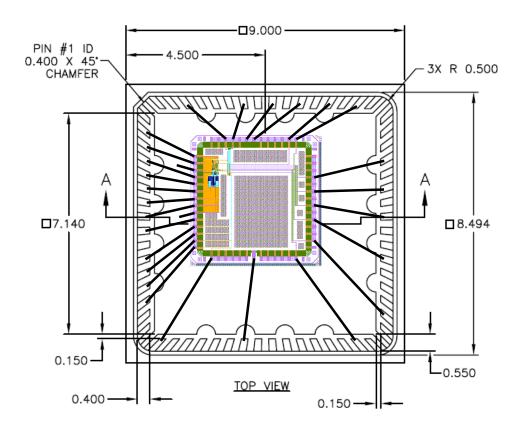

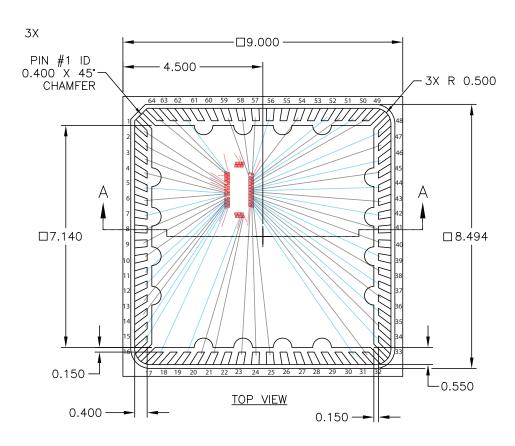

| 5.8  | Wirebonding diagram for the first-generation prototype ADC. Die is shown larger than the scale suggests. Die is 2 mm×2 mm, QFN-64 package is 9 mm×9 mm               | 70 |

| 5.9  | Time-domain waveform showing 1 cycle of a 146.1 kHz sine wave.                                                                                                       | 72 |

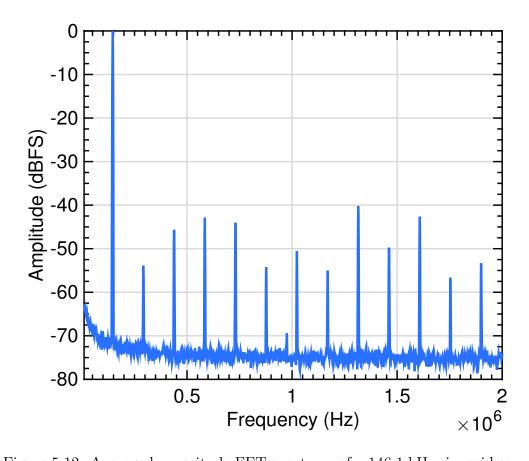

| 5.10 | Magnitude FFT spectrum of a 146.1 kHz sinusoid sampled with $f_s=144~\mathrm{MHz}$                                                                                   | 73 |

| 5.11 | Averaged magnitude FFT spectrum of a 146.1 kHz sinusoid sampled with $f_s=144~\mathrm{MHz}, N_{avg}=30~\ldots$                                                       | 74 |

| 5.12 | Averaged magnitude FFT spectrum of a 146.1 kHz sinusoid sampled with $f_s = 144$ MHz, OSR = 36, Showing DC to $\frac{f_s}{2 \cdot OSR}$ .                            | 75 |

| 6.1  | VTC/Adder circuit showing ramp generator and comparator .                                                                                                            | 79 |

| 6.2  | Digital-to-time converter (DTC) phase (phase 0) of the DTC/TDC circuit. Output pulse is recirculated through the block a second time for the TDC operation (phase 1) | 80 |

| 6.3  | Time-to-digital converter (TDC) phase (phase 1) of the DTC/TDC circuit. Note the reuse of the unit delay elements from the previous phase (DTC)                      | 81 |

| 6.4  | Delay Control Unit, including phase detector                                                                                                                         | 82 |

| 6.5  | Complete PWM-based $\Delta\Sigma$ ADC System                                                                                                                         | 83 |

| 6.6  | Core Layout                                                                                                                                                          | 83 |

| 6.7  | Example of a staggered wire bond [1]. Note the different heights and angles used to avoid other wires.                                                               | 86 |

| 6.8  | Wirebonding diagram for the second-generation prototype ADC. Die is 2 mm×1 mm, QFN-64 package is 9 mm×9 mm                                                           | 87 |

| 6.9  | Time-domain waveform showing 1 cycle of a $0.5~\mathrm{MHz}$ sine wave.                                                                                              | 89 |

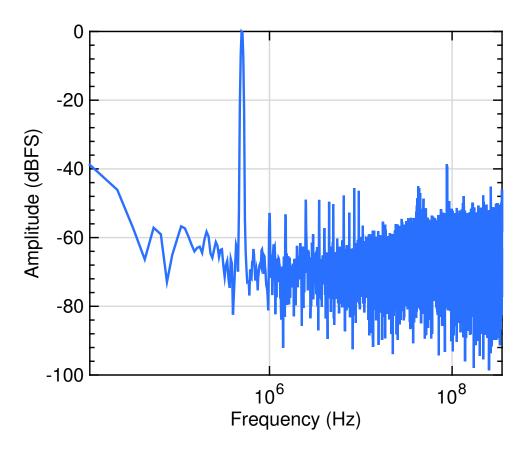

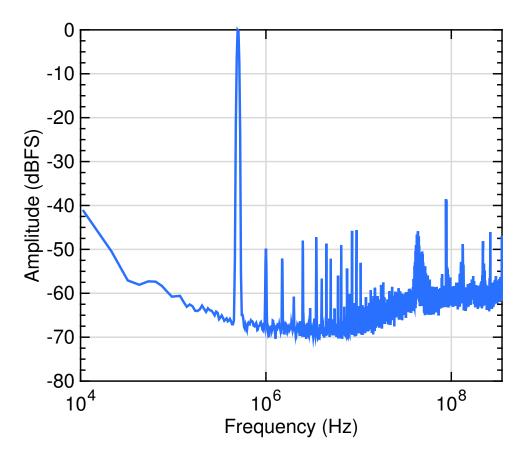

| 6.10 | Magnitude FFT spectrum of a 500 kHz sinusoid sampled with $f_s=705~\mathrm{MHz}$                                                                                     | 90 |

| 6.11 | Averaged Magnitude FFT spectrum of a 500 kHz sinusoid sampled with $f_s=705$ MHz, $N_{FFT}=64$ K, $N_{avg}=30$                                                       | 91 |

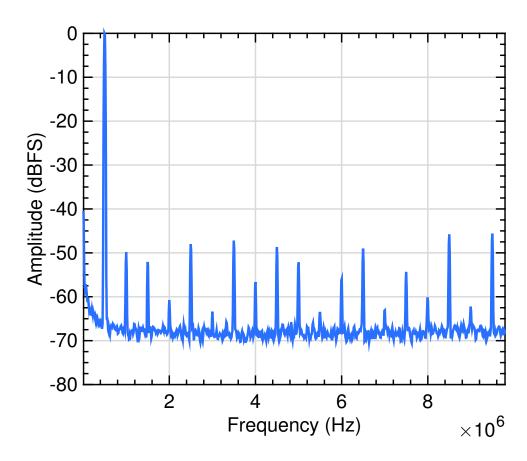

| 6.12 | Magnitude FFT spectrum of a 500 kHz sinusoid sampled with $f_s = 705$ MHz, OSR = 36, showing DC to $\frac{f_s}{2 \cdot OSR}$                                         | 92 |

| 7.1  | Simulated magnitude spectrum showing (a) no DTC mismatch, (b) DTC mismatch, and (c) DTC mismatch with LUT correction with perfect knowledge of $\epsilon[u]$         | 96 |

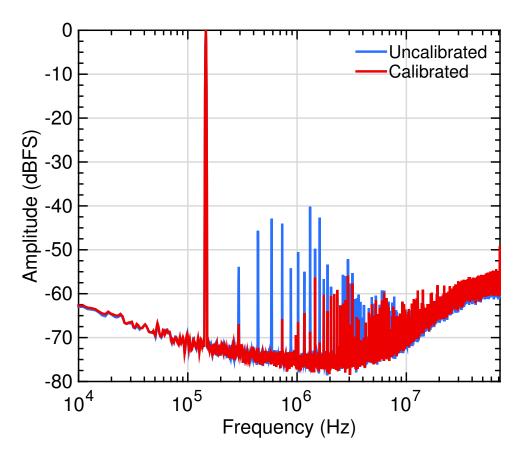

| 7.2 | Spectrum showing linearity improvement using the calibration algorithm for first generation chip measured data. Uncalibrated THD = $-34.5$ dB, calibrated THD = $-45.7$ dB. THD is improved by 11.2 dB for OSR = 14, BW = $5.14$ MHz                                             | 100 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.3 | Spectrum showing linearity improvement using the calibration algorithm for first generation chip measured data. Uncalibrated THD = $-34.5$ dB, calibrated THD = $-45.7$ dB. THD is improved by 11.2 dB for OSR = 14, BW = $5.14$ MHz                                             | 101 |

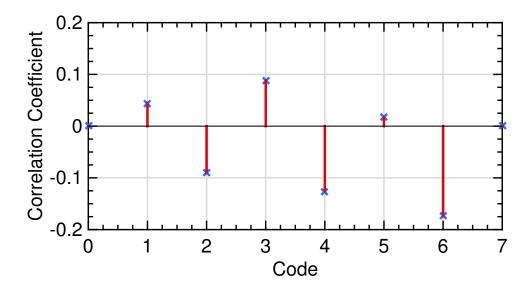

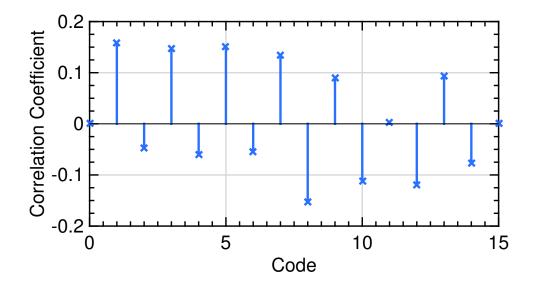

| 7.4 | Estimated mismatch coefficients for each code on measured first chip data                                                                                                                                                                                                        | 102 |

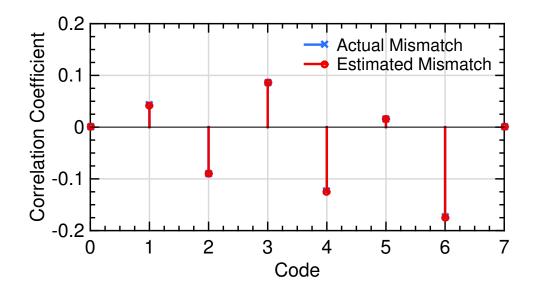

| 7.5 | Actual and estimated mismatch coefficients for each code on simulated data. Mean squared error is $\approx 10^{-7}$                                                                                                                                                              | 103 |

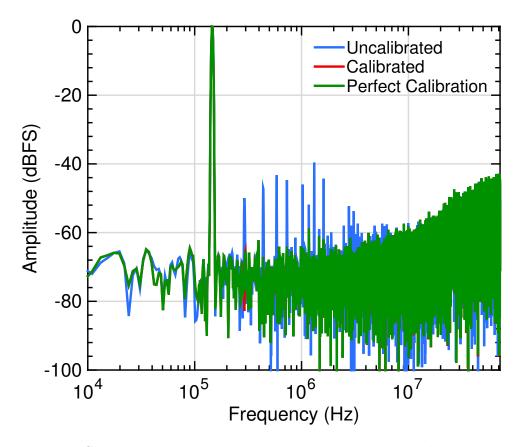

| 7.6 | Spectrum showing linearity improvement using the calibration algorithm for simulated data that matches the estimated mismatch of the first generation chip. Uncalibrated THD = $-35.4$ dB, calibrated THD = $-49.1$ dB. THD is improved by 13.7 dB for OSR = 14, BW = $5.14$ MHz | 104 |

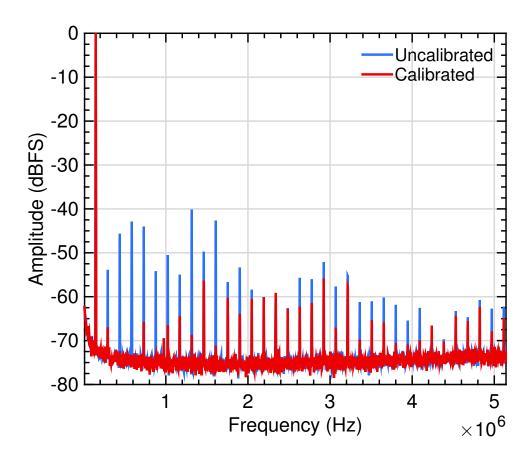

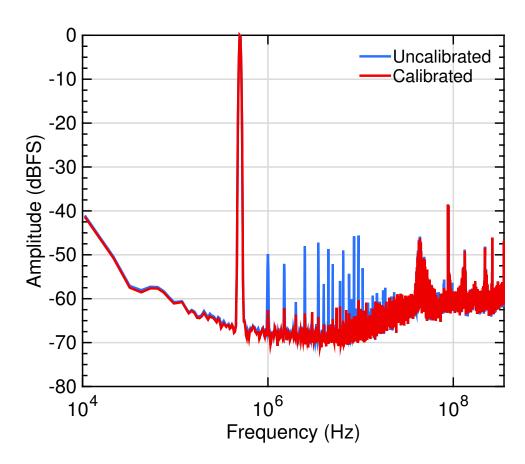

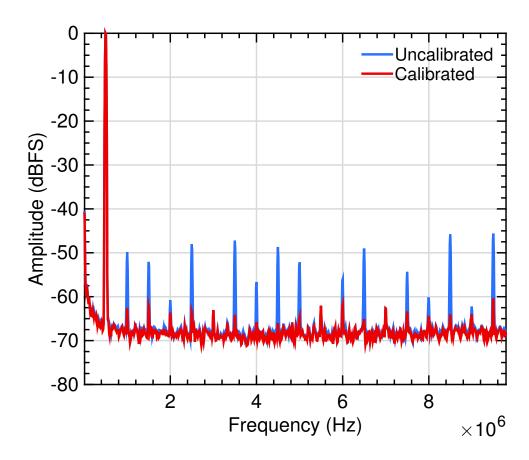

| 7.7 | Spectrum showing linearity improvement using the calibration algorithm for second generation chip measured data. Uncalibrated THD = $-35.0$ dB, calibrated THD = $-51.0$ dB. THD is improved by 16.0 dB for OSR = 36, BW = 9.8 MHz                                               | 106 |

| 7.8 | Spectrum showing linearity improvement using the calibration algorithm for second generation chip measured data. Uncalibrated THD = $-35.0$ dB, calibrated THD = $-51.0$ dB. THD is improved by 16.0 dB for OSR = 36, BW = 9.8 MHz                                               | 107 |

| 7.9 | Estimated mismatch coefficients for each code on measured second chip data                                                                                                                                                                                                       | 108 |

### Chapter 1

#### Introduction

Moore's Law [2], or the doubling of transistors on an integrated circuit (IC) every 18–24 months, has been the driving force behind the exponential growth in the consumer electronics industry over the past few decades. State-of-the-art CMOS fabrication processes continually offer smaller transistors, which are faster and consume less active power due to lower capacitive loading and lower supply voltage. Nowadays, commercial technology nodes offer minimum transistor gate lengths of 65 nm, 45 nm, 22 nm, ... rendering multibillion-transistor ICs not only feasible, but also cost effective.

The demand for reducing costs and building more compact electronic devices has provided incentives to integrate more functionality on a single application-specific IC (ASIC). Multi-chip solutions are less attractive in today's battery-powered handheld devices in which low-power operation is key. This is in part due to the need to reduce printed circuit board (PCB) size, as well as to reduce power lost in package pins, bond wires, and matched 50  $\Omega$  transmission-lines. Given these constraints, single-chip ASICs that integrate not only digital but also analog functions have become a necessity for many years. These so-called "mixed-signal" ICs present a plethora of new challenges

that have been partially addressed.

Consider a wireless radio receiver as an example application that requires both analog and digital processing. Examples of analog circuits used in this application include: low-noise amplification of low-level signals received by the antenna, bandpass filtering to remove a large portion of out-of-band noise and interference, and mixing the radio frequency (RF) signal down to an intermediate frequency (IF). At the boundary between analog and digital, an analog-to-digital converter (ADC) samples the analog signal into quantized (digital) discrete-time samples that are streamed to the baseband processor. The role of the digital baseband processor is to efficiently decode the transmitted message using digital signal processing algorithms.

Availability of increasingly smaller transistors in state-of-the-art CMOS processes translates into faster digital as well as analog circuits; however, analog circuit accuracy generally degrades with reduced dimensions and supply voltages. These mixed-signal integrated circuits are a hostile environment for analog circuit design for several reasons, such as:

- Due to the market dominance of digital circuits, the latest CMOS processes are generally optimized for digital circuits while quantities of interest to analog circuit design, such as intrinsic transistor gain, are sacrificed.

- Coexistence of a larger number of analog and digital circuits in closer proximity increases the noise coupled onto analog circuits from fast-

switching digital circuits.

- Reduced supply voltages to avoid breakdown of thin gate oxides reduces voltage headroom of analog circuits, thereby resulting in smaller linear operating regions and lower dynamic range.

- Reduced transistor dimensions reduces analog matching accuracy due to process variations [3], and reduced area lowers capacitance, which in turn increases thermal noise (kT/C noise).

Thus, there is both a need and a trend to rethink the design of analog circuits to be viable in advanced "digital-friendly, but analog-hostile" processes. The focus of this work is an important mixed-signal circuit that interfaces between analog and digital circuits, the Analog-to-Digital Converter (ADC). For the rest of this work, I restrict my focus to ADC circuits but many of the techniques could be used for other mixed-signal circuits with a similar approach. The rest of this chapter serves as an introduction to current approaches to improving ADCs in nanometer-scale CMOS processes.

Murmann [4] plots the trends in ADC performance from a power-efficiency viewpoint and observes an average reduction in energy by a factor of two approximately every 1.9 years. However, from a speed-resolution viewpoint, a weak doubling every 3.6 years is observed, although top performance has not increased much since the early 2000s. Additionally, he studies impact of scaling in ADC design is studied and references improved architectural schemes.

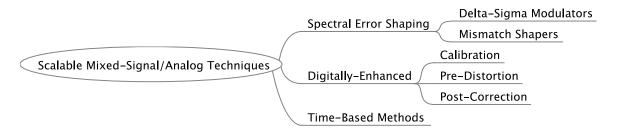

Figure 1.1: A classification of techniques to improve scaling of analog integrated circuits in nanometer-scale CMOS processes.

#### 1.1 ADC Circuits Suited for Scaling

Several techniques can make ADC circuits more suitable for CMOS scaling. These techniques either relax accuracy requirements of analog circuits for improved area/power efficiency, or provide a means to mitigate the impairments associated with scaling. Here, I classify the techniques into three main categories: spectral error shaping, digitally-enhanced analog, and time-based processing. This classification is illustrated in Fig. 1.1 and the approaches are briefly explained below. For another classification and additional insight, please refer to [5].

#### 1.1.1 Spectral Error Shaping

A widely used technique that allows one to build accurate mixedsignal/analog circuits is used in delta-sigma ( $\Delta\Sigma$ ) modulators (DSM). Simply stated, DSMs create a feedback loop to perform noise-shaping by pushing most of the energy of quantization noise into the high end of the spectrum. Combined with oversampling and low-pass filtering, DSMs enable overall higher resolution conversion with components as inaccurate as 1-bit ADCs. DSMs are also used in DACs. Another widely used technique to push error signal due to mismatch into the high end of the spectrum is mismatch shaping [6]. The  $\Delta\Sigma$  ADC is introduced in more detail in Section 2.2.

#### 1.1.2 Digitally-Enhanced Analog

The term "Digitally-Enhanced Analog" or "Digitally-Assisited Analog" refers to a collection of techniques that utilize digital signal processing (DSP) algorithms to improve the overall performance of a mixed-signal/analog circuit by relaxing the analog component requirements and letting DSP algorithms correct for the losses. The DSP overhead must be such that the area/energy efficiency of the overall system be better than the case where a more accurate analog component is used.

As processes scale and analog accuracy becomes harder to achieve, the reduced cost of digital gates makes this approach increasingly effective. Examples of digitally-assisted circuits will be given in Chapter 7.

#### 1.1.3 Time-Based Methods

As voltages and currents scale down, voltage and current accuracies are reduced. Analog circuit linearity decreases when supply voltages are reduced. Also, thermal noise (kT/C) increases when capacitance decreases. The idea to move analog quantities from the (voltage or current) amplitude axis to the time axis becomes attractive. Scaled processes offer higher time resolution,

and continue to do so. If analog quantities are represented on the time axis, an opportunity exists for circuits designed with this paradigm to not only be viable to scaling, but also improve with process generation. In Section 2.3, I discuss time-based signal processing in more detail.

### 1.2 Proposed Contributions

I propose to improve performance of mixed-signal/analog circuits, in particular Analog-to-Digital Converters (ADCs), in nanometer-scale CMOS using novel architectures and techniques. In particular, I will be defending the following thesis statement:

Architecting low-area delta-sigma data converters that scale with CMOS technology requires replacing voltage-domain with time-domain processing.

I will give evidence to support this claim through the following contributions:

- 1. Design and modeling of a novel noise-shaping  $\Delta\Sigma$  ADC architecture that features the following:

- (a) mostly-digital time-based processing, which

- i. accepts a voltage signal at the input, but internally converts it to a pseudo-differential pulse, and

- ii. all subsequent processing is performed on pulses whose widths encode the signal information.

- (b) asynchronous modulator with loop delay calibration unit, which

- i. provides a known time base using an external reference clock,

- ii. removes harmonic distortion due to non-uniform sampling, which arises from input-dependent time drift in the asynchronous loop, and

- iii. reduces the need for an accurate clock network.

- (c) a novel multi-bit invertible TDC/DTC (ADC/DAC), wherein

- i. the width of the pulse is quantized by a delta-sigma modulator with a flash time-to-digital converter (TDC) as the internal ADC,

- ii. reduces area through sharing the unit delay elements,

- (d) removes the sample-and-hold amplifier and replaces it with a continuoustime comparator which simplifies the circuit even further.

- 2. Design, fabrication, and testing two prototype ADC chips using the proposed architecture (in collaboration with Dr. Woo Young Jung), using

- (a) TSMC 180nm CMOS process, and

- (b) IBM 45nm SOI process.

- 3. Nonlinear circuit linearization of the ADC

- (a) using digital post-correction to estimate and correct for nonlinearity due to DTC mismatch

- (b) without the need of a calibrating DAC

### 1.3 Organization

Background information about ADCs,  $\Delta\Sigma$  modulation, and time-based approaches are presented in Chapter 2. The proposed time-based delta-sigma ADC is discussed in Chapter 3. Behavioral modeling of the proposed time-based delta-sigma ADC is presented in Chapter 4. First and second generation chip prototypes are presented in Chapters 5 and 6, respectively. Chapter 7 discusses the source of nonlinearity in the two prototype chips and shows a method of calibrating the nonlinearity. Finally, conclusions are drawn in Chapter 8.

#### 1.4 Abbreviations

ADC Analog-to-Digital Converter ADPLL All Digital Phase Lock Loop

ASIC Application-Specific Integrated Circuit

CMOS Complementary Metal Oxide Semiconductor

DAC Digital-to-Analog Converter

DPLL Digital Phase Locked Loop

DSP Digital Signal Processing

DSM Delta-Sigma Modulator

DTC Digital-to-Time Converter

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

IC Integrated Circuit

LSB Least Significant Bit

LVCMOS Low Voltage CMOS

LVDS Low Voltage Differential Signaling

LVTTL Low Voltage Transistor-to-Transistor Logic OFDM Orthogonal Frequency Division Multiplexing

OSR OverSampling Ratio RMS Root Mean Squared

SFDR Spurious-Free Dynamic Range

SOI Silicon-on-Insulator

TDC Time-to-Digital Converter VCO Voltage Controlled Oscillator VTC Voltage-to-Time Converter

## Chapter 2

## Background and Prior Work

This chapter introduces important concepts which will be used in subsequent chapters. Toward this goal, an overview of ADC architectures is presented. Then, the concept of delta-sigma modulation as applicable to ADCs is presented. Next, the time-based approach in analog signal processing is described. Finally, different methods of combining time-based techniques with delta-sigma modulation are reviewed.

### 2.1 Analog-to-Digital Conversion

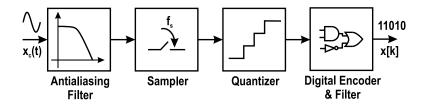

Analog-to-Digital Conversion is the process of converting a real-valued continuous-time waveform  $x_c(t)$  to a discrete-amplitude discrete-time sequence x[k], suitable for digital signal processing. Typical ADCs consist of: 1) low-pass filtering (anti-aliasing filter), 2) sampling, 3) quantization, and 4) digital ecoding and filtering (see Fig. 2.1). First I review the Nyquist sampling theorem to explain the first two operations, then I introduce concepts in quantization and coding.

Figure 2.1: Block diagram of a typical analog-to-digital converter

#### 2.1.1 Sampling Theory

The Nyquist Sampling Theorem (see [7]) states that a band-limited signal  $x_c(t)$  with

$$X_c(f) = 0 \quad \text{for } |f| \ge f_N, \tag{2.1}$$

is uniquely determined by its samples  $x[n] = x_c(nT), n = 0, \pm 1, \pm 2, \dots$  if

$$f_s = \frac{1}{T} \ge 2f_N. \tag{2.2}$$

where  $f_N$  is called the Nyquist frequency and  $2f_N$  is the Nyquist rate. In practice, bandlimited signals are rare (or impossible for finite-duration signals) and there exists additive noise that may fill the higher frequency range. Thus to avoid aliasing into the lower frequency range, an analog prefilter (called an antialiasing filter) must enforce bandlimitedness. Without, oversampling, i.e., when  $f_s = 2f_N$ , an ideal "brick wall" low-pass filter is required. In the frequency domain, this ideal filter is defined as:

$$H_{AA}(f) = \begin{cases} 1, & |f| < f_s/2 \\ 0, & |f| > f_s/2 \end{cases}, \tag{2.3}$$

but since such a filter would be noncausal and have infinite delay, it must be approximated by a physically-realizable analog filter. Limitations of the

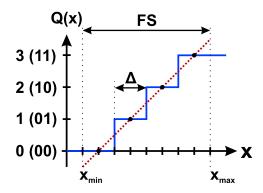

Figure 2.2: N = 2-bit uniform quantizer function

analog filter include finite stop-band attenuation, finite transition-band slope, and non-zero pass-band ripple. To obtain a better approximation to the ideal brick wall filter, the implementation cost of the antialiasing filter increases.

With oversampling (sampling above the Nyquist rate), the requirements of the analog filter can be relaxed at the expense of increasing the rate of the Digital Signal Processing (DSP) downstream. If the DSP algorithm desires the rate to be reduced to the Nyquist rate, a (digital) decimation filter is required. Thus oversampling can be viewed as a technique to trade analog filter complexity with digital decimation filter complexity.

#### 2.1.2 Quantization

In contrast to ideal sampling at the Nyquist rate or greater, which preserves information in the signal, quantization is an irreversible (lossy) operation that is inherently non-linear. A typical N-bit uniform quantizer, such as the one shown in Fig. 2.2, rounds the real-valued (analog) sample to the near-

est one of  $2^N$  discrete levels. Such a quantizer y = Q(x), divides the interval  $[x_{min}, x_{max}]$  with full-scale range  $FS = x_{max} - x_{min}$  into  $2^N$  uniform intervals with width  $\Delta = \frac{FS}{2^N}$ , also called the LSB. Within the full-scale range, i.e., no saturation, the uniform quantizer function may be described mathematically as:

$$Q(x) = \left| \frac{x - x_{min}}{\Delta} \right|, \qquad x_{min} \le x < x_{max}$$

(2.4)

where  $\lfloor u \rfloor$  denotes the flooring operation, i.e., the largest integer  $\leq u$ . Thus Q(x) is a number from 0 to  $2^N - 1$ , and the analog equivalent of Q(x) is:

$$\tilde{Q}(x) = \Delta \left| \frac{x - x_{min}}{\Delta} \right| + x_{min}, \quad x_{min} \le x < x_{max}$$

(2.5)

The difference between the quantized version of a sample and the true analog value is called quantization error or quantization noise:

$$e = x - \tilde{Q}(x), \tag{2.6}$$

which ranges from  $-\frac{\Delta}{2}$  to  $\frac{\Delta}{2}$ . For large inputs within the quantization range (i.e., no saturation), the error can be assumed to be a uniformly-distributed random variable uncorrelated with the input, thus the quantization noise power (variance) is:

$$\sigma_e^2 = \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} \frac{1}{\Delta} e^2 de = \frac{\Delta^2}{12} = \frac{FS^2}{12(2^N)^2}$$

(2.7)

A linear model for quantization therefore becomes:

$$y = G\left(x - x_{min}\right) + e \tag{2.8}$$

Figure 2.3: First-order delta-sigma analog-to-digital converter

Figure 2.4: Sampled-data linear model of the analog portion of the first-order delta-sigma analog-to-digital converter shown in Fig. 2.3

where G is the gain (or the slope of the dotted line connecting  $x_{min}$  and  $x_{max}$  in Fig. 2.2), which may be assumed to be 1, without loss of generality.

The larger the number of quantization bits N, the smaller the LSB ( $\Delta$ ), and hence the smaller the quantization noise. Every application usually has its own requirement for N, but it may range from a few bits (control applications) up to 24 bits (hi-fidelity audio). The output of the quantizer is subsequently encoded; i.e., each quantization level is assigned a binary digital code, e.g., a 2's complement signed N-bit number.

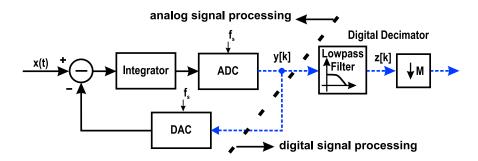

#### 2.2 Delta-Sigma Modulation

In the 1950s and 1960s, it was shown that the effective resolution of a coarse quantizer may be increased by using feedback and oversampling. The so-called delta modulator [8], [9] and its successor the delta-sigma ( $\Delta\Sigma$ ) modulator [10] have since then evolved considerably both in theory and practice. To understand its operation [11–13], consider the first-order  $\Delta\Sigma$  ADC and its equivalent sampled-data model shown in Fig. 2.3 and Fig. 2.4, respectively. The output of the accumulator is

$$w[k] = x[k-1] - e[k-1]$$

(2.9)

and the output of the ADC is

$$y[k] = w[k] + e[k] = x[k-1] + (e[k] - e[k-1])$$

(2.10)

Therefore, the output y[k] contains a delayed version of the input x[k-1] plus a differentiated version of the quantization error. In other words, the first difference of the noise appears at the output while the signal is unchanged. The spectral density of the noise is given by [11]:

$$N(f) = E(f) |1 - e^{-j2\pi fT}| = 2 e_{\rm rms} \sqrt{2T} \sin\left(\frac{2\pi fT}{2}\right)$$

(2.11)

As shown in Fig. 2.5, the  $\Delta\Sigma$  modulator reduces the noise in low frequencies at the expense of increasing noise at high frequencies. The high frequency noise is removed by the digital low-pass filter that is part of the decimator used to reduce the sampling rate. When the oversampling ratio (OSR) defined as

Figure 2.5: Spectral density of noise from delta-sigma quantization N(f) compared to ordinary quantization E(f)

$M = \frac{f_s/2}{f_0}$  is high, the modulation noise in the signal band is much less than the ordinary quantization error. The total noise in the signal band is:

$$n_0^2 = \int_0^{f_0} |N(f)|^2 df \approx e_{\text{rms}}^2 \frac{\pi^2}{3} (2f_0 T)^3 \qquad f_s \gg f_0$$

(2.12)

In other words, the RMS value is:

$$n_0 \approx e_{\rm rms} \frac{\pi}{\sqrt{3}} (OSR)^{-3/2} \tag{2.13}$$

Therefore, with a highly selective digital low-pass filter, every doubling of OSR reduces the noise by 9 dB (1.5 bits), but in practice for the sake of relaxing the requirements of the digital filter, some of the high frequency noise is allowed to alias into the signal band. With higher orders of integration, the slope of N(f) at low frequency increases and thus reduces in-band noise even lower. Reference [14] provides a more detailed analysis that is not included here for brevity.

Figure 2.6: Error feedback only delta-sigma modulator

Another topology for first-order noise shaping is that of the error feed-back topology, shown in Fig. 2.6. While it is used less often in traditional voltage-based ADCs, it has advantages which will become clear in Chapter 3. To conclude this section, note the benefits of using  $\Delta\Sigma$  modulation from a scaling perspective [15]:

- 1. Reduced analog accuracy requirements, e.g., a coarse internal quantizer, as low a single-bit may be used for an overall higher resolution converter.

- 2. A large component, namely the digital decimation filter improves with scaling (implemented by digital gates)

- 3. Analog antialiasing filter prior to sampling has more relaxed specifications

### 2.3 Time-Based Signal Processing

Traditionally, analog circuits represent and manipulate information in the (voltage) amplitude domain, which becomes increasingly unreliable in nanometer-scale mixed-signal integrated circuits. This is due to reduced supply voltages, reduced linearity, short-channel effects, and coupled noise from digital circuits on the same chip. Thus one needs to rethink analog processing to find techniques that are more viable to CMOS scaling. One method of solving this problem in state-of-the-art CMOS processes is to exchange the amplitude axis for the time axis [16]. Thus, an analog voltage quantity is converted to time and is subsequently processed. This approach not only alleviates the problem of reduced voltage, but it also takes advantage of the increased time-resolution due to higher intrinsic transistor speeds. The voltage-to-time conversion (VTC) may take many forms, such as pulse frequency modulation, pulse duration modulation and duty-cycle modulation [16].

In ADC applications, a time-based signal represented by a pulse duration, may be quantized using a time-to-digital converter (TDC) circuit which measures the time between two pulses. TDCs have been traditionally been used in applications such as time-of-flight measurement in physics experiments, and digital phase lock loops (DPLL). It is one of the fundamental components in time-based signal processing. Another block is the digital-to-time converter (DTC), which is the reverse operation of the TDC. In [17], an overview of TDC and DTC circuits is given, and TDCs are classified into four categories:

- 1. Single counter

- 2. Flash TDC

- 3. Vernier oscillator, e.g., [18, 19]

Figure 2.7: A 3-bit flash time-to-digital converter [17]

4. Cyclic pulse-shrinking TDC, e.g., [20]

As an example, consider the flash TDC illustrated in Fig. 2.7. Such a circuit is implemented using digital circuits: buffers for unit delay by  $\tau$ , latches for strobing the value of the input pulse at equally spaced time-intervals, and digital logic to convert a thermometer code to a binary word. The benefits of time-based processing are clear by examining this circuit:

- 1. Improved timing accuracy with transistor scaling

- 2. Time-based operations have "digital" implementation that scale well (even if treated as analog with custom layout)

3. Not thermal noise limited, therefore no need for large capacitances

Examples of circuits and systems using the time-based processing approach include: an all-digital PLL (ADPLL)-based Bluetooth radio frequency synthesizer [21], or recent voltage-controlled oscillator (VCO)-based ADCs in which the information in the phase-domain is quantized.

#### 2.4 Time-Based Delta Sigma ADCs

Analog-to-digital converter systems that combine  $\Delta\Sigma$  modulation and time-based processing include the following:

- 1. Voltage-Controlled Oscillator (VCO)-based ADCs,

- 2. Time-Based Delta-Sigma ADCs.

The concept of using VCOs as multi-bit quantizers in  $\Delta\Sigma$  ADCs was introduced in 1999 [22]. Since its inception, many prototypes have utilized this scheme for a variety of applications, primarily in the design of high-speed data converters for wireless systems. The key advantage of using a VCO in an oversampling converter is that the conversion from voltage to time using a VCO that generates binary pulses whose frequency is proportional to the input voltage, and whose phase is the integral of the frequency. Thus by sampling the phase of the VCO, quantization of the integral of input voltage is achieved. This architecture provides inherent noise-shaping properties and can operate at low supply voltages and high sampling rates. While the natural integration

and quantization using a VCO quantizer achieves first-order noise shaping, it may be used as the quantizer in a multi-order  $\Delta\Sigma$  ADC with additional OpAmp-based integration stages [23–25].

It is widely known that the linearity of a VCO's voltage-to-frequency relationship is limited [26]. Thus, a lot of the focus in VCO-based ADC implementations is on the linearity improvement. Taylor and Galton use pseudorandom binary sequences and an auxiliary DAC to measure nonlinearity using an LMS algorithm and cancel it at the output of the modulator using a lookup table [27–29]. On the other hand, Rao, et al proposed the use of a two-level pulse-width modulator (PWM) in front of the VCO-based  $\Delta\Sigma$  ADC [30]. By restricting VCO input to only two levels, the architecture becomes insensitive to VCO voltage-to-frequency nonlinearity. However the PWM modulator is built using OpAmps which do not scale well.

Despite drawbacks to the VCO-based  $\Delta\Sigma$  ADC, many solutions to these drawbacks have been proposed and the momentum is moving towards commercially viable data converters. This architecture is particularly attractive at bulk CMOS process nodes at or below 65nm. There is evidence of commercial VCO-based ADC designs under development.

Alternative time-based ADCs are proposed [31], [32], and [33]. A time-domain ADC architecture that implements a PWM and time-to-digital converter (TDC) in the feedback loop is presented [34]. This architecture improves the linearity of PWM. However, major analog blocks (integrator and filter) are required for the noise shaping. Another innovative architecture [35]

replaces the quantizer and DAC in a  $\Delta\Sigma$  ADC with a time-encoding quantizer (TEQ).

# 2.5 Summary

In summary, I introduced analog-to-digital conversion, and described  $\Delta\Sigma$  modulation as a leading approach that benefits from CMOS process scaling due to oversampling and noise shaping. I reviewed time-based concepts for signal processing. Then, I mentioned advantages of combining the two approaches as an attractive method of reducing ADC circuit area in scaled process nodes.

In the next chapter, I discuss the design of an ADC circuit that uses both the time-based processing scheme and  $\Delta\Sigma$  modulation, therefore combining the benefits of the two approaches for improved performance with scaling.

# Chapter 3

# Time-Based $\Delta\Sigma$ ADC

# 3.1 Introduction

In Chapter 2, I discussed the benefits of delta-sigma modulation (DSM) and time-based processing from a scaling point-of-view. In this chapter, I propose a time-based  $\Delta\Sigma$  ADC that aims to benefit from the merits of both techniques in order to improve the viability of ADCs under transistor scaling. The proposed mostly-digital asynchronous time-based  $\Delta\Sigma$  ADC features the following:

- 1. At the input, the ADC accepts a voltage signal, which is internally converted to a pseudo-differential pulse. All subsequent processing is performed on pulses whose widths encode the signal information.

- 2. The asynchronous modulator can be synchronized to an external clock through a loop delay calibration unit. This scheme provides a known time base, and removes harmonics due to non-uniform sampling which arises from input-dependent time drift in the asynchronous loop.

- 3. The width of the pulse is quantized by a delta-sigma modulator with a flash time-to-digital converter (TDC) as the internal ADC.

- 4. A novel multi-bit invertible TDC/DTC (ADC/DAC) is possible thanks to time-domain processing. This approach reduces area.

- 5. The proposed structure presents an opportunity to use the "minimalistic design" scheme [4] to further reduce power through reliance on digital calibration rather than precision analog circuitry.

- 6. It also removes the sample-and-hold amplifier and replaces it with a continuous-time comparator which simplifies the circuit even further.

In the following section, I review analog-to-digital converter systems that combine  $\Delta\Sigma$  modulation and time-based processing.

## 3.2 Time-Based $\Delta\Sigma$ Modulator Architecture

This section describes the operation principle of the proposed timebased  $\Delta\Sigma$  ADC, whose model is shown in Fig. 3.1. First, the concept of information encoding using pseudo-differential pulses is described. Then pulse width addition and subtraction in the time domain is introduced. Finally, the modulator topology of the proposed ADC is presented.

#### 3.2.1 Pulse Width Information Encoding

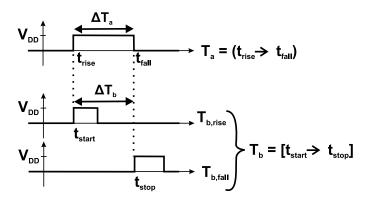

In the proposed ADC, analog information is encoded in the form of "pulse width." A conventional digital pulse  $T_a$ , shown in Fig. 3.2, consists of a signal that is either low (0 V) or high  $(V_{DD})$ . The pulse width is defined as the duration of time in which the pulse is high. Conceptually, this definition

Figure 3.1:  $\Delta\Sigma$  modulator model showing boundaries of voltage/time/digital domain processing. VTC = voltage-to-time converter, TDC = time-to-digital converter, DTC = digital-to-time converter

Figure 3.2: Definition of pulse and pseudo-differential (conceptual) pulse

is simple to understand; however, for both accuracy and robustness, pseudo-differential pulses are often preferred. A pseudo-differential pair of pulses  $(T_{b,rise}, T_{b,fall})$  as shown in Fig. 3.2, encode pulse width in the time duration between the rise transition of  $T_{b,rise}$  and that of  $T_{b,fall}$ .

The advantages of pseudo-differential pulses for encoding analog quantities are twofold: (1) By encoding information in the rise-to-rise delay rather than rise-to-fall delay, errors due to skewed low-to-high vs. high-to-low propagation delays are eliminated, and (2) this encoding removes the restriction on minimum pulse widths due to vanishing pulses. Every circuit in the proposed ADC operates using pseudo-differential pulses, even though some of the timing diagrams in this chapter illustrate the conventional pulse (for simplicity).

In reference to the pulses illustrated in Fig. 3.2, the following notation is used for the remainder of this chapter:

• A pulse represented by a pair of numbers  $T_a = (t_{rise} \to t_{fall})$  indicates a transition from zero to  $V_{DD}$  at time  $t_{rise}$  and back to zero at time  $t_{fall}$ .

The pulse width represented by  $\Delta T_a = t_{fall} - t_{rise}$  is the analog quantity encoded by the pulse.

- A pseudo-differential pulse (or **conceptual pulse**) is represented as a pair of numbers  $T_b = [t_{start} \to t_{stop}]$  and is defined as two pulses, the "rise pulse"  $T_{b,rise} = (t_{start} \to t_{start} + \Delta t_r)$  and the "fall pulse"  $T_{b,fall} = (t_{stop} \to t_{stop} + \Delta t_f)$ . Square brackets denote pseudo-differential pulses. The information contained in the pseudo-differential pulse is  $\Delta T_b = t_{stop} t_{start}$  which is the rise-to-rise delay between the two pulses, which is called **pulse width**. Note that  $\Delta t_r$  and  $\Delta t_f$  have no significance in the signal information; however, they are required to be a fraction of a sampling period.

- The rise pulse of  $T_b$  is denoted by  $rise(T_b) = t_{start}$

- The fall pulse of  $T_b$  is denoted by fall $(T_b) = t_{stop}$

The remainder of this chapter uses pseudo-differential pulses for all circuits, even if conventional pulses are shown in the timing diagrams (for simplicity).

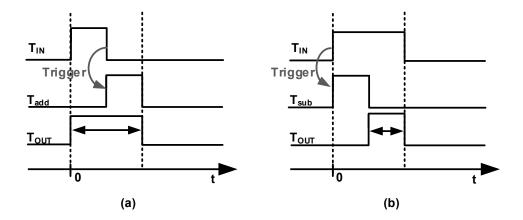

### 3.2.2 Time-Domain Addition and Subtraction

Analog time-domain processing using pulse width as the analog quantity is shown in Fig. 3.3. To add two pulses, say  $T_{in}$  and  $T_{add}$ , as depicted in Fig. 3.3(a), we align the start of  $T_{add}$  to the end of  $T_{in}$ . Then the sum of the pulse widths is simply the pulse  $T_{out}$  that begins with  $T_{in}$  and ends with

Figure 3.3: (a) Addition and (b) subtraction in time-domain using pulse widths

$T_{add}$ . Subtraction, depicted in Fig. 3.3(b), requires aligning the start of  $T_{sub}$  with that of  $T_{in}$ . The result of subtraction is the pulse  $T_{out}$  which begins when  $T_{sub}$  ends, and ends when  $T_{in}$  ends. Aligning pulses in the manner described requires a triggering mechanism (and asynchronous digital circuits), which is described later.

With respect to pseudo-differential pulses, it is clear how pulse widths can be added and subtracted. If two pulses are appropriately aligned, adding a pulse to another is achieved by simply delaying the f pulse of the output. Similarly, to subtract two pulses aligned with their r pulses, only the output r pulse needs to be delayed. This method of pulse arithmetic has the advantage of simple implementation using digital logic gates. It also has the complexity of dealing with the alignment of pulses. In the next section, it shall become clear that using an error feedback structure, where the order of addition and

subtraction is reversed (relative to conventional first-order  $\Delta\Sigma$  modulators) resolves the pulse alignment problem.

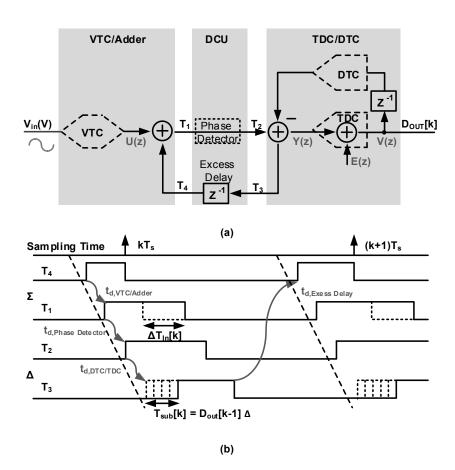

### 3.2.3 Modulator Topology and System Modeling

The proposed time-based  $\Delta\Sigma$  ADC architecture is shown in Fig. 3.4(a). It comprises three major blocks:

- 1. VTC/Adder,

- 2. Delay Control Unit (DCU), and

- 3. Time-to-Digital Converter/Digital-to-Time Converter (TDC/DTC).

The conceptual timing digram depicted in Fig. 3.4(b) shows conventional pulses for brevity; however, pseudo-differential pulses are used throughout this chapter. The topology of the modulator is first order error feedback (introduced in Fig. 2.6). The system equations are the following:

$$V(z) = Y(z) + E(z)$$

$$(3.1)$$

$$= (U(z) + z^{-1}Y(z) - z^{-1}V(z)) + E(z)$$

(3.2)

$$= U(z) + E(z) - z^{-1} (V(z) - Y(z))$$

(3.3)

$$V(z) = U(z) + (1 - z^{-1})E(z)$$

(3.4)

This shows that the signal transfer function (STF) is unity

$$STF = \frac{V(z)}{U(z)} = 1, \tag{3.5}$$

Figure 3.4: (a) Architecture and (b) timing diagram of the time-based  $\Delta\Sigma$  ADC. VTC = voltage-to-time converter, DCU = delay control unit, TDC = time-to-digital converter, DTC = digital-to-time converter.

and the noise transfer function (NTF) is that of a first order  $\Delta\Sigma$  modulator:

$$NTF = \frac{V(z)}{E(z)} = 1 - z^{-1}$$

(3.6)

The input to the ADC is an analog voltage-domain waveform  $V_{in}(t)$ , which after sampling at  $t = kT_s$  is converted to a time-domain quantity by the Voltage to Time Converter (VTC). The analog sample  $V_{in}(kT_s)$  is converted to a conceptual pulse (pseudo-differential pulse) [see definition in Section 3.2.1] after a transformation such as a linear transformation (for simplicity):

$$\Delta T_{in}[k] = a + b V_{in}(kT_s). \tag{3.7}$$

The VTC/Adder block adds the pulse widths of the feedback pulse and the input sample,  $\Delta T_4$  and  $\Delta T_{in}$ , respectively.

$$\Delta T_1[k] = \Delta T_4[k] + \Delta T_{in}[k]. \tag{3.8}$$

The Delay Control Unit (DCU) block has two functions:

- 1. to control the startup conditions, and

- 2. to take measurements that facilitate loop delay calibration and tracking.

The output of this block,  $T_2$ , under normal closed-loop operation of the ADC, is simply a delayed version of  $T_1$ . Therefore, the duration of the pulse is unchanged, and

$$\Delta T_2[k] = \Delta T_1[k] \tag{3.9}$$

The TDC/DTC block implements both subtraction and quantization operations in the time domain. Quantization in the time domain is achieved using a multi-bit (e.g., 3-4 bit) Flash Time-to-Digital Converter (TDC) with quantization step  $\Delta$ . Subtraction is achieved by delaying the pulse rise by the appropriate number of quantization steps, as determined by  $D_{out}$  from the previous cycle (i.e.,  $D_{out}[k-1]$ ). Subtraction precedes quantization, and the delay stages used in the DTC are reused in the TDC sequentially.

$$\Delta T_3[k] = \Delta T_2[k] - D_{out}[k-1]\Delta \tag{3.10}$$

$$D_{out}[k] = \left| \frac{T_3[k]}{\Delta} \right| \tag{3.11}$$

The Excess Delay block outputs  $T_4$ , which is a delayed version of  $T_3$ , without changing its width.

$$\Delta T_4[k] = \Delta T_3[k-1] \tag{3.12}$$

The combination of the delays due to the *Excess Delay* block and all other blocks in one cycle should ensure that the sampling interval is approximately uniform. The required amount of delay is calculated in Section 3.2.6.

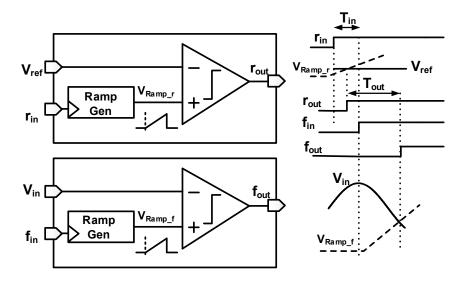

### 3.2.4 Voltage-to-Time Converter/Adder

The addition as well as the preceding voltage-to-time conversion operation shown in Fig. 3.4 is performed by the VTC/Adder block. At every cycle, the VTC/Adder conceptually adds to its input pulse  $T_4$ , a pulse width proportional to  $V_{in} - V_{ref}$ , and  $T_1$  results. Both the input and output pulses are pseudo-differential pulses  $(r_{in}, f_{in})$  and  $(r_{out}, f_{out})$ . To implement the voltageto-time conversion and addition, two identical half-circuits are used, as shown

Figure 3.5: Functional block diagram and timing diagram of the VTC/Adder.

in Fig. 3.5. The identical circuits have a ramp generator and a continuous-time comparator.

As shown in the bottom half of Fig. 3.5, the analog input  $V_{in}(t)$  is connected to a continuous-time comparator. The fall edge of the feedback pulse  $f_{in} = T_{4,fall}$  triggers a ramp generator to produce a linear ramp from 0 to 1.8V. Once the ramp generator output  $(V_{Ramp,r})$  crosses  $V_{in}$ , the output  $f_{out}$  propagates. The larger the value of  $V_{in}$ , the longer it takes for the ramp voltage to reach  $V_{in}$ . Therefore, the information about the voltage amplitude of  $V_{in}$  is stored in time. The proportionality is linear, when the ramp is linear,

and therefore

$$f_{out} = \text{fall}(T_1[k]) = \text{fall}(T_4[k]) + t_d + k V_{in}(kT_s)$$

(3.13)

where

$$t_d = t_{\text{ramp gen}} + t_{\text{comparator}}, \quad \text{and}$$

(3.14)

$$k = (\text{ramp slope})^{-1}[\text{s/V}] \tag{3.15}$$

The simplest way to remove the fixed offset  $t_d$  due to the delays of the ramp generator and comparator in the VTC/Adder is to replicate the same circuit for the rise signal (top half of Fig. 3.5).  $V_{ref}$  represents the minimum usable input voltage (which may be different from zero if the input voltage range is other than 0 to 1.8V) due to linearity concerns. This replica circuit for removing offset is not optimal in terms of power, but it follows the pseudo-differential principle where the paths between both the rise and fall pulses of the pseudo-differential pulse are equalized as much as possible.

$$rise(T_1[k]) = rise(T_4[k]) + t_d + k V_{ref}$$

(3.16)

Combining (3.13) and (3.16) results in:

$$\Delta T_1[k] = \text{fall}(T_1[k]) - \text{rise}(T_1[k]) \tag{3.17}$$

$$= \Delta T_4[k] + k(V_{in}(kT_s) - V_{ref})$$

(3.18)

$$= \Delta T_4[k] + \Delta T_{in}[k] \tag{3.19}$$

which means the transformation from voltage to time is linear as stated in (3.7) and the VTC/Adder implements addition according to (3.8).

Figure 3.6: Functional block diagram of the TDC/DTC

The output of the VTC/Adder  $(T_1)$  passes through the phase detector block of the Delay Control Unit  $(T_2)$  without modification, except for delay  $t_{d,\text{Phase Detector}}$  applied to both rise and fall pulses. It is then processed by the TDC/DTC block described next.

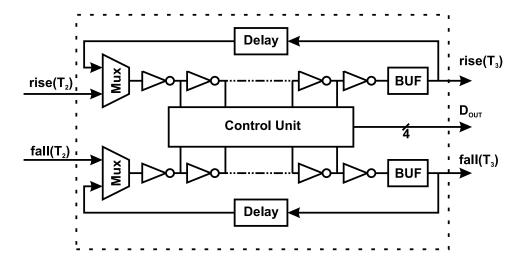

### 3.2.5 Time-to-Digital Converter/Digital-to-Time Converter

The TDC/DTC block performs the functions of both the ADC and the DAC in the first-order delta-sigma error feedback only structure shown in Fig. 2.6. In an effort to save area, a reusable structure for both subtraction and multi-bit quantization is devised. This novel invertible ADC/DAC is possible thanks to time-domain processing and is not possible in voltage-domain processing.

Fig. 3.6 shows the block diagram of the TDC/DTC. It consists of

tapped inverter stages with delay of  $\Delta$  per stage. 16 stages are required for 4-bit quantization; however, to reduce variation in the boundary stages and add extra timing margin, additional "dummy stages" are inserted before and after the main stages.

When a pseudo-differential pulse is received, the fall pulse passes through the dummy stages, but the rise pulse passes through the dummy stages and  $D_{out}[k-1]$  out of 16 stages, where  $D_{out}[k]$  is defined in Fig. 3.4. Therefore:

$$rise(T_3[k]) = rise(T_2[k]) + t_{dummy stages} + D_{out}[k-1]\Delta \qquad (3.20)$$

$$fall(T_3[k]) = fall(T_2[k]) + t_{dummy stages}$$

(3.21)

Thus, the subtraction operation is implemented as

$$\Delta T_3[k] = \Delta T_2[k] - D_{out}[k-1]\Delta \tag{3.22}$$

After the first time through the inverter stages, and after a small delay, the result of the subtraction is fed back through the same inverter stages to quantize the time between the two pulses (i.e., the width of the pseudo-differential pulse) in terms of the number of inverter stages:

$$D_{out}[k] = \left\lfloor \frac{\Delta T_3[k]}{\Delta} \right\rfloor \tag{3.23}$$

### 3.2.6 Delay Control Unit

The main responsibilities of the DCU are to properly startup the loop after global reset and also prevent unwanted pulse drifts through dynamically adjusting the excess loop delay. The two components of the DCU are

#### 1. Phase Detector

### 2. Excess Delay

The role of the Excess Delay block is to calibrate and "equalize" the loop delay to maintain constant sampling interval that matches the external reference clock over process, temperature, and supply variation as well as modulation by the input itself. Because sampling occurs effectively at the fall edge of  $T_4$  (as shown in Fig. 3.4) and fall( $T_3[k]$ ) is a function of the kth sample ( $\Delta T_{in}[k]$ ), as the input grows larger, fall( $T_3$ ) arrives later in time, and therefore the Excess Delay block must add a smaller delay to  $T_3$  (to get  $T_4$ ) to counteract the change. This will ensure that sampling instances, i.e., fall( $T_4$ ) are approximately uniformly-spaced. Equivalently:

$$T_s \approx \operatorname{fall}(T_4[k+1]) - \operatorname{fall}(T_4[k])$$

(3.24)

$$= t_d + \Delta T_{in}[k] + t_{d.Excess\ Delay}, \quad \text{where}$$

(3.25)

$$t_d = t_{d,VTC/Adder} + t_{d,Phase\ Detector} + t_{d,DTC}$$

(3.26)

(3.27)

Where  $t_{d,block}$  is the propagation delay through the named block (delay experienced by both rise and fall pulses). Therefore, the Excess Delay block must add an additional propagation delay according to the following formula:

$$t_{d,Excess\ Delay} \approx T_s - (t_d + \Delta T_{in}[k]) > 0.$$

(3.28)

Since a high amount of oversampling is used and drift is assumed to be slow, a slow tracking loop may be used to follow the changes, by using the bang-bang control signals provided by the Phase Detector block (*lead* and *lag* outputs).

The Phase Detector block compares the f pulses at each cycle with the rising edge of a clock with frequency  $f_s = 1/T_s$ . This activates either a lead or lag signal that is then applied to the excess delay block of the modulator to increase or decrease the loop delay of both r and f pulses through the excess delay block. The excess delay block overcompensates every time a lead or lag signal is present. Mathematically,

$$lead = \Im(fall(T_4(k)) < kT_s - T_{d,hyst})$$

(3.29)

$$lag = \Im\left(\text{fall}(T_4(k)) > kT_s + T_{d,hyst}\right) \tag{3.30}$$

where  $\mathfrak{I}(\cdot)$  is the indicator function.

With these two bits (lead, and lag) the Excess Delay block adjusts the excess loop delay by 0 (no adjustment) or  $\pm T_{d,hyst2}$  in each cycle. Note  $T_{d,hyst2} > T_{d,hyst}$ . This is in addition to a programmable fixed delay for a wide tuning range of  $f_s$ . By using this approach, one can ensure that the average oversampling frequency is always locked to an external  $f_s$  clock. It is important to recognize that the fluctuation in the sampling time of this time-based ADC does create errors that are similar in nature to noise artifacts generated by noisy clocks.

After releasing the global reset signal, the Phase Detector provides an initial zero-width pseudo-differential pulse to startup the circuit. In normal

mode, the Phase Detector passes through the input pulse to the output with a constant amount of delay ( $t_{d,\text{Phase Detector}}$ ) in Fig. 3.4.

# 3.3 Summary

In this chapter, I propose a novel time-based delta-sigma ADC quantizing pseudo-differential pulse width. I explain the system model and mathematically model the system. The advantages of the structure are the following:

- 1. Utilization of time-based processing in the pulse domain enables mostly-digital (two-level) circuits for processing the analog quantity, with the benefit of improved resolution with CMOS scaling.

- 2. At the input, the ADC accepts a voltage signal, which is internally converted to a pseudo-differential pulse. All subsequent processing is performed on pulses whose widths encode the signal information.

- 3. The asynchronous (and self-oscillating) modulator can be synchronized to an external clock through a loop delay calibration unit. This scheme provides a known time base, and removes harmonics due to non-uniform sampling which arises from input-dependent time drift in the asynchronous loop. It also reduces the need for an accurate clock network.

- 4. The width of the pulse is quantized by a delta-sigma modulator with a flash time-to-digital converter (TDC) as the internal ADC.

- 5. A novel multi-bit invertible TDC/DTC (ADC/DAC) is possible thanks to time-domain processing. This approach reduces area.

- 6. It also removes the sample-and-hold amplifier and replaces it with a continuous-time comparator which simplifies the circuit even further.

In the next chapter, I present the behavioral model of the proposed modulator in MATLAB/Simulink along with plots showing the operation of the modulator. I also investigate and model non-idealities associated with different sub-blocks.

# Chapter 4

# Behavioral Modeling of Time-Based $\Delta\Sigma$ ADC

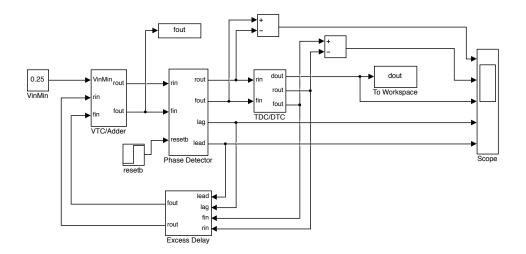

To study the operation of the proposed time-based  $\Delta\Sigma$  ADC, a behavioral model is created in MATLAB/Simulink. Every block in the model calculates and propagates the rise and fall times of the pseudo-differential pulse in each cycle. Every block is modeled according to the equations described in Chapter 3. With this model, quick exploration of different parameters in the system is possible, thereby allowing a designer to understand the system from a high-level before making decisions about circuit implementation of the individual blocks.

## 4.1 Functional Model

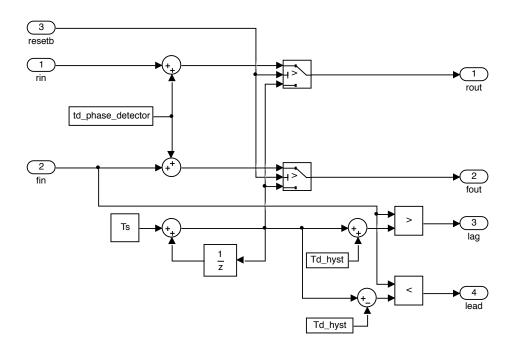

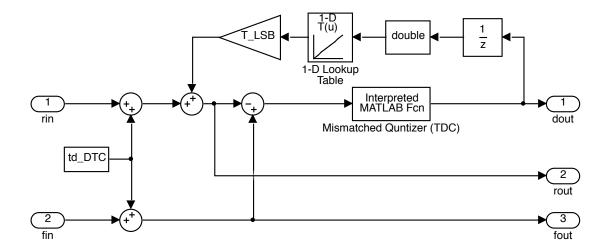

A top-level Simulink block diagram of the proposed time-based  $\Delta\Sigma$  ADC is shown in Fig. 4.1. Individual sub-blocks of the model are shown in Figs. 4.2, 4.3, 4.4, and 4.5. The model uses a fixed time-step solver.

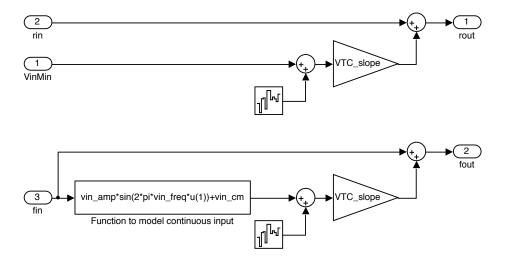

# 4.1.1 VTC/Adder Model

To model the time-varying sampling operation, the VTC/Adder block (Fig. 4.2) converts from continuous-time to discrete-time by evaluating a math-

Figure 4.1: Top-Level Simulink Model of the proposed time-based  $\Delta\Sigma$  ADC ematical sine function at the true sampling instance in each cycle  $(t = f_{in}(k))$ . This is the reason for the absence of an input sine wave in the model of the proposed ADC. Instead, the sine function is evaluated internally in the VTC/Adder block.

#### 4.1.2 Phase Detector Model

The model for the phase detector (Fig. 4.3), keeps track of an ideal external reference clock with period  $T_s$ . In each cycle, the reference is incremented by  $T_s$  and compared to the edge of  $f_{in}$  input to the Phase Detector block. Recall, this is the edge that corresponds to sampling and needs to be uniformly spaced from one cycle to the next. If  $f_{in}$  is within  $\pm T_{d,hyst}$  of the ideal edge, then lead and lag are both 0. Otherwise, one of lead or lag is asserted and the Excess Delay block compensates by adding more or less delay,

Figure 4.2: Simulink model for the VTC/Adder block of the proposed time-based  $\Delta\Sigma$  ADC

respectively. Besides generating lead and lag signals, the Phase Detector block is responsible for startup with a zero width pulse, i.e., same edges for  $r_{out}$  and  $f_{out}$  (in this case ideal clock). Under normal operation, this block only adds a fixed delay to both rise and fall pulses, as evident in the model of Fig. 4.3.

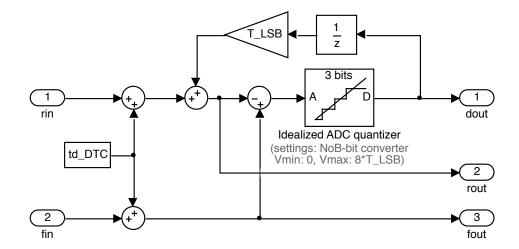

## 4.1.3 TDC/DTC Model

The TDC/DTC block is modeled as shown in Fig. 4.4. In the DTC phase, in addition to adding fixed delay  $(t_{d,DTC})$  to both edges, this block delays the  $r_{in}$  edge by  $T_{LSB} \cdot D_{out}[k-1]$ , effectively shortening the resulting pseudo-differential pulse by the same amount. In the TDC phase, the output of the pseudo-differential pulse from the DTC phase is quantized. This requires taking the time difference between,  $f_{out}$  and  $r_{out}$ , the fall and rise pulses from

Figure 4.3: Simulink model for the Phase Detector block of the proposed time-based  $\Delta\Sigma$  ADC

Figure 4.4: Simulink model for the TDC/DTC block of the proposed time-based  $\Delta\Sigma$  ADC

the DTC phase.

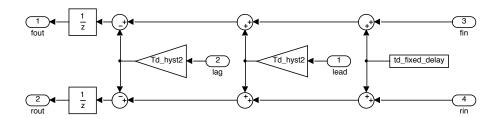

### 4.1.4 Excess Delay Model

The Excess Delay block is modeled according to the block diagram shown in Fig. 4.5. As described in the description of the Phase Detector block, this block compensates for pulse drift due to various delays and the delay modulation due to the input itself. In response to lead and lag signals generated in the Phase Detector block, the Excess Delay block adds or subtracts delay to both edges such that  $f_{out}$  becomes approximately uniformly spaced from cycle to cycle. This effect is seen in the simulation results in Section 4.1.5 below.

Figure 4.5: Simulink model for the Excess Delay block of the proposed time-based  $\Delta\Sigma$  ADC

Table 4.1: Parameters used in the behavioral simulation

| Parameter                     | Value         | Units  |

|-------------------------------|---------------|--------|

| Ts                            | 6.94          | ns     |

| $vin\_freq$                   | 200           | kHz    |

| $vin_amp$                     | 0.18          | V      |

| vin_cm                        | 0.482         | V      |

| $VTC\_slope$                  | 1.5           | nV / s |

| $td\_phase\_detector$         | 0.5           | ns     |

| $\mathrm{td}_{-}\mathrm{DTC}$ | 2.7           | ns     |

| $td\_fixed\_delay$            | 3.025         | ns     |

| $T_LSB$                       | 100           | ps     |

| NoB                           | 3             | _      |

| $	ext{trip\_en}$              | 0/1           | _      |

| $Td_hyst$                     | trip_en & 0.3 | ns     |

| $Td_hyst2$                    | trip_en & 0.4 | ns     |

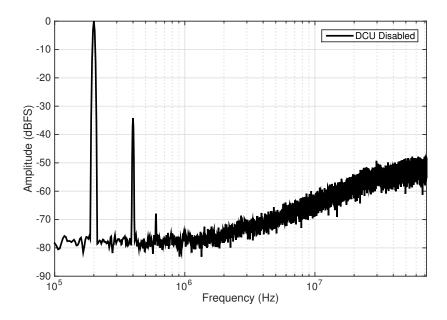

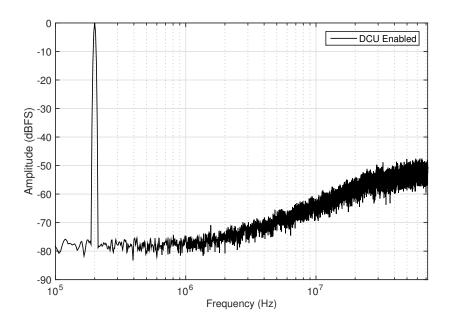

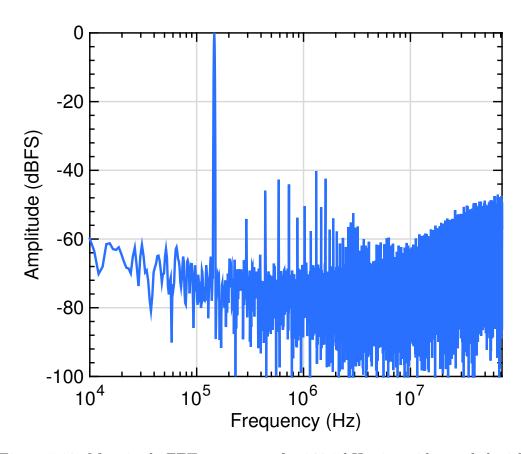

Figure 4.6: Averaged FFT Spectrum of the behavioral model with DCU disabled. Odd harmonics are due to input-dependent modulation of sampling interval when the DCU is disabled.

### 4.1.5 Simulation Results

In this section, simulation results showing the operation of the proposed time-based  $\Delta\Sigma$  ADC is presented. The parameters used in the simulation are listed in Table 4.1. To understand the effectiveness and need for the DCU and loop delay compensation, Td\_hyst and Td\_hyst2 are set to zero first. The resulting spectrum is shown in Fig. 4.6, in which dominant third harmonic of the input sine wave is observed. This is caused by the input-dependent modulation of sampling interval, and results in a total harmonic distortion (THD) of -34 dB. Therefore, the non-uniform sampling needs to be made uniform.

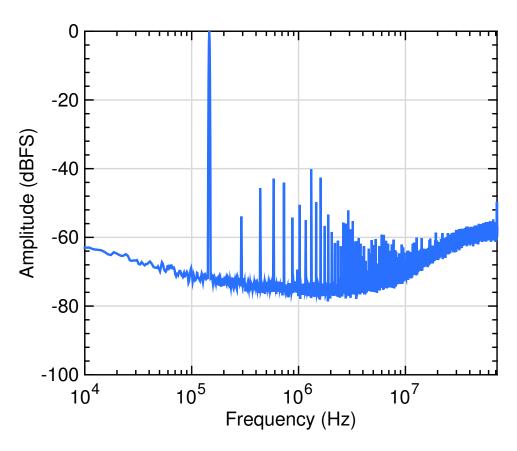

Figure 4.7: Averaged FFT Spectrum of behavioral model with DCU enabled.

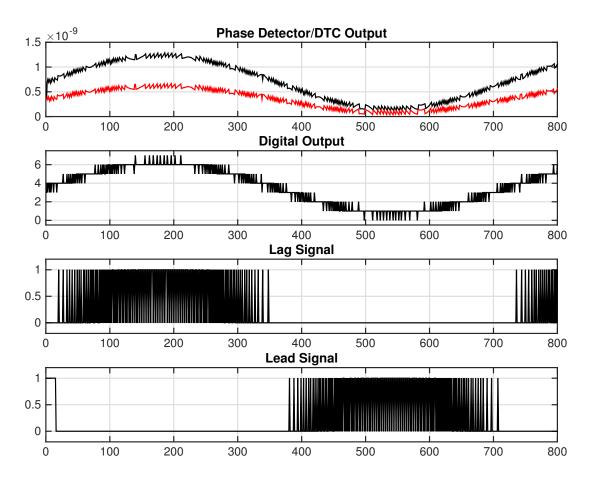

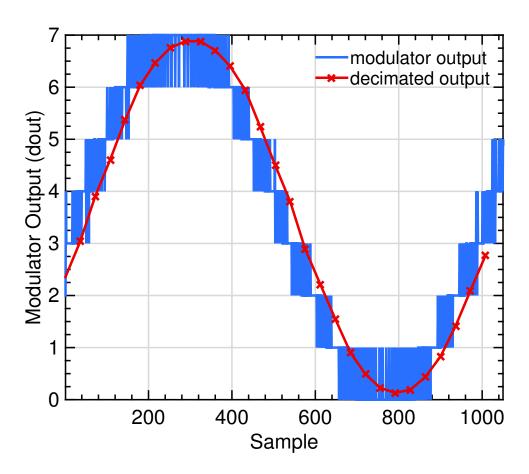

If the DCU is enabled by setting Td\_hyst and Td\_hyst2 to nonzero values with Td\_hyst2 > Td\_hyst, the spectrum of Fig. 4.7 is obtained. Note: the odd harmonics are removed. With the DCU enabled, the sampling interval becomes approximately uniform. A typical waveform showing the operation of the time-based  $\Delta\Sigma$  ADC is shown in Fig. 4.8. As illustrated, when the input is at its highest, the pulse widths at the phase detector output and the DTC output are their highest values. Higher pulse widths create extra delay: therefore, there will be a larger density of lag signals. On the contrary, when the input is at its lowest, the density of lead is highest.

One measurable quantity to better understand the effect of the DCU

Figure 4.8: Waveforms for different signals in the behavioral model of the proposed time-based  $\Delta\Sigma$  ADC.

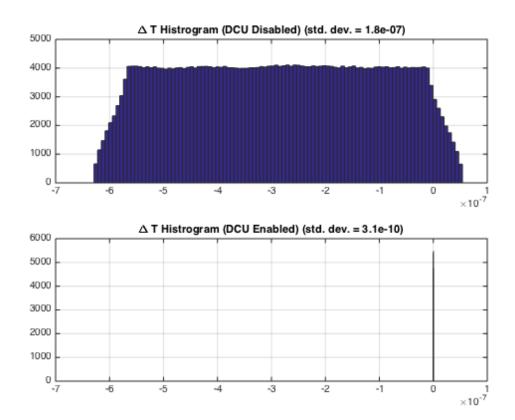

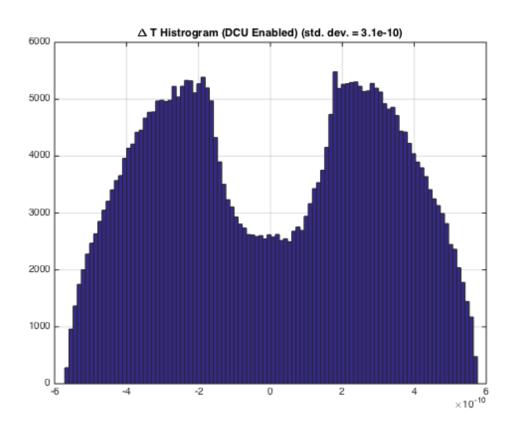

Figure 4.9: Histograms for  $\Delta T = t(f_{\text{out, phase detector}}) - k \cdot T_s$  showing the deviation from ideal sampling times  $k \cdot T_s$  when the DCU is disabled/enabled