# EE382M.20: System-on-Chip (SoC) Design

## Lecture 2 – Electronic System-Level (ESL) Design

with sources from: Christian Haubelt, Univ. of Erlangen-Nuremberg

#### Andreas Gerstlauer

Electrical and Computer Engineering University of Texas at Austin gerstl@ece.utexas.edu

# **SoC Design Challenges**

- Complexity

- High degree of parallelism at various levels

- Heterogeneity

- · Of components

- · Of tools

- Low-level communication mechanisms

- Programming model

Source: C. Haubelt, Univ. of Erlangen-Nuremberg

EE382M.20: SoC Design, Lecture 2

© 2018 A. Gerstlauer

2

## **Lecture 2: Outline**

- ✓ Introduction

- SoC design methodology

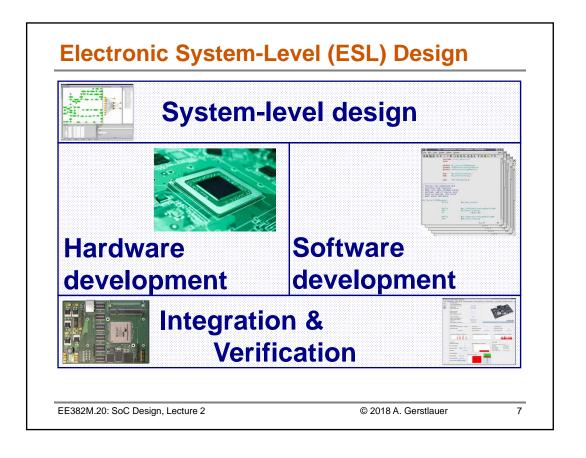

- Electronic system-level design (ESL/SLD)

- System-level design process

- Synthesis

- Modeling

- Summary and conclusions

EE382M.20: SoC Design, Lecture 2

© 2018 A. Gerstlauer

4

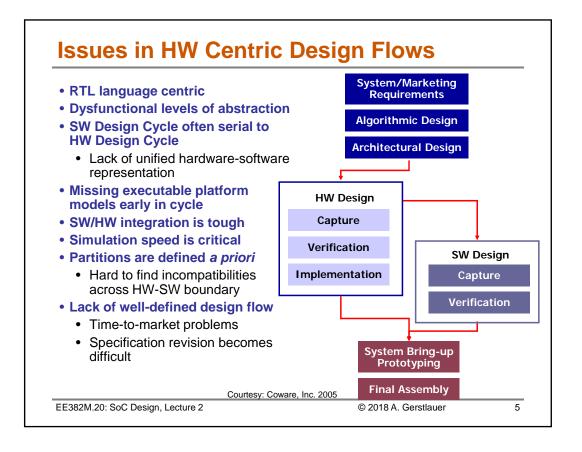

# **Design Methodologies**

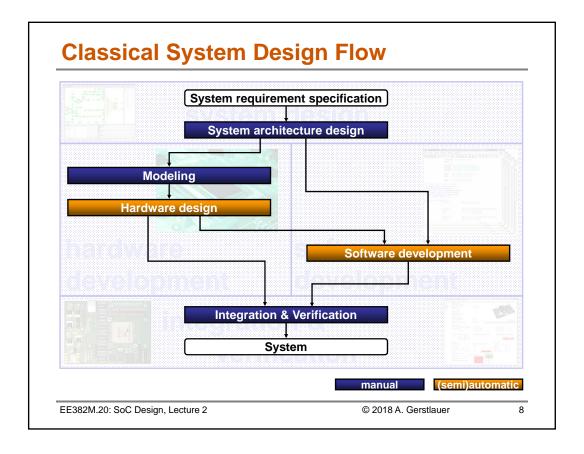

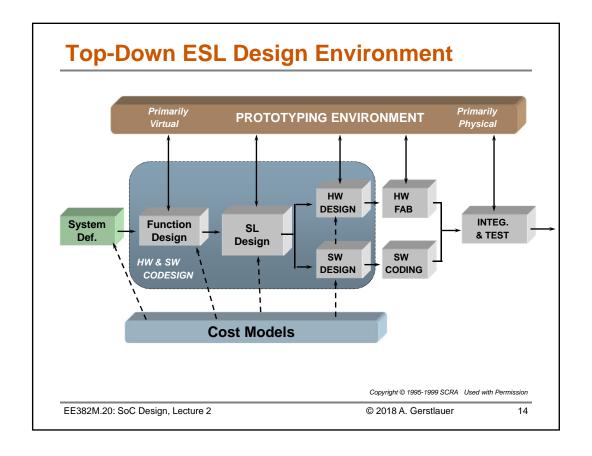

#### Top down design

- Starts with functional system specification

- Application behavior

- Models of Computation (MoC)

- Successive refinement

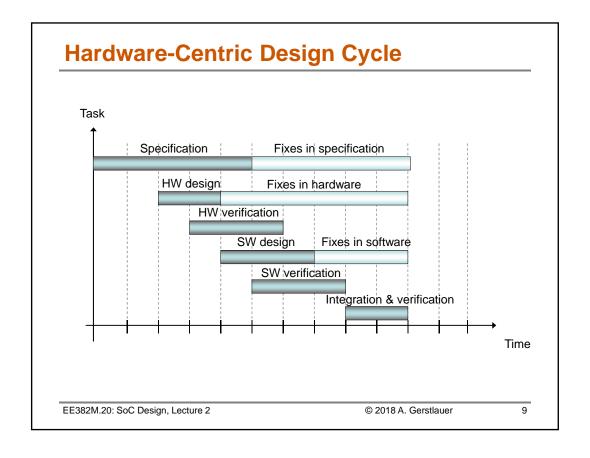

- Connect the hardware and software design teams earlier in the design cycle.

- Allows hardware and software to be developed concurrently

- Goes through architectural mapping

- The hardware and software parts are either manually coded or obtained by refinement from higher model

- Ends with HW-SW co-verification and System Integration

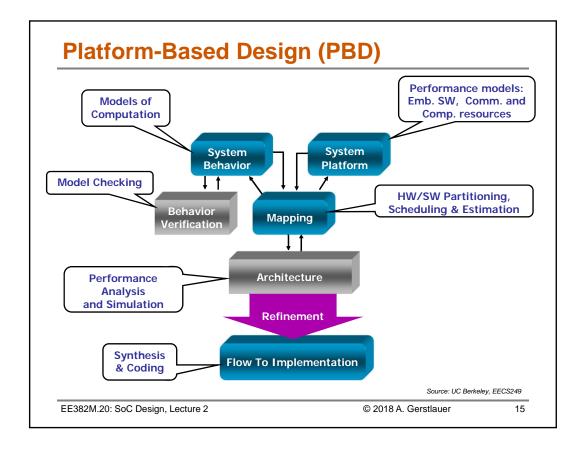

#### Platform based design

- Starts with architecting a processing platform for a given vertical application space

- Semiconductor, ASSP vendors

- Enables rapid creation and verification of sophisticated SoC designs variants

- PBD uses predictable and preverified firm and hard blocks

- PBD reduces overall time-tomarket

- Shorten verification time

- Provides higher productivity through design reuse

- PBD allows derivative designs with added functionality

- Allows the user to focus on the part that differentiate his design

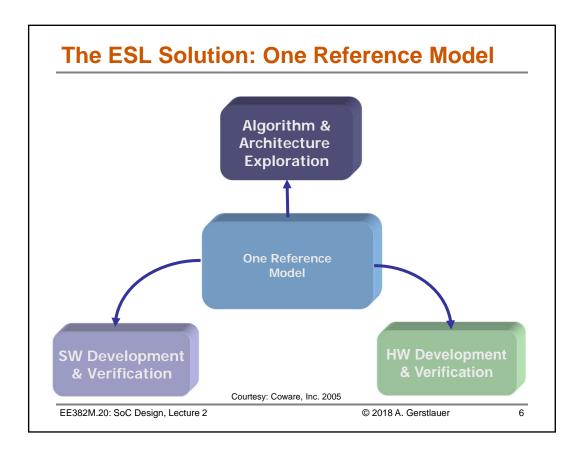

Source: Coware, Inc., 2005

EE382M.20: SoC Design, Lecture 2

© 2018 A. Gerstlauer

13

## **Lecture 2: Outline**

- **✓ Introduction**

- √ SoC design methodology

- System-level design

- Synthesis

- Modeling

- Summary and conclusions

EE382M.20: SoC Design, Lecture 2 © 2018 A. Gerstlauer

16

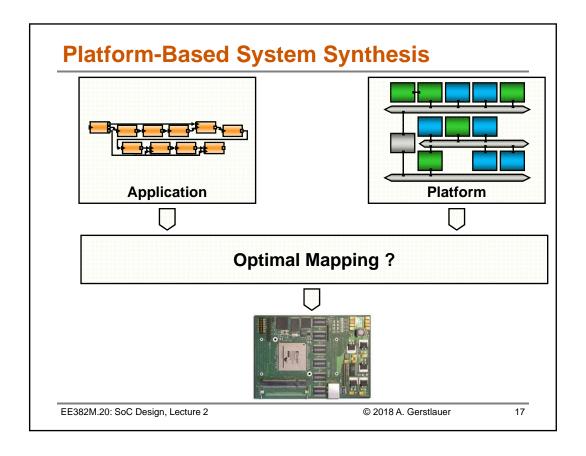

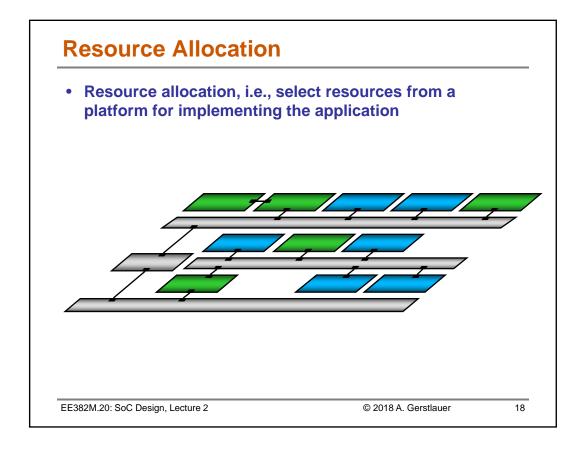

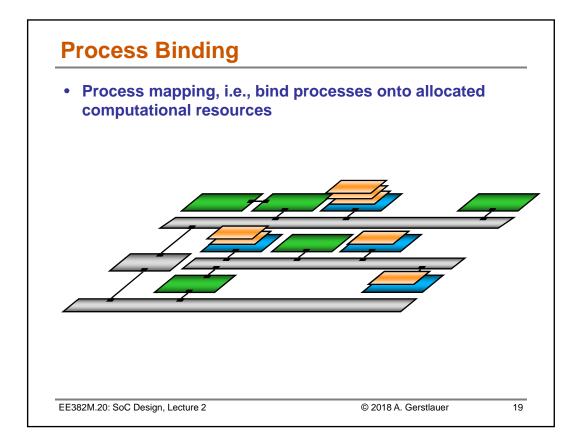

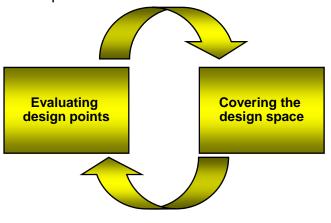

# **Design Space Exploration**

- Design Space Exploration is an iterative process:

- How can a single design point be evaluated?

- How can the design space be covered during the exploration process?

EE382M.20: SoC Design, Lecture 2

© 2018 A. Gerstlauer

21

## **Lecture 2: Outline**

- ✓ Introduction

- ✓ SoC design methodology

- System-level design

- √ Synthesis

- Modeling

- Summary and conclusions

EE382M.20: SoC Design, Lecture 2

© 2018 A. Gerstlauer

22

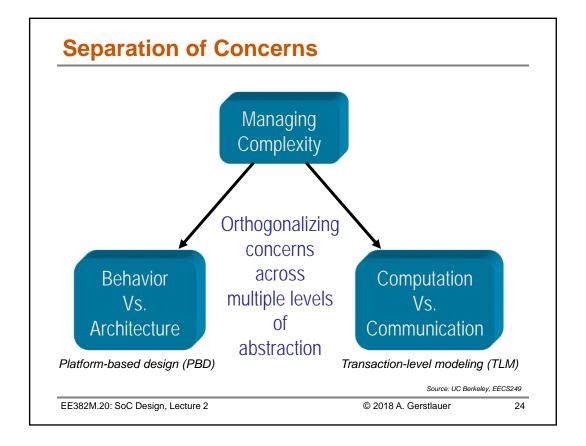

## System Modeling

- Design models as abstraction of a design instance

- Representation for validation and analysis

- Specification for further implementation

- Documentation & specification

#### Systematic methodology

- Set of models and transformations (design steps)

- Modeling flow defines the design process

- From specification to implementation

#### Well-defined, rigorous semantics

- · Unambiguous, explicit abstractions

- Formal models

- > Synthesis and verification

EE382M.20: SoC Design, Lecture 2

© 2018 A. Gerstlauer

23

14

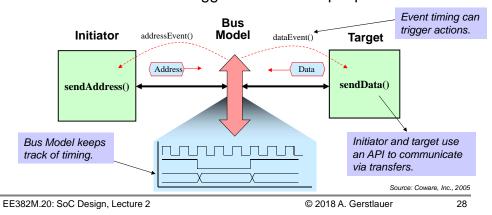

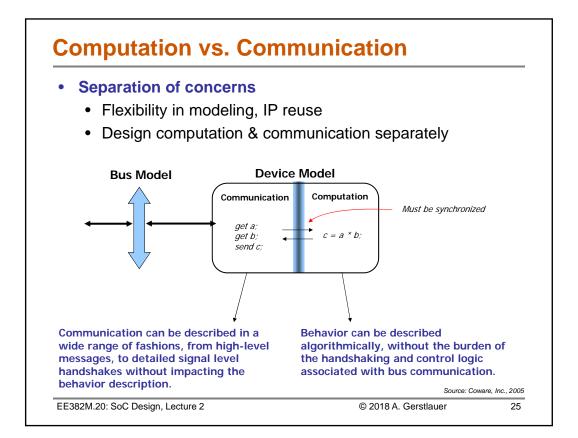

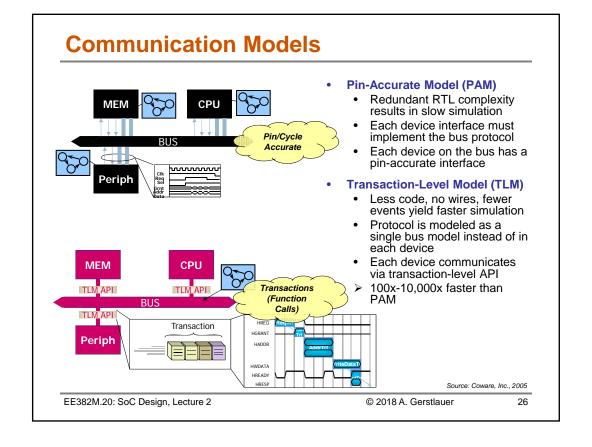

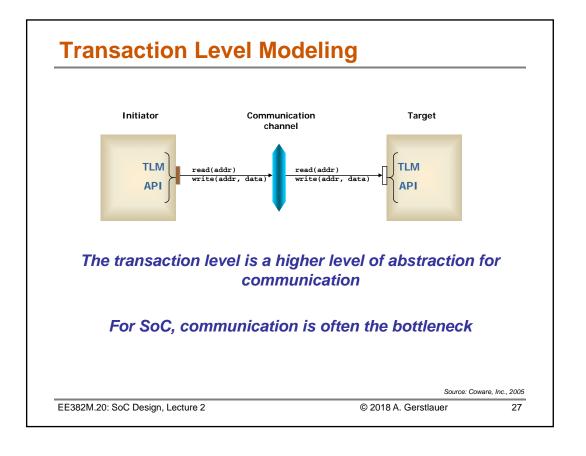

# TLM Details

- Abstracted communication

- Detailed signal handshaking is reduced to series of generic events called "transactions".

- Blocks are interconnected via a bus model, and communicate through an API.

- The bus model handles all the timing, and events on the bus can be used to trigger action in the peripherals.