## **SpecC Modeling Guidelines**

Andreas Gerstlauer

Technical Report ICS-00-48 August 6, 2001

Center for Embedded Computer Systems University of California, Irvine Irvine, CA 92697-3425, USA (949) 824-8059

> gerstl@cecs.uci.edu http://www.cecs.uci.edu/~gerstl

## **SpecC Modeling Guidelines**

Andreas Gerstlauer

Technical Report ICS-00-48 August 6, 2001

Center for Embedded Computer Systems University of California, Irvine Irvine, CA 92697-3425, USA (949) 824-8059

> gerstl@cecs.uci.edu http://www.cecs.uci.edu/~gerstl

#### Abstract

Raising the level of abstraction to the system level has been touted as the main solution for closing the productivity gap designers of embedded systems-on-chip (SOCs) are facing increasingly. However, in order to achieve the required productivity gains, a well-defined methodology enabling a synthesis-oriented flow is necessary. The basis for every methodology are clear and unambiguous models at different levels of abstraction.

In this report, we will define the four models that comprise the SpecC system-level design methodology. Using actual code templates, we will show their features and properties in detail. All together, this report provides comprehensive guidelines for modeling a design at each level. In addition to standardizing manually written models, the exact definition of the models builds the basis of all automated tools for exploration, refinement, synthesis or verification.

## Contents

| 1  | Intro | oduction                      | 1  |

|----|-------|-------------------------------|----|

|    | 1.1   | System Design Flow            | 2  |

|    | 1.2   | SpecC Methodology             | 3  |

|    | 1.3   | SpecC Language                | 4  |

| 2  | Spec  | cification Model              | 4  |

|    | 2.1   | Specification Model Example   | 4  |

|    | 2.2   | Concurrency                   | 5  |

|    | 2.3   | Communication                 | 6  |

|    | 2.4   | Summary                       | 7  |

| 3  | Arcl  | hitecture Model               | 9  |

| •  | 3.1   | Architecture Model Example    | 9  |

|    | 3.2   | Storage                       | 11 |

|    | 5.2   | 3.2.1 Local Memory            | 11 |

|    |       | 3.2.2 Global Memory           | 11 |

|    | 3.3   | Synchronization               | 13 |

|    | 3.4   | IP Components                 | 14 |

|    | 3.5   | Scheduling                    | 16 |

|    | 3.6   | Time                          | 17 |

|    | 3.7   | Summary                       | 17 |

|    |       |                               |    |

| 4  | Com   | nmunication Model             | 18 |

|    | 4.1   | Communication Model Example   | 18 |

|    |       | 4.1.1 Bus Wires               | 20 |

|    |       | 4.1.2 Bus Adapters            | 20 |

|    | 4.2   | Protocol Layer                | 21 |

|    | 4.3   | Application Layer             | 23 |

|    |       | 4.3.1 Synchronization         | 23 |

|    |       | 4.3.2 Addressing              | 25 |

|    |       | 4.3.3 Data slicing            | 25 |

|    | 4.4   | Transducers                   | 25 |

|    | 4.5   | Arbitration                   | 27 |

|    | 4.6   | Timing                        | 29 |

|    | 4.7   | Summary                       | 30 |

| 5  | Imp   | lementation Model             | 30 |

|    | 5.1   | Behavioral RTL                | 31 |

|    |       | 5.1.1 Custom Hardware         | 31 |

|    |       | 5.1.2 Programmable Processors | 33 |

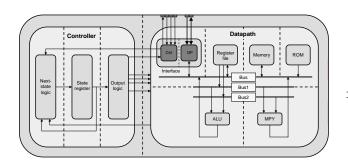

|    | 5.2   | Structural RTL                | 34 |

|    |       | 5.2.1 Clock                   | 35 |

|    |       | 5.2.2 Controller              | 35 |

|    |       | 5.2.3 Datapath                | 36 |

|    |       | 5.2.4 Bus Interface           | 37 |

|    | 5.3   | Summary                       | 39 |

| 6  | Sum   | nmary and Conclusions         | 39 |

|    |       | •                             |    |

| Ke | feren | ices                          | 39 |

# List of Figures

| 1  | Y-Chart                                                               |

|----|-----------------------------------------------------------------------|

| 2  | SpecC methodology                                                     |

| 3  | SpecC models in the Y-Chart                                           |

| 4  | Specification model                                                   |

| 5  | Specification model with explicit dependencies                        |

| 6  | Specification model with message-passing communication                |

| 7  | Architecture model                                                    |

| 8  | Shared memory architecture model                                      |

| 9  | Architecture model with multiple inter-component behavior transitions |

| 10 | Architecture model with IP                                            |

| 11 | Communication model                                                   |

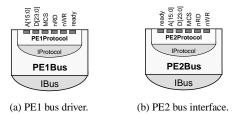

| 12 | PE bus adapters                                                       |

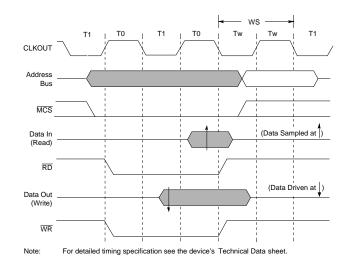

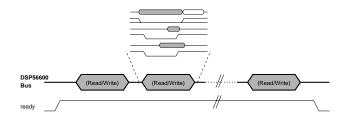

| 13 | DSP56600 protocol timing diagram                                      |

| 14 | Application layer synchronization protocol                            |

| 15 | Communication model with IP                                           |

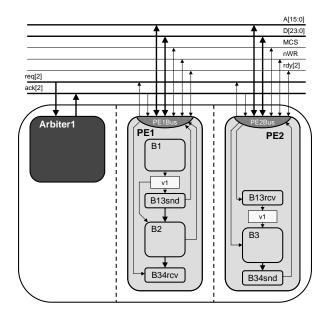

| 16 | Communication model with arbiter                                      |

| 17 | Implementation model                                                  |

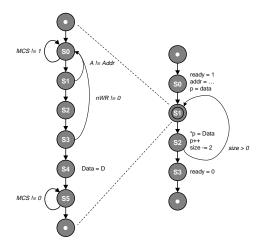

| 18 | Custom hardware bus interface FSMD                                    |

| 19 | Structural RTL model for custom hardware                              |

# List of Listings

| 1  | Specification model.                                    | 5  |

|----|---------------------------------------------------------|----|

| 2  | Specification model with explicit dependencies.         | 6  |

| 3  | Message-passing channel.                                | 7  |

| 4  | Specification model with message-passing communication. | 7  |

| 5  | Architecture model                                      | 10 |

| 6  | Shared memory architecture model.                       | 12 |

| 7  | Global memory component.                                | 12 |

| 8  | Shared memory accesses in leaf behaviors                | 13 |

| 9  | IP component model.                                     | 15 |

| 10 | Architecture model with IP                              | 16 |

| 11 | IP accesses in leaf behavior <i>B3</i>                  | 16 |

| 12 | Behavior timing.                                        | 17 |

| 13 | Communication model.                                    | 19 |

| 14 | Signal channel for modeling of wires.                   | 20 |

| 15 | PE bus adapter interface.                               | 21 |

| 16 | Bus adapter protocol layer.                             | 22 |

| 17 | Bus adapter application layer.                          | 24 |

| 18 | Communication model with IP.                            | 26 |

| 19 | Transducer component model.                             | 27 |

| 20 | Communication model with arbiter.                       | 28 |

| 21 | Bus adapter with arbitration.                           | 28 |

| 22 | Arbiter component model.                                | 29 |

| 23 | Implementation model.                                   | 30 |

| 24 | Custom hardware behavioral RTL model.                   | 31 |

| 25 | Custom hardware bus interface FSMD                      | 32 |

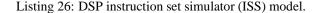

| 26 | DSP instruction set simulator (ISS) model.              | 34 |

| 27 | Structural RTL model for custom hardware.               | 35 |

| 28 | Clock generator.                                        | 35 |

| 29 | Custom hardware controller.                             | 36 |

| 30 | State register.                                         | 36 |

| 31 | Output logic.                                           | 36 |

| 32 | Next state logic.                                       | 36 |

| 33 | Custom hardware datapath.                               | 37 |

| 34 | Bus interface hardware unit.                            | 38 |

| 35 | Bus interface controller                                | 38 |

## **SpecC Modeling Guidelines**

A. Gerstlauer

Center for Embedded Computer Systems University of California, Irvine Irvine, CA 92697-3425, USA

#### Abstract

Raising the level of abstraction to the system level has been touted as the main solution for closing the productivity gap designers of embedded systems-on-chip (SOCs) are facing increasingly. However, in order to achieve the required productivity gains, a well-defined methodology enabling a synthesis-oriented flow is necessary. The basis for every methodology are clear and unambiguous models at different levels of abstraction.

In this report, we will define the four models that comprise the SpecC system-level design methodology. Using actual code templates, we will show their features and properties in detail. All together, this report provides comprehensive guidelines for modeling a design at each level. In addition to standardizing manually written models, the exact definition of the models builds the basis of all automated tools for exploration, refinement, synthesis or verification.

## **1** Introduction

The design of embedded computer systems is the process of implementing a given specification of the desired system on a chip in silicon. Following a formal methodology, defined as a set of models and a set of transformation between the models, the design is gradually refined to lower and lower levels of abstraction.

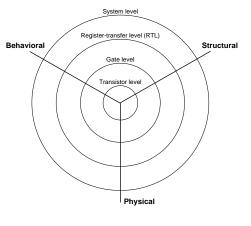

As depicted by the Y-Chart (Figure 1), four general layers of abstraction are commonly distinguished [1]:

- (a) System level

- (b) Register-transfer level (RTL)

- (c) Gate level

- (d) Transistor level

With lower levels, the design process focuses on more and more detailed aspects of the system. At each level, the designer works with a specific set of objects. Objects at higher levels of abstraction are hierarchically composed

Figure 1: Y-Chart.

of lower-level design objects. For example, at the system level, components of the system architecture are processing elements (PEs) and system busses. At the registertransfer level, in turn, the microarchitecture of PEs is build out of functional units, registers, and so on.

At each layer, the design object at that level can be described or modeled in three different views:

(a) A *behavioral view* describes the functionality of the design in terms of abstract concepts, independent of any implementation details.

Building blocks of a behavioral description are abstract entities that do not represent physical components. Each block describes a piece of functionality that takes inputs, processes them and finishes after producing its output. In a behavioral view, such blocks are then arranged hierarchically to model the control and data dependencies between them.

Parallelism in a behavioral description does not imply true concurrency in hardware. Again, behavioral blocks are abstract representations of algorithms that are free of implementation assumptions.

(b) A *structural view* describes the design as a netlist of lower-level components and their connectivity.

Building blocks of a structural description represent real, physical objects that are connected via wires. As such, each of the blocks is active all the time, constantly processing data. In a structural view, the system is then modeled as a set of non-terminating, concurrent processes representing the way the system is composed out of tangible lower-level components. Dependencies have to be modeled as part of the processes' functionality by inserting synchronization as needed.

Since the processes of a structural description represent real hardware, the parallel composition of the processes reflects the true concurrency available among the set of physical components on the chip or the board.

(c) A *physical view* describes the spatial layout of the lower-level components on the chip. A physical view describes the floorplan of how the components and their interconnect are placed and routed on the chip.

Points in the Y-Chart form specific levels of abstracting a design. In addition to the amount of structure as shown by the layers and views of the Y-Chart, models of the design at certain abstraction levels are defined by the amount of order in the model.

In general, given two events  $e_1$  and  $e_2$ , where an event  $e_i$ is a tuple  $(a_i, t_i)$  of action  $a_i$  occurring at time  $t_i$ ,  $e_1$  and  $e_2$ are ordered iff it can be determined that  $t_1 < t_2$  or  $t_2 < t_1$ . A system is totally ordered if all pairs of events are ordered as is the case with real time on the chip, for example. A system is partially ordered if only subsets of all events are ordered. For example, at higher levels, a relationship between independent parts is not specified. An abstraction level employs a model of time to specify order. Real time is abstracted as discrete logical time. Two unordered events are modeled to occur at the same logical time, leaving the freedom of implementing them in any oder in real time.

#### 1.1 System Design Flow

Design is the process of moving from a behavioral to a structural (and eventually physical) description at a certain level, implementing the desired functionality through an architecture of subcomponents. The subcomponents, in turn, are designed by moving from a behavioral description to a structural (and physical) description of the subcomponent at the next lower level of abstraction. For example, at the system level, the designer will create a system architecture consisting of a set of processing elements (PEs) connected through system busses that implements the desired system functionality. The processing element's functionality, in turn, is implemented by designing a microarchitecture of functional units, registers files, and so on for the PE at the register-transfer level.

A design flow can be bottom-up or top-down. In a bottom-up approach, design moves from the lowest level of abstraction up to the system level by assembling previously designed components such that the desired behavior is achieved at each level. In a top-down approach, design starts with a specification of the system behavior and moves down in the level of abstraction by mapping the desired behavior at each level onto a set of components and specifying the behavior of each component for the next level.

In order to automate the design process with CAD tools, the models and transformations of the design methodology must be formalized. Languages with special support to describe different views of the design at different levels of abstraction in a formal and efficient manner are needed. In addition to the application of formal methods for verification, an executable language allows validation through simulation of the models.

Once the models for the different design views at different abstraction levels are formally defined, CAD tools can automate parts of the design process. Specifically, the formalized process of deriving a structural description from a behavior description of the desired functionality is called *synthesis*. The synthesis processes at the highest levels of abstraction are:

(a) System synthesis

Given a specification of the system behavior, synthesize a system architecture consisting of processing elements and system busses that implements the desired functionality.

(b) High-level/behavioral synthesis

Given a behavioral description of a PE, synthesize a microarchitecture implementation out of RTL components like functional units, register files, and so on.

(c) Logic synthesis

Given a description of the functionality of an RTL component, synthesize a gate netlist that implements the combinatorial/sequential logic for the component.

In this report, we formalize the different models of the SpecC system-level design methodology, representing different views of the design at different levels of abstraction. The SpecC methodology covers system and registertransfer levels of abstraction. Formalizing the models of the methodology forms the basis for developing the corresponding system-level and high-level synthesis tools.

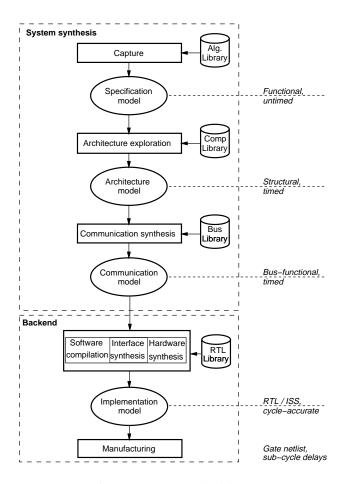

Figure 2: SpecC methodology.

#### 1.2 SpecC Methodology

The SpecC system-level design methodology is shown in Figure 2. The SpecC methodology is a set of four models and three transformation steps that take a system specification down to an RTL implementation [2].

The SpecC design flow consists of two main parts: (a) system synthesis, and (b) a backend for high-level synthesis and compilation. In the SpecC methodology, system synthesis is further subdivided into two orthogonal tasks, architecture exploration and communication synthesis. Architecture exploration implements the computation behavior of the specification on a set of processing elements that form the system architecture. Communication synthesis, on the other hand, implements the communication functionality of the specification over the system busses.

Each system synthesis and backend task refines the model of the design at the current stage of the design process into a new model representing the details of the implementation added during the synthesis step. At the output of each task, the model of the design reflects the implementation decisions made in the previous step. At the same time, each model forms the input to the next task.

The system-level design process starts off with a specification of the desired system behavior. This specification model is written by the user and forms the input to the design process. It is purely functional and free of any implementation details. There is no notion of time yet and only a purely causal ordering of events, i.e. events in the system are limited to synchronization events only which are needed to ensure causality.

In the SpecC methodology, the first task of system synthesis is architecture exploration. Architecture exploration selects a set of processing elements and maps the computation behavior of the specification onto the PEs. Architecture exploration refines the specification model into the intermediate architecture model. The architecture model describes the PE structure of the system architecture and the mapping of computation behaviors onto the PEs, including estimated execution times for the behavior of each PE.

Architecture exploration is followed by communication synthesis to complete the system synthesis process. Communication synthesis selects a set of system busses and protocols, and maps the communication functionality of the specification onto the system busses. Communication synthesis creates the communication model which reflects the bus architecture of the system and the mapping of communication onto the busses.

The communication model is the result of the system synthesis process. It describes the structure of the system architecture consisting of PEs and busses, and the implementation of the system functionality on this architecture. It is timed in both computation and communication, i.e. simulation detail is increased by events for estimated execution and communication delays.

The communication model is a structural view at the system level. At the same time, the specification of the functionality of each PE of the system in the form of a behavioral view at the register-transfer level forms the input to the RTL synthesis of those components in the backend. In a hierarchical fashion, each PE is synthesized separately in the backend and the behavioral view of the PE is replaced with a structural view of its RTL or instruction-set (IS) microarchitecture. The result of this backend process is the implementation model.

The implementation model is a cycle-accurate, structural description of the RTL/IS architecture of the whole system. In a hierarchical fashion, the implementation model describes the system structure and the RTL structure of each PE in the system. Simulation detail is increased down to the clock level, i.e. the timing resolution is in terms of clock events for each local PE clock.

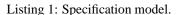

Figure 3: SpecC models in the Y-Chart.

Figure 3 summarizes the four models of the SpecC methodology by their position in the views and abstraction layers of the Y-Chart.

#### 1.3 SpecC Language

The SpecC methodology is supported by the SpecC system-level design language [2]. The SpecC language was developed to satisfy all the requirements for an efficient formal description of the models in the SpecC methodology. It supports behavioral and structural views and contains features for describing a design at all levels of abstraction.

In general, at all levels of abstraction, behavioral and structural views of a SpecC behavior at any point in the code hierarchy are defined as follows:

- (a) A behavioral view is modeled as a serial-parallel composition of behaviors. Behaviors terminate after they are finished processing the current input data set and producing corresponding outputs. Behaviors are then arranged hierarchically to explicitly model data and control flow between blocks, describing the desired functionality.

- (b) A structural view is defined as a set of nonterminating, communicating, and concurrent behaviors representing the tangible components of the architecture. In SpecC, a structural description is a parallel decomposition of a behavior into subbehaviors that each execute in endless loops and communicate through ports and variables, events, or channels.

Starting with the system behavior description at the top level, behavioral views are replaced with structural views as design progresses down to lower levels.

In the SpecC methodology, all four models of the design process starting with the specification model and down to the implementation model are written and described in the SpecC language. One common language removes the need for tedious translation. Furthermore, all the models in SpecC are executable which allows for validation through simulation, reusing one single testbench throughout the whole design flow. In addition, the formal nature of the models enables application of formal methods, e.g. for verification or equivalence checking.

The purpose of this report is to define the four different models of the SpecC methodology within the framework of the SpecC language and to define how each model is described in SpecC. Based on code templates and examples, we will give guidelines for modeling implementation details available at each level of abstraction and in each design view.

The rest of this report is organized as follows: the report starts with a description of the specification model in Section 2. Section 3 and Section 4 detail the architecture and communication models, respectively. Finally, Section 5 introduces the major aspects of the implementation model. The report then concludes with a summary in Section 6.

## 2 Specification Model

The specification model is the input of architecture exploration. It is written by the user to specify the desired system functionality. The specification is a behavioral view of the system, i.e. it describes the desired functionality in an abstract manner. The specification model is a purely functional model, free of any implementation details. For example, objects at the specification level are abstract entities that do not correspond to real components.

In general, the specification is hierarchically composed of behaviors. Behaviors are arranged sequentially, concurrently, or in a mix of both, i.e. in a pipelined fashion. Behaviors at the leaves of the hierarchy contain basic algorithms that perform arithmetic and logical operations on data. In addition to temporary data, leaf behaviors will encapsulate any permanent storage required by the algorithm.

The ordering of events in the system is based on causal relationships only and there is no notion of time. The system is partially ordered based on causality as determined by the dependencies between behaviors. Simulation detail is limited to events used for synchronization to ensure causality.

#### 2.1 Specification Model Example

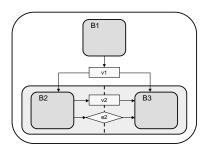

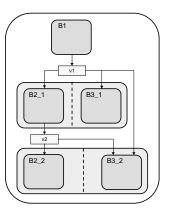

Figure 4 shows an example of a simple yet typical specification model. The corresponding SpecC code is shown in Listing 1. The design is a hierarchical, serial-parallel composition of behaviors. In the example, behavior B1 is followed by the parallel composition of behaviors B2 and B3. The three leaf behaviors B1, B2, and B3 contain algorithms in the form of C code.

```

11

leaf behavior

1

behavior B1( out type1 v1 )

ł

void main(void) {

5

= ...

v1

};

10 // leaf behavior

2

behavior B2( in

type1 v1,

out type2 v2,

out event e1 )

15

void main(void) {

v^2 = f^2 (v^1, \dots);

notify ( e1 );

20

}

};

// leaf behavior

3

behavior B3( in

type1 v1,

type2 v2,

25

in

in

event e1)

ł

void main(void) {

30

wait ( e1 );

f3 ( v1, v2, ... );

. . .

}

};

35

B2 B3

behavior B2B3( in type1 v1 )

type2 v2;

40

event e1;

B2 b2 ( v1, v2, e1 );

B3 b3 ( v1, v2, e1 );

45

void main (void)

par { b2.main();

b3.main(); \}

3

};

50 // Top-level

behavior Design ()

type1 v1;

55

B1

b1 (v1);

B2B3 b2b3 (v1);

void main(void) {

b1.main();

60

b2b3.main();

}

};

```

Figure 4: Specification model.

Behaviors communicate through variables attached to their ports. Synchronization of concurrent behaviors is handled through events connected to behavior ports. In this case, behavior B1 produces the variable v1 of type type1 at its output The variable is passed into B2 and B3 by connecting v1 to the corresponding inputs of those two behaviors. The concurrent behaviors B2 and B3 communicate through the variable v2 (of type type2) and the event e1. Behavior B2 writes to v2 and notifies B3 when the data is ready. Behavior B3 in turn waits for event notification before reading from variable v2.

#### 2.2 Concurrency

In general, concurrent behaviors in the specification model should reflect the available parallelism in the specification. Therefore, they should be as independent as possible. Data or control dependencies between behaviors at the specification level should be explicitly captured through the behavior hierarchy. Instead of concurrent behaviors that communicate or synchronize through variables or events, the behaviors should be split into independent parts that can run in parallel and dependent parts that have to be executed sequentially.

Figure 5 and Listing 2 show the specification model example after splitting the concurrent behaviors B2 and B3 to explicitly model the data dependency through the serialparallel behavior hierarchy. Instead of synchronization via the event e1, the dependency on variable v2 is represented by executing the corresponding parts of the behaviors sequentially.

Note, however, that the modified example introduces an artificial dependency between behaviors  $B3\_1$  and  $B2\_2$ . Depending on the actual implementation, this dependency might result in an unnecessary delay before the execution of behavior  $B2\_2$ . Therefore, the tradeoff between implicit versus explicit parallelism and dependencies will determine whether to cut or combine concurrent threads.

```

leaf behavior 2, two parts

behavior B2_1 ( in type1

v1.

out type2 v2 )

5

void main(void) {

v2 = f2 (v1, ...);

10 behavior B2_2( in type2 v2 )

void main(void) {

15};

// leaf behavior 3, two parts

behavior B3_1 ( in type1 v1 )

20

void main(void) {

. . .

}

}:

behavior B3_2( in

type1 v1.

25

in

type2 v2)

void main(void) {

f3 ( v1, v2, ... );

30

};

// B2 || B3, two parts

behavior B2B3_1 ( in type1 v1,

35

out type2 v2 )

ł

B2_1 b2(v1, v2);

B3_1 b3 (v1);

40

void main(void) {

par { b2.main();

b3. main (): \}

behavior B2B3_2( in

type1 v1,

45

in

type2 v2)

ł

B2_2 b2(v2);

B3_2 b3 (v1, v2);

void main(void) {

50

par { b2.main();

b3.main(); \}

};

55 // Top-level

behavior Design ()

type1 v1;

type2 v2;

60

b1

( v1 );

B2B3_1 b23_1 ( v1, v2 );

B2B3_2 b23_2 ( v1, v2 );

65

void main(void) {

b1.main();

b23_1.main();

b23_2.main();

70 };

```

Listing 2: Specification model with explicit dependencies.

Figure 5: Specification model with explicit dependencies.

#### 2.3 Communication

If the relationship of concurrent behaviors in the specification model extends beyond synchronization through pure events and necessitates some actual form of data communication, the specification needs to clearly separate such communication from the normal computation by encapsulating communication functionality in the form of channels.

In general, behaviors at the specification level communicate via message-passing channels. Behaviors exchange data by sending and receiving messages over communication channels with appropriate semantics. In the case of a sequential composition, message-passing degenerates to simple variables. Data is exchanged by reading and writing from/to the variable. In the case of a parallel composition with simple synchronization only, the synchronization is implemented via a single event. In the general case of data communication between concurrent behaviors, however, a message-passing channel is instantiated.

The specification model instantiates channels out of a SpecC channel library. The library contains channels with abstract communication semantics like buffered and unbuffered message-passing, FIFOs, shared-memory semaphores/mutexes, and so on. By using the predefined channels out of the library, commonly needed communication functionality is available for integration into the specification model.

The simulation model for a channel with blocking message-passing semantics for messages of arbitrary type is shown in Listing 3. Both, the send() and recv() methods block the sender and receiver until the other end acknowledges receipt or signals readiness to complete the data communication. The double-handshake protocol inside the channel effectively implements the rendevouz-style semantics of blocking message-passing.

Note that the simulation model of the channel does not

```

interface ISend

void send ( void * data , int size );

interface IRecv {

void recv( void * data, int size );

5

};

channel ChMP() implements ISend, IRecv

10

void

* buf = 0;

11

temporary buffer

// handshake

event

eReady, eAck;

events

// blocking send

void send ( void * data, int size ) {

15

// copy data to temp. buffer

buf = malloc ( size );

memcpy ( buf, data, size );

// notify receiver

notifyone ( eReady );

20

// wait for acknowledge

wait ( eAck );

}

// blocking receive

type2 recv( void * data, int size ) {

25

// wait for data

while ( ! buf ) wait ( eReady );

// read data from temp. buffer

memcpy( data, buf, size );

free ( buf );

30

// acknowledge receipt

buf = 0;

notify ( eAck );

}

};

```

Listing 3: Message-passing channel.

imply any specific implementation of the message-passing semantics. The code inside the channel is for simulation of the correct semantics during execution only. It is the task of communication synthesis to refine those abstract channels into an actual implementation of the desired semantics using the available system bus protocols and PE interfaces.

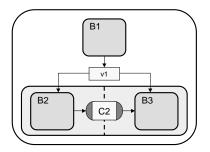

An example of the specification model which uses an abstract message-passing channel for communication between the concurrent behaviors *B2* and *B3* is shown in Figure 6 and Listing 4. The global variable *v2* and event *e1* are replaced with a message-passing channel *C2* that connects the two concurrent behaviors *B2* and *B3* via the channel's sender and receiver interfaces *ISend* and *IRecv*.

Inside the concurrent leaf behaviors B2 and B3, the algorithms operate on local copies of the variable v2. Whenever the copies of v2 need to be updated, they are transfered between the behaviors by calling the *send()* and *recv()* methods of the channel.

#### 2.4 Summary

The purpose of the specification model is to clearly and unambiguously described the system functionality. The specification model is free of any implementation issues. It is

Figure 6: Specification model with message-passing communication.

```

leaf behavior 2

behavior B2( in type1 v1, ISend c2 ) {

void main(void) {

type2 v2;

5

v2 = f2 (v1, ...);

// send message

c2.send(&v2, sizeof(v2));

10

. . .

}

};

// leaf behavior 3

15 behavior B3( in type1 v1, IRecv c2 )

ł

void main(void) {

type2 v2;

20

// receive message

c2.recv(\&v2, sizeof(v2));

f3 (v1, v2, ...);

. . .

}

25 };

// B2 || B3

behavior B2B3( in type1 v1 ) {

ChMP c2;

// message-passing channel

30

B2 b2 ( v1, c2 );

B3 b3 (v1, c2);

void main(void) {

35

par { b2.main();

b3.main(); \}

};

// Top-level

40 behavior Design () {

type1 v1;

B1

b1 (v1);

B2B3 b2b3 (v1);

45

void main(void) {

b1.main();

b2b3.main();

50 };

```

Listing 4: Specification model with message-passing communication. a purely behavioral model specifying the desired functionality of the system. Any hierarchical, serial-parallel composition of behaviors is allowed without implying anything about the structure of the system architecture.

Through the specification model, the user defines the basis for synthesis and exploration. Therefore, the quality of the specification model is critical. Synthesis results can always only be as good as the input description. General guidelines for the specification model are:

**Hierarchy** At each level of hierarchy, the system should be composed of self-contained blocks with welldefined interfaces enabling easy composition, rearrangement, and reuse. Closely related functionality is grouped through hierarchy. Higher-level behaviors encapsulate tightly coupled groups of subbehaviors such that the ratio of external to internal communication is minimized. On the other hand, the number of subbehaviors per parent should be kept small and manageable. As a guideline, behaviors typically have 2-5 children on average.

At each level, the behavior hierarchy should be clean. Different behavioral concepts shouldn't be mixed in the same level. A behavior is either a hierarchical composition of subbehaviors or a leaf behavior with sequential code. Similarly, a hierarchical behavior is either a sequential, parallel, pipelined or FSM composition of subbehaviors but does not contain arbitrary C code.

**Granularity** Behaviors at the leaves of the hierarchy define the granularity for exploration. Leaf behaviors contain basic algorithms in the form of C code, reading from their inputs, processing a data set, and producing outputs. An algorithm is a sequence of computational steps that transform the input into the output [3]. Leaf code is split into behaviors along the boundaries defined between reading and writing of data structures. On the other hand, all the code needed to process a complete, consistent data set should be kept together in one leaf behavior.

Also, similar to higher levels of hierarchy, the ratio of communication to computation should be minimized yet the size of the leaf behaviors be kept small and manageable with well-defined, sensible interfaces and possible reuse in mind. As a rule of thumb, what would be a traditional C function will become a leaf behavior with typically half a page to maximally two pages of code.

**Communication** Computation and communication in the specification model are separated into behaviors and

channels, respectively, allowing for a separate implementation of both concepts. Data dependencies should be reflected explicitly in the behavioral hierarchy as transitions between behaviors, either through a sequential composition or conditionally using the f sm statement. In this case, channels degenerate to simple variables connecting behaviors, and the need for implicit synchronization through message-passing is eliminated.

All dependencies are explicitly captured through the connectivity between behaviors and no hidden side effects exist. Global variables should be avoided completely. Static variables accessed from a single leaf behavior become member variables of that behavior. Global variables used for communication have to be turned into explicit dependencies in the form of connectivity as behaviors are only allowed to exchange data through their ports.

**Encapsulation** In general, information should be localized as much as possible. This includes code (functions, methods), storage (variables), and communication (port variables, channels). Each hierarchical unit (behavior) encapsulates and abstracts as many local details as possible, hiding them from the higher levels. Hierarchical behaviors encapsulate dependencies and communication of a group of subbehaviors, providing only an interface to their combined functionality.

At the leaves, behaviors encapsulates all the code and storage needed by the algorithm. As mentioned above, global, static variables become member variables of the leaf behavior. Furthermore, global functions that are called out of leaf behaviors should be avoided. Instead, depending on size and number of callers, consider converting functions into separate leaf behaviors that get instantiated as subbehaviors of the caller, or move global functions into the calling behavior where they become local methods. An exception are small helper functions with a few lines of code that are used ubiquitously and can be considered basic operations (on the same level as additions or multiplications).

**Parallelism** Any concurrency available between independent behaviors should be exposed through their parallel or pipelined composition. That is, all behaviors that do not have any control or data dependencies (or data dependencies only across iterations) should be arranged to execute in a concurrent fashion. Furthermore, the behavior hierarchy should be constructed in such a way as to maximize the number of independent behaviors and hence the available parallelism. Dependent behaviors, on the other hand, should generally not be arranged in a concurrent fashion. Instead, their dependencies should be captured explicitly through transitions as explained above and in Section 2.2. An exception are rare (control) dependencies between otherwise highly independent top-level tasks, for example. In those cases, communication and synchronization are modeled using channels between the tasks.

**Time** The specification model is untimed and all behaviors execute in zero logical time. The only events in the system are events for synchronization in order to specify causality. Synchronization events establish a partial order among concurrent threads of behaviors.

In summary, the specification model hierarchically groups closely related functionality, defines the granularity of the exploration units (behaviors), exposes the available behavior-level parallelism, clearly separates computation from communication, and identifies dependencies through system states, events and transitions.

## **3** Architecture Model

The architecture model is the intermediate model after architecture exploration. Architecture exploration maps the computational parts of the system specification represented by the SpecC behaviors onto processing elements (PEs) of a system architecture. The architecture model represents this mapping, thus exposing the communication between the components to be implemented by the following communication synthesis task.

The architecture model reflects the PE structure of the synthesized system architecture. Therefore, it represents a structural view of the design at the system level. At the top level of the architecture model, the system is described as a parallel composition of non-terminating, concurrent behaviors representing the PEs of the architecture.

Communication in the architecture model, on the other hand, remains at an abstract message-passing level. Communication between behaviors mapped to different PEs becomes system-global communication. Corresponding message-passing channels are instantiated between PE behaviors at the top level, and behaviors inside the PEs are connected to the channels through the PE's ports.

PEs with fixed, pre-defined external communication semantics are modeled as behaviors that directly provide communication channel functionality at their interfaces. A behavior's channel interface abstracts the PE's internal communication implementation and provides a canonical access for communication with the PE at the messagepassing level. Examples are IPs or memories that are not capable of implementing arbitrary communication.

The PE behaviors of the architecture model represent a behavioral view of the PEs. The functionality of each PE is described by grouping the behaviors of the original specification under the PE behaviors according to the selected system partitioning. The original hierarchy is preserved and communication and synchronization behaviors are inserted to preserve the original semantics.

In addition to computation, a PE in general provides system-level storage capabilities. The union of variables inside the behaviors executing in a PE represents the local memory of the PE. A special case of PEs are dedicated system memories which are not capable of executing functionality and only provide variable storage.

All parallelism in the architecture model is captured through the structure of concurrent PEs. Internally, PEs allow a single thread of control only. Behaviorals mapped onto a PE are scheduled to serialize their execution. Static or dynamic scheduling results in a total order among the behaviors inside each PE. Dynamic scheduling emulates parallelism through multitasking yet its time-shared nature allows for only one active behavior at any given time. True parallelism is only available at the PE level with all PEs being constantly active.

The architecture model introduces the notion of time for the computation mapped onto the PEs. Based on estimated execution times on the target PE, behaviors are annotated with timing information. Apart from the total order created by scheduling behaviors inside PEs, execution delays refine the partial order among PEs. Depending on the granularity of the timing information, actions are further ordered in time beyond the pure causality of the specification.

#### 3.1 Architecture Model Example

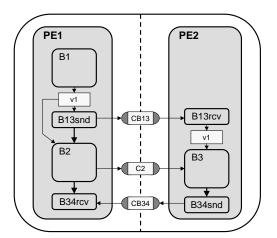

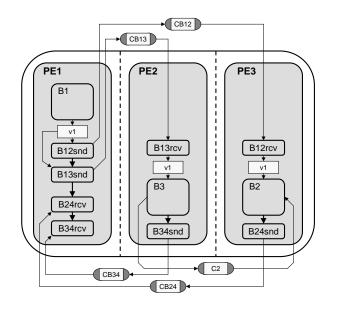

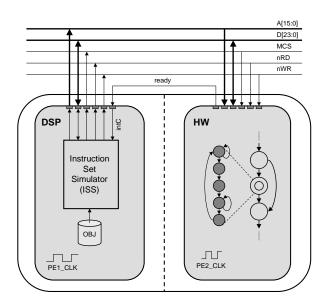

Figure 7 and Listing 5 show the architecture model for the example design from Section 2.1 (Figure 4 and Listing 1) after mapping the specification onto a system architecture with two components, *PE1* and *PE2*. Behaviors *b1* and *b2* are mapped onto *PE1*, while *b3* is mapped onto *PE2*.

Inside the two PE behaviors, the parts of the original behavior hierarchy that are mapped to the corresponding component are instantiated. In addition, pairs of behaviors, B13Snd / B13Rcv and B34Snd / B34Rcv (Listing 5(a)), are inserted into the hierarchy to transfer control and data from *PE1* to *PE2* in oder to preserve the execution semantics of the original specification. The behavior pairs communicate over two system-global message-passing channels, *CB13* and *CB34*, that are inserted between the PEs.

In this example, communication between behaviors mapped to different PEs is transformed into an implemen-

```

// Send data from B1 to B3

behavior B13Snd( in type1 v1, ISend cb13 ) {

void main(void) { cb13.send(&v1, sizeof(v1)); }

};

5 behavior B13Rcv( out type1 v1, IRecv cb13 ) {

void main(void) { cb13.recv(&v1, sizeof(v1)); }

};

// Send data from B3 to B4

10 behavior B34Snd( ISend cb34 ) {

void main(void) { cb34.send( 0, 0 ); }

};

behavior B34Rcv( IRecv cb34 ) {

void main(void) { cb34.recv( 0, 0 ); }

15 };

```

(a) Communication and synchronization behaviors.

```

// Processing element 1

behavior PE1( ISend cb13, ISend c2, IRecv cb34 )

type1 v1;

5

B1

b1

(v1);

B13Snd b13snd (v1, cb13);

B2 b2 (v1, c2);

B34Rcv b34rcv ( cb34 );

10

void main(void) {

// original behavior

B1

b1.main();

b13snd.main(); // send Bl output to B3

// original behavior

b2.main();

B2

b34rcv.main(); // receive B3 output

15

}

};

// Processing element 2

20 behavior PE2( IRecv cb13, IRecv c2, IRecv cb34 )

ł

type1 v1;

B13Rcv b13rcv ( cb13, v1 );

(v1, c2);

25

B3

b3

B34Snd b34snd ( cb34 );

void main (void) {

receive B3 input from B1

b13rcv.main(); //

30

// original behavior B3

b3.main();

b34snd.main(); // send B3 output

}

};

35 // Top-level

behavior Design () {

ChMP c2;

// message-passing channels

ChMP cb13, cb34;

PE1 pe1( cb13, c2, cb34 );

PE2 pe2( cb13, c2, cb34 );

40

void main(void) {

par { pe1.main(); pe2.main(); }

45

};

```

| (b) Top | level | hierarchy. |

|---------|-------|------------|

|---------|-------|------------|

Listing 5: Architecture model.

Figure 7: Architecture model.

tation with message-passing between PEs. Local copies of the variable v1 used for communication between sequential behaviors B1 and B3 are created in the local memories of each PE. Inside the PEs, the behaviors operate on the local copies of the variable. In addition, code is inserted to update and synchronize local variable copies over message-passing channels at points where control is transfered between PEs. In the example, the new value of v1 is communicated through the synchronization and communication behavior pair B13Snd / B13Rcv and the messagepassing channel CB13 together with transferring control from behavior B1 on PE1 to behavior B3 on PE2.

In case of concurrent behaviors mapped to different PEs (e.g. behaviors B2 and B3 mapped to PE1 and PE2), communication between the behaviors is transformed into a message-passing implementation as described in Section 2.3 (Figure 6 and Listing 4). The message-passing channel C2 used for communication between the behaviors becomes a system-global channel connecting PE1 and PE2, and send() and recv() calls in the behaviors are routed through behavior and PE ports to the global channel.

In the example, behaviors inside the PEs are statically scheduled (see Section 3.5). As shown in Figure 7 and Listing 5, scheduling is done in a straightforward way based on the constraints posed by the behavior dependencies with the goal to exploit the available parallelism. On *PE1*, execution starts with behavior *B1*. After *B1* is finished, behavior *B3* on *PE2* can then run in parallel with behavior *B2* on *PE1*. Finally, behavior *B2* on *PE1* is followed by behavior *B34Rcv* which waits for the results of *B3* from *PE2*. On component *PE2*, execution starts with behavior *B13Rcv*, waiting for *B1*'s results. Once the data is received from *PE1*, behavior *B3* is started. After *B3* is finished, control is transfered back to *PE1* through behavior *B34Snd*.

#### 3.2 Storage

Member variables of the behaviors in the specification model represent storage that has to be mapped to memories in the implementation of the architecture model. This includes member variables as part of leaf behaviors as well as variables connecting subbehavior ports that are used for communication.

In the implementation, the memory space of the system is formed by the union of the system PE memories. In general, processing elements each have local memories as part of their microarchitecture. If the local memory of a PE can be accessed from other PEs it becomes global system memory. A special case are memory components whose sole purpose is to provide global storage. They are not able to execute any computational behavior and, therefore, do not provide any processing functionality.

Member variables in the specification are mapped to local or global memories in the architecture. Of special interest are variables used for communication between behaviors mapped to different PEs (see Section 3.3). If a member variable connects two subbehaviors mapped to different PEs it becomes a shared variable on the system level. In a message-passing implementation, such variables are mapped to local memories and messages are passed among the components to communicate updated values. In a shared memory implementation, on the other hand, shared variables are mapped to a global memory components which is accessed directly by the PEs.

#### 3.2.1 Local Memory

In the PE behaviors of the architecture model, the union of all its subbehavior's member variables (i.e. of all the behaviors instantiated under the PE behavior in the architecture model hierarchy) represents the amount of local memory occupied in the PE. For example, in the architecture model of Section 3.1 (Figure 7), both *PE1* and *PE2* provide storage for a variable v1 in their local memories, as specified by the declarations in line 4 and line 22 of Listing 5, respectively.

Unless mapped to global memory (Section 3.2.2), a behavior's member variables will normally be stored in the local memory of the PE the behavior is mapped to. However, member variables that connect subbehaviors mapped to different PEs need to be shared between PEs. In a message-passing implementation, copies of the shared variable are created in the local memories of all PEs accessing the variable. Behaviors inside the PEs then operate on the local copies. In order to implement the shared semantics of the variable and to keep local copies in sync, updated variable values are communicated over messagepassing channels between the components at synchronization points, as discussed in detail in Section 3.3.

The example of Section 3.1 implements such a messagepassing implementation. As defined by the original specification model (Section 2.1), variable v1 is shared between behaviors B1, B2, and B3. Since behavior B3 is mapped to a different PE than behaviors B1 and B2, variable v1 has to be shared between the PEs of the system architecture. As shown in Figure 7 and Listing 5, local copies of the variable are instantiated in the components PE1 and PE2. Inside the components, the corresponding ports of behaviors B1, B2, and B3 are connected to the local copies of v1. Finally, the additional communication and synchronization behaviors B13Snd and B13Rcv (see Listing 5(a)) send and receive updated values of v1 from PE1 to PE2 after behavior B1has finished and before behavior B3 starts to execute.

#### 3.2.2 Global Memory

As discussed in the previous section, the scope of variables stored in the local PE memories usually limits access to behaviors inside the PE. However, if a PE allows other PEs to access variables stored in its local memory, this storage becomes global memory in both scope and lifetime.

Usually, only dedicated shared memory components will support external access of variables stored inside the component. Such memory components provide storage only and can not execute arbitrary functionality, i.e. no behavior can be mapped onto a memory component. On the other hand, it is generally possible for any PE to provide global access to its local memory. In this case, a PE provides global system storage in addition to implementing computation.

In general, any member variable of any behavior running on a certain processing element can be mapped to global memory, for example if the PE's local memory is exhausted. The variable is then removed from the behavior and all accesses to the variable inside the behavior are replaced with global memory accesses.

However, especially the variables used for communication between behaviors mapped to different PEs are candidates for a mapping to global, shared memory. In a message-passing implementation (as described in Section 3.2.1), local copies of such variable have to be created in each connected PE, increasing the total storage cost of the system. In a shared memory implementation, on the other hand, shared variables are mapped to global memory where they can be directly accessed from each PE. Again, accesses to the variable in the leaf behaviors are replaced with accesses to the shared variable in the global memory. Synchronization that is added to preserve the execution semantics of the specification (see Section 3.3) also ensures that global variable accesses are properly ordered according to their sequence in the original specification.

```

// Send data from B1 to B3

behavior B13Snd( ISend cb13 ) {

void main(void) { cb13.send(0,0); }

};

5 behavior B13Rcv( IRecv cb13 ) {

void main(void) { cb13.recv(0,0); }

};

// Send data from B3 to B4

10 behavior B34Snd( ISend cb34 ) {

void main(void) { cb34.send(0,0); }

};

behavior B34Rcv( IRecv cb34 ) {

void main(void) { cb34.recv(0,0); }

15 };

```

(a) Synchronization behaviors.

```

Processing

element 1

behavior PE1(

IMem m1,

ISend cb13,

ISend c2

5

IRecv cb34 ) {

B1

b1

(m1);

B13Snd b13snd ( cb13 );

B2

h2

(

m1, c2 );

B34Rcv b34rcv ( cb34 );

10

void main(void) {

// original behavior

b1.main();

B1

b13snd.main(); // B1->B3 transition

// original behavior B2

b2.main();

b34rcv.main(); // wait for B3 to finish

15

}

};

// Processing element 2

20 behavior PE2(

IMem m1,

IRecv cb13,

IRecv c2.

IRecv cb34 ) {

B13Rcv b13rcv ( cb13 );

25

b3

( m1, c2 );

B3

B34Snd b34snd ( cb34 );

void main(void) {

b13rcv.main(); // wait for B1 to finish

// original behavior B3

30

b3.main();

b34snd.main(); // send B3 completion

}

};

35 // Top-level

behavior Design () {

ChMP c2:

// message-passing channels

ChMP cb13, cb34;

40

M1 m1();

// Shared memory

PE1 pe1 ( m1, cb13, c2, cb34 );

PE2 pe2 ( m1, cb13, c2, cb34 );

45

void main(void) {

par { pe1.main(); m1.main(); pe2.main(); }

}

};

```

| (b) Top | level | hierarchy. |

|---------|-------|------------|

|---------|-------|------------|

Listing 6: Shared memory architecture model.

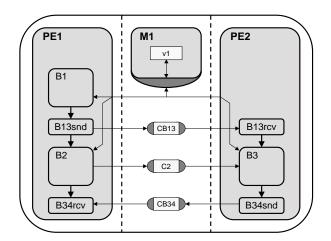

Figure 8: Shared memory architecture model.

```

// Shared memory interface

interface IMem {

type1 r_v1 ( void );

void w_v1 ( type1 d );

5 };

// Shared memory component

behavior M1() implements IMem

{

10 type1 v1;

// Memory read/write interface

type1 r_v1 ( void ) { return v1; }

void w_v1 ( type1 d ) { v1 = d; }

5

void main(void) { /* nothing */ };

};

```

Listing 7: Global memory component.

A shared memory implementation of the architecture model from Section 3.1 is shown in Figure 8 and Listing 6. Instead of a message-passing implementation, the variable v1, which is shared between behaviors B1, B2, and B3, is mapped to a dedicated shared memory component M1. There are no local copies of v1 in components PE1 or PE2, and all three behaviors access the variable v1 inside the global memory M1 instead.

Like other system components, the dedicated memory component is represented by a behavior which is instantiated at the top level of the architecture model, running in parallel with all other PEs. The code for the global memory component behavior *M1* is shown in Listing 7. Since it is a dedicated memory component that does not execute any computational functionality, the behavior's *main()* method remains empty. In general, if global memory is provided by a processing element, the PE behavior will execute the behaviors mapped to the component in addition to implementing an interface to its memory.

```

// leaf behavior 1

behavior B1( IMem mem )

void main(void) {

5

mem. w_v1(\ldots);

// Memory write v1

}

};

10 // leaf behavior 2

behavior B2( IMem mem, ISend c2 )

void main(void) {

type2 v2;

15

v2 = f2 (mem. r_v1 (), ...); // read v1

c2.send(&v2, sizeof(v2));

20

}

};

// leaf behavior 3

behavior B3( IMem mem, IRecv c2 )

25 {

void main(void) {

type2 v2;

c2.recv(&v2, sizeof(v2));

30

f3 ( mem. r_v1 (), v2 , ... ); // read v1

}

};

```

Listing 8: Shared memory accesses in leaf behaviors.

The shared variable v1 is instantiated as a member variable of the memory behavior (line 10). The memory behavior provides access to the global variables through a channel interface *IMem*. Other PEs can connect to the memory's interface which supplies type-safe methods to read  $(r_v v1())$  and write  $(w_v v1())$  shared variables stored inside.

Inside the processing elements, accesses to the shared variable v1 are replaced with corresponding read or write accesses to the global memory component through behavior ports, PE ports, and the memory interface. Listing 8 shows the updated accesses to variable v1 in the leaf behaviors. Variable reads are replaced with calls of the memory's  $r_v v1()$  method and variable assignments with calls to the  $w_v v1()$  method.

Since updated values of v1 are exchanged between PEs via the shared memory, behaviors B13Snd and B13Rcv (see Listing 6(a)) only perform pure synchronization by exchanging empty messages. No data communication is performed over the message-passing channels. All data transfers are handled through the global memory. On the other hand, the synchronization behaviors ensure that the shared variable v1 is accessed by B3 only after B1 is finished, in consistency with the original specification.

#### 3.3 Synchronization

In the architecture model, synchronization has to be inserted to preserve the execution semantics of the original specification. The behaviors of the specification model are mapped onto a set of concurrent components according to the structural nature of the architecture model. Therefore, synchronization has to ensure that behaviors execute in the proper order according to the transitions in the original specification.

All communication and synchronization between system components in the architecture model is handled via message-passing channels connecting the components. As shown in the architecture model example in Section 3.1 (Figure 7 and Listing 5), for each behavior transition that crosses component boundaries (transitions from *B1* to *B3* and back), a pair of synchronization behaviors (behavior pairs *B13Snd / B13Rcv* and *B34Snd / B34Rcv*, see Listing 5(a)) that communicate over a message-passing channel (channels *CB13* and *CB34*) is inserted.

By passing messages over the channels, the synchronization behavior pairs ensure that the semantics of the corresponding original behavior transition are preserved among the PEs. In this case, for example, behavior *B13Rcv* blocks execution of *B3* on *PE2* until it receives the message from behavior *B13Snd* that *B1* on *PE1* has finished. Similarly, behavior *B34Snd* on *PE2* notifies *B34Rcv* on *PE1* that *B3* has completed execution.

Along with passing control from one behavior to another, a behavior transition usually represents a transfer of data through the shared variables connecting the ports of the behaviors. If the transition crosses PE boundaries, this data has to be transfered together with passing control. In a shared memory implementation (see Section 3.2.2), data is transfered via a global system memory component and simple synchronization via synchronization behavior pairs and message-passing channels is sufficient for implementation of inter-component transitions.

On the other hand, in a message-passing implementation (see Section 3.2.1), local copies of the shared variables are created inside the components, and local values have to be synchronized across behavior transitions. In this case, communication of data values is combined with control synchronization using the behavior pairs and message-passing channels. For each transition that crosses components, the synchronization message contains all the updated data values shared between the behaviors. Local copies of variables connecting the source behavior's output ports to the target behavior's input ports are transfered in the message for each inter-component behavior transition. The communication and synchronization behavior pairs are responsible for assembling and disassembling messages from/into local variables.

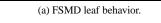

Figure 9: Architecture model with multiple intercomponent behavior transitions.

For example, in the architecture model presented earlier in Section 3.1, local copies of the variable v1 shared between behaviors B1 and B3 are synchronized when executing the transition from B1 on PE1 to B2 on PE2. As shown in Listing 5(a), the synchronization behaviors B13Snd and B13Rcv for that transition read the local value of v1 in PE1, pass it in a message over channel CB13, and update the local value of v1 in PE2. Together with the synchronization described earlier, this ensures that B3 doesn't start executing until B1 has finished and all the output data of B1needed by B3 is available.

In general, there can be multiple inter-component behavior transitions originating from a single behavior on a PE. For each such transition, a message-passing channel and a synchronization behavior pair is inserted. For example, if behavior B2 had been mapped to a third component PE3 in our example, an additional channel CB12 and an additional behavior pair B12Snd / B12Rcv would have been inserted after B1 and before B2 on PE1 and PE3, respectively (Figure 9). Likewise, an additional channel CB24 and an additional behavior pair B24Snd / B24Rcv would have been inserted to signal completion of B2.

Note that it is part of the implementation issues related to the architecture model to decide in which order the send and receive behaviors are scheduled inside the PEs, e.g. whether *B13Snd* will execute before or after *B12Snd* on *PE1* (for more discussion of scheduling issues see Section 3.5).

Finally, after scheduling has determined the order of synchronization behaviors, an optional code optimization

step can be applied to merge consecutive synchronization behaviors inside the same component into a single synchronization behavior that successively sends and receives the necessary messages. For example, in the model from Figure 9, the behaviors *B13Snd* and *B12Snd* could be merged into a single behavior *B1Snd*. Alternatively, behaviors *B12Snd*, *B13Snd*, *B24Rcv*, and *B34Rcv* on *PE1* could be merged into one large synchronization behavior (e.g. *B14Sync*).

#### **3.4 IP Components**

Intellectual property (IP) processing elements are characterized by the fact that their computational functionality (behavior), their communication functionality (interface), or both are predefined and fixed. In general, IP supplier and IP intergrator are different entities, either in-house or among a global IP trading marketplace. The IP supplier provides models of the IP component which are integrated into the architecture and following models for validation and synthesis. An IP creator can choose to supply different models of an IP varying in their amount of detail at different levels, trading off accuracy and simulation speed, for example.

In the architecture model, a behavioral model of the IP is required. At this level, the IP model describes the IP functionality annotated with performance and other quality metrics similar to other PE models (see also Section 3.6 about timing annotation). However, in their interfaces to other PEs, IPs, by definition, are not capable of implementing arbitrary inter-PE communication, and it is not possible to simply connect any message-passing channels to the IP in the architecture model, for example.

Therefore, IP models directly provide a channel interface at the message-passing level. An IP's channel interface describes the communication with the rest of the system supported by the IP. It abstracts the underlying IP behavior and IP interface to the external world. Furthermore, IP channel interfaces at this high level are canonical for all IPs of the same class, enabling plug-and-play of IPs without modifications to the rest of the system. For example, different DCT IPs from different suppliers can be easily exchanged since they all provide the same channel interface.

Listing 9 shows an example of an IP model. For this example, we assume that the functionality of B2 is available in the form of this IP. As part of exploration, we then have the option to implement B2 using the IP instead of mapping it onto a general-purpose PE, depending on quality metrics like performance, cost, and power.

The purely behavioral model in Listing 9(a) is at the highest level of abstraction for integration into the architecture model and as such the minimal requirement an IP

// IP interface interface IIP Start IP, send parameters 5 void start ( type1 v1 ); // Get value of v2 from IP type2 v2( void ); Wait for IP to finish, get result void done (void);  $10 \};$ // IP model behavior IP() implements IIP; Declaration only 15 // Implementation is external // Annotations **note** IP.WMOPS = 13476; // Quality metrics (a) Behavioral IP. // Bus-functional IP model behavior IPBF( inout **bit** [63:0] data, in event start, **bit** [2] ready. out 5 out event done ); 11 Declaration only Implementation is external // Behavioral IP model 10 behavior IP() implements IIP ł // IP bus **bit** [63:0] dat; st, dn; event 15 bit [2] rdy; // Bus-functional IP instance IPBF ip ( dat, st, rdy, dn ); // Implementation of IP communication void start (type1 v1) { 20 // Put params on bus, notify IP dat = v1; notify ( st ); 25 } type2 v2( **void** ) { // wait for data, read from bus

while ( ! rdy[1] ) wait ( dn ); 30 return dat; } void done( void ) {

// wait until IP becomes ready again while ( ! rdy [0] ) wait ( dn ); 35 Run internal bus-functional model void main(void) { ip.main(); } 40};

(b) Bus-functional IP with wrapper.

Listing 9: IP component model.

supplier must provide. The interface *IIP* defines the possible communication with the IP. Corresponding to its *B2* functionality (compare to Listing 4), the interface provides three message-passing methods: *start()* sends the parameter *v1* to the IP and starts execution of one iteration; *v2()* receives the value of *v2* from the IP during its execution; finally, *done()* waits for the message from the IP that it has finished. Again, note that this is the general interface for all possible IP components that provide functionality equivalent to *B2*.

The actual IP model *IP* then implements the *IIP* interface, modeling the IP functionality (and performance) in response to incoming data and generating outgoing messages from/to other PEs. Usually, the IP supplier will want to protect the details of the IP implementation. Therefore, only the declaration of *IP* is provided. The actual code is supplied in the form of a precompiled library that will get linked into the architecture model for simulation. In addition, the IP is annotated with various information about quality metrics, verification properties, and so on. Note that the IP supplier always has the option to provide full source code. Especially at the behavioral level, source code can serve as additional documentation about IP functionality without disclosing any implementation details.

In Listing 9(b), a slightly more detailed IP model is shown. In this case, the IP model includes a bus-functional IP description *IPBF* that will be needed for the communication model later anyway. As will be explained in Section 4.4, the bus-functional IP model describes communication with the IP as events on the actual IP bus in a timingaccurate manner. In our example, the IP bus includes bidirectional data wires (*data[63:0]*), status lines (*ready[2]* and *done*), and control lines (*start*).

The behavioral IP model *IP* then wraps a channel interface around the bus-functional model. Internally, the behavioral model instantiates *IPBF* and executes its functionality in the *main()* method. The wrapper then implements the message-passing communication of the channel interface by translating them into actions on the IP bus according to the IP protocol. For example, the v2() method waits for the corresponding *ready* line to be asserted before reading the value from the *data* bus.

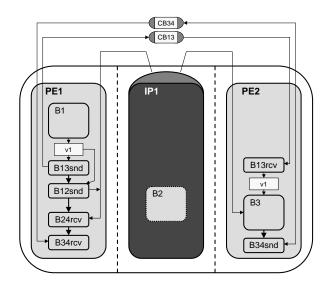

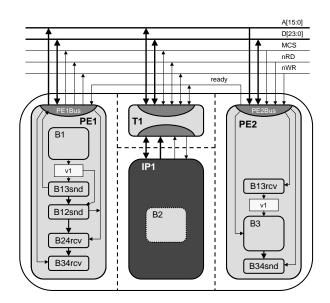

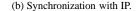

Figure 10 and Listing 10 show the architecture model in which B2 is mapped onto an instance IP1 of the IP processing element. Instead of PE3, the IP component is instantiated in the top level of the design (Listing 10(b)). Compared to the model from Section 3.3 (Figure 9), all communication with B2 on PE3 is replaced with direct connections to the IP's channel interface. Inside the communication and synchronization behaviors B12Snd and B24Rcv (Listing 10(a))), message-passing methods of the IP's channel interface are called for all communication

```

// Send data to IP

behavior B12Snd( in type1 v1, IIP ip1 ) {

void main(void) { ip1.start(v1); }

};

// Receive results from IP

behavior B24Rcv( IIP ip1 ) {

void main(void) { ip1.done(); }

};

```

(a) Synchronization with IP.

```

// Processing element 1

behavior PE1( ISend cb13, IIP ip1, IRecv cb34 )

type1 v1;

5

B1

b1

(v1);

B13Snd b13snd (v1, cb13);

B12Snd b12snd (v1, ip1);

B24Rcv b24rcv ( ip1 );

10

B34Rcv b34rcv ( cb34 );

void main(void) {

// original behavior B1

b1.main();

b13snd.main(); // B1->B3 transition

b12snd.main(); // B1->B2 transition

15

b24rcv.main(); // wait for B2 to finish

b34rcv.main(); // wait for B3 to finish

};

20

// Processing element 2

behavior PE2( IRecv cb13, IIP ip1, IRecv cb34 )

type1 v1;

25

B13Rcv b13rcv ( cb13 , v1 );

B3

b3

( v1, ip1 );

B34Snd b34snd ( cb34 );

void main(void) {

30

b13rcv.main(); // wait for B1 to finish

// original behavior B3

b3.main();

b34snd.main(); // send B3 completion

}

35 };

// Top-level

behavior Design ()

40

ChMP cb13, cb34; // message-passing channels

IP ip1();

// IP component

PE1 pe1 ( cb13 , ip1 , cb34 );

PE2 pe2 ( cb13, ip1, cb34 );

45

void main(void) {

par { pe1.main(); ip1.main(); pe2.main(); }

}

50 };

```

(b) Top level hierarchy.

Listing 10: Architecture model with IP.

Figure 10: Architecture model with IP.

Listing 11: IP accesses in leaf behavior B3.

with the IP. Similarly, inside leaf behavior B3, all channel calls for communication with B2 are replaced with calls to the IP's corresponding interface methods, as shown in Listing 11.

#### 3.5 Scheduling

By definition, the components of the system architecture are single-threaded in terms of the computation they are executing. According to the inherently sequential nature of components, behaviors mapped onto a PE have to be scheduled in order to serialize their execution. The order of execution of both, the original computation behaviors and the additional communication/synchronization behaviors determines the schedule of computation and communication on each PE.

In the simplest case, static scheduling is performed. The execution order of the behavioral blocks inside the PEs is fixed by introducing artificial dependencies according to the selected schedule. Therefore, the behavior hierarchy inside the components becomes a purely sequential composition. Behaviors are executed in the pre-defined order defined by the sequential transitions inside the PEs of the architecture model. For example, as described in Section 3.1, the subbehaviors in each PE of the architecture model from Figure 7 (Listing 5) are executed sequentially in the order determined by the static schedule. Hence, the *PE1* and *PE2* behaviors are a purely sequential composition executing their subbehaviors in the given order.

In a dynamic scheduling approach, on the other hand, the order of execution is determined dynamically during runtime. Behaviors are arranged into potentially concurrent tasks. Inside each task, behaviors are executed sequentially. Tasks can be dynamically forked and joined through par statements in the code. A scheduler maintains a pool of task behaviors and dynamically selects a task to execute according to its scheduling algorithm. The scheduler in the architecture model is a behavioral abstraction of the scheduling policy of the underlying operating system.

#### **3.6** Time

After behaviors have been partitioned onto PEs, the concept of time is introduced for the computation represented by the behaviors. Behaviors grouped under a PE are refined to include execution times on the target. As a result, behavior executions among the concurrent PEs are ordered additionally beyond the pure causality established by the inter-PE synchronization.

Behavior execution delays can be based on estimated execution times derived from a model of the target component, for example. Alternatively, execution delays can describe a timing budget allocated for different behaviors. These budgets will later serve as timing constraints for the behavior implementation on the target PEs.

Execution times can be specified on different levels of granularity, ranging from the statement level to the behavior level. Execution delays at the behavior level are used to model average or worst-case execution times of the corresponding behavior. On the other hand, execution times at the basic-block level can accurately model even data-dependent delays. The leaf behaviors are annotated with waitfor() statements to model execution time. In addition to providing feedback about logical time during simulation, the annotations serve as constraints for synthesis and verification tools.

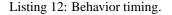

Listing 12 shows a code template for a leaf behavior with estimated timing. In this case, execution delays are modeled at the basic block level. At this granularity, datadependent delays are accurately modeled while keeping the simulation overhead incurred by the waitfor() statements at a minimum.

```

behavior Bx(...)

{

void main (void)

if ( ... ) {

5

waitfor ( T1 );

// execution

time 1

else

{

10

waitfor (T2);

11

time 2

execution

}

waitfor ( T3 );

execution

time 3

Cy. send ( ... );

15

waitfor ( T4 );

execution

time 4

}

};

```

#### 3.7 Summary

The architecture model describes the implementation of the computation on the PEs of the system architecture. It is a structural view of the system's PE architecture. It contains behavioral views of the PEs that represent the mapping of computation onto each PE. Communication, on the other hand, remains at an abstract level. The architecture model exposes the communication between PEs which will be implemented in the next step.

In summary, properties of the architecture model are:

- (a) At the top level of the behavior hierarchy, the PE structure is modeled as a parallel composition of non-terminating PE behaviors.

- (b) PE behaviors communicate via system-global message-passing channels connecting their ports.

- (c) PE behaviors with predefined, fixed communication functionality (IPs. memories) directly provide channel interfaces for communication.

- (d) Original specification behaviors are grouped under the PE behaviors to specify the functionality to be implemented by each PE.

- (e) Member variables of behaviors instantiated inside a PE represent the amount of storage allocated in the local PE memory.

- (f) Behaviors inside different PEs communicate by sending and receiving messages over ports and global channels.

- (g) True parallelism is limited to the concurrency among PEs. Internally, PEs are single-threaded. Execution of behaviors inside a PE is serialized in time through static or dynamic scheduling.

(h) Computation in the leaf behaviors is annotated with estimated or projected execution times on its target PE.

All in all, the architecture model accurately reflects the implementation of the computational aspects of the system for analysis and validation.

## 4 Communication Model

The communication model is the final output of the system-level design process after architecture exploration implements computation on the PEs and communication synthesis implements communication over the busses of the system architecture. The communication model represents the mapping of computation and communication onto PEs and busses, respectively.

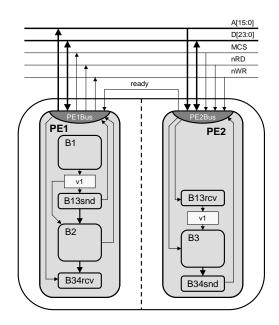

The communication model is a structural view of the complete system including computation and communication. It shows the PE and bus structure of the final system architecture. The system is described as a netlist of concurrent, non-terminating PEs connected via system bus wires.