# **Vivado Design Suite**

# Creating, Packaging Custom IP Tutorial

UG1119 (v2016.1) May 5, 2016

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                      |

|------------|---------|-----------------------------------------------|

| 05/05/2016 | 2016.1  | Added Lab 4: Packaging IP located in a Trunk. |

# **Table of Contents**

| Creating, Packaging Custom IP Tutorial <u>www.xilinx.com</u> Send Feedback | 3  |

|----------------------------------------------------------------------------|----|

| Step 1: Create a New Vivado Project                                        | 42 |

| Introduction                                                               | 42 |

| Lab 3: Packaging Legacy IP                                                 | 42 |

| Conclusion                                                                 | 41 |

| Step 5: Validate the Custom IP                                             | 39 |

| Step 4: Examine and Update the Packaged IP                                 | 35 |

| Step 3: Package the IP Directory                                           | 33 |

| Step 2: Create a New Vivado Project                                        | 31 |

| Step 1: Examine the IP Directory                                           | 30 |

| Introduction                                                               | 30 |

| Lab 2: Packaging a Specified Directory                                     | 30 |

| Conclusion                                                                 | 29 |

| Step 7: Validate the New IP                                                | 23 |

| Step 6: Review and Package the IP                                          | 22 |

| Step 5: Add a Product Guide to the IP                                      | 19 |

| Step 4: Modify the IP Definition                                           | 17 |

| Step 3: Package the IP                                                     | 15 |

| Step 2: Preparing Design Constraints                                       | 8  |

| Step 1: Open the Vivado Project                                            | 7  |

| Introduction                                                               | 7  |

| Lab 1: Packaging a Project                                                 | 7  |

| Locating Tutorial Design Files                                             | 6  |

| Tutorial Design Description                                                | 6  |

| Software Requirements                                                      | 6  |

| Introduction                                                               | 5  |

| Introduction to Creating and Packaging Custom IP                           | 5  |

| Revision History                                                           | 2  |

Introduction to Creating and Packaging Custom IP

| Step 2: Package a Library Core                 | 45 |

|------------------------------------------------|----|

| Step 3: Package the GPIO IP                    | 49 |

| Step 4: Validate the New Custom IP             | 53 |

| Conclusion                                     | 54 |

| Lab 4: Packaging IP located in a Trunk         | 55 |

| Introduction                                   | 55 |

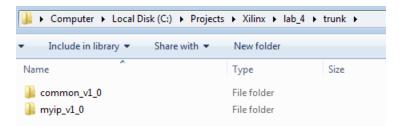

| Step 1: Examine the Repository Trunk Directory | 55 |

| Step 2: Create a New Vivado Project            | 56 |

| Step 3: Package the Library Core               |    |

| Step 4: Package the IP                         | 61 |

| Step 5: Validate the IP                        | 68 |

| Conclusion                                     |    |

| Legal Notices                                  | 70 |

| Please Read: Important Legal Notices           | 70 |

# Introduction to Creating and Packaging Custom IP

### Introduction

This tutorial takes you through the required steps to create and package a custom IP in the Vivado<sup>®</sup> Design Suite IP packager tool.

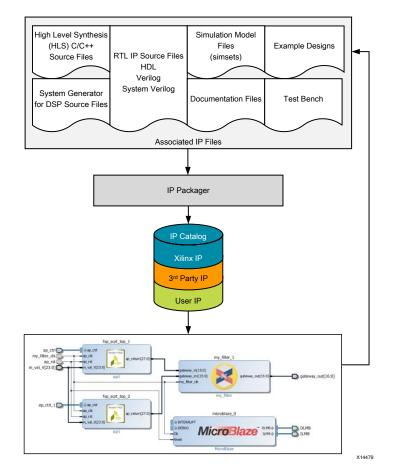

The Vivado Design Suite provides an IP-centric design flow that helps you quickly turn designs and algorithms into reusable IP. As shown in the following figure, the Vivado IP Catalog is a unified IP repository that provides the framework for the IP-centric design flow. This catalog consolidates IP from all sources including Xilinx<sup>®</sup> IP, third-party IP, and end-user designs targeted for reuse as IP into a single environment. The following figure provides a diagram of Vivado Design Suite IP design flow.

Figure 1: Vivado Design Suite IP Design Flow

www.xilinx.com

UG1119 (v2016.1) May 5, 2016

Ľ.

Introduction to Creating and Packaging Custom IP

The Vivado IP packager tool is a unique design reuse feature, which is based upon the IP-XACT standard. The IP packager tool provides you with the ability to package a design at any stage of the design flow and deploy the core as system-level IP.

See the *Vivado Design Suite User Guide: Creating and Packaging Custom IP* (UG1118) for more information about the Vivado IP packager.

**VIDEO:** You can also learn more about the creating and using IP cores in Vivado Design Suite by viewing the quick take videos: <u>Configuring and Managing Custom IP</u> and <u>Customizing</u> and <u>Instantiating IP</u>.

**TRAINING**: Xilinx provides training courses that can help you learn more about the concepts presented in this document. Use these links to explore related courses:

Essentials of FPGA Design

Embedded Systems Software

### **Software Requirements**

See the *Vivado Design Suite User Guide: Release Notes, Installation, and Licensing* (UG973) for a complete list and description of the system and software requirements.

# **Tutorial Design Description**

The small sample design used in this tutorial has a set of RTL design sources consisting of Verilog files, along with a PDF that describes how to add a document file to your IP.

# **Locating Tutorial Design Files**

Download ug1119-vivado-creating-packaging-ip-design.zip, from the Reference Design Files on the Xilinx website.

Extract the zip file contents into any write-accessible location.

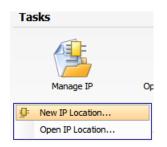

# Lab 1: Packaging a Project

### Introduction

In this lab, you define a new custom IP from an existing Vivado project, using the Create and Package IP wizard.

You start with an existing design project in the Vivado IDE, define identification information for the new IP, add documentation to support its use, and add the IP to the IP Catalog.

After packaging, you verify the new IP through synthesis in a separate design project.

The lab project contains Verilog source files for a simple UART interface.

### **Step 1: Open the Vivado Project**

Launch Vivado.

#### **On Linux:**

- Change to the directory where the lab materials are stored: cd <Extract\_Dir>/lab\_1

- Launch the Vivado IDE: **vivado**

#### **On Windows**:

• Launch the Vivado Design Suite IDE:

#### Start > All Programs > Xilinx Design Tools > Vivado 2016.1> Vivado 2016.1

Or

Click the Vivado 2016.1 desktop icon to start the Vivado IDE

The Vivado IDE Getting Started page displays with links to open or create projects, and to view documentation. For either Windows or Linux, continue the lab from this point.

1. Click Open Project, and browse to: <Extract\_Dir>/lab\_1/my\_simple\_uart

Note: Your Vivado Design Suite installation might have a different name on the Start menu.

2. Select the my\_simple\_uart.xpr project and click OK.

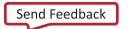

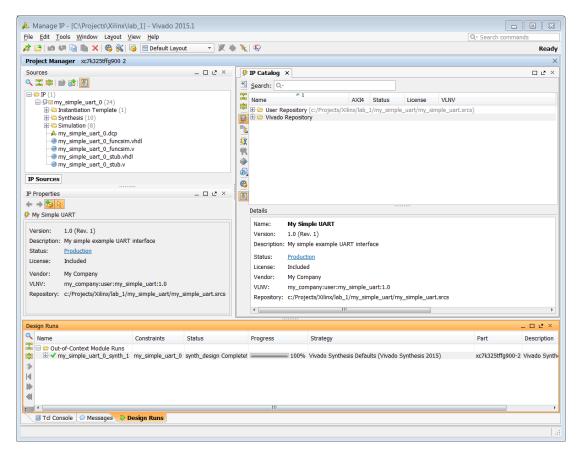

The design loads, and you see the Vivado IDE in the default layout view, with the Project Summary information as shown in the following figure.

| 3 io 🕫 🖿 🖿 🗙 🕨            | .ayout View Help<br>` 🍪 💥 ∑ 🌠 😬 Default Layou                                   | - X & X @                                  | Q- Search commands                              |

|---------------------------|---------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------|

|                           |                                                                                 |                                            | Rei                                             |

| Flow Navigator ? «        | Project Manager - my_simple_uart                                                | [                                          | ?                                               |

| < ∑ ⊜                     | Sources ? _ D L <sup>a</sup> ×                                                  | <b>D</b> Project Summary X                 | ? 🗆 ピ                                           |

| Project Manager           | 🔍 🛣 😂 i 📾 🔂                                                                     | Project Settings                           | Edi                                             |

| Project Settings          | Design Sources (1)     Design Sources (1)     Design Juart_top (uart_top.v) (2) | Project name: my_simple_uart               |                                                 |

| Add Sources               | B Gonstraints (1)                                                               | Project location: C:/Projects/Xilinx/lab_1 |                                                 |

| Language Templates        | Simulation Sources (1)                                                          | Product family: Kintex-7                   |                                                 |

| IP Catalog                |                                                                                 | Project part: <u>xc7k325tffq900-2</u>      |                                                 |

|                           |                                                                                 | Top module name: <u>uart top</u>           |                                                 |

| IP Integrator             |                                                                                 | Target language: <u>VHDL</u>               |                                                 |

| ở Create Block Design     |                                                                                 | Simulator language: <u>Mixed</u>           |                                                 |

| P Open Block Design       |                                                                                 | Synthesis                                  | Implementation                                  |

| 🍓 Generate Block Design   |                                                                                 | Status: Not started                        | Status: Not started                             |

| Simulation                | Hierarchy Libraries Compile Order                                               | Messages: No errors or warnings            | Messages: No errors or warnings                 |

| 🚳 Simulation Settings     |                                                                                 | Part: xc7k325tffg900-2                     | Part: xc7k325tffg900-2                          |

| ( Run Simulation          | Properties ? _ D L <sup>a</sup> ×                                               | Strategy: <u>Vivado Synthesis Defaults</u> | Strategy: <u>Vivado Implementation Defaults</u> |

| -                         | ← → 100 k                                                                       |                                            | Incremental compile: None                       |

| RTL Analysis              |                                                                                 |                                            |                                                 |

| Elaboration Settings      |                                                                                 | DRC Violations                             | Timing                                          |

| Open Elaborated Design    |                                                                                 |                                            |                                                 |

| Synthesis                 | Select an object to see properties                                              | Run Implementation to see DRC results      | Run Implementation to see timing results        |

| Synthesis Settings        | Select an object to see properties                                              | Utilization                                | Power                                           |

| Run Synthesis             |                                                                                 | Uchización                                 | Power                                           |

| Open Synthesized Design   |                                                                                 | Run Synthesis to see utilization results   | Run Implementation to see power results         |

| Implementation            |                                                                                 |                                            | 1                                               |

| Implementation Settings   | Design Runs                                                                     |                                            | ? _ 🗆 🗳                                         |

| Run Implementation        | Name                                                                            | Constraints Status WNS TNS WHS THS TP      | WS Failed Routes LUT FF BRAM URAM DSF           |

| Open Implemented Design   | 🔀 🖃 🔿 synth_1                                                                   | constrs_1 Not started                      |                                                 |

|                           | impl_1                                                                          | constrs_1 Not started                      |                                                 |

| Program and Debug         |                                                                                 |                                            |                                                 |

| Bitstream Settings        |                                                                                 |                                            |                                                 |

| 🚵 Generate Bitstream      |                                                                                 | III                                        |                                                 |

| 🕨 📑 Open Hardware Manager | 💭 Tcl Console 💭 Messages 🛛 🕄 L                                                  | og 🕒 Reports 🗊 Design Runs                 |                                                 |

Figure 2: Project Default View Layout

# **Step 2: Preparing Design Constraints**

The existing design includes timing constraints defined in an XDC file (uart\_top.xdc). These constraints were defined for the UART design as a standalone design. However, when packaged as an IP, the design inherits some of the needed constraints from the parent design. In this case, you must modify the XDC file to separate constraints the IP requires when used in the context of a parent design, and the constraints the IP requires when used out-of-context (OOC) in a standalone capacity. This requires splitting the current XDC file.

You should prepare the design constraints prior to packaging the design for inclusion in the IP catalog; however, you can also perform these steps after packaging the IP.

**IMPORTANT:** The Vivado tools create a synthesized design checkpoint (DCP) as part of the default Out-of-Context (OOC) design flow for IP packaging and use.

To ensure that the packaged IP functions properly in the default Out-of-Context (OOC) design flow, the IP packaging must include a standalone XDC file to define all external clocking information for the IP.

8

Vivado synthesis uses the standalone XDC file in the OOC synthesis run to constrain the IP to the recommended clock frequency.

When used in the context of a top-level design, the parent XDC file provides the clock constraints and the standalone OOC XDC file is not needed.

For more information on the Out-Of-Context (OOC) design flow, and the use of the DCP file, see the *Vivado Design Suite User Guide: Designing with IP* (<u>UG896</u>).

**TIP:** Depending on the function and use of the packaged IP, you might need to adjust the design constraints to ensure proper scoping. For more information, See "Constraints Scoping" in the Vivado Design Suite User Guide: Using Constraints (<u>UG903</u>).

### Analyze the Current Constraints Files

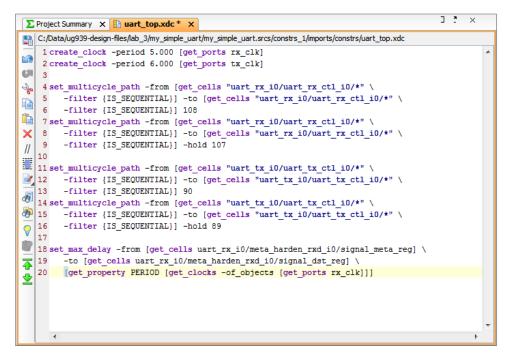

1. In the Hierarchy pane of the Sources window, open the target XDC file (uart\_top.xdc) under the /Constraints folder.

#### Figure 3: File Contents of uart\_top.xdc

There are two items to take note of in the XDC file, as seen in , above.

- create\_clock constraints (Lines 1 and 2)

- set\_max\_delay constraint relying on the clock object period value (line 18).

**Note:** The line numbers referenced in Figure 3 might differ from the line numbers in your XDC file because the constraints were edited for easier viewing in this tutorial.

2. Examine all create\_clock constraints prior to packaging the new IP definition.

Creating, Packaging Custom IP Tutorial <u>www.xilinx.com</u>

UG1119 (v2016.1) May 5, 2016

9

Lab 1: Packaging a Project

If the created clock is internal to the IP (GT), or if the IP contains an input buffer (IBUF), the create clock constraint should stay in the IP XDC file because it is needed to define local clocks.

In the next sub-step, you move clocks that are not internal, or local, to the IP from the IP XDC file to an OOC XDC file, because they are provided by the parent design.

For this example, you move the create\_clock constraints on line 1 and 2 from the design XDC file to an OOC XDC file. When a user instantiates the IP you are packaging from the IP catalog into a design, the IP inherits the clock definitions from the parent design.

The set\_max\_delay constraint is also noteworthy in that it has a dependency on the PERIOD property of defined clocks, (get\_clocks -of\_objects). This dependency is affected by the order of processing of the constraints of the IP and top-level design.

By default, when IP customizations are instantiated into a design, the Vivado IDE processes the XDC files of an IP before the XDC files of the top-level design. This is known as EARLY processing, and is defined by the PROCESSING\_ORDER property on the XDC file.

By default, the XDC files of the top-level design are marked for **NORMAL** processing. This means that the processing of XDC files for IP constraints happens before the top-level design constraints created by the user. However, in the case of the set\_max\_delay constraint, the dependency on the clock PERIOD will cause errors in processing the IP constraints early and defining the clock later.

3. To resolve this issue, you mark the XDC files of the UART IP for LATE processing.

**TIP:** Xilinx delivered IP with \_clock appended to the XDC filename are all marked for LATE processing.

### Creating an Out-Of-Context (OOC) XDC file

1. From the Flow Navigator, or from the File menu, select **Add Sources**, or select the **Add Sources** button **b**.

The Add Sources dialog box opens.

- 2. Select Add or Create Constraints, and click Next.

- 3. In the Add or Create Constraints dialog box, click the **Add an Existing or Create file** button 📩.

- 4. In the Create Constraints File dialog box, fill in the constraints file information, as shown in the following figure.

- File type: **XDC**

- o File name: uart\_top\_ooc.xdc

- File location: <Local to Project>

- 5. Click OK.

| 🚴 Create Cons                                            | traints File                         |  |  |  |  |

|----------------------------------------------------------|--------------------------------------|--|--|--|--|

| Create a new constraints file and add it to your project |                                      |  |  |  |  |

| File type, name                                          | and location                         |  |  |  |  |

| File type:                                               | 🚯 XDC 🔻                              |  |  |  |  |

| File name:                                               | uart_top_ooc.xdc                     |  |  |  |  |

| File location:                                           | 🛜 <local project="" to=""> 👻</local> |  |  |  |  |

|                                                          | OK Cancel                            |  |  |  |  |

Figure 4: Create Constraints File Dialog Box

**TIP:** For Xilinx-delivered IP, the out-of-context XDC file has \_ooc appended to the filename; however, it is the USED\_IN property of the file that determines if it is an OOC XDC file, not the filename.

6. Click Finish to complete the Add Sources dialog box.

The Vivado tools create a new XDC file in the project and displays the file under the Constraints section in the Hierarchy pane of the Sources window.

You now move the create\_clock constraints from the XDC file of the original design (uart top.xdc) into the OOC XDC file (uart top ooc.xdc).

- 7. In the Sources window, open the new OOC XDC file (uart\_top\_ooc.xdc) by double-clicking the file. The file is empty.

- 8. Cut and paste the create\_clock constraints, from lines 1 and 2 of the IP XDC file (uart\_top.xdc) into the empty OOC XDC file.

The OOC XDC file contains only the two create\_clock constraints.

| Σ        | roject Summary 🗙 📳 uart_top.xdc 🗙 🚹 uart_top_ooc.xdc * 🗙                      |  |

|----------|-------------------------------------------------------------------------------|--|

|          | C:/Projects/my_simple_uart/my_simple_uart.srcs/constrs_1/new/uart_top_ooc.xdc |  |

| _        | create_clock -period 5.000 [get_ports rx_clk]                                 |  |

| 6        | create_clock -period 6.000 [get_ports tx_clk]                                 |  |

| CII.     |                                                                               |  |

| So       |                                                                               |  |

|          |                                                                               |  |

| <b>i</b> |                                                                               |  |

| ×        |                                                                               |  |

|          |                                                                               |  |

Figure 5: OOC XDC

- 9. Select the **Save File** button 🖺 to save the updated contents of the OOC XDC file.

- 10. Check to be sure that the create clock commands are removed from the IP XDC file (uart top.xdc), and save the file.

The create clock constraints are not necessary because parent design defines the clocks. The IP XDC file should now only contain the constraints, as shown in the following figure. The OOC XDC file defines the clocks needed for standalone processing.

| ∑ Project Summary × 📴 uart_top.xdc × 📳 uart_top_ooc.xdc ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 ? | . × |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|

| C:/Data/ug939-design-files/lab_3/my_simple_uart/my_simple_uart.srcs/constrs_1/imports/constrs/uart_top.xdc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |   |

| 1 set_multicycle_path -from [get_cells "uart_rx_i0/uart_rx_ctl_i0/*" \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     | * |

| 2 -filter {IS_SEQUENTIAL}] -to [get_cells "uart_rx_i0/uart_rx_ctl_i0/*" \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |   |

| Image: Sequential of the sequence of the se |     |     |   |

| 4 set_multicycle_path -from [get_cells "uart_rx_i0/uart_rx_ctl_i0/*" \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |   |

| 5 -filter {IS_SEQUENTIAL}] -to [get_cells "uart_rx_i0/uart_rx_ctl_i0/*" \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |     |   |

| <pre>X 8 set_multicycle_path -from [get_cells "uart_tx_i0/uart_tx_ct1_i0/*" \</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |   |

| <pre>// 9 -filter {IS_SEQUENTIAL}] -to [get_cells "uart_tx_i0/uart_tx_ctl_i0/*" \</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |     |   |

| <pre>10 -filter {IS_SEQUENTIAL}] 90 11 set multicycle path -from [get cells "uart tx i0/uart tx ctl i0/*" \ 12 -filter {IS_SEQUENTIAL}] -to [get cells "uart tx i0/uart tx ctl i0/*" \</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |   |

| <pre>11 set multicycle_path -irom [get_cells "uart_tx_10/uart_tx_ct1_10/*" \</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

| a 13 -filter {IS_SEQUENTIAL}] -hold 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |   |

| 15 set max delay -from [get cells uart rx i0/meta harden rxd i0/signal meta reg] \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

| <pre>     16 -to [get_cells uart_rx_10/meta_harden_rxd_10/signal_dst_reg] \     17 [get property PERIOD [get clocks -of objects [get ports rx clk]]] </pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

| <b>⊉</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     | - |

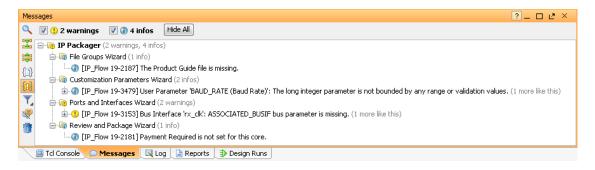

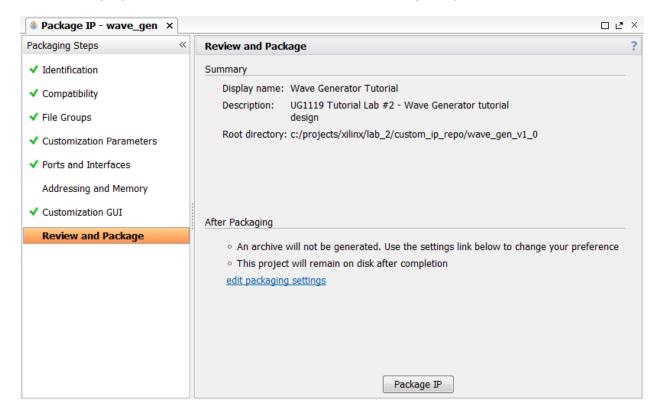

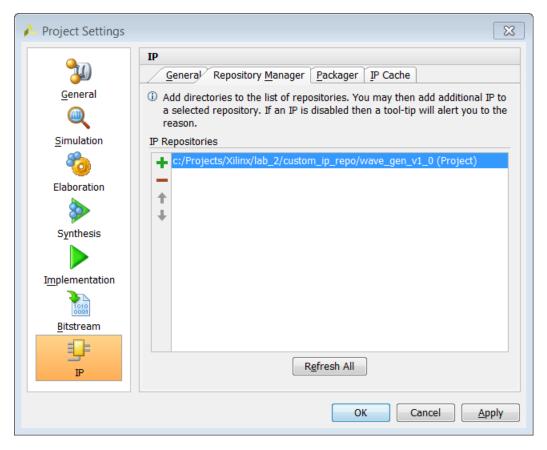

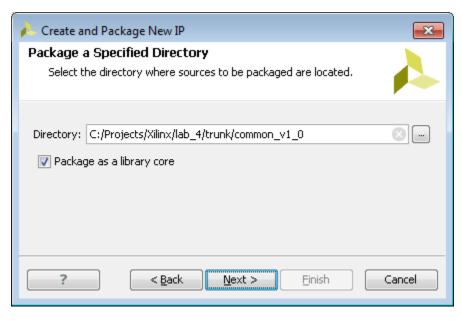

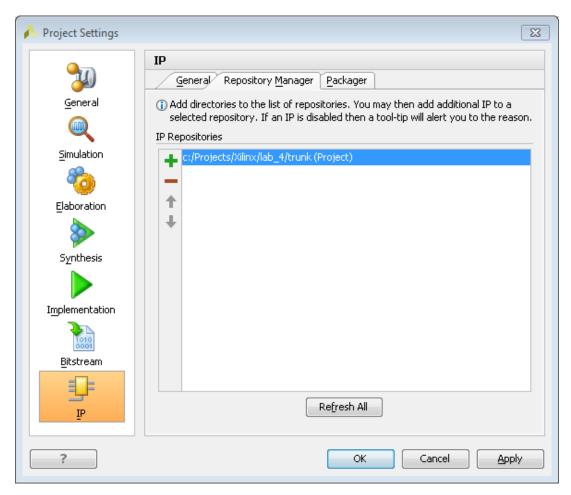

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | - b |   |