# Zynq UltraScale+ MPSoC Embedded Design Methodology Guide

UG1228 (v1.0) March 31, 2017

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                |

|------------|---------|-------------------------|

| 03/31/2017 | 1.0     | Initial public release. |

# Table of Contents

| Revision History | <br> |

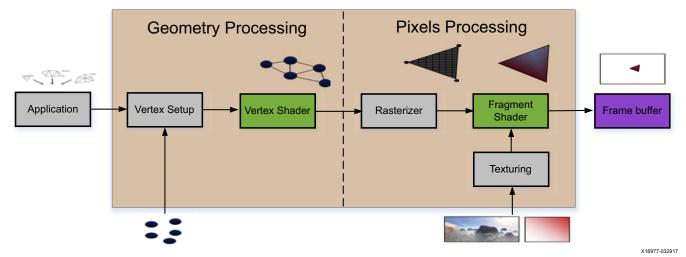

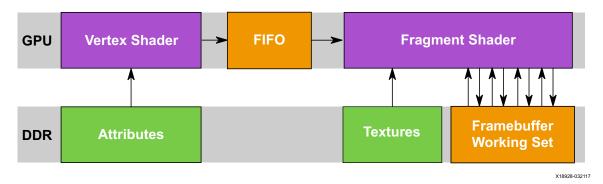

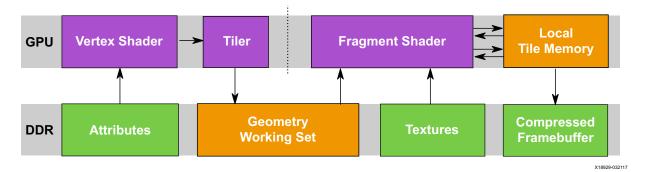

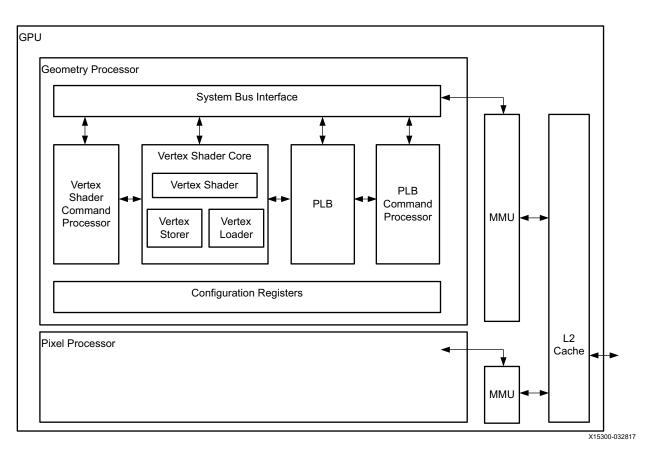

|------------------|------|

|                  |      |

#### **Chapter 1: Introduction**

| Block Diagram                        | 7  |

|--------------------------------------|----|

| Vector Methodology                   | 9  |

| Accessing Documentation and Training | 11 |

#### Chapter 2: Processing System

| Defining Your Processing Needs 1             | 3 |

|----------------------------------------------|---|

| Processing System Methodology 14             | 4 |

| Heterogeneous Computing Concepts 18          | 8 |

| Application Processing Unit (APU) 20         | 0 |

| APU Virtualization Support    2              | 3 |

| Real-Time Processing Unit (RPU)    2         | 7 |

| Interconnect                                 | 9 |

| Interrupts                                   | 7 |

| Workload Acceleration Using the PL         4 | 2 |

| General-Purpose Computing Acceleration 44    | 4 |

#### **Chapter 3: System Software Considerations**

| Defining Your System Software Needs | 46 |

|-------------------------------------|----|

| System Software Methodology         | 47 |

| Boot Process Software               | 53 |

| System Software Stacks              | 58 |

| OpenAMP Framework                   | 64 |

| Xen Hypervisor                      | 67 |

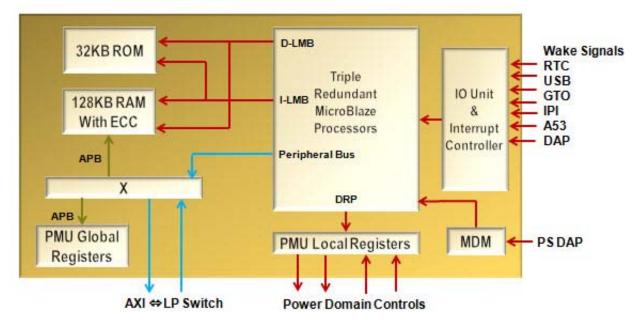

| PMU Software                        | 70 |

| Software Development Tools          | 72 |

| Developer Flow                      | 75 |

#### **Chapter 4: Power Considerations**

| Defining Your Power Needs | 80 |

|---------------------------|----|

| Power Tuning Methodology  | 81 |

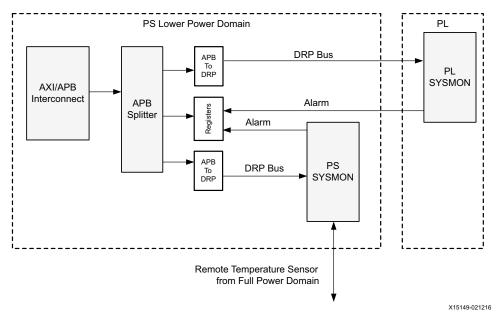

| Four Major Power Domains               | 86 |

|----------------------------------------|----|

| Power Islands and Power Gating         | 92 |

| Platform Management Unit               | 93 |

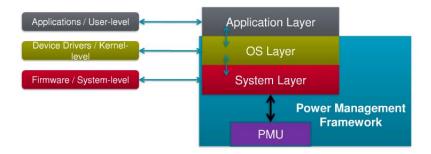

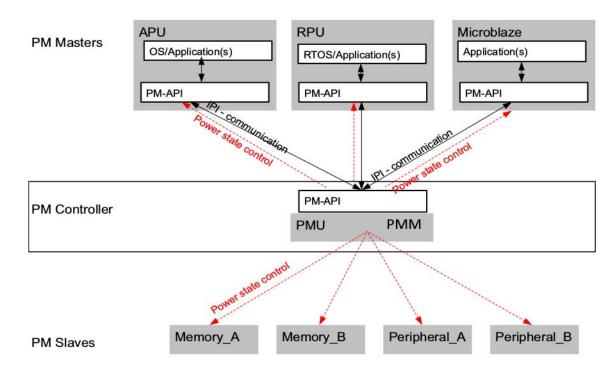

| Power Management Software Architecture | 95 |

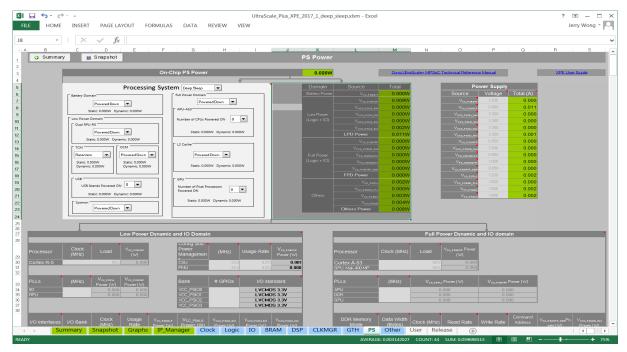

| Xilinx Power Estimator                 | 96 |

### Chapter 5: Programmable Logic

| Defining Your PL Needs                    | 97  |

|-------------------------------------------|-----|

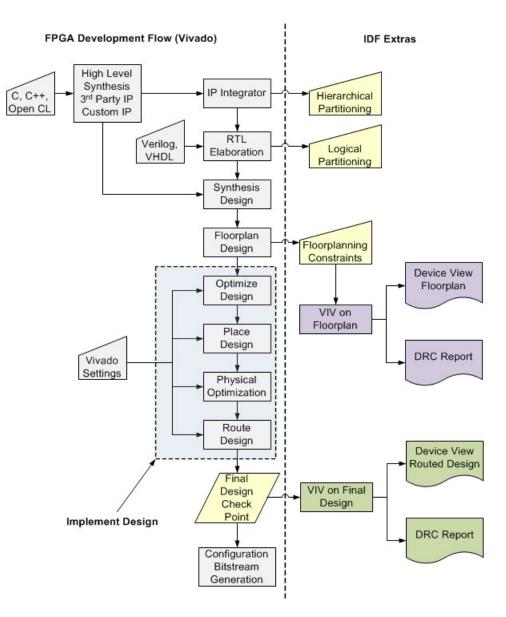

| PL Methodology                            | 98  |

| Logic                                     | 104 |

| Integrated IP Support                     | 108 |

| Configuration and Partial Reconfiguration | 110 |

| Power Reduction Features                  | 111 |

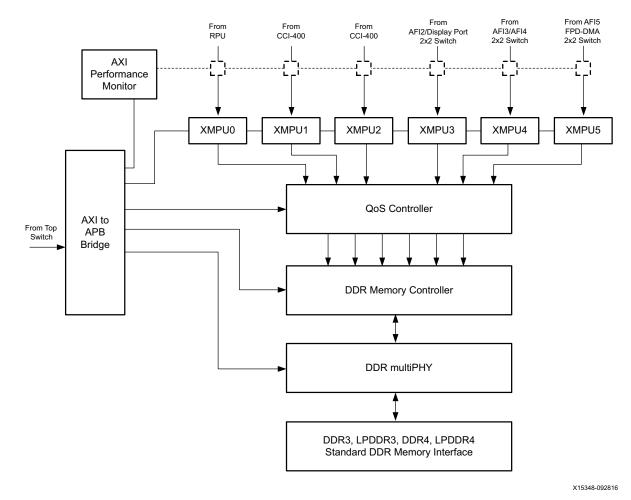

#### Chapter 6: Memory

| Memory Introduction          | 113 |

|------------------------------|-----|

| Defining Your Memory Needs   | 113 |

| Memory Methodology           | 114 |

| Built-In Memory Blocks       | 116 |

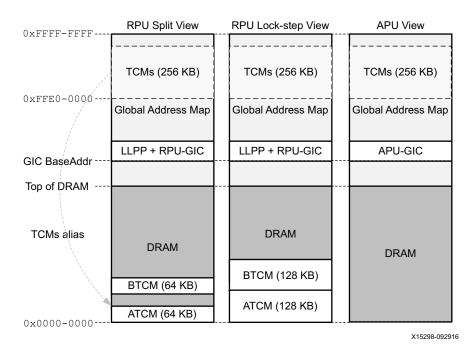

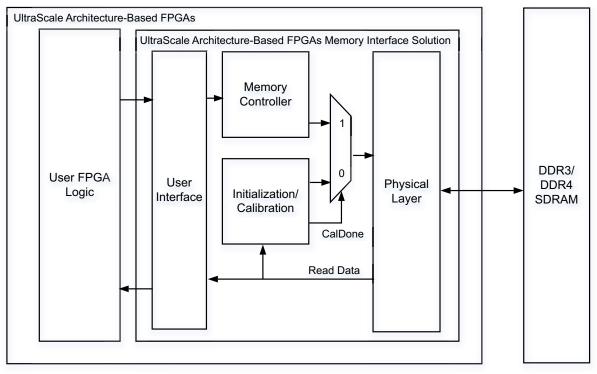

| PS DDR Memory and Controller | 118 |

| Global System Memory Map     | 119 |

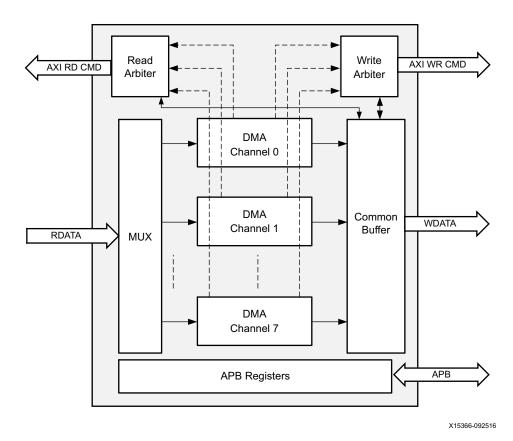

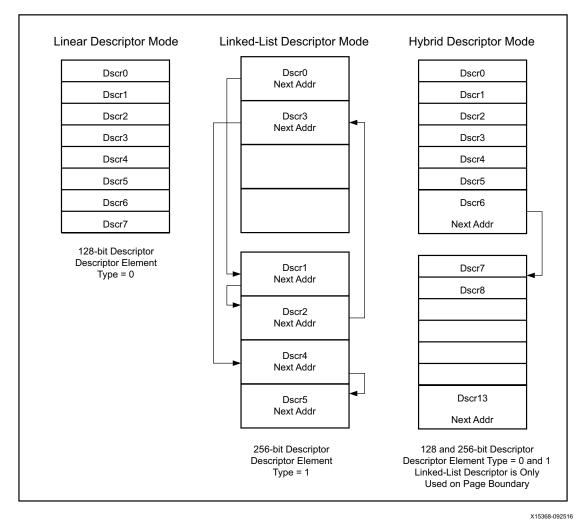

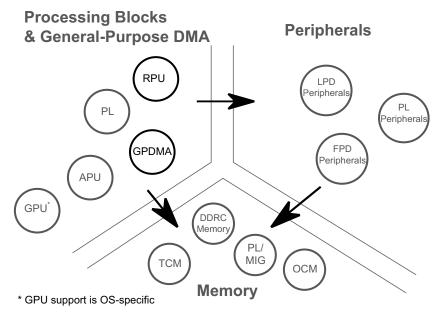

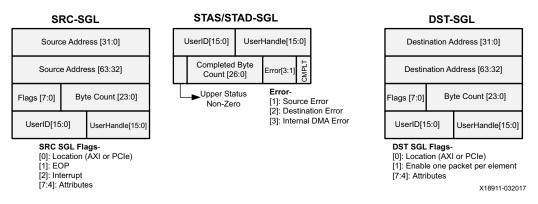

| PS DMA Controllers           | 121 |

| External Memory with the PL  | 125 |

#### **Chapter 7: Resource Isolation and Partitioning**

| Defining Your Resource Isolation and Partitioning Needs | 127 |

|---------------------------------------------------------|-----|

| Resource Isolation and Partitioning Methodology         | 128 |

| ARM TrustZone                                           | 135 |

| System Memory Management Unit                           | 139 |

| Xilinx Memory Protection Unit                           | 142 |

| Xilinx Peripheral Protection Unit                       | 145 |

| Xen Hypervisor                                          | 149 |

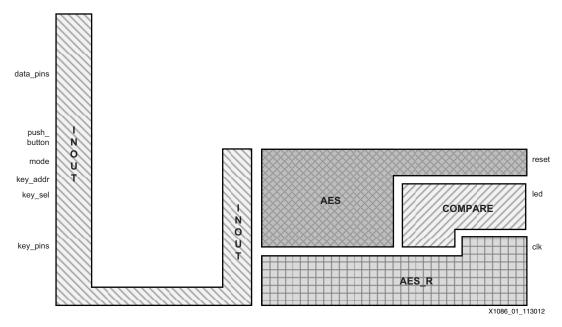

### Chapter 8: Security

| Defining Your Security Needs           | 150 |

|----------------------------------------|-----|

| Security Methodology                   | 151 |

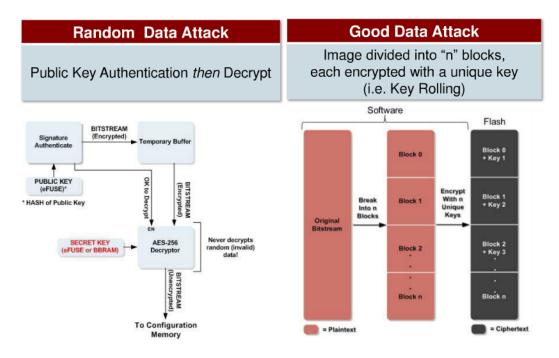

| Security Features Overview             | 153 |

| Configuration Security and Secure Boot | 155 |

| Device and Data Security               | 159 |

| Protection Against DPA Attacks         | 162 |

| CSU Hardware Accelerators | 163 |

|---------------------------|-----|

| Functional Safety         | 163 |

#### **Chapter 9: Multimedia**

| Defining Your Multimedia Needs | 165 |

|--------------------------------|-----|

| Multimedia Methodology         | 166 |

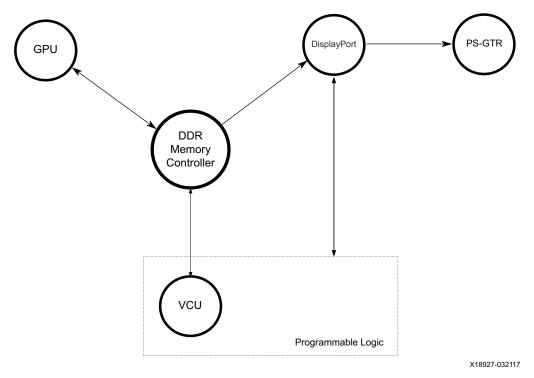

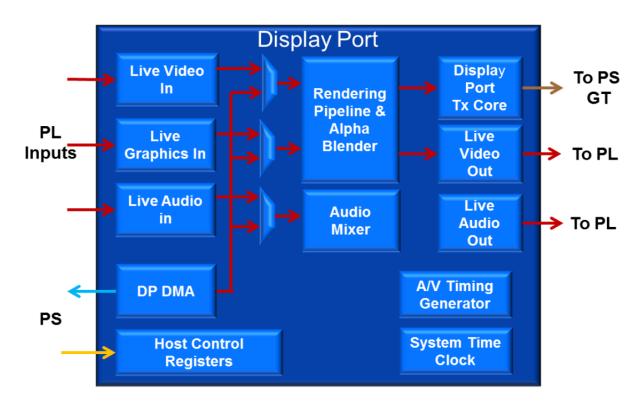

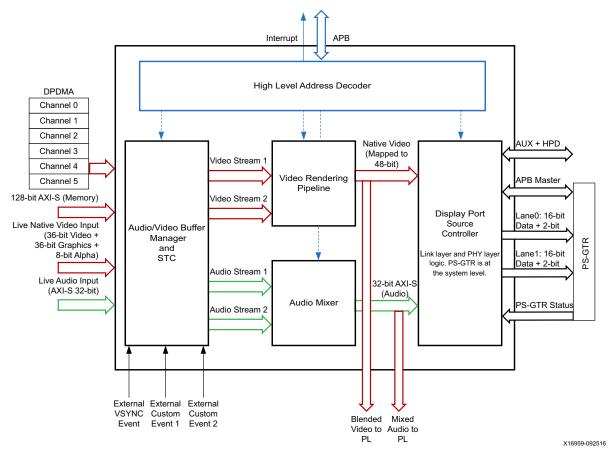

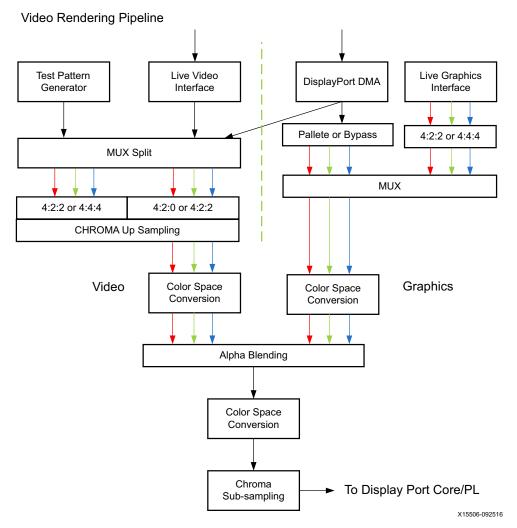

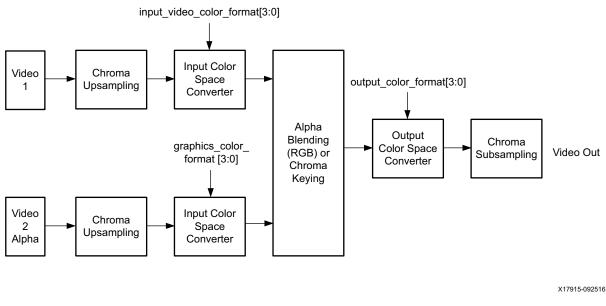

| DisplayPort                    | 167 |

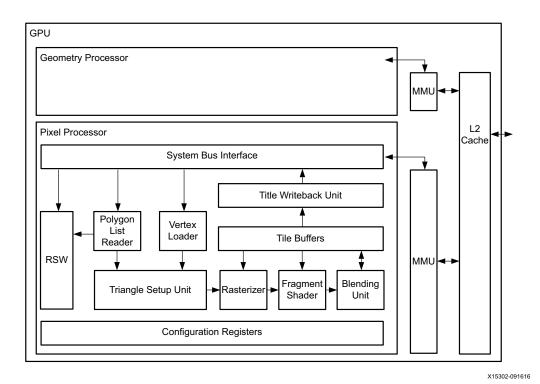

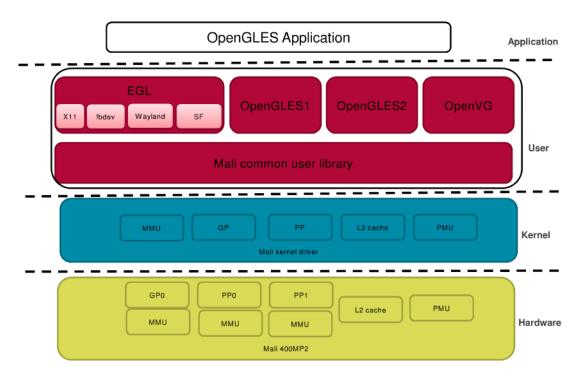

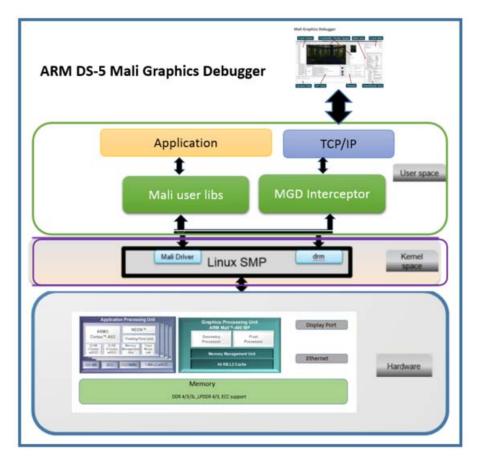

| GPU                            | 173 |

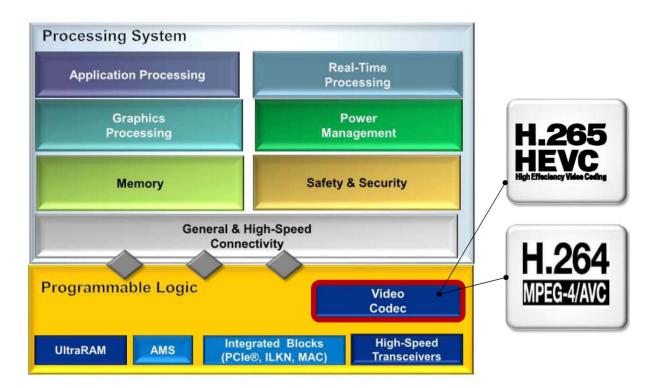

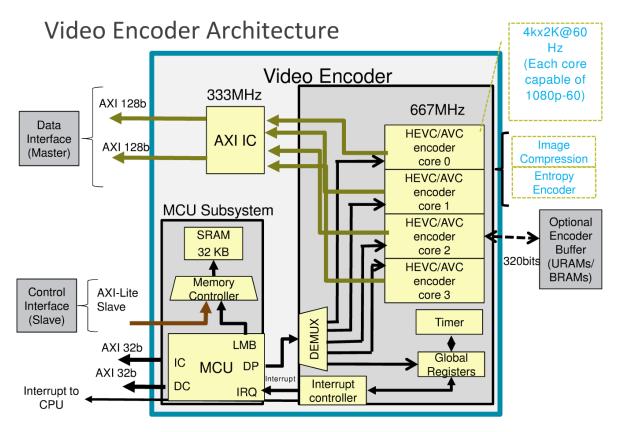

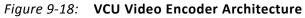

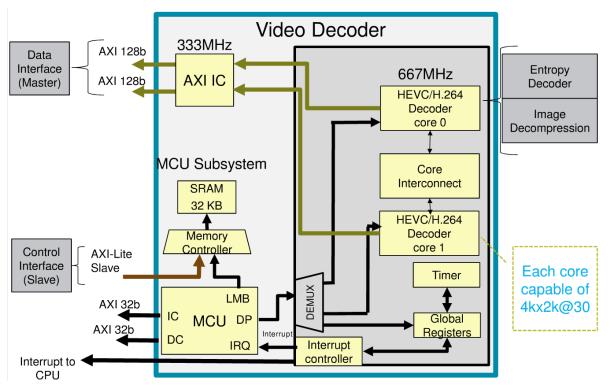

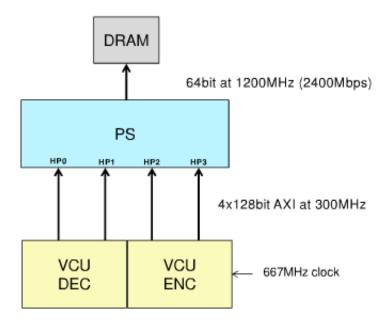

| VCU                            | 181 |

#### **Chapter 10: Peripherals**

| Defining Your Peripherals Needs 1 | .87 |

|-----------------------------------|-----|

| Peripherals Methodology 1         | .88 |

| GPIO 1                            | 91  |

| I2C 1                             | .94 |

| SPI 1                             | .95 |

| UART 1                            | .96 |

| CAN Controller                    | .97 |

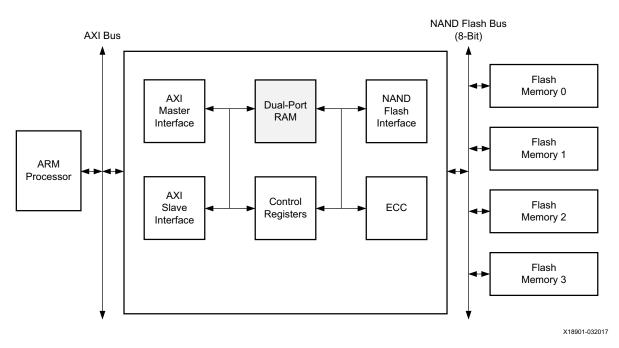

| NAND 2                            | 01  |

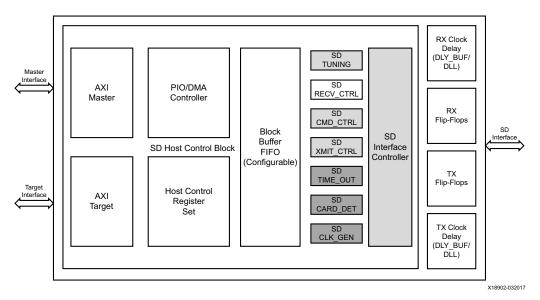

| SD/SDIO/eMMC                      | 02  |

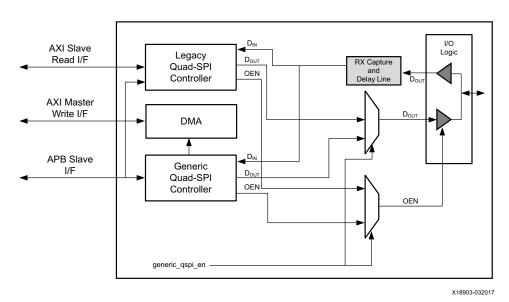

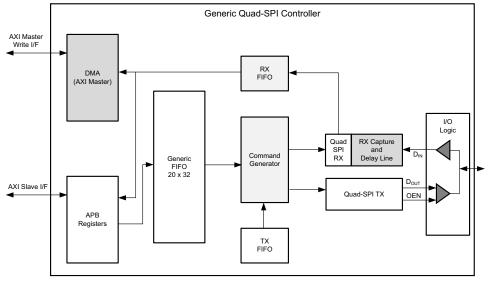

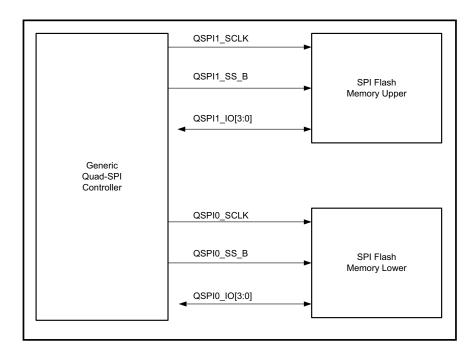

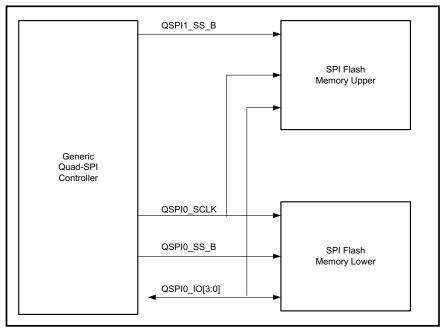

| Quad-SPI                          | 03  |

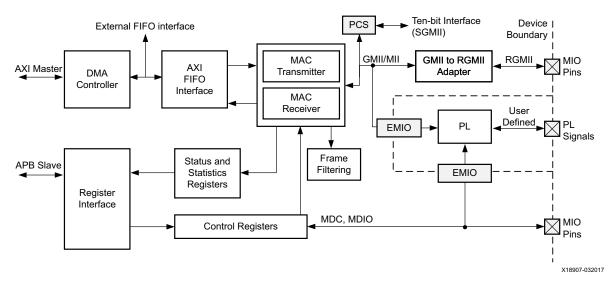

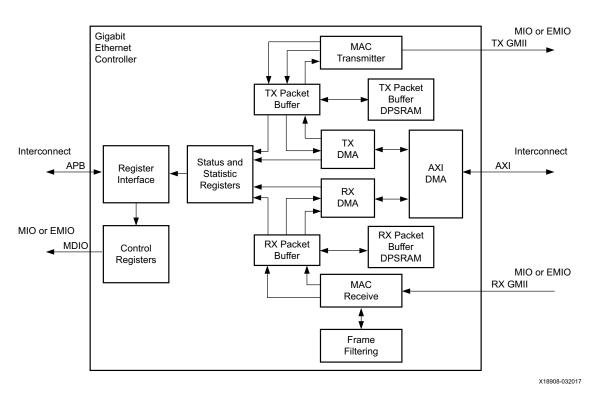

| Gigabit Ethernet Controller 2     | 06  |

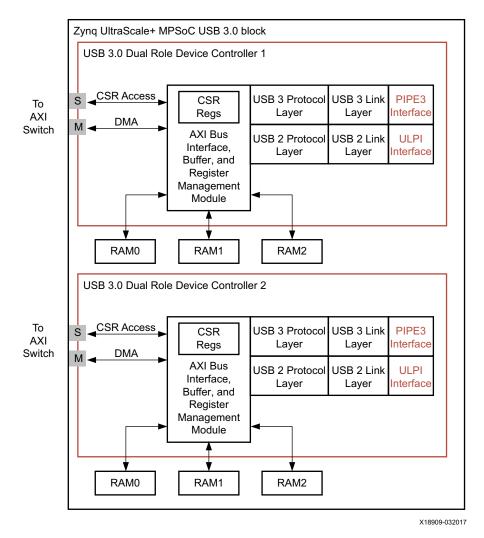

| USB 2                             | :09 |

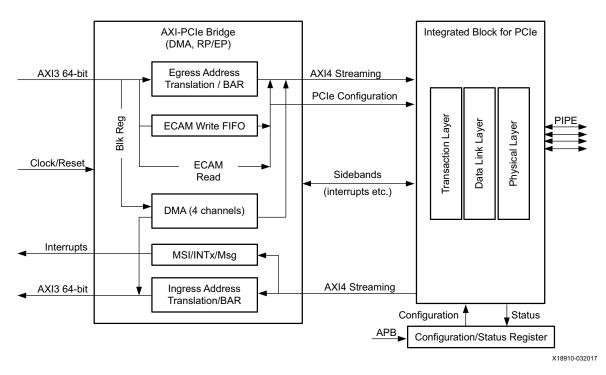

| PCI Express                       | 11  |

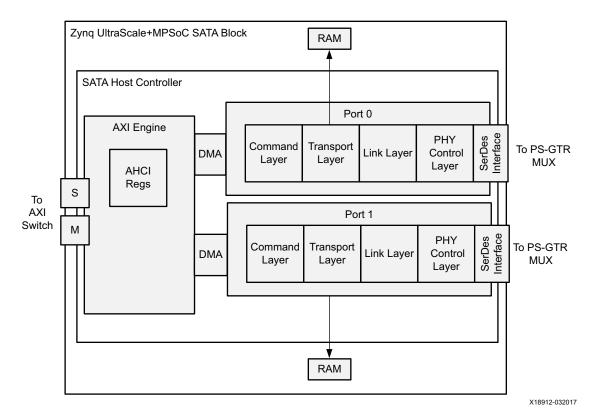

| SATA 2                            | 13  |

| DisplayPort                       | 14  |

### Appendix A: Additional Resources and Legal Notices

| 215 |

|-----|

| 215 |

| 215 |

| 216 |

| 217 |

|     |

# Chapter 1

# Introduction

The Zynq® UltraScale+<sup>™</sup> MPSoC platform offers designers the first truly all-programmable, heterogeneous, multiprocessing system-on-chip (SoC) device. Smart systems are increasing in complexity with applications in the automotive industry, large database deployments, and even space exploration, pushing the requirements of each new generation of SoC to its limits. Requirements for increased power control, real-time applications, intensive graphical capabilities, and processing power demand a platform with maximum flexibility. The Zynq UltraScale+ MPSoC platform provides leading edge features that modern systems designers demand.

Built on the next-generation 16 nm FinFET process node from Taiwan Semiconductor Manufacturing Company (TSMC), the Zynq UltraScale+ MPSoC contains a scalable 32 or 64-bit multiprocessor CPU, dedicated hardened engines for real-time graphics and video processing, advanced high-speed peripherals, and programmable logic. The platform delivers maximum scalability through either dual or quad-core APU devices, offloading of critical applications like graphics and video pipelining to dedicated processing blocks, and the ability to turn blocks on and off through efficient power domains and gated power islands. With a wide range of interconnect options, digital signal processing (DSP) blocks, and programmable logic choices, the Zynq UltraScale+ MPSoC has the flexibility to fit a diverse set of user application requirements.

This guide can be viewed as a toolbox for making decisions for a user design with respect to the UltraScale+ MPSoC feature set. Please review the recommendations and trade-offs carefully when determining what works best for your product. This guide is organized around the Vector Methodology (described in Vector Methodology) to provide an initial diagrammatic view of system design requirements mapped against the Zynq UltraScale+ MPSoC primary features. The Vector Methodology does not ensure maximum use of the capabilities of the platform, but rather provides a graphical representation of the trade-offs and solutions a user can make when building their product on the platform. This can result in the de-prioritization of certain platform features within the context of the overall solution. Using the Vector Methodology allows designers to accurately target other team members, such as Hardware Designers, Architects, and Software Engineers, to the relevant sections of the methodology applicable to their roles.

# **Block Diagram**

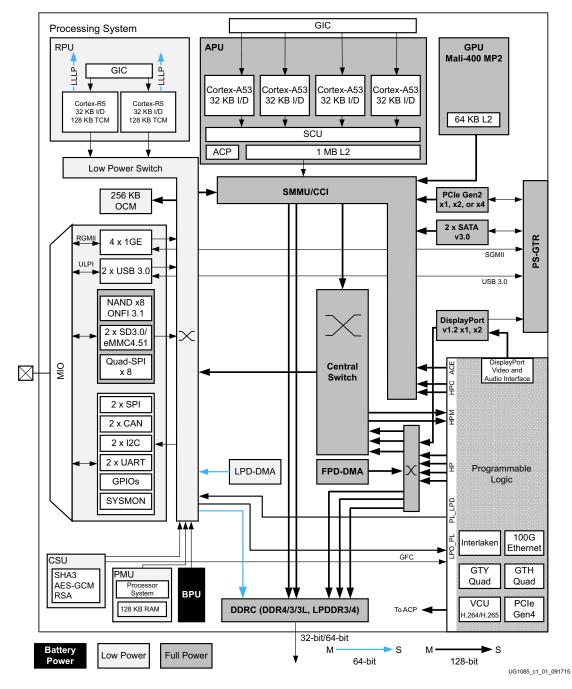

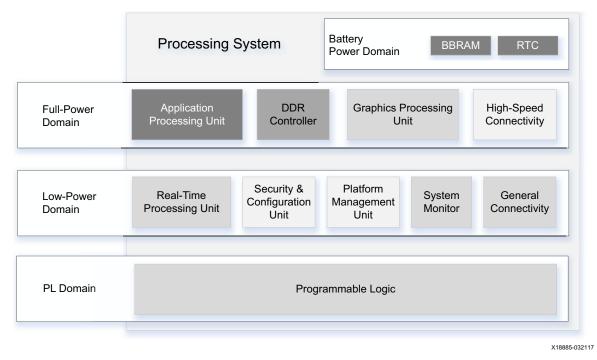

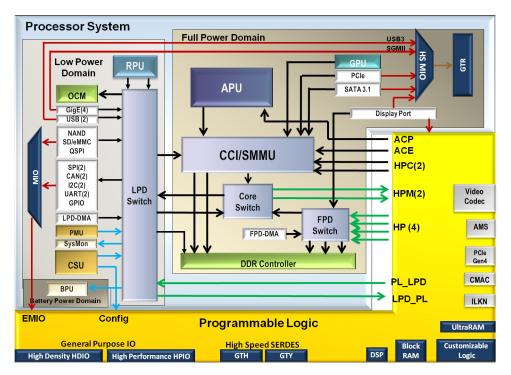

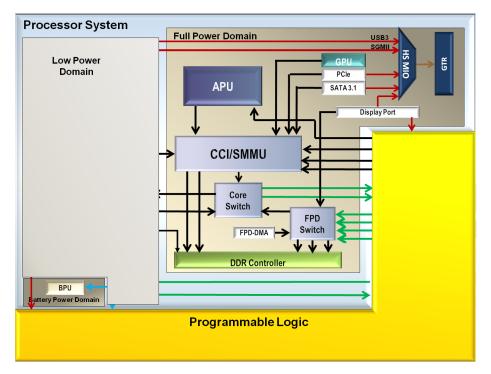

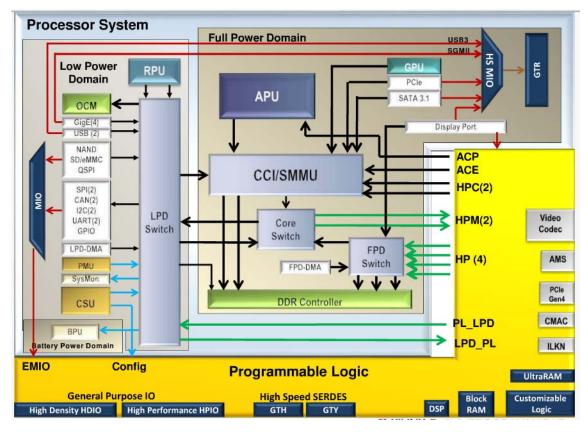

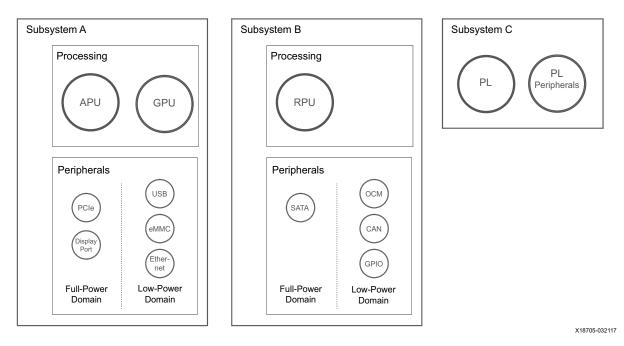

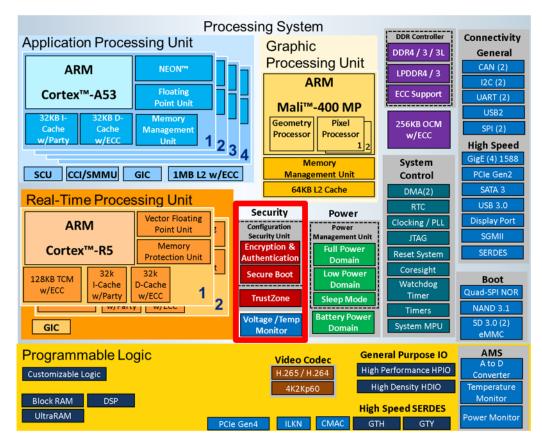

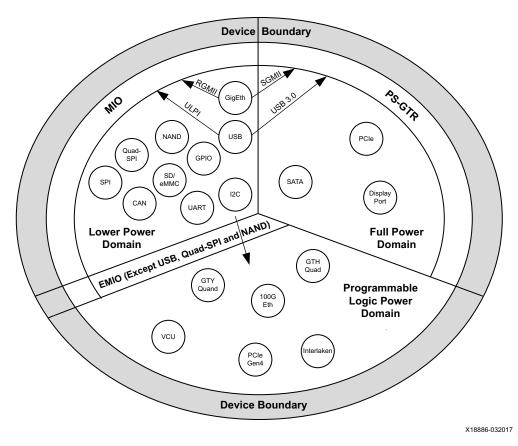

A Zynq UltraScale+ MPSoC device consists of two major underlying processing system (PS) and programmable logic (PL) blocks in two isolated power domains.

PS acts as one standalone MPSoC device and is able to boot and support all the features shown in Figure 1-1, page 8 without powering on the PL. Each of the individual embedded blocks are covered in this manual.

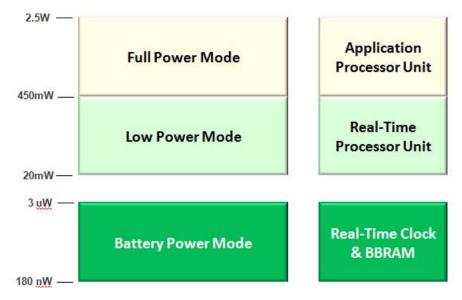

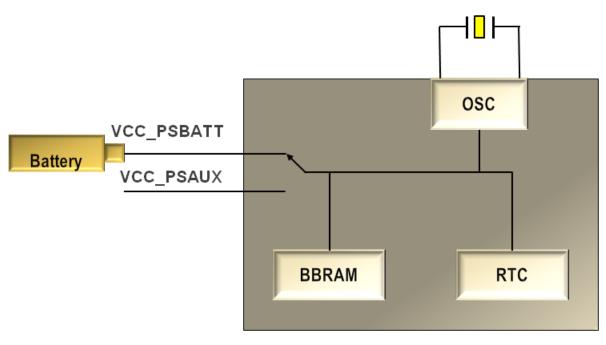

The Zynq UltraScale+ MPSoC device has four different power domains:

- Low-power domain (LPD)

- Full-power domain (FPD)

- PL power domain (PLPD)

- Battery power domain (BPD)

Each power domain can be individually isolated. The platform management unit (PMU) on the LPD facilitates the isolation of each of the power domains. Since each power domain can be individually isolated, functional isolation (an important aspect of safety and security applications) is possible. Additionally, the isolation can be automatically turned on when

one of the power supplies of the corresponding power domain unintentionally powers down.

Figure 1-1: Block Diagram

# **Vector Methodology**

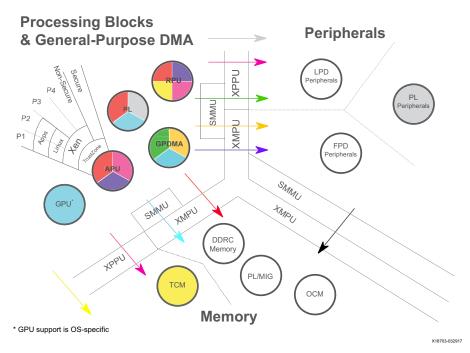

The Vector Methodology, as applied to the Zynq UltraScale+ MPSoC device, is described by the following diagram:

Figure 1-2: Vector Methodology Diagram

In this diagram, each line radiating out from the center point represents a functional domain of the Zynq UltraScale+ MPSoC platform. The center point represents zero requirements/need for that functional domain, while the end of each line represents a high level of requirements/need/complexity. Taking this diagram as a starting point, a Systems Architect, working with a FAE or Sales Engineer, can plot the degree to which a specific functional domain applies to their design and link those points together to get a general sense of the problem set they are trying to address.

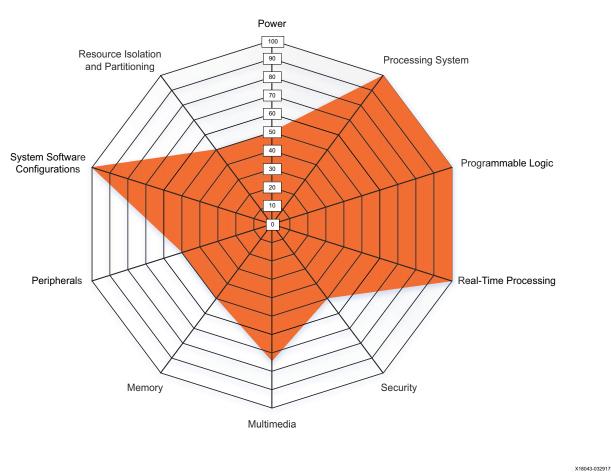

Consider the following Advanced Driver Assistance System (ADAS) example:

#### Advanced Driver Assistance System (ADAS) Design Example

#### Figure 1-3: Vector Methodology Example: Advanced Driver Assistance System

In this example, we can see that the system software configurations, real-time processing, programmable logic, and processing system are all at the maximum value. This translates into a likely greater emphasis on specific chapters within this guide that explain the parts of the MPSoC that a designer needs to focus on, and their pros/cons and limitations for every one of those four vectors. With average need for power, security, multimedia, peripherals, and resource isolation and partitioning needs, you can then appropriately scale back the efforts to use in these areas. This allows more freedom to focus efforts on vectors that are more critical to the product. Therefore, use of this guide allows you to translate your level of requirements into a set of design choices and vary the degree of effort and the resources put into optimizing certain parts of their UltraScale+ MPSoC-based designs.

**Note:** Although the diagram is meant as flexible tool for gauging the relevance of this guide's different chapters, that is NOT to say that any vectors should be skipped. Be sure to read the entire methodology guide before you make final design decisions.

# **Accessing Documentation and Training**

Access to the right information at the right time is critical for timely design closure and overall design success. Reference guides, user guides, tutorials, and videos get you up to speed as quickly as possible with Xilinx tools. This section lists some of the sources for documentation and training.

### Using the Documentation Navigator

The Xilinx Documentation Navigator ships as part of the Xilinx tools. It provides an environment to access and manage the entire set of Xilinx software and hardware documentation, training, and support materials. Documentation Navigator allows you to view current and past Xilinx documentation. The documentation display can be filtered based on release, document type, or design task. When coupled with a search capability, you can quickly find the right information.

Documentation Navigator scans the Xilinx website to detect and provide documentation updates. The Update Catalog feature alerts you to available updates, and gives details about the documents that are involved. Xilinx recommends that you always update the catalog when alerted to keep it current. You can establish and manage local documentation catalogs with specified documents.

The Documentation Navigator has a tab called the *Design Hub View*. Design hubs are collections of documentation related by design activity, such as Zynq UltraScale+ MPSoC Design Overview, PetaLinux Tools, and the Xilinx Software Development Kit (SDK). Documents and videos are organized in each hub in order to simplify the learning curve for that area. Each hub contains an Embedded Processor Design section, a Design Resources section, and a list of support resources. For new users, the Embedded Processor Design section (shown in Figure 1-4) provides a good place to start.

| Xilinx Documentation Navigator                                         |   | 4 - Catalog View                                                                         |     |            |          |            |

|------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------|-----|------------|----------|------------|

| Catalog View Design Hub View                                           |   |                                                                                          |     |            |          |            |

| Catalog 2017.03.14                                                     | _ | Xilinx Design Tools 2016.4/14.7   CurrentFilterSettings+Hidden                           |     | 💽 (M) 🔎    |          |            |

| Document Filters                                                       | _ | Find in Grid: power estimator 🛛 🗙 💌 👔 🖄 🖄                                                |     | 1          | M Search | n Docs     |

| Silicon Devices<br>Zyng UltraScale+ MPSoC                              |   | Displaying 41 of 4059 Documents                                                          | тос | Doc ID     | Version  | Published  |

| UltraScale & UltraScale+                                               |   | 늘 Zynq UltraScale+ MPSoC : Data Sheets                                                   |     |            |          |            |

| Zynq-7000                                                              |   | 搅 Zyng UltraScale+ MPSoC Overview                                                        |     | 🔵 DS891    | V1.4     | 2017-02-15 |

| 7 Series                                                               |   | 🔀 XA Zyng UltraScale+ MPSoC Overview                                                     |     | DS894      | V1.1     | 2017-03-23 |

| Virtex-6                                                               |   | Zyng UltraScale+ MPSoC Product Tables and Product Selection Guide                        |     | XMP104     | V2.2     | 2017-02-15 |

| Virtex-5<br>Spartan-6                                                  |   |                                                                                          |     | -          |          |            |

| CoolRunner                                                             |   | 📜 XA Automotive Portfolio Product Tables and Product Selection Guide                     |     | XMP106     | V1.0     | 2017-03-09 |

| Design Tools                                                           |   | 📜 Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics                 |     | OS925      | V1.1     | 2017-02-10 |

| PetaLinux                                                              |   | 💼 Zynq UltraScale+ MPSoC : User Guides                                                   |     |            |          |            |

| SDAccel                                                                |   | 💢 Zynq UltraScale+ MPSoC: Software Developers Guide                                      |     | 💮 UG1137   | V3.0     | 2016-12-15 |

| SDSoC                                                                  |   | Zyng UltraScale+ MPSoC Packaging and Pinouts Product Specification                       |     | G1075      | V1.2     | 2017-01-13 |

| Software Development Kit Vivado                                        |   | Z Zyng UltraScale+ MPSoC Technical Reference Manual                                      |     | UG1085     | V1.4     | 2017-02-02 |

| ISE Design Suite                                                       |   |                                                                                          |     | •          |          |            |

| ChipScope                                                              | = | Zynq UltraScale+ MPSoC: Power Management Framework User Guide                            |     | 🔘 UG1199   | V1.0     | 2016-10-05 |

| EDK and SDK                                                            |   | 🚺 Zynq UltraScale+ MPSoC QEMU: User Guide                                                |     | 🎯 UG1169   | V2016.4  | 2016-11-30 |

| ISE ISE                                                                |   | 搅 Zynq UltraScale+ MPSoC OpenAMP: Getting Started Guide                                  |     | 🍚 UG1186   | V2016.4  | 2017-02-14 |

| PlanAhead                                                              |   | Zynq UltraScale+ MPSoC Register Reference                                                |     | 🔗 UG1087   |          |            |

| System Generator                                                       |   | 💢 Embedded Energy Management Interface: EEMI API Reference Guide                         |     | 💮 UG1200   | V1.0     | 2016-09-07 |

|                                                                        |   | Zyng UltraScale+ MPSoC : Methodology Guides                                              | _   |            |          |            |

| Document Types                                                         |   |                                                                                          |     | UG1046     | V2.1     | 2015-04-22 |

| Application Notes                                                      |   | UltraFast Embedded Design Methodology Guide                                              |     | •          |          |            |

| Characterization Reports                                               |   | Zynq Migration Guide: Zynq-7000 AP SoC to Zynq UltraScale+ MPSoC Devices                 |     | 🔘 UG1213   | V2.0     | 2016-11-30 |

| Customer Notices                                                       |   | Zynq UltraScale+ MPSoC : Device Models                                                   |     |            |          |            |

| <ul> <li>Data Sheets</li> <li>Design Advisories</li> </ul>             |   | Zynq UltraScale+ MPSoCs - BSDL Models                                                    |     | ð          |          | 2016-10-20 |

| Design Hubs                                                            |   | Zyng UltraScale+ MPSoCs - IBIS Models                                                    |     | ð          |          | 2016-05-12 |

| V Device Models                                                        |   | Zynq UltraScale+ MPSoCs - Package Thermal Models                                         |     | ð          |          | 2016-05-06 |

| ✓ Errata                                                               |   | Zynq UltraScale+ MPSoC : Design Advisories                                               |     | •          |          |            |

| V Help                                                                 |   |                                                                                          |     | 1.000074   |          | 2046 42 42 |

| <ul> <li>Methodology Guides</li> <li>Package Specifications</li> </ul> |   | R Design Advisory Master Answer Record for Zynq UltraScale+ MPSoC Devices                |     | 2 AR66071  |          | 2016-12-12 |

| Package Specifications Product Guides                                  |   | R Design Advisory for Zynq UltraScale+ MPSoC: Boot from NAND might fail if there is data | •   | AR68615    |          | 2017-02-14 |

| Product Pages                                                          |   | 🖻 Design Advisory for Zynq UltraScale+ MPSoC: FSBL authenticates the boot image in exter |     | 🔗 AR68210  |          | 2016-12-05 |

| Reference Guides                                                       |   | R Design Advisory for Zynq UltraScale+ MPSoC and Kintex UltraScale+ FPGA - Updated pac.  |     | 2 AR66944  |          | 2016-08-23 |

| Release Notes                                                          |   | R Design Advisory for Zyng UltraScale+ MPSoC Processing System - How do I upgrade fro    |     | AR67861    |          | 2016-10-13 |

| Tutorials & Getting Started                                            |   | Zynq UltraScale+ MPSoC : Application Notes                                               |     | -          |          |            |

| User Guides                                                            |   |                                                                                          |     | A VADD1202 | 10.0.0   | 2017 02 27 |

| Video Tutorials White Papers                                           |   | XAPP1303 - Integrating LogiCORE SEM IP with AXI in Zynq UltraScale+ Devices              |     | XAPP1303   |          | 2017-02-27 |

| Functional Categories                                                  |   | XAPP1298 - Integrating LogiCORE SEM IP in Zynq UltraScale+ Devices                       |     | XAPP1298   |          | 2017-02-27 |

| AXI                                                                    |   | 📜 XAPP1289 - Using DMA with Zynq UltraScale+ MPSoC Controller for PCI Express as Root P. | . I | 🍚 XAPP1289 | V1.0     | 2016-06-20 |

| Boards & Kits                                                          | - | 💢 XAPP1276 - All Digital VCXO Replacement Using a Gigabit Transceiver Fractional PLL     |     | XAPP1276   | V1.0     | 2016-05-27 |

Figure 1-4: Documentation Navigator

# Chapter 2

# **Processing System**

The Zynq® UltraScale+<sup>™</sup> MPSoC device gives system designers considerable power and flexibility in the way the on-board processing capabilities can be used. In addition to the configurability of the application processing unit (APU) and the real-time processing unit (RPU), the Zynq UltraScale+ MPSoC device provides several dedicated processing blocks for taking care of different types of tasks. This chapter covers the processing system capabilities of the Zynq UltraScale+ MPSoC device, their interconnection and the recommendations for their use.

## **Defining Your Processing Needs**

Modern-day embedded designs often combine a complex mix of workloads, constraints and external dependencies. Finding the best fit between each of your application's processing needs within the many processing blocks of the Zynq UltraScale+ MPSoC device is crucial to ensuring overall product success. The next section will start introducing you to the core concepts behind each of the processing blocks of the Zynq UltraScale+ MPSoC device while each block and important component will be discussed in greater detail later in this chapter.

Meanwhile, you can start thinking about the following questions with regards to your design:

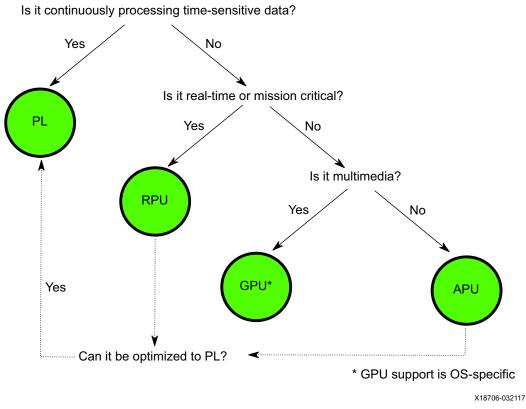

- 1. What are the critical needs for your application? For each part:

- a. Is it continuously processing time-sensitive data?

- b. Is it real-time or mission critical?

- c. Does it relate to multimedia? Or, rather, is it a general-purpose computing workload?

- d. Does it require acceleration beyond the processing system's performance?

- 2. What type of interaction is required between system components? For each set of components:

- a. Do they need to exchange data?

- b. If so, how much and at what frequency?

- c. Do they need to notify each other of key events?

- 3. What type of interaction is required with the external world? For each part:

- a. What kind of memory needs does it have?

- b. Is it triggered by or does it respond to interrupts?

- c. Does it need to utilize peripheral I/O?

- 4. Which components in your design are power sensitive?

# **Processing System Methodology**

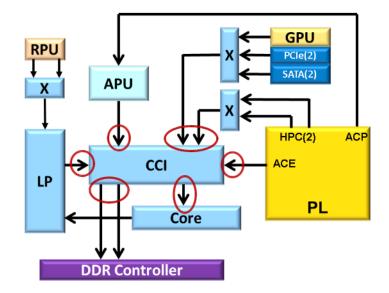

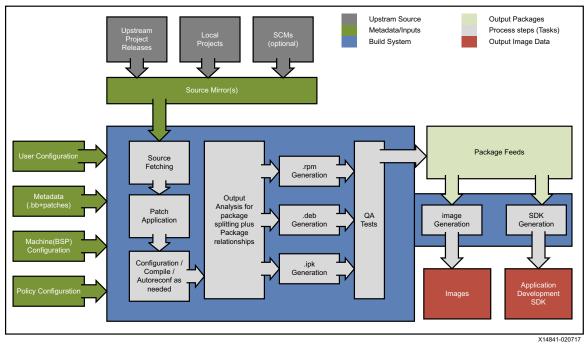

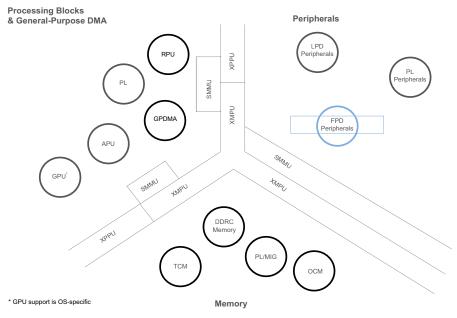

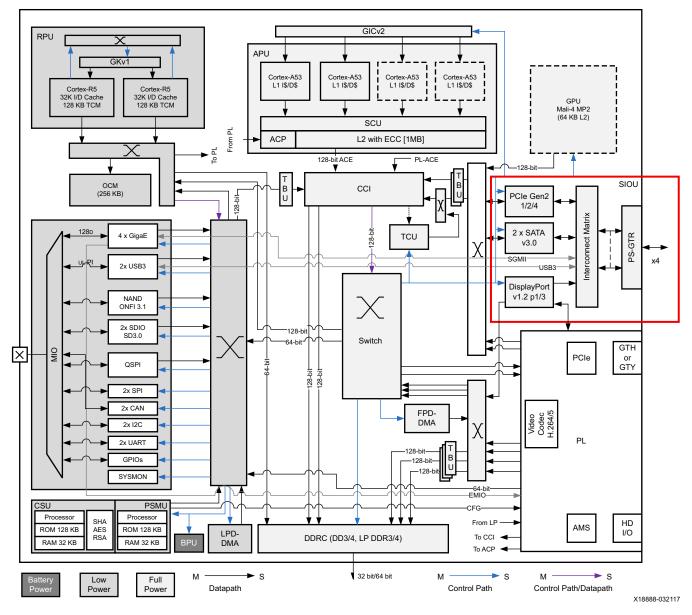

Given the flexibility of the Zynq UltraScale+ MPSoC device, care must be taken in thoroughly analyzing its processing capabilities before mapping your design to any given part. To that end, the following diagram provides a simplified view of the full system diagram presented in this guide's introduction that highlights the main processing blocks of the Zynq UltraScale+ MPSoC device and their interconnection through the interconnect, with the blocks capable of conducting some form of customizable processing highlighted in green.

**Note:** Figure 2-1 does NOT attempt to precisely represent the internal blocks of the Zynq UltraScale+ MPSoC device. Instead, it is primarily a conceptual view for the purposes of the present explanation.

Figure 2-1: Overall Processing-Capable Blocks

In the following sections we will cover the various highlighted blocks in detail along with their related interrupt capabilities, the interconnect, and the main inter processor communication mechanism of the Zyng UltraScale+ MPSoC device. There interconnect is made up of several different types of blocks, for instance, each warranting its own separate discussion. For the purposes of the present explanation, we will focus on the high-level capabilities of each part of the system.

Looking at any given type of processing need found in your design, what you can control as hinted to by the questions in the previous section - is:

- Processing location ٠

- Interconnect between processing locations ٠

- Interaction with external world: •

- 0 Memory

- Interrupts ۰

- Peripheral I/O ۰

In terms of processing location, there are typical candidate blocks for certain types of workloads:

| Block | Optimized For:                                                            | Ideal For:                                                                                                       |

|-------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| APU   | High-level OS support such as Linux                                       | • HMI/UX                                                                                                         |

|       | Hypervisor-based computing                                                | Business logic                                                                                                   |

|       | Symmetric Multi-Processing and Supervised     Asymmetric Multi-Processing | Network/Cloud interaction                                                                                        |

| RPU   | Deterministic Operation                                                   | Deterministic response time                                                                                      |

|       | Low-Latency Memory Accesses                                               | software                                                                                                         |

|       |                                                                           | <ul> <li>Safety-critical software</li> </ul>                                                                     |

|       |                                                                           | • Standards-compliant software stack (ex: radio)                                                                 |

| PL    | Accelerating Applications                                                 | Acceleration / Parallelization                                                                                   |

|       |                                                                           | <ul> <li>Hardware-assisted effects,<br/>transformations, filtering,<br/>processing, encoding/decoding</li> </ul> |

| GPU   | • 2D and 3D Graphics Acceleration under Linux                             | • Display                                                                                                        |

|       |                                                                           | Multimedia                                                                                                       |

Т

These are general guidelines and your design might call for a different approach. Another way to help you decide on where to locate a certain processing load is to follow this decision tree:

Figure 2-2: Processing Location Decision Tree

The answers to the questions in the above diagram for each of your system's components should be fairly straight forward. If you have continuous data streams or requests that need to be constantly processed within certain time limits, chances are the programmable logic (PL) is the best location to put the majority of your system's components involved in processing those data streams or requests. If a workload doesn't fit that description but still needs to respond deterministically (i.e. in real-time) to external events or if it's mission critical then the RPU is probably a very good candidate. If it still doesn't fit that description then it's probably a general-purpose computing problem that should either be taken care of by the graphics processing unit (GPU) in case of graphics or the APU for everything else.

Still, even if on a first pass you determine that certain pieces of software should be handled by the RPU or the APU, there might be further optimization opportunities for moving those to the PL. If, for instance, the functionality to be achieved can be described as a fixed list of mathematical equations, such as an FFT, and/or a known set of states or state machines, especially if they can be run in parallel, it's probably a good candidate for embedding as part of the PL.

One way to gauge whether moving certain functionality into the PL is beneficial is obviously manual testing and prototyping. Xilinx, however, provides you with an even more effective way of identifying and handling optimization candidates for the PL. Indeed, the SDSoC<sup>™</sup> and Xilinx® SDK development tools can profile your application code and, in the case of SDSoC, enable you to offload code sections to the PL for performance testing at the click of a button. SDSoC will automatically compile the necessary logic into the PL, assign the

necessary data movers and software drivers to enable the rest of your APU- or RPU-bound software to transparently use the accelerated software portions. SDSoC therefore helps streamline the software acceleration process by greatly simplifying all steps involved. The use of SDSoC vs. manual offloading is therefore a trade off between ease of implementation and hand-crafted performance tuning.

An additional aspect to keep in mind is the top clock speeds of the processing blocks:

- APU Up to 1.5 GHz

- RPU Up to 600 MHz

- GPU Up to 667 MHz

**Note:** Keep in mind that those are *top* speeds. While each block can run at a maximum at those speeds, it's very unlikely to be running at those speeds all the time nor will it necessarily make sense for your design.

With its ARM® Cortex®-A53 processors, the APU is the fastest general purpose computing resource on the Zynq UltraScale+ MPSoC device. At first glance it might therefore seem to be the best candidate for workloads requiring maximum computing power, especially since you can have up to four Cortex-A53 processors on the Zynq UltraScale+ MPSoC device. Maximum frequency however does not necessarily mean best fit for function. The APU's Cortex-A53 processors, for instance, are not as well suited to real-time workloads as the RPU's ARM® Cortex®-R5 processor. Among many other factors, there's therefore a trade off between performance and determinism in choosing between the APU and the RPU.

Once the most likely candidate blocks for housing a given functionality have been identified, you still need to identify the best way to move data between blocks through the interconnect and how each processing location interacts with the various processing resources internal to the system as well as interfaces and resources within the outside world. The interconnect and interrupt processing are discussed in detail later in this chapter. For all aspects related to peripheral I/O, refer to Chapter 10, Peripherals. For information regarding the Memory, refer to Chapter 6, Memory. For more information regarding the PL's capabilities, including its built-in accelerators, refer to Chapter 5, Programmable Logic.

Note that while the present guidelines might prescribe a given recommended processing block, it's entirely possible that after reviewing the entire set of content related to a given part of your design that an alternate, better-suited configuration might become evident to best fit your specific product needs. The decision tree presented earlier, for example, recommended using the RPU for your real-time software. Your design might, instead, call for running a real-time operating system (RTOS) on the APU with the Cortex-R5 processors being run bare-metal. Another example is network communications. The above recommendations categorize network communication as being best slated for the APU. Yet, the PL contains integrated blocks for 100G Ethernet and PCIe which, together, can be used to efficiently accomplish network-related tasks that would typically be designated for the APU. The Xilinx White Paper Unleash the Unparalleled Power and Flexibility of Zynq UltraScale+ MPSoCs (WP470) [Ref 10] describes the flexibility of the Zynq UltraScale+ MPSoC outlines such an example use-case for a data center application. It also covers two

more example uses-cases, namely a central Advanced Driver Assistance System (ADAS) module and software-defined radio (SDR), which are likely to help you get a better understanding of how to partition your design's processing.

Yet another important aspect to keep in mind when determining where to conduct any given part of your design's processing is power management. The architecture of the Zynq UltraScale+ MPSoC device allows fine-grained control over power management. The power domains illustrated in Figure 2-1, page 14 are part of this power management as is detailed in Chapter 4, Power Considerations. Whenever you decide to run a given workload on a given Zynq UltraScale+ MPSoC device block, keep in mind how this choice relates to your power management needs. If, for example, a key algorithm runs on the APU and yet you would like to have the APU be powered down during certain periods of time then you might want to move that algorithm to either the PL or the RPU. The APU might be the most powerful block in the system, as was explained earlier, but it also happens to be the one that can consume the most power.

# **Heterogeneous Computing Concepts**

Understanding the processing capabilities of the Zynq UltraScale+ MPSoC device and the surrounding functionality calls on several key concepts not typically used outside the field of heterogeneous computing. This is therefore a quick introduction to some terminology you will find being used throughout this guide and the rest of the Zynq UltraScale+ MPSoC device documentation.

The Zynq UltraScale+ MPSoC device includes two main layers of multi-processing components (i.e. processors working in parallel to each other.) At the first layer, there are the main processing blocks:

- APU

- RPU

- PL

- GPU

At the second layer, there are the processing units within those blocks:

- Dual or Quad Cortex-A53 cores within the APU

- Dual Cortex-R5 processor cores within the RPU

- PL-optimized applications and/or MicroBlaze<sup>™</sup> processor instances within the PL

- Graphics processing pipelines in the GPU

The relationship between the main components of the Zynq UltraScale+ MPSoC device is generally considered "asymmetrical." That is, each of the APU, RPU, PL, and GPU have

different capabilities and constraints, they do not necessarily share a common OS, nor can a workload be seamlessly moved between those blocks. Instead, designers who want to use one of these components for a certain workload must tailor that workload specifically for that component. This is what is called Asymmetric Multi-Processing (AMP).

Within the APU, the relationship between the Cortex-A53 processors can take four different forms.

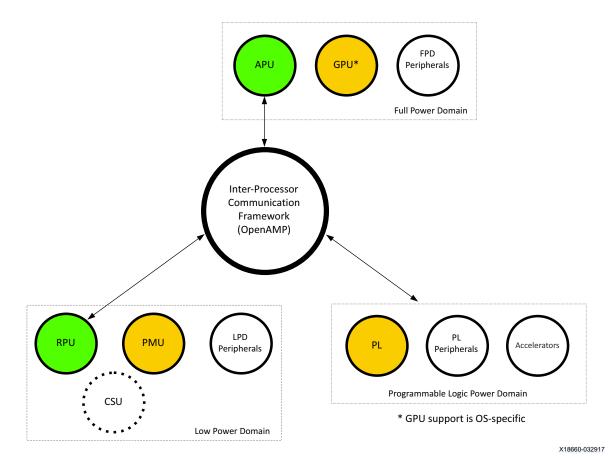

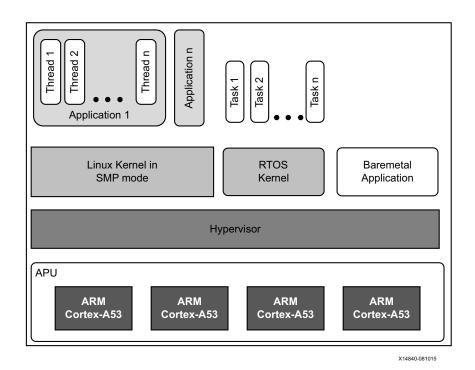

- If all the Cortex-A53 processor cores are used to run a single common OS such as Linux, which is another recommended configuration, then they are said to have a "symmetrical" relationship to one another. In this case, the common OS, Linux, can dispatch and move workloads -- effectively OS processes -- between processors transparently. From a software development point of view the OS API boundaries guarantee that the software will operate just the same no matter which Cortex-A53 processor it runs on. This type of operation is known as Symmetric Multi-Processing (SMP).

- If the Cortex-A53 processors are still operated independently, but a hypervisor such as the open source Xen or various commercial offerings is used to coordinate their combined operation, they would be considered as having a "supervised" asymmetrical relationship to each other. That is, the hypervisor acts as a supervisor between the Cortex-A53 processors and ensures there is a commonly-agreed upon arbitrator between the independent software stacks running in parallel on the Cortex-A53 processors. Supervised AMP mode for the APU is one of the recommended configurations in Chapter 3, System Software Considerations for certain types of applications.

- The APU hardware should also permit a hybrid configuration. A hypervisor can be used to segment the Cortex-A53 processors in supervised AMP mode while a subset of those cores can be managed collectively by a single OS image in SMP mode. This however is an advanced configuration that is neither provided nor supported by Xilinx.

- If the Cortex-A53 processors are operated independently, each running different system software without a common OS or hypervisor between them, they too would be considered as having an asymmetrical relationship to one another. More specifically, they would be said to be running in "unsupervised" AMP mode, indicating that there is no single software coordinating the operation of the Cortex-A53 processors. Note, however, that due to the complexities of a supervised AMP configuration on the Cortex-A53 processors, this is neither a recommended nor a Xilinx-supported configuration for the APU, as is explained in Chapter 3, System Software Considerations.

Finally, the APU hardware should also permit a hybrid configuration. A hypervisor can be used to segment the Cortex-A53 processors in supervised AMP mode while a subset of those cores can be managed collectively by a single OS image in SMP mode. This however is an advanced configuration that is neither provided nor supported by Xilinx.

Overall, because the Zynq UltraScale+ MPSoC device combines many different types of processors and processor cores in a single device, it is referred to as providing "heterogeneous" computing. Being such a type of device, the Zynq UltraScale+ MPSoC device enables the many processors and processor sets to relate to the other blocks or processors within the same block in the various ways just described.

The following is a quick recap of the previous explanation:

- SMP: When processing cores within the APU are managed by a single OS

- AMP: When processing blocks operate independently of one another

- Supervised: When there's a hypervisor coordinating AMP blocks

- Unsupervised: When there isn't a single arbiter between AMP blocks

- Heterogeneous computing: combining different processor types in the same device

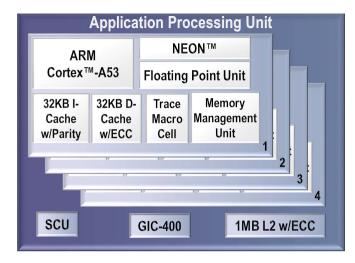

# **Application Processing Unit (APU)**

The APU on the Zynq UltraScale+ MPSoC device includes Dual or Quad Cortex-A53 processors, depending on the specific Zynq UltraScale+ MPSoC device model you are using.

#### Figure 2-3: Application Processing Unit (APU) Block Diagram

Each of the Cortex-A53 processor cores provides, among many other features:

- ARMv8-A architecture support

- 64 or 32 bit operation

- Up to 1.5GHz performance

- Independent Memory Management Unit (MMU)

- Dedicated L1 cache

- Individual power gating

- ARM TrustZone support

- VFPv4 FPU Implementation

- NEON and Crypto API support

**Note:** Refer to the Zynq UltraScale+ MPSoC device datasheet and *Zynq UltraScale*+ MPSoC Technical Reference Manual (UG1085) [Ref 7] for the full list of features.

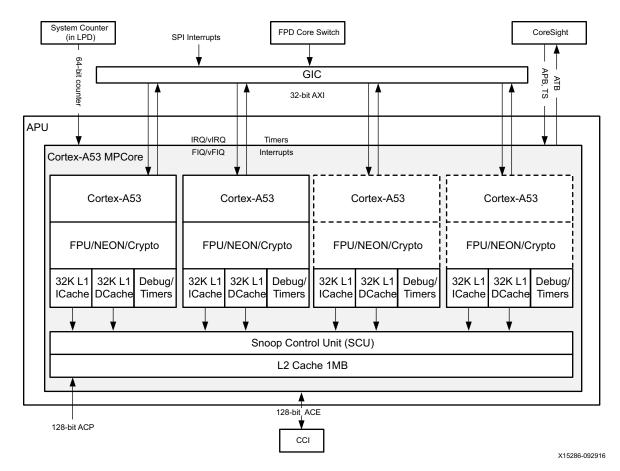

The Cortex-A53 processors therefore provide the same high-end general-purpose computing capabilities required to run high-end general purpose applications and OSes as other computing platforms as discussed in Chapter 3, System Software Considerations. Note that while the Cortex-A53 processors are mostly independent, some of the APU's resources, including its Global Interrupt Controller (GIC) covered below, must be managed coherently for all Cortex-A53 processors in order for the APU to operate correctly.

Here is a more detailed view of the APU:

Figure 2-4: Detailed APU Block Diagram

For more information regarding the software operation of the APU, refer to Chapter 3, System Software Considerations and Zynq UltraScale+ MPSoC: Software Developers Guide (UG1137) [Ref 5]. The rest of this section will focus on the APU's processing capabilities.

### SMP on the APU

Xilinx provides an open source Linux that contains a kernel that is SMP aware and can be further configured to the developer's needs. The kernel configuration allows the developer to specify the number of CPU cores that can be used for the OS' SMP feature. Selecting a number below the amount of available cores, and deploying with an underlying hypervisor will keep one or more cores free for other applications such as custom bare-metal applications created through the Xilinx SDK.

### **Unsupervised AMP on the APU**

Unsupervised AMP on the APU implies handing control over to the first processor, which in turn boots specific OS and runs workloads on other processors. In this working mode, resource sharing is left for the developer to implement. As was mentioned earlier, due to subtle complexities of implementation, this is neither a Xilinx recommended nor supported use case of the Zynq UltraScale+ MPSoC device.

### Supervised AMP on the APU

A hypervisor can be used on the APU for deploying different OSes or bare-metal workloads on the available cores. Depending on the hypervisor itself and specific customer needs, it can typically be used to manage resource sharing in a way that is either transparent (full virtualization) or semi-transparent (paravirtualization) to the guests it runs. Virtualization support is the subject of the next section.

### 64 or 32 Bit Operations

The Cortex-A53 processor is compatible with the ARMv8 specification which means it has the capacity to operate in 64 bit (AArch64) and 32 bit (AArch32) execution modes. The limitations of each mode are the same as those inherent the ARM architecture. The AArch32 execution mode on the Zynq® UltraScale+<sup>™</sup> MPSoC is compatible with the Zynq 7000 device family and the ARMv7 specification, and has been extended to support some of ARMv8 features like SIMD and the cryptographic extension. The choice of using either execution mode generally depends on the software meant to run on the device.

In hypervisor mode, the choice of whether to use AArch32 and AArch64 is dictated by what execution state is used by the hypervisor.

- A 64 bit hypervisor can run an operating system kernel running in AArch64 or AArch32 mode. Note that an OS kernel running as AArch32 can only run applications in AArch32 execution mode, even if said kernel is running within a hypervisor in AArch64 mode.

- A 32 bit hypervisor is limited to AArch32 OSes and applications.

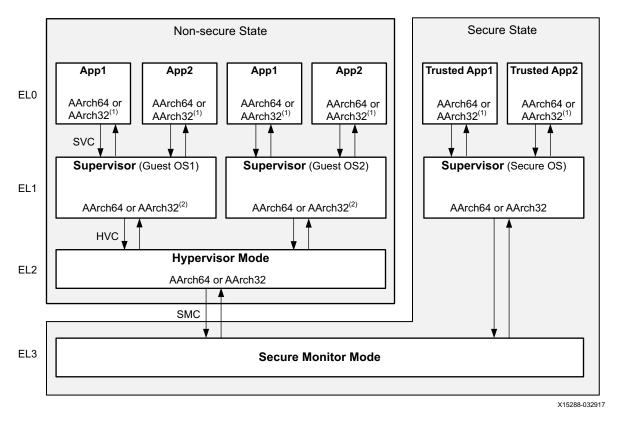

# **APU Virtualization Support**

The Zynq UltraScale+ MPSoC device supports hardware virtualization through 4 key components. Several are already being used by system software designed for the Zynq UltraScale+ MPSoC device, such as the Xen hypervisor. Understanding those capabilities will enable you to more effectively design your system around the Zynq UltraScale+ MPSoC device.

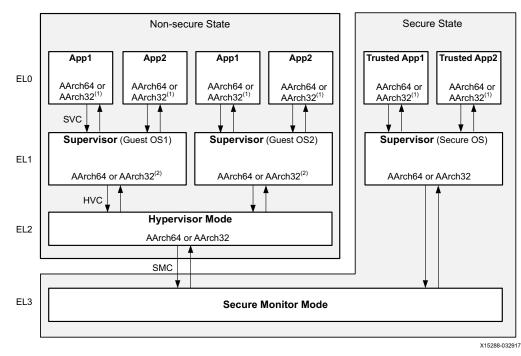

### **Cortex-A53 Processor Virtualization**

Support for virtualization on the APU is typically implemented through one of the Exception Levels (ELs) defined in the ARMv8 architecture specification of the Cortex-A53 processor. There are 4 ELs supported by ARMv8 and EL2 can be used by supported hypervisors to isolate the hypervisor context from the guest OSes. The Cortex-A53 processor's ELs are discussed in detail as part of the ARM TrustZone section in Chapter 7, Resource Isolation and Partitioning.

Figure 2-5: TrustZone's Exception Levels

### **Interrupt Virtualization**

Interrupt virtualization is discussed in APU Interrupt Virtualization, page 39.

## System MMU for I/O Virtualization

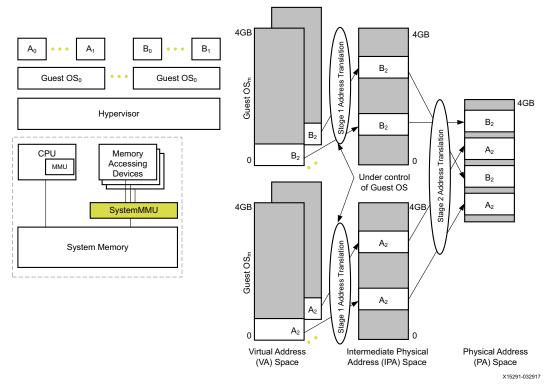

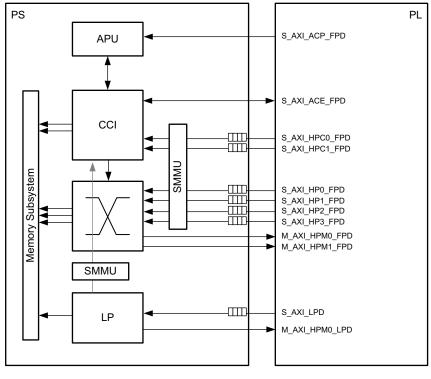

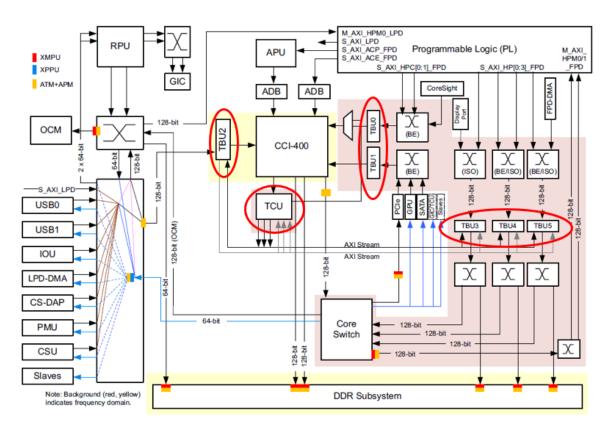

The System MMU (SMMU) simplifies the virtualization of addresses for I/O and hypervisor use by automating address translation based on software-managed tables. The following figure illustrates one example of the SMMU's virtualization of addresses:

Figure 2-6: Example Use of the SMMU

The SMMU can operate in two stages, as illustrated above as "S1," "S2," or "S1/S2:"

• Stage 1:

This stage operates like a traditional single-stage CPU MMU. It takes Virtual Addresses (VAs) and translates them to Intermediate Physical Addresses (IPAs).

• Stage 2:

In a hypervisor environment, this stage simplifies the hypervisor's design by enabling guest OSes to directly configure DMA capable devices in the system without having to interface with the hypervisor for those requests. In this stage, it takes IPAs and converts to Physical Addresses (PAs).

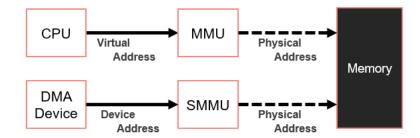

The following figure illustrates the SMMU's virtualization of addresses in a hypervisor environment:

Figure 2-7: SMMU Address Translation Stages

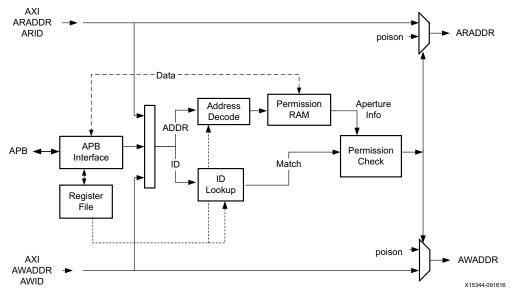

The SMMU has the following key components that interface with the Zynq UltraScale+ MPSoC device Interconnect described in the next section:

- Translation Buffer Unit (TBU): For translating addresses

- Translation Control Unit (TCU): For controlling and managing address translation

Chapter 7, Resource Isolation and Partitioning discusses this topic further.

### **Peripheral Virtualization**

In general, the SMMU can be used by the hypervisor to allow guests to exclusively own a DMA-capable device. In system designs that wish to share a single hardware device across multiple guest OSes, a technique called paravirtualization is used. This requires new device drivers for all OSes that want to share the device. The throughput of a shared device is accordingly less than an exclusively-owned device, as mapped by the SMMU.

## **Timer Virtualization**

The ARM processor includes generic hardware timers for various tasks. One timer calculates the global passing of time for the system. This generic timer is associated with a counter incremented at a rate which depends on the system setting or the CPU frequency. Each CPU core contains a physical counter which contains the system counter value. Each CPU core also has a virtual counter that indicates virtual time. This virtual counter is saved and paused when a virtual machine gets interrupted and the control returns to the hypervisor. Access to the counter values can be controlled by the OS depending on the execution levels.

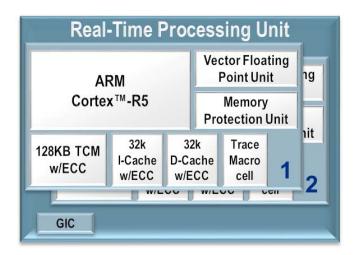

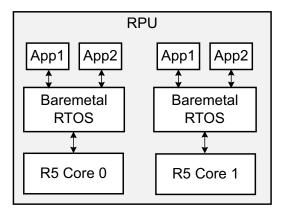

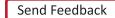

# **Real-Time Processing Unit (RPU)**

The Zynq® UltraScale+<sup>™</sup> MPSoC comes equipped with two Cortex-R5 processors which are typically used for operations requiring deterministic low-latency operations and response-time critical applications:

Each Cortex-R5 processor provides, among other features:

- ARMv7-R architecture support

- 32-bit operation

- Up to 600MHz performance

- Dedicated L1 cache

- 128KB of Tightly-Coupled Memory (TCM) with error-correcting code (ECC)

- Single and double-precision FPU

Note that like the case of the APU, while the Cortex-R5 processors can be operated independently, some of the resources of the RPU, including the Global Interrupt Controller discussed further below, must be managed coherently for both Cortex-R5 processors in order for the RPU to operate correctly.

The Cortex-R5 processors can be set to operate in two different modes depending on your needs:

• Split Mode / Unsupervised AMP:

Also known as the Performance Mode, this is the default mode of the Cortex-R5 processors. In this mode, each core operates independently, except for the interrupt controller as was just explained. In split mode, one core may be running an RTOS while another could be running bare-metal, or both could be running different RTOSes. Unlike the APU, all such configurations in this mode would be considered as unsupervised AMP as the Cortex-R5 processor cannot support a hypervisor. Communication between the Cortex-R5 processors could be done by simply passing interrupts and sharing memory with Xilinx bare-metal libraries or enabling a range of advanced features by means of advanced features available in OpenAMP framework. Refer to the *Zynq UltraScale*+*MPSoC OpenAMP: Getting Started Guide* (UG1186) [Ref 8] for more information.

• Lock-Step Mode:

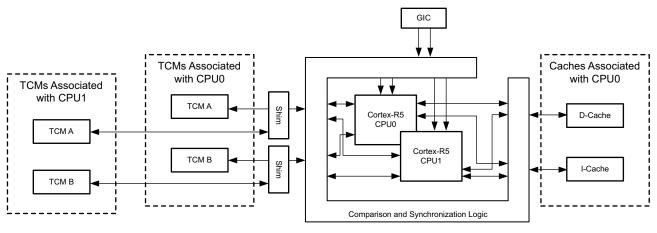

Also known as the Safety Mode, in this mode of operation the Cortex-R5 processors acts as a single CPU with regards to the rest of the system. Internally, however, the cores are processing the same instruction in parallel; delayed by 1 ½ clock cycles to allow detection of single event upsets. Should output from the two cores differ, the comparison and synchronization logic would detect and signal the error for a subsequent, custom response. For example tampering could cause the lock-step cores to get out of sync and, in response to this, you could decide to shut down or lock out the system. The following diagram illustrates the operation of the RPU in this mode:

X15295-092916

Figure 2-9: Lock-Step of the Cortex-R5 Processors

If your application is mission critical or if you require functional safety with detection of single event upsets, then lock-step mode is likely preferable. If, on the other hand, you would like to benefit from the full performance made possibly by having two Cortex-R5 processors available for your application, the default split mode is best.

As is explained in Chapter 4, Power Considerations, the Cortex-R5 processor are part of what is known as a "power island" and can be gated together. They cannot, however, be power gated individually.

The RPU is discussed in more detail in the Real-Time chapter.

# Interconnect

The Zynq UltraScale+ MPSoC device's Interconnect is at the heart of its heterogeneous architecture. It links together all of the processing blocks together and enables them to interface with the outside world through access peripherals, devices and memory. It's therefore fundamental to understand its functionality in order to best tune your system.

The Zynq UltraScale+ MPSoC device's interconnect is based on ARM's Advanced eXtensible Interface (AXI) defined as part of ARM's Advanced Microcontroller Bus Architecture (AMBA) 4.0 specification, and incorporates many other related ARM technologies such as Cache Coherent Interconnect (CCI-400) and CoreLink NIC-400 Network Interconnect. ARM describes those technologies in great detail in the corresponding specifications and documentation it makes available. For the purposes of the present discussion, however, a brief introduction to the relevant core concepts will prove helpful in determining how to tweak the Zynq UltraScale+ MPSoC device's interconnect to your needs.

## **AXI Interfaces**

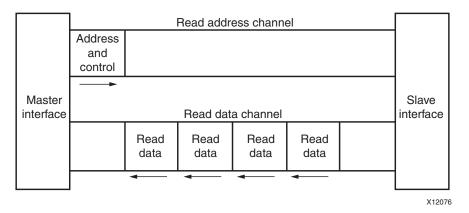

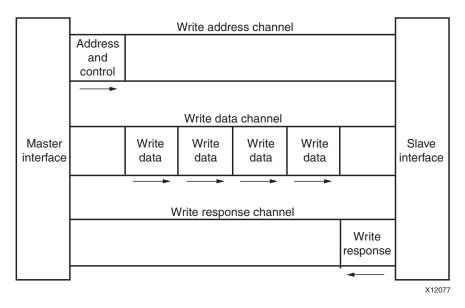

The primary mechanism for linking any pair of blocks within the Zynq UltraScale+ MPSoC device is an AXI interface. At its most basic level, an AXI interface is specified as linking an AXI Master to one or more AXI Slaves. The master issues the requests that the slave(s) needs to fulfill. Each AXI interface consists of five different channels:

- Read Address Channel

- Write Address Channel

- Read Data Channel

- Write Data Channel

- Write Response Channel

The following figures summarize the interaction between master and slave.

Figure 2-10: AXI Master and Slave Interaction, Read Channels

Figure 2-11: AXI Master and Slave Interaction, Write Channels

Each Zynq UltraScale+ MPSoC device block can contain many interface masters and slaves. Given the number of components in the Zynq UltraScale+ MPSoC device and the complex relationships between them, masters and slaves are rarely connected directly. Instead, several switches are located at strategic points in the Zynq UltraScale+ MPSoC device to enable the various blocks to connect to one another while keeping with the Zynq UltraScale+ MPSoC device's emphasis on power management, security, isolation, and overall flexibility.

### **Traffic Priority and Coherency**

There is significant parallel traffic occurring at any point in time in the Zynq UltraScale+ MPSoC device. Different processing blocks and resources have however different priorities while still many parties on the interconnect are accessing the memory simultaneously. There must therefore be a way to prioritize traffic and, at the same time, preserve the coherency of traffic going to the memory.

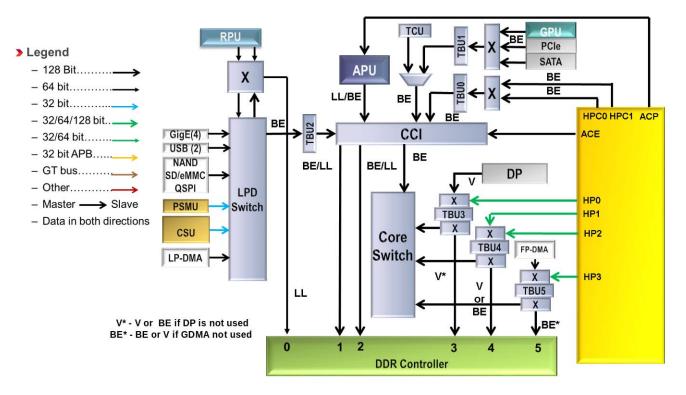

With regards to traffic, not all of it coming in and out of the interconnect switches is given the same level of priority. Instead, AXI traffic within the Zynq UltraScale+ MPSoC device's interconnect falls under one of three categories:

• Low Latency (High Priority)

This type of traffic generally needs to be prioritized over other types of traffic. Such is the case for traffic between the APU and RPU, and the memory.

• High Throughput (Best Effort)

This type of traffic can tolerate higher latencies, but must have very high throughput. Such is the case of GPU and the PL.

• Isochronous (Video class)

This type of traffic is mostly tolerant of long latencies, except at some critical moments. Such is the case of video/image data in general. When timeouts are about to expire, this class of traffic is given the highest priority.

The following diagram provides a simplified view of the Zynq UltraScale+ MPSoC device's interconnect along with the traffic classes:

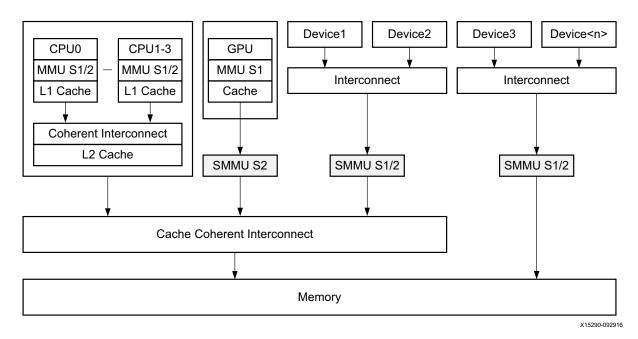

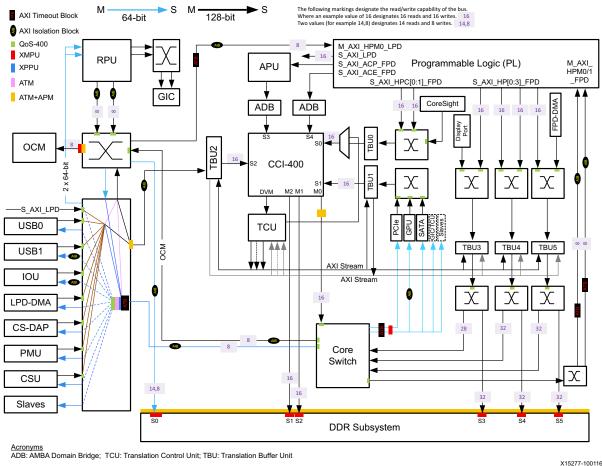

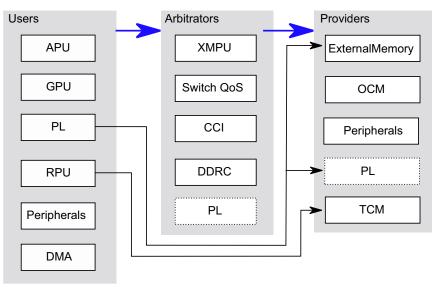

*Figure 2-12:* Simplified View of Interconnect with Traffic Classes

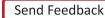

The default traffic classes are illustrated as "LL" for Low Latency, "BE" for Best Effort, and "V" for Video. Many of the blocks in this diagram have already been covered earlier in this chapter or have been introduced earlier in this section. Note that the TBU and TCU blocks are part of the SMMU discussed in the previous section. This diagram therefore also shows the tight relationship between the SMMU and the interconnect.

Apart from the switches, the other key component of the Zynq UltraScale+ MPSoC device's interconnect is the Cache-Coherent Interconnect (CCI) which ensures that memory transactions are coherent no matter which parts of the Zynq UltraScale+ MPSoC device are involved.

The following diagram highlights the CCI's role:

Figure 2-13: Role of the CCI

### **Detailed View**

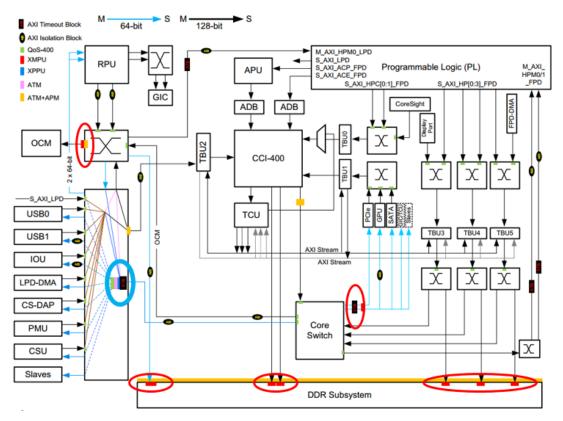

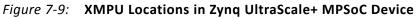

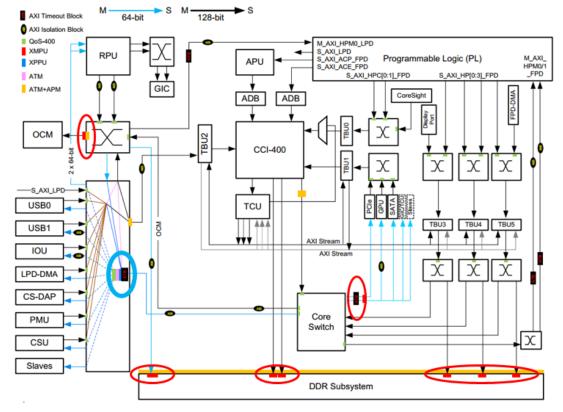

In addition to the components presented earlier in this section, the Zynq UltraScale+ MPSoC device's interconnect also contains a few additional submodules worth knowing about:

• AXI Timeout Blocks:

Prevents masters from hanging due to unresponsive slaves

• AXI Isolation Blocks (AIBs):

Manages power-down transitions across system blocks

• XMPU/XPPU:

Enforces isolation between master and slave blocks -- discussed in Chapter 7, Resource Isolation and Partitioning.

• AXI Trace Macrocell (ATMs):

Retrieves AXI traces for CoreSight using the Advanced Trace Bus (ATB)

• AXI Performance Monitor (APMs):

Captures AXI performance metrics

The following diagram captures the detailed view of the Zyng UltraScale+ MPSoC device's interconnect based on the previous explanations:

X15277-100116

#### Figure 2-14: Detailed View of the Zynq UltraScale+ MPSoC Device Interconnect

### Quality of Service (QoS)

Another very important aspect of the interconnect that is illustrated in the previous diagram is Quality of Service (QoS). There are two parts of the system participating in QoS, the interconnect switches and the CCI.

#### Switch-based QoS

If you look closely at the diagram, you will notice that most switches include QoS-400 capabilities. QoS-400 is an ARM addition to the CoreLink NIC-400 standard mentioned earlier that is used by the Zyng UltraScale+ MPSoC device for its switch interconnect. A QoS-400 regulator is assigned to most AXI masters in the interconnect.

**Note:** A QoS-400 "regulator" is the term used in ARM documentation to describe the blocks associated with AXI masters to control their behavior.

This regulator allows limiting the following for each AXI master:

- Maximum number of outstanding transactions possible at any one time

- Command issue rate

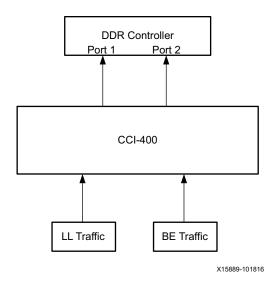

### CCI-based QoS

The CCI-400 used in the Zynq UltraScale+ MPSoC device has a QoS Virtual Network (QVN) feature that is used to avoid the head-of-line blocking (HOLB) effect from occurring during memory accesses from requests generated by two different traffic priority classes. The following figure illustrates this scenario:

*Figure 2-15:* **CCI-based QoS**

In this case, one traffic going through the CCI is tagged as Low-Latency while the other is tagged as Best Effort. HOLB would occur if the lower priority traffic, namely Best Effort, would "hold the line" (i.e. a DDR port) from the higher priority traffic, namely Low Latency. The QVN uses different queues and tokens to arbitrate the traffic between the two DDR ports and avoid the delay caused by HOLB.

This is helpful in the case of the APU as it isn't confined to using a single preassigned DDR port and is instead switching constantly between the two DDR ports attached to the CCI-400 to which the APU is itself attached; see the diagram from the previous section.

Since the APU's traffic is generally Low-Latency and most other traffic sharing the CCI with it is Best Effort, the use of QVN as just explained ensures the APU gets the appropriate QoS for its memory accesses.

### **Customizing QoS**

In the vast majority of cases there is no need to modify the QoS setup used by default in the Zynq UltraScale+ MPSoC device. However, if you are having issues and would like to possibly tweak some of the QoS-400 regulators, for instance, start by using the built-in data collection capabilities made possible by the APMs and ATMs mentioned earlier. *Xilinx Software Development Kit (SDK) User Guide: System Performance Analysis* (UG1145) [Ref 11] helps you use the performance monitoring capabilities of the freely-available Xilinx Software Development Kit (SDK) to model traffic and retrieve live runtime information from the Zynq UltraScale+ MPSoC device. You can also do the same with the SDSoC Development Environment. This is a unique feature of Xilinx enabling you not just to retrieve information from the APU but from the rest of the interconnect connecting all the Zynq UltraScale+ MPSoC device's internal blocks.

With the data from these tools, and review of the full interconnect diagram shown earlier, you can identify hot paths in your system and adjust its configuration as necessary. This is typically done by identifying which traffic from which AXI masters is being negatively impacted by traffic from lower priority masters. You can then throttle the less important AXI masters by tweaking their corresponding QoS-400 regulators. If the traffic from the APU and the RPU is less important than that of the PL, for example, you can configure the APU's and RPU's regulators to favor traffic from the PL instead. To effectively pull this off, however, you must make sure that you have a solid understanding of the traffic flow within the Zynq UltraScale+ MPSoC device.

Only pursue this if the default settings don't work for your design.

### **PL Interfaces**

One aspect of the Zynq UltraScale+ MPSoC device interconnect that is under the designer's full control are the connections between the PL and the rest of the system. As can be seen in the main interconnect diagram presented earlier and as will be discussed in Chapter 5, Programmable Logic, there are several paths from the PL to the interconnect and therefore the rest of the system. The explanations found in Chapter 5 build on the explanations provided earlier in this section.

### **Additional Information**

For additional information regarding the interconnect, refer to the corresponding chapter in *Zynq UltraScale+ MPSoC Technical Reference Manual* (UG1085) [Ref 7], as well as the official ARM documentation regarding:

- AMBA 4.0-the core AXI standard

- NIC-400-the switch interconnect

- CCI-400-the cache coherent interconnect

- QoS-400-the QoS addition to NIC-400

### Interrupts

With its highly integrated, heterogeneous design the Zynq UltraScale+ MPSoC device comprises a large number of interrupt sources and several ways of handling them. Most of the integrated peripherals, for instance, trigger interrupts to notify processors of important events; this includes Ethernet, USB, GPU, DisplayPort, DMA, UART, SPI, SD, etc. The PL can also trigger 16 different interrupts.

Additionally, the Zynq UltraScale+ MPSoC device includes configurable Inter-Processor Interrupts (IPIs) that can be used to enable the independent processing blocks to communicate with each other.

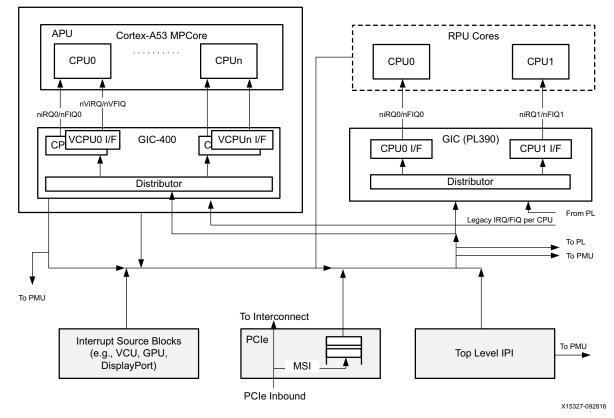

There are two interrupt controllers in on the Zynq UltraScale+ MPSoC device, one for the APU and one for the RPU. The APU's interrupt controller implements the ARM Global Interrupt Controller version 2 (GICv2) specification while the RPU's interrupt controller is based on the ARM GICv1 specification. A key benefit of the former is enabling interrupt virtualization on the APU.

The following diagram illustrates the Zynq UltraScale+ MPSoC device's interrupt routing:

Figure 2-16: Zynq UltraScale+ MPSoC Device Interrupt Routing

The block marked GIC-400 is the APU's GICv2 interrupt controller while the block marked GIC (PL390) is the RPU's GICv1 interrupt controller.

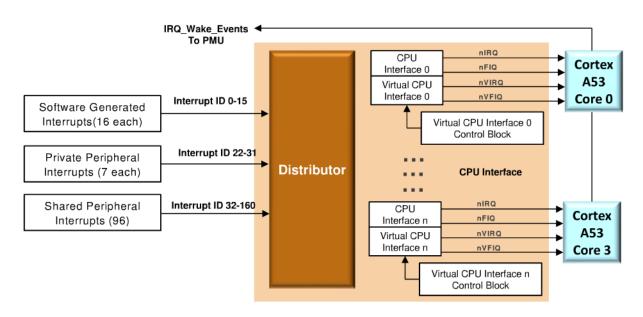

### **APU Interrupt Controller**

Each Cortex-A53 processor has four interrupt lines as input:

- nIRQ are normal priority interrupts

- nFIQ are high-priority or Fast Interrupts

- nVIRQ are normal priority virtual interrupts, for virtualization support on the APU

- nVFIQ are high priority virtual interrupts, for virtualization support on the APU

The APU's interrupt controller handling of the Cortex-A53 processors' interrupts is illustrated in the following figure:

The interrupt controller is separated into 2 parts. The distributor is responsible for registering the inbound interrupts and prioritizing them before distributing them to the right target CPU. The second part of the interrupt controller interfaces with each CPU's interrupt lines to trigger the actual interrupt on the relevant Cortex-A53 processor.

The interrupt controller handles 3 types of interrupts:

- 16 Software Generated Interrupts (SGI) for sending interrupts between cores

- 7 Private Peripherals Interrupt (PPI) are targeted to a single Cortex CPU core

- 92 Shared Peripherals interrupts (SPI) shared between all APU and RPU cores

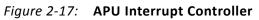

#### **APU Interrupt Virtualization**

When an interrupt is received while the APU is running a hypervisor, the hypervisor will interface with the APU's interrupt controller to generate virtual interrupts for the guest OSes as illustrated below. Those interrupt will be delivered directly to the guest OS which will handle and clear them. The hypervisor can handle and clear interrupts locally if the interrupt isn't meant to reach guests.

Figure 2-18: APU Interrupt Virtualization

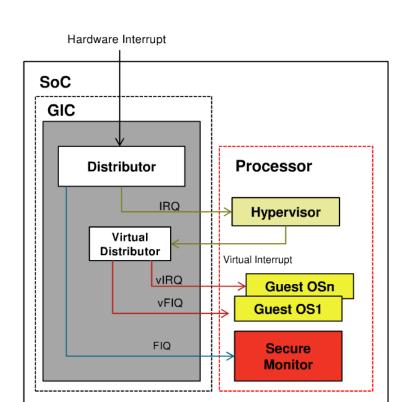

### **RPU Interrupt Controller**

The RPU's GICv1 interrupt is attached to the Cortex-R5 processors as shown below. It's similar to the APU's interrupt controller but doesn't support virtual interrupts. It also handles fewer interrupts for each of the previously-mentioned types (i.e. SGI, PPI, SPI).

Figure 2-19: RPU Interrupt Controller

### Secure State and Interrupts

As will be explained in Chapter 7, Resource Isolation and Partitioning, all of the Zynq UltraScale+ MPSoC device's blocks connected through the interconnect are categorized as either secure or non-secure, per the ARM TrustZone specification. While the details will be covered in Chapter 7, note that the interrupt controllers of both the APU or the RPU do not distinguish between the party triggering an interrupt as either being secure or non-secure. By convention, FIQs on the APU are sent to the secure monitor but this is a software choice, not a hardware requirement.

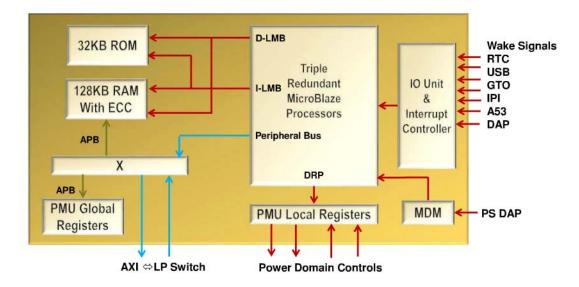

#### **Inter-Processor Interrupts**

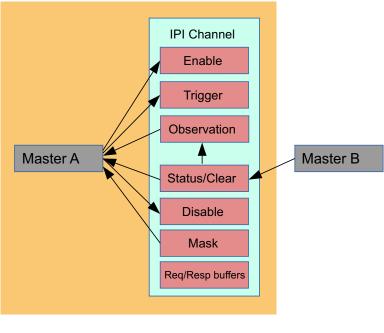

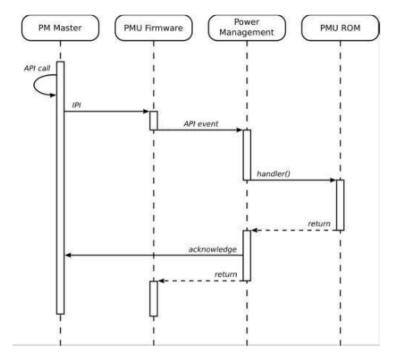

Inter-Processor Interrupts (IPIs) are the underpinning of communication between processing blocks in the Zynq UltraScale+ MPSoC device, providing a channel to interrupt a remote processor and carry and can carry a certain amount of payload. One of the main uses of IPI, for instance, is power management. If the full power domain is powered down, an IPI can be sent to the PMU to request that it be powered back on.

There are 11 IPI channels among which 4 are reserved for communication with the Platform Management Unit (PMU). Each IPI channel, except some reserved to communication with the PMU, have two 32 byte buffers and 6 registers that are used for communication between the source and target. The first buffer is used by the master to store the request and the second one is used by the target to store the response. The figure below illustrates how the registers are manipulated by the master to trigger an IPI and by the target to acknowledge and reply to the interrupt.

X18707-032117

Figure 2-20: Inter-Processor Interrupt Channel Registers

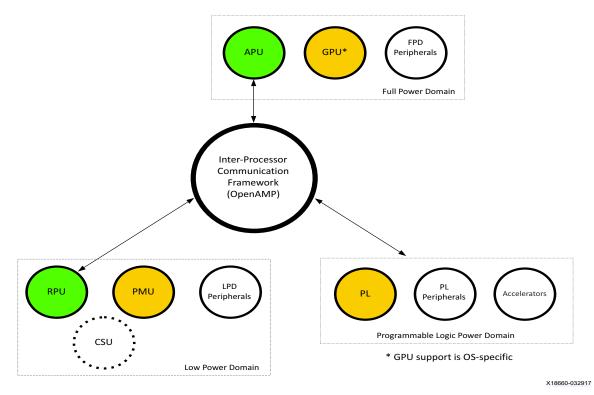

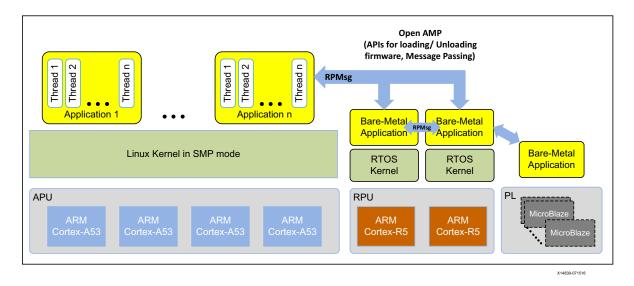

#### OpenAMP

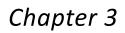

Using IPIs directly for cross-block communication within the Zynq UltraScale+ MPSoC device can be tedious. Xilinx therefore provides the OpenAMP framework, discussed in greater detail in Chapter 3, System Software Considerations, to facilitate the development of AMP systems in a heterogeneous environment. OpenAMP is built on IPIs and exposes two key components to allow CPU cores to communicate:

- Remoteproc: for starting and managing the life cycle of remote CPUs

- RPMsg: for communicating between remote CPUs.

Refer to Chapter 3, System Software Considerations for more information about OpenAMP and its usage.

## Workload Acceleration Using the PL

As mentioned in Processing System Methodology, page 14, the Zynq UltraScale+ MPSoC device's PL can be used to offload processing through hand coding, or by way of using either the Vivado® HLS or the Xilinx SDSoC development environments. This, therefore, enables system designers to easily move software to the PL for performance acceleration.

The process to offloading processing to the PL using SDSoC can be summarized as follows:

| Baseline Hardware Function                | Determine performance with compiler defaults                              |

|-------------------------------------------|---------------------------------------------------------------------------|

| 1: Optimization for Metrics               | Define loop trip counts                                                   |

| 2: Pipeline for Performance               | Pipeline and Dataflow                                                     |

| 3: Optimize Structures for<br>Performance | <ul> <li>Partition memories</li> <li>Remove false dependencies</li> </ul> |

| 4: Reduce Latency                         | Optionally specify latency requirements                                   |

| 5: Improve Area                           | Optionally recover resources through sharing                              |

Figure 2-21: PL Offloading Process Summary

SDSoC has several features which allow developers to analyze the performance of an application running on MPSoC hardware. It allows developers to identify repetitive segments of code by generating a complete report on the code. That report identifies if the code built in the environment can be improved by offloading to the PL and gives an estimation of how it would improve the performance of the system along with how much it would cost in terms of PL resources. The screen capture below is an example of the type of information the SDSoC environment can give.

| Performance estin         | nates for 'main' fu | nction          |               |  |

|---------------------------|---------------------|-----------------|---------------|--|

| SW-only (Measured cycles) |                     |                 | 2473554900    |  |

| HW accelerated (I         | Estimated cycles)   |                 | 1157553490    |  |

| Estimated speedup         |                     | 1               | 2.14          |  |

| etails                    |                     |                 |               |  |

| Performance estin         | nates for functions | s 'madd in main | .cpp:128      |  |

| SW-only (Measured cycles) |                     |                 | 1305300       |  |

| HW accelerated (          | Estimated cycles)   |                 | 20143         |  |

| Estimated speedup         |                     | 64.8            |               |  |

| Resource utilizatio       | n estimates for ha  | rdware accelera | ators         |  |

| Resource                  | Used                | Total           | % Utilization |  |

| DSP                       | 162                 | 220             | 73.64         |  |

| BRAM                      | 32                  | 140             | 22.86         |  |

| LUT                       | 23781               | 53200           | 44.7          |  |

|                           | 13773               | 106400          | 12.94         |  |

Figure 2-22: Example PL Acceleration Output by SDSoC

The C/C++ code can then be converted into a block placed inside the ZU's PL. This step is done using the Vivado HLS (for High-Level Synthesis) compiler.

After synthesis, a report about selection of the Data Movers by the synthesis environment is available to the developer. SDSoC automatically chooses your data movers and drivers, but these can be easily overridden by user control if desired. It is also possible to generate calling wrappers to allow applications running on the APU or the RPU to call into IP blocks generated in Verilog or VHDL in the PL section of the board. This technique skips the HLS compilation just described.

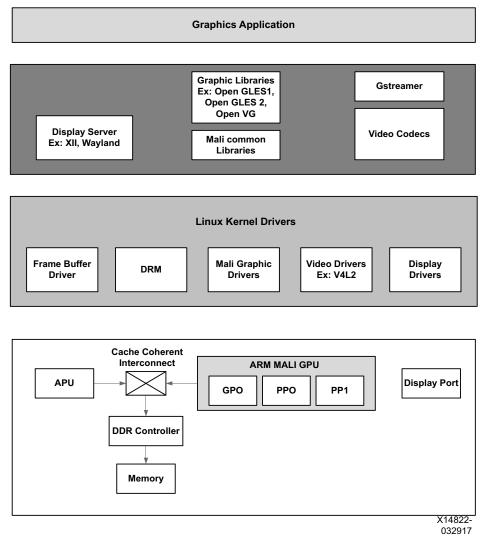

## **General-Purpose Computing Acceleration**

Aside from the targeted work of either manually or automatically offloading workloads to the PL covered in the previous section, there are several commonly-used techniques and technologies for accelerating general-purpose computing. These include the use of OpenCL libraries and general-purpose computing on graphics processing units that support GPGPU. The Zynq UltraScale+ MPSoC device's PL offloading capabilities just discussed offer a compelling computational acceleration path when compared to other industry techniques. The MALI-400 GPU used in the Zynq UltraScale+ MPSoC device is architectured exclusively for graphics acceleration and isn't suitable for GPGPU.

The following table shows independently-published results where optimization through FPGA beats the combination of a general-purpose GPU and CPU:

| Domain / Topic                                                       | Title / Author / DOI                                                                                                                                               | Improvement<br>over<br>CPU+GPGPU | Improvement<br>over CPU-Only |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------|

| Digital Signal Processing<br>Sliding Windows                         | A Performance and Energy Comparison of FPGAs, GPGPUs,<br>and Multicores for Sliding Window Applications, Fowers,<br>http://dx.doi.org/10.1145/2145694.2145704      | 11x                              | 57x                          |

| Graph Processing<br>Tree-reweighted Message<br>Passing (TRW-S)       | GraphGen for CoRAM: Graph Computation on FPGAs,<br>Weisz, http://dx.doi.org/10.1109/FCCM.2014.15                                                                   | 10.3x                            | 14.5x                        |

| Monte Carlo Simulation<br>Random Number<br>Generation                | A Comparison of CPUs, GPGPUs, FPGAs, and Massively<br>Parallel Processor Arrays for Random Number Generation,<br>Thomas, http://dx.doi.org/10.1145/1508128.1508139 | 3x                               | 30x                          |

| Machine Vision<br>Moving Average with Local<br>Difference (MALD)     | CPU, GPGPU and FPGA Implementations of MALD: Ceramic<br>Tile Surface Defects Detection Algorithm, Hocenski,<br>http://dx.doi.org/10.7305/automatika.2014.01.317    | 14x                              | 35x                          |

| Bioinformatics<br>De Novo Genome<br>Assembly                         | Hardware Accelerated Novel Optical <i>De Novo</i> Assembly for Large-Scale Genomes, Kastner,<br>http://dx.doi.org/10.1109/FPL.2014.6927499                         | 8.5x                             | 11.9x                        |

| Atmospheric Modelling<br>Solvers for Global<br>Atmospheric Equations | Accelerating Solvers for Global Atmospheric Equations through Mixed-Precision Data Flow Engine, Gan, http://dx.doi.org/10.1109/FPL.2013.6645508                    | 4x                               | 100X                         |

#### Figure 2-23: FPGA vs. CPU+GPGPU and CPU-Only Optimizations

Finally, the table below provides the general reasons why using the PL (i.e. FPGA) might give better results than using the GPGPU for acceleration:

|                   | GPGPU                                                              | FPGA                                                                |

|-------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|

| Program Execution | Runs SW                                                            | Direct hardware<br>implementation of<br>algorithms                  |

| Latency           | ms                                                                 | ns                                                                  |

| Performance       | Dependant on<br>memory,<br>communication<br>and<br>synchronization | deterministic                                                       |

| Concurrency       | Single kernel<br>(SIMD)                                            | Many kernels can<br>run in parallel                                 |

| Floating Point    | FP-only array of cores                                             | Configurable,<br>distributed DSP<br>(multiply-<br>accumulate) cores |

| Pipeline          | Kernel to memory                                                   | Kernel to I/O,<br>kernel to kernel,<br>kernel to memory             |

Figure 2-24: FPGA Acceleration Benefits Compared to GPGPU

In sum, if you are looking for accelerating software, we strongly encourage you to explore the PL's offloading capabilities. Apart from the SDSoC tool mentioned earlier, another tool you might want to consider is the Xilinx SDAccel<sup>™</sup> Development Environment. SDAccel is tailored for OpenCL, C and C++ acceleration on FPGA.

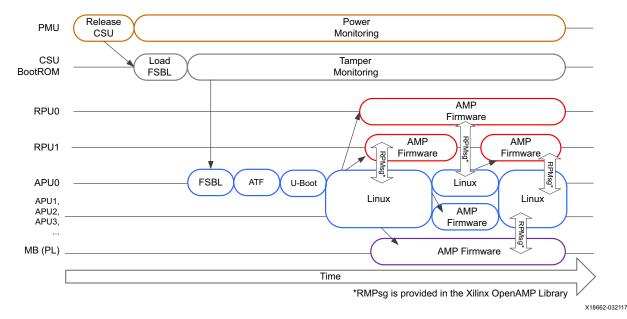

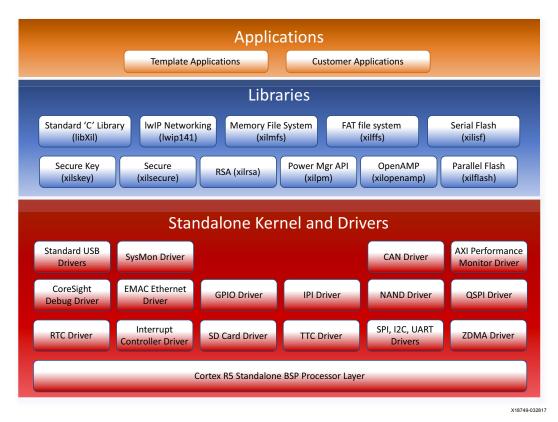

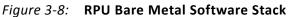

# System Software Considerations

Software across the Zynq® UltraScale+<sup>™</sup> MPSoC permeates virtually all areas of the device. Software can exist as Bare Metal applications, middleware, firmware, drivers, high level operating systems (HLOS), libraries, high level applications, graphics applications, communication protocols, and so forth. Depending on your specific Zynq US+ MPSoC application, the software components across the silicon can be included or excluded, enable specific hardware features, affect speed and efficiency of the device, and in general provide the overriding execution environment you desire. In short, your particular software footprint is the glue for your system.

### **Defining Your System Software Needs**

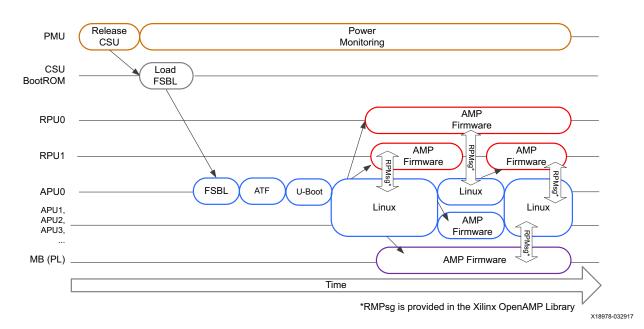

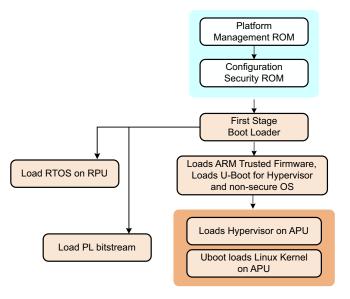

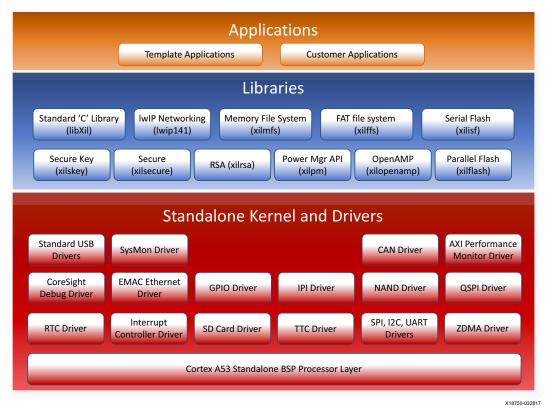

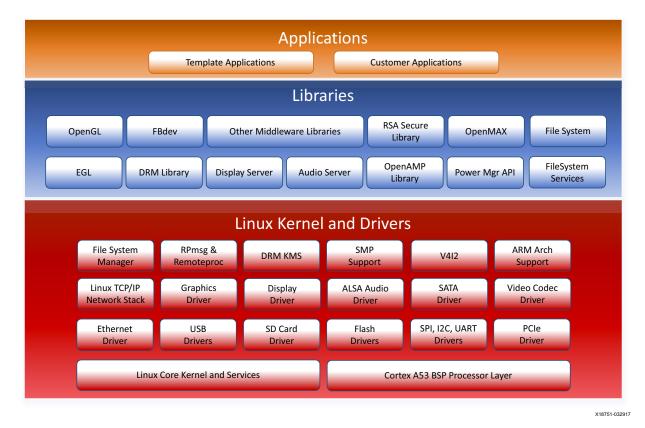

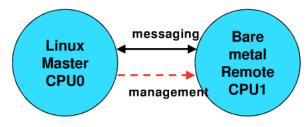

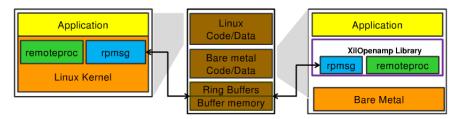

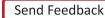

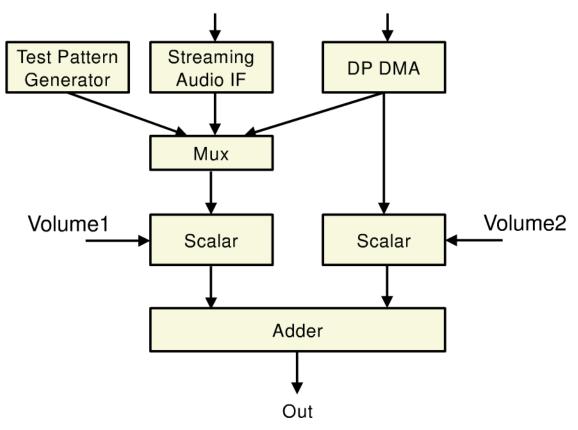

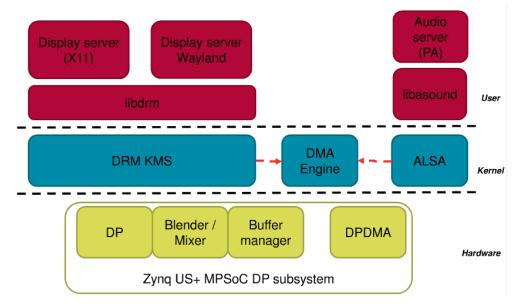

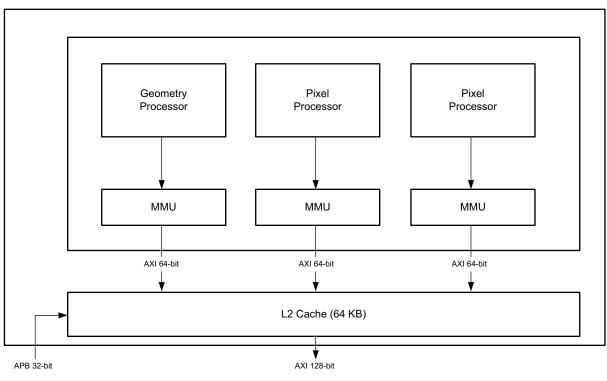

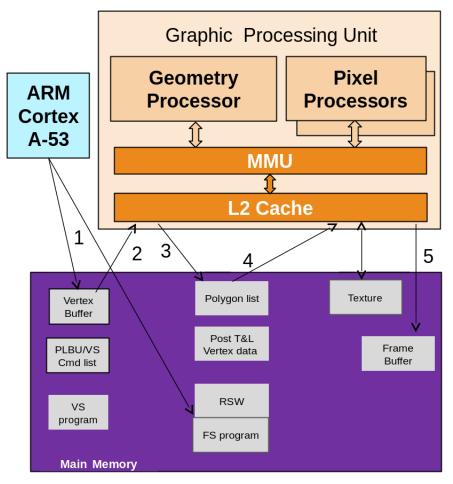

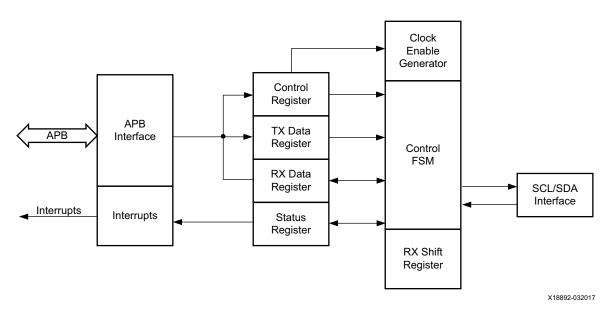

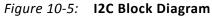

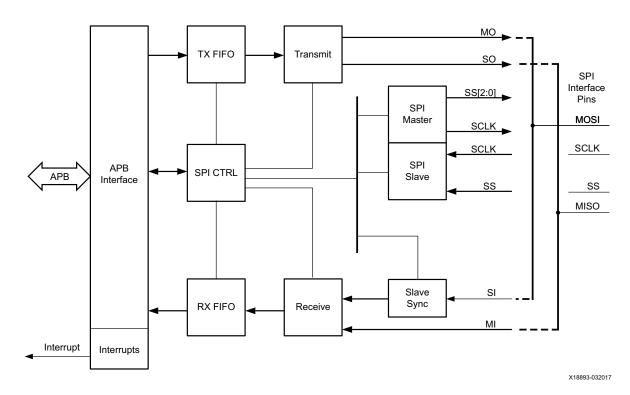

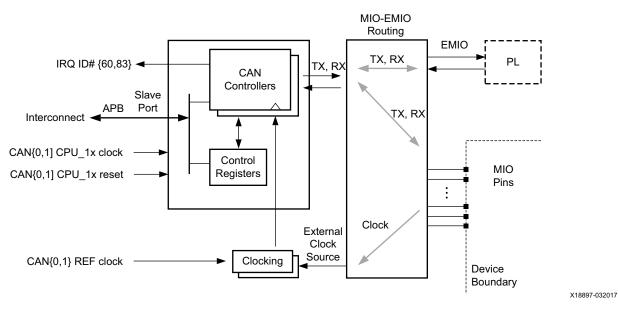

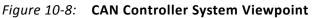

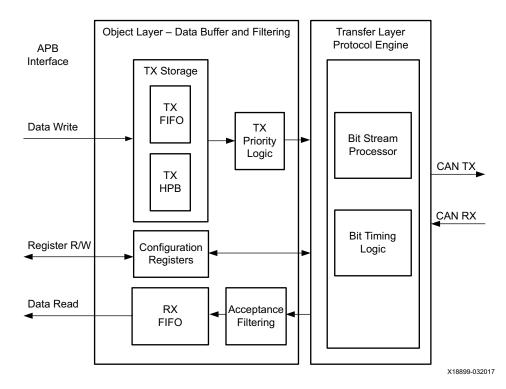

Given the software flexibility afforded by the Zynq UltraScale+ MPSoC device and yet its importance to unlocking the Zynq UltraScale+ MPSoC device's full potential, designers must ensure that they have a strong understanding of the software options available for use with the Zynq UltraScale+ MPSoC device's various parts. This chapter guides you through the software choices available for the Zynq UltraScale+ MPSoC device along with the relevant recommendations.