#### Lecture 5: CMOS Transistor Theory

#### **Mark McDermott**

Electrical and Computer Engineering The University of Texas at Austin

## Outline

- Introduction

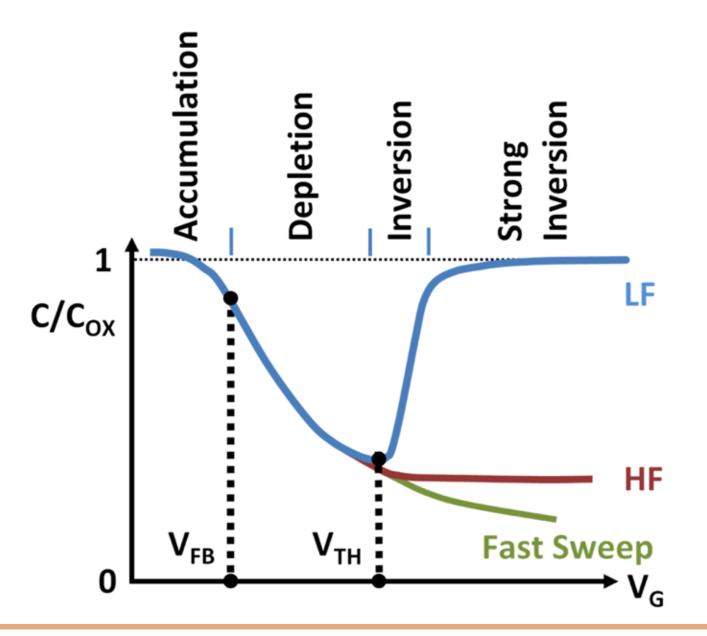

- MOS Capacitor

- nMOS I-V Characteristics

- pMOS I-V Characteristics

- Gate and Diffusion Capacitance

- MOS Channel resistance

- Resistors & RC approximation

#### Introduction

- So far, we have treated transistors as ideal switches

- An ON transistor passes a finite amount of current

- Depends on terminal voltages

- Derive current-voltage (I-V) relationships

- Transistor gate, source, drain all have capacitance

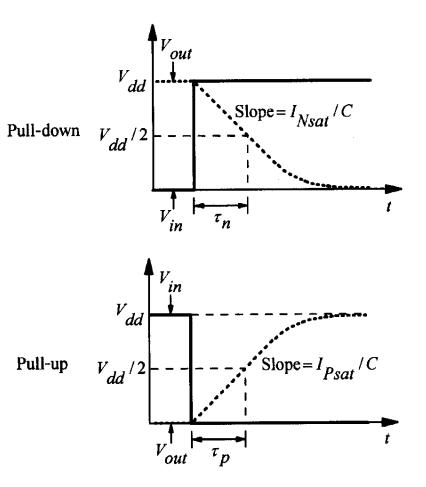

- $-I = C (\Delta V / \Delta t) \rightarrow \Delta t = (C/I) \Delta V$

- Capacitance and current determine speed

## **Electrical Properties of MOS Devices**

- Necessary to understand the basic electrical properties of the MOS transistor (geometry => electrical), e.g., delay/power

- Ensure that the circuits are robust

- Create working layouts

- Predict delays and power consumption

- As technology advances and circuit dimensions scale down, electrical effects become more important

- Secondary/non-ideal effects (next lecture)

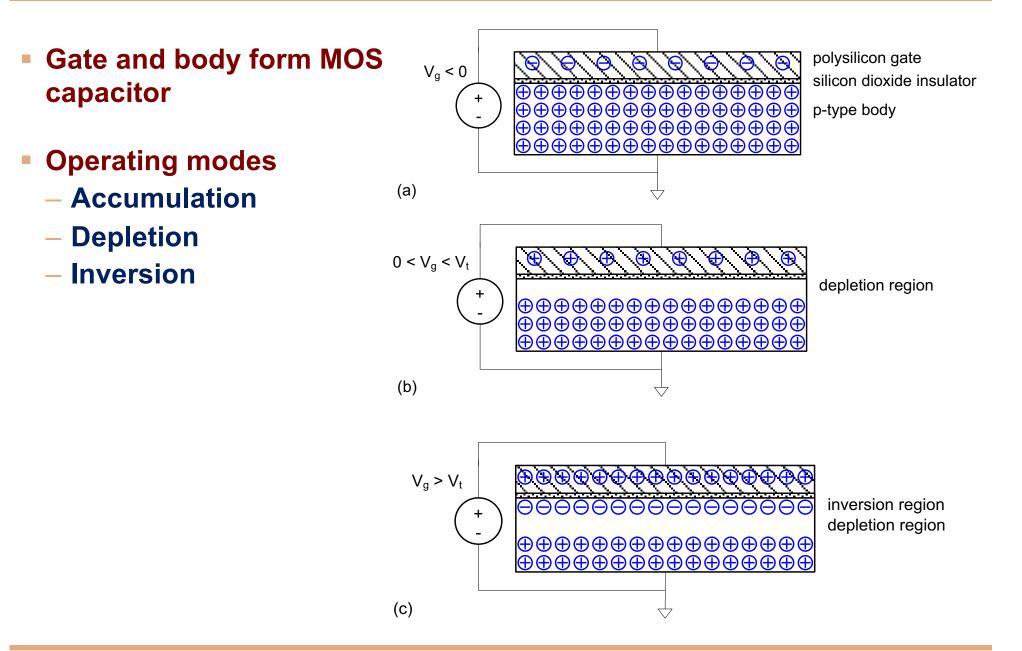

#### **MOS Capacitor**

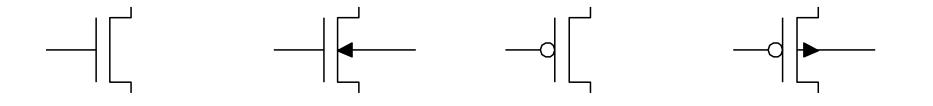

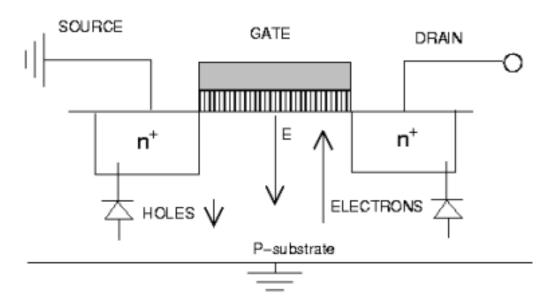

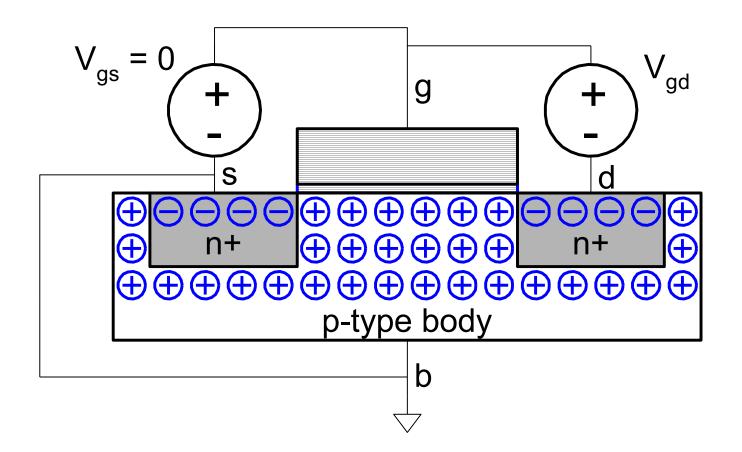

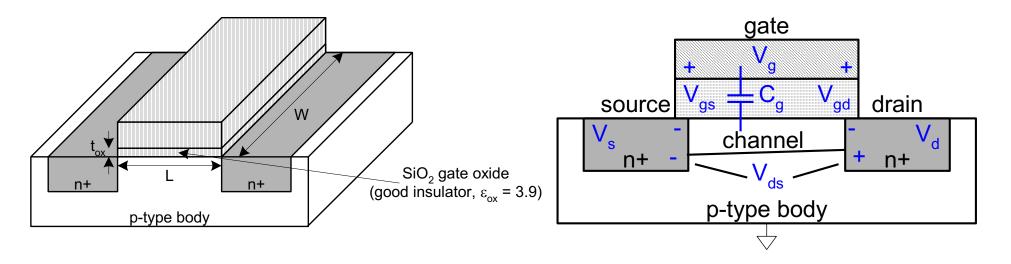

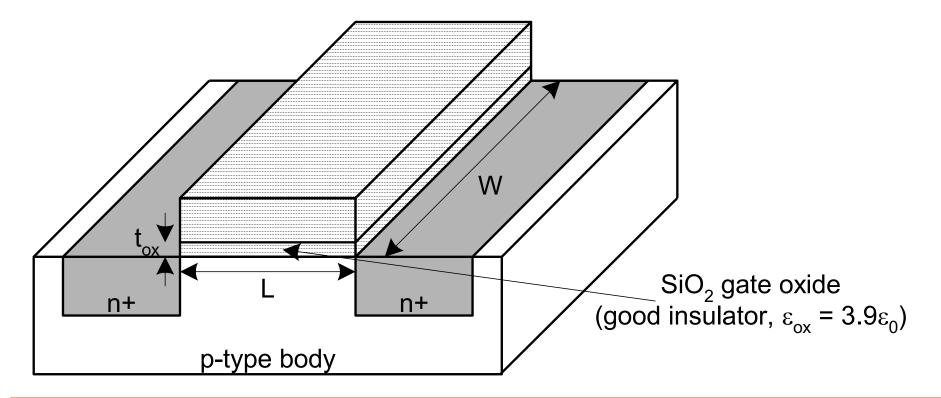

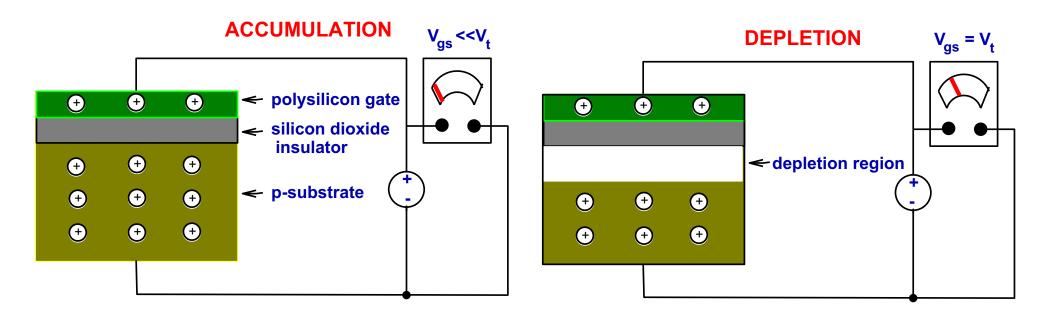

# The nMOS Transistor

Moderately doped p- type substrate (or well) in which two heavily doped n+ regions, the Source and Drain are diffused

Gate is insulated from substrate by thin oxide

– Resistance of oxide is >  $10^{12} \Omega$ , so current ~ 0

#### Two types of nMOS transistor

- Enhancement mode: non conducting when gate voltage Vgs = Vsb (source voltage) (normally used)

- Depletion mode: conducting when  $V_{gs} = V_{sb}$

## **Terminal Voltages**

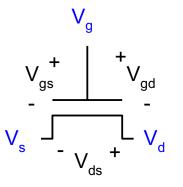

Mode of operation depends on V<sub>g</sub>, V<sub>d</sub>, V<sub>s</sub>

V<sub>gs</sub> = V<sub>g</sub> - V<sub>s</sub>

V<sub>gd</sub> = V<sub>g</sub> - V<sub>d</sub>

V<sub>ds</sub> = V<sub>d</sub> - V<sub>s</sub> = V<sub>gs</sub> - V<sub>gd</sub>

- Source and drain are symmetric diffusion terminals

- By convention, source is terminal at lower voltage

- Hence  $V_{ds} \ge 0$

- nMOS body is grounded; for simple designs, assume source is grounded too

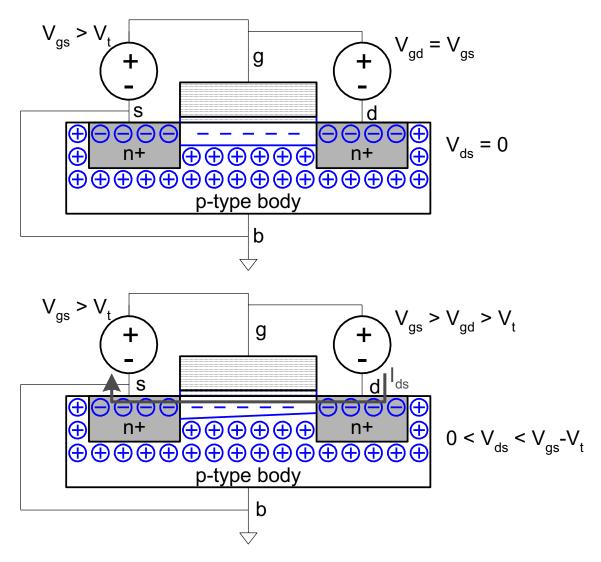

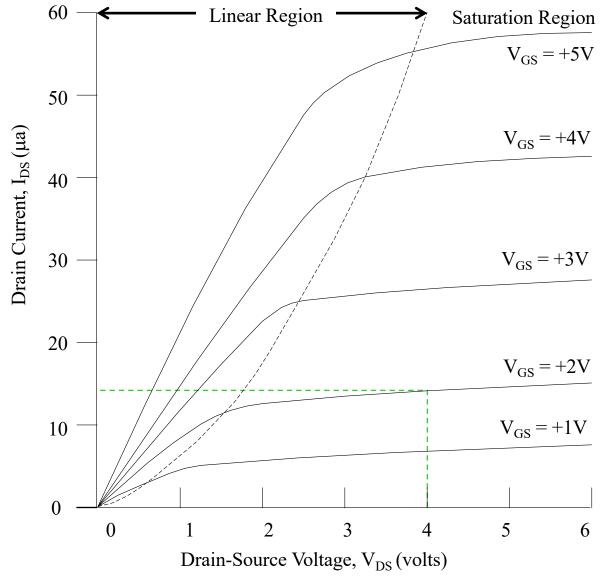

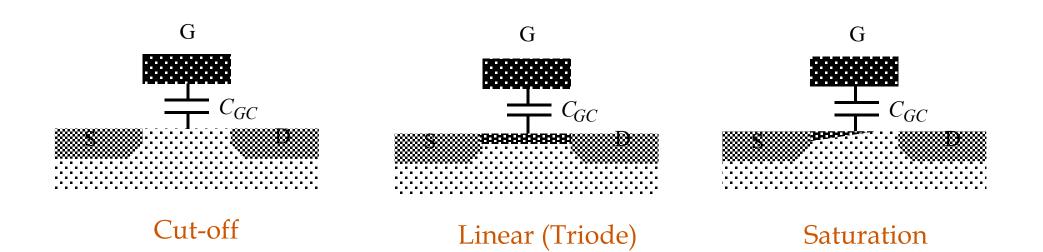

- Three regions of operation

- Cutoff

- Linear

- Saturation

No channel

I<sub>ds</sub> ≈ 0

## **nMOS** Linear

#### Channel forms

- Current flows from d to s

- e<sup>-</sup> from s to d

- I<sub>ds</sub> increases with V<sub>ds</sub>

- Similar to linear resistor

- Since there is a threshold voltage (V<sub>t</sub>) required to invert the charge under the gate, this means that the effective gate voltage is:

$$V_g = V_{gs} - V_t$$

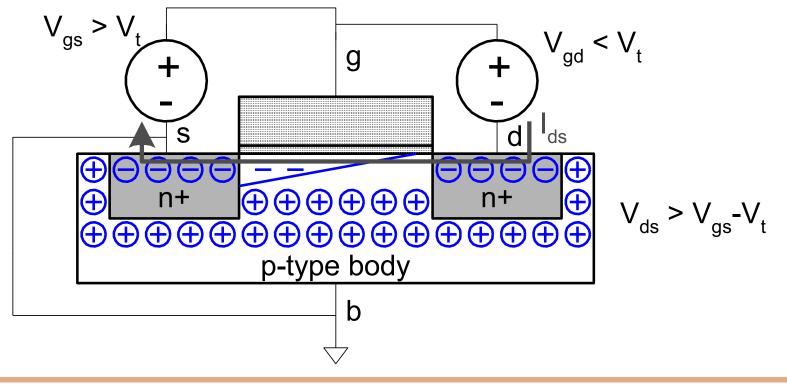

- Channel pinches off

- I<sub>ds</sub> independent of V<sub>ds</sub>

- Current saturates

- Similar to current source

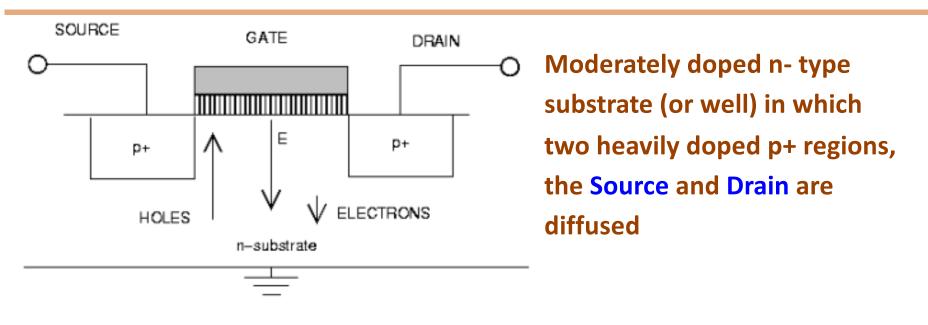

# The pMOS Transistor

Application of a negative gate voltage (w.r.t. source) draws holes into the region below the gate; channel changes from n to p-type (source-drain conduction path)

Conduction due to holes; negative V<sub>d</sub> sweeps holes from source (through channel) to drain

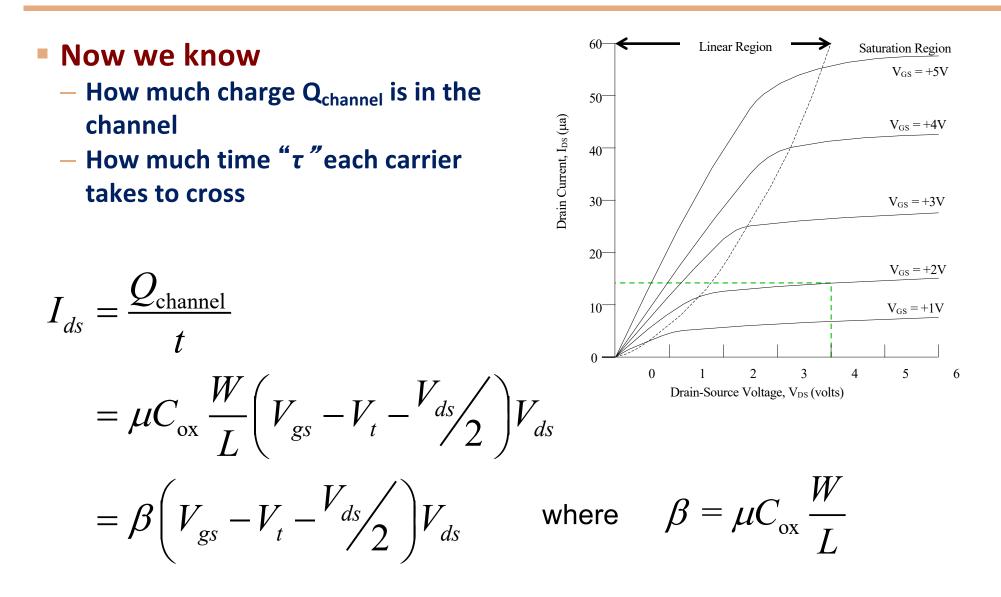

## **I-V Characteristics**

- In Linear region, I<sub>ds</sub> depends on

- How much charge is in the channel?

- How fast is the charge moving?

MOS structure looks like parallel plate capacitor while operating in inversion

**Gate – oxide – channel**

$$Q_{channel} = CV$$

$$C = C_g = \varepsilon_{ox}WL/t_{ox} = C_{ox}WL$$

where  $C_{ox} = e_{ox} / t_{ox}$

$$V = V_{gc} - V_t = (V_{gs} - V_{ds}/2) - V_t$$

- Charge is carried by e-

- Carrier velocity v proportional to lateral E-field between source and drain:

$v = \mu E_{da}$

where

$$E_{ds} = \frac{V_{ds}}{L}$$

Time for carrier to cross channel:

$\tau_{sd} = \frac{Length \, of \, the \, channel \, (L)}{Velocity \, (v)}$

or  $\tau_{sd} = \frac{L^2}{\mu V_{ds}}$

where  $\mu$  is the electron/hole mobility

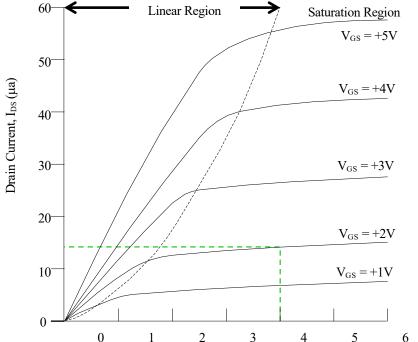

## **nMOS Linear I-V**

- If V<sub>gd</sub> < V<sub>t</sub>, channel pinches off near drain

- When  $V_{ds} > V_{dsat} = V_{gs} V_t$

$=\frac{\beta}{2} \left( V_{gs} - V_t \right)^2$

Now drain voltage no longer increases current

$$I_{ds} = \beta \left( V_{gs} - V_t - \frac{V_{dsat}}{2} \right) V_{dsat}$$

Drain-Source Voltage, VDS (volts)

#### **nMOS I-V Summary**

#### Shockley 1<sup>st</sup> order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{cutoff} \\ \beta \left( V_{gs} - V_t - \frac{V_{ds}}{2} \right) V_{ds} & V_{ds} < V_{dsat} & \text{linear} \\ \frac{\beta}{2} \left( V_{gs} - V_t \right)^2 & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

## Example

#### Example: a 0.6 μm process from AMI semiconductor

$- t_{ox} = 100 \text{ Å}$ 2.5  $-\mu = 350 \text{ cm}^2/\text{V*s}$  $V_{gs} = 5$  $-V_{t} = 0.7 V$ 2 1.5 I<sub>ds</sub> (mA)  $V_{gs} = 4$ Plot I<sub>ds</sub> vs. V<sub>ds</sub> 1  $-V_{gs} = 0, 1, 2, 3, 4, 5$  $V_{gs} = 3$ - Use W/L = 4/2  $\lambda$ 0.5  $V_{gs} = 2$  $V_{gs} = 1$ 0 2 3 4 5 1 0  $\mathsf{V}_{\mathsf{ds}}$

$$\beta = \mu C_{ox} \frac{W}{L} = (350) \left( \frac{3.9 \bullet 8.85 \cdot 10^{-14}}{100 \cdot 10^{-8}} \right) \left( \frac{W}{L} \right) = 120 \frac{W}{L} \mu A / V^2$$

All dopings and voltages are inverted for pMOS

#### • Mobility $\mu_p$ is determined by holes

- Typically 2-3x lower than that of electrons  $\mu_n$  for older technologies.

- Approaching 1 for gate lengths < 20nm.</p>

#### Thus pMOS must be wider to provide the same current

- Simple assumption,  $\mu_n / \mu_p = 2$  for technologies > 20nm

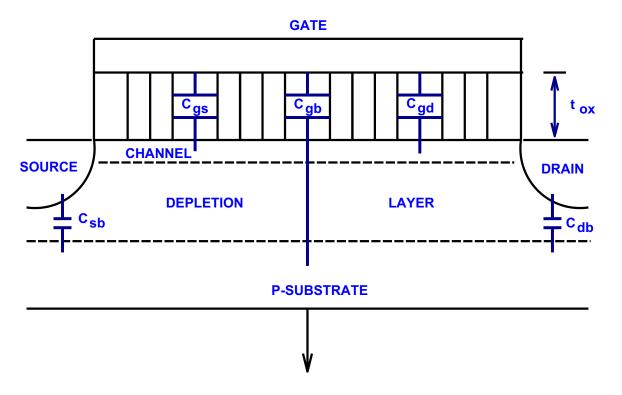

- Any two conductors separated by an insulator have capacitance

- Gate to channel capacitor is very important

- Creates channel charge necessary for operation

- Source and drain have capacitance to body

- Across reverse-biased diodes

- Called diffusion capacitance because it is associated with source/drain diffusion

#### **Gate Capacitance**

- Approximate channel as connected to source

- $C_{gs} = \varepsilon_{ox}WL/t_{ox} = C_{ox}WL = C_{per/micron}W$

- C<sub>permicron</sub> is typically about 2 fF/µm for minimum channel length device

## **Capacitance Estimation**

The dynamic response (switching speed) of a CMOS circuit is very dependent on parasitic capacitances associated with the circuit

#### **Parasitic Capacitances:**

$C_{gs}$ ,  $C_{gd}$  = gate-to-channel capacitances lumped at source and drain regions  $C_{sb}$ ,  $C_{db}$  = source and drain diffusion capacitances to bulk (substrate)

#### Add routing capacitances to get total capacitance.

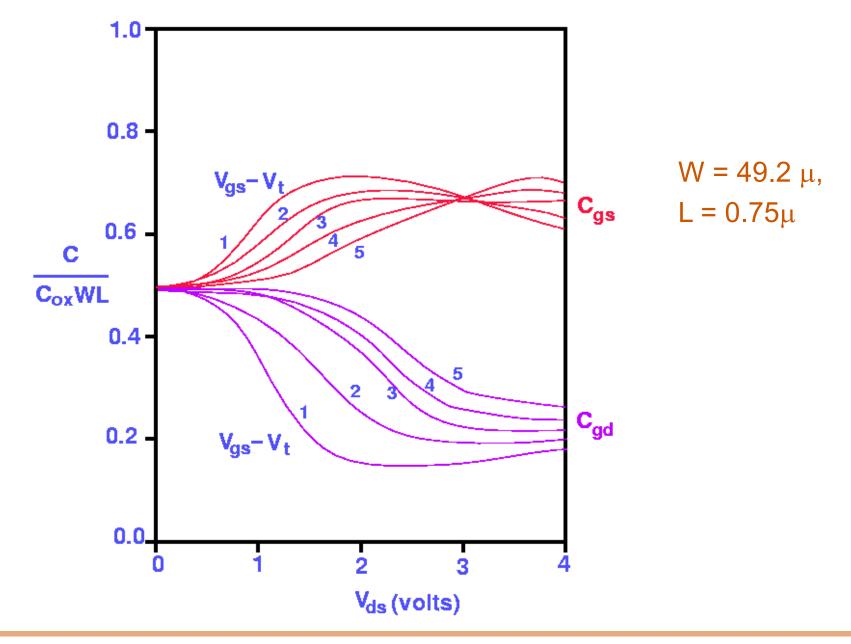

## **Gate Capacitance of MOS Transistor**

#### Gate Capacitance of MOS Transistor (cont.)

## **Gate Capacitance: Operation Region Dependence**

| Operation Region | $C_{gb}$                          | C <sub>gs</sub>       | $C_{gd}$           |

|------------------|-----------------------------------|-----------------------|--------------------|

| Cutoff           | C <sub>ox</sub> WL <sub>eff</sub> | 0                     | 0                  |

| Triode           | 0                                 | $C_{ox}WL_{eff}/2$    | $C_{ox}WL_{eff}/2$ |

| Saturation       | 0                                 | $(2/3)C_{ox}WL_{eff}$ | 0                  |

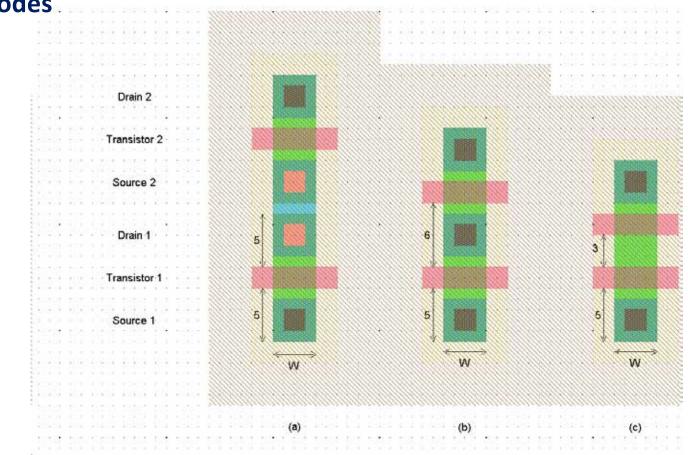

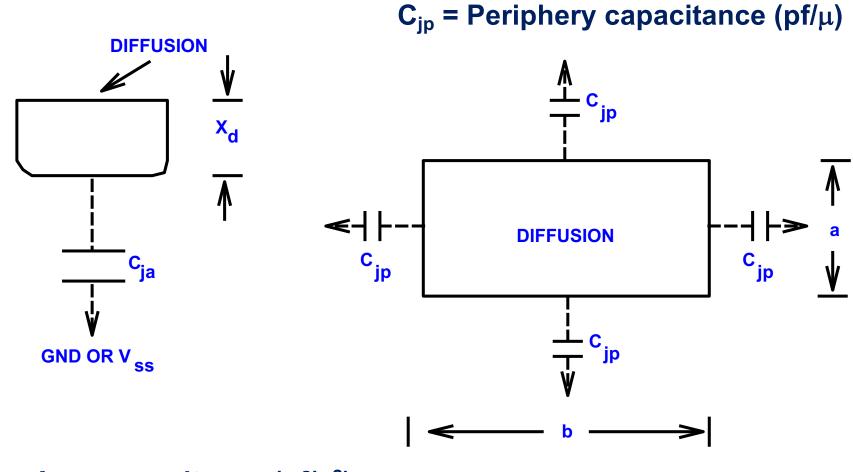

## **Diffusion Capacitance**

- C<sub>sb</sub>, C<sub>db</sub> from Source/Drain

- Undesirable, called parasitic capacitance

- Capacitance depends on area and perimeter

- Use small diffusion nodes

- Comparable to C<sub>g</sub>

for contacted diff

- ½ C<sub>g</sub> for uncontacted

- Varies with process

## **Area and Periphery Capacitance**

$C_{ja}$  = Area capacitance (pf/ $\mu^2$ )

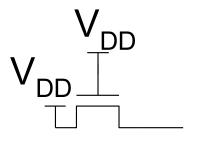

# We have assumed source is grounded

- What if source > 0?

- -e.g. pass transistor passing V<sub>DD</sub>

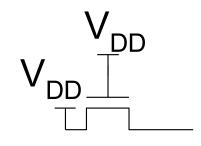

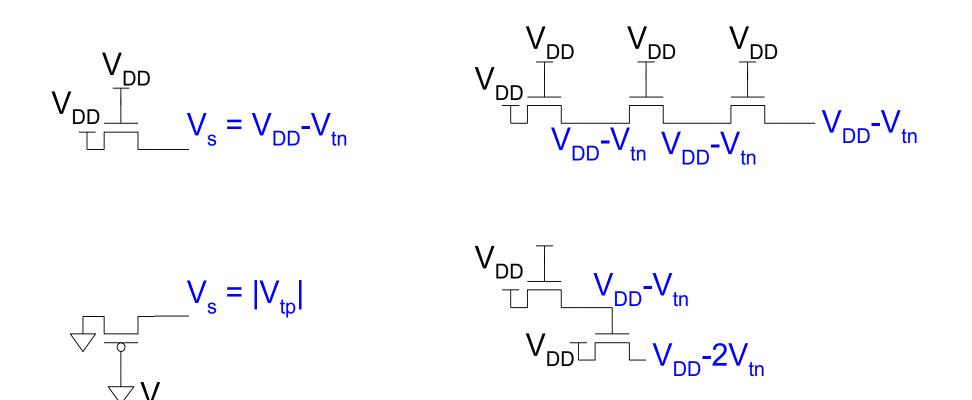

#### **Pass Transistors**

# We have assumed source is grounded

- What if source > 0?

- -e.g. pass transistor passing V<sub>DD</sub>

- $\bullet V_g = V_{DD}$

- If V<sub>s</sub> > V<sub>DD</sub>-V<sub>t</sub>, V<sub>gs</sub> < V<sub>t</sub>

- Hence transistor would turn itself off

# nMOS pass transistors pull no higher than V<sub>DD</sub>-V<sub>tn</sub>

- Called a degraded "1"

- Approach degraded value slowly (low I<sub>ds</sub>)

- pMOS pass transistors pull no lower than V<sub>tp</sub>

#### **Pass Transistor Circuits**

**NOTE:** These values are for steady state conditions only.

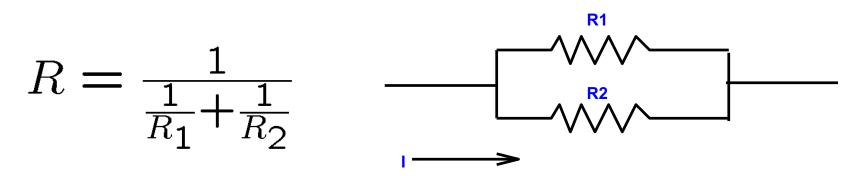

## **Effective Resistance**

#### Shockley models have limited value

- Not accurate enough for modern transistors

- Too complicated for hand analysis

- Simplification: treat transistor as resistor

- Replace I<sub>ds</sub>(V<sub>ds</sub>, V<sub>gs</sub>) with effective resistance R

- $I_{ds} = V_{ds}/R$

- R averaged across switching of digital gate

- Too inaccurate to predict current at any given time

But good enough to predict RC delay

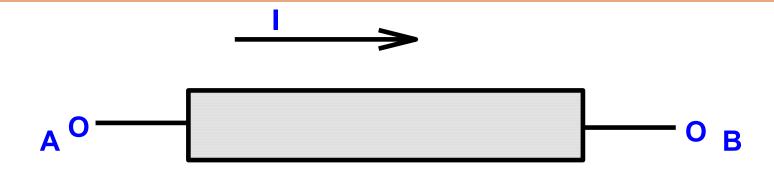

#### **The MOS Resistor**

#### Resistance of a bar of uniform material

$R = \frac{\rho \times L}{A} = \left(\frac{\rho}{t}\right) \left(\frac{L}{W}\right)$

where  $\rho = \text{resistivity of the material}$ ,

A = cross-section of the resistor

t, W =thickness, width of the material

The channel resistance of a MOS transistor in the linear region

$$R_c = k(\frac{L}{W}),$$

where  $k = \frac{1}{\mu C_{ox}(V_{gs} - V_t)}$

W/L ratio defines size of N and P channel transistors Channel resistance of turned-on transistor is:

$$R_c = k(\frac{L}{W})$$

, where  $k = \frac{1}{\mu C_{ox}(V_{gs} - V_t)}$

k is in the range of 1000 -- 30,000  $\Omega$  / Resistance increases by about 0.25%/°C above 25°C

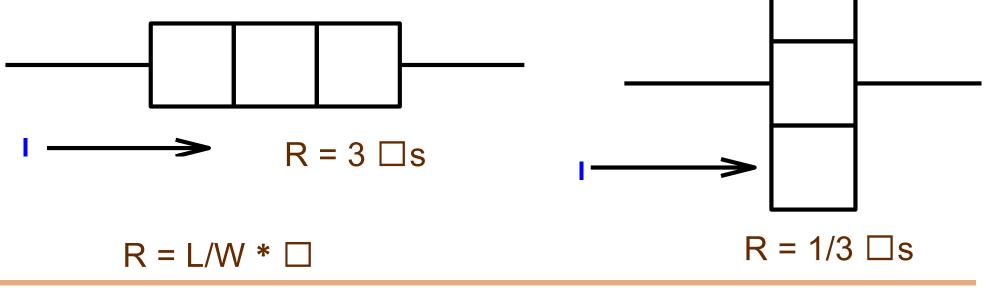

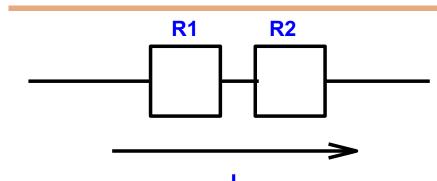

#### **Resistors Connected in Series**

Sheet Resistance,  $R_s$ : Any material on the chip can be divided into squares W on a side with ( $R_s \Omega/\Box$ ) R =  $R_s(L/W)\Omega$

Typical sheet resistances ( $\Omega/\Box$ ) for 0.25 $\mu$  TSMC process: 4.7 for N+, 3.5 for P+, 4.2 for Poly, 0.06 for Metal1, 0.08 for Metal2 - Metal4, 0.03 for Metal5, and 1190 for the N-well Increase of about 0.3%/° C (metal, poly), 1%/° C (diffusion)

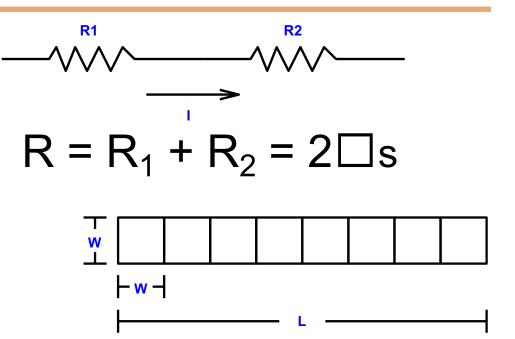

#### **Resistors Connected in Parallel**

For two squares in parallel, the equivalent resistance is ½ Expressing sheet resistance in S simplifies the calculations Contact resistance becomes more important as processes scale down

About 6  $\Omega$  for N+, P+, Poly, Metal 4

2  $\Omega$  for Metal2

4  $\Omega$  for Metal3

8  $\Omega$  for Metal5

in a 0.25m TSMC process

Use multiple contacts/vias for low resistance connections

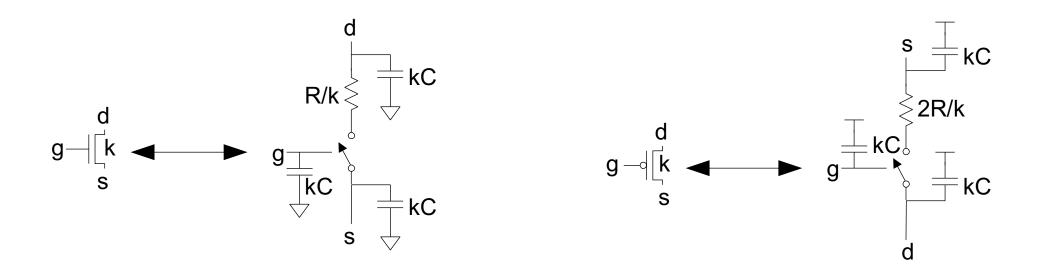

## **RC Delay Model**

- Use equivalent circuits for MOS transistors

- Ideal switch + capacitance and ON resistance

- Unit nMOS has resistance R, capacitance C

- Unit pMOS has resistance 2R, capacitance C

- Capacitance proportional to width

- Resistance inversely proportional to width

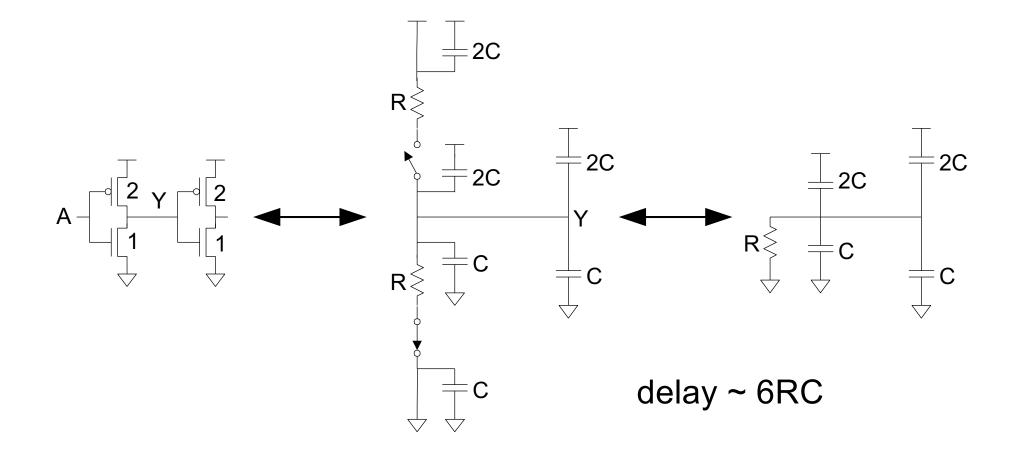

#### **Inverter Delay Estimate**

#### Estimate the delay of a fanout-of-1 inverter

## Backup

```

*file asic3.sp test of 10 stage lumped mos model

* comments

.option scale=1e-6 post=2 nomod

vin in 0 pl 0v 0n 5v 100ps

.param rpoly=40 wt=100 lt=1.2

m1 single in 0 0 n w=wt l=lt

xm1 lumped in 0 0 lrgtp xw=wt xl=lt

vsingle single 0 5v

vlumped lumped 0 5v

.tran 25ps 4ns

.graph tran model=time1 single=par('-i(vsingle) ') lumped=par('-i(vlumped)')

.model time1 plot xmin=0ps xmax=800ps

* subckt and model on next page

*.subckt lrgtp drain gate source bulk

```

.subckt lrgtp drain gate source bulk m1 drain gate source bulk n w='xw/18' l=xl m2 drain g1 source bulk n w='xw/9' l=xl m3 drain g2 source bulk n w='xw/9' l=xl m4 drain g3 source bulk n w='xw/9' l=xl m5 drain g4 source bulk n w='xw/9' l=xl m6 drain g5 source bulk n w='xw/9' l=xl m7 drain g6 source bulk n w='xw/9' l=xl m8 drain g7 source bulk n w='xw/9' l=xl m9 drain g8 source bulk n w='xw/9' l=xl m10 drain g9 source bulk n w='xw/18' l=xl

# Example of SPICE Deck, Cont'd

```

r1 gate g1 'xw/xl*rpoly/9'

r2 g1 g2 'xw/xl*rpoly/9'

r3 g2 g3 'xw/xl*rpoly/9'

r4 g3 g4 'xw/xl*rpoly/9'

r5 g4 g5 'xw/xl*rpoly/9'

r6 g5 g6 'xw/xl*rpoly/9'

r7 g6 g7 'xw/xl*rpoly/9'

r8 g7 g8 'xw/xl*rpoly/9'

r9 g8 g9 'xw/xl*rpoly/9'

.ends lrgtp

** model section *

.model n nmos level=3 vto=0.7 uo=500 kappa=.25 kp=30u

eta=.03 theta=.04 +vmax=2e5 nsub=9e16 tox=250e-10

gamma=1.5 pb=0.6 js=.1m xj=0.5u ld=0.0

+nfs=1e11 nss=2e10 cgso=200p cgdo=200p cgbo=300p

.end

```

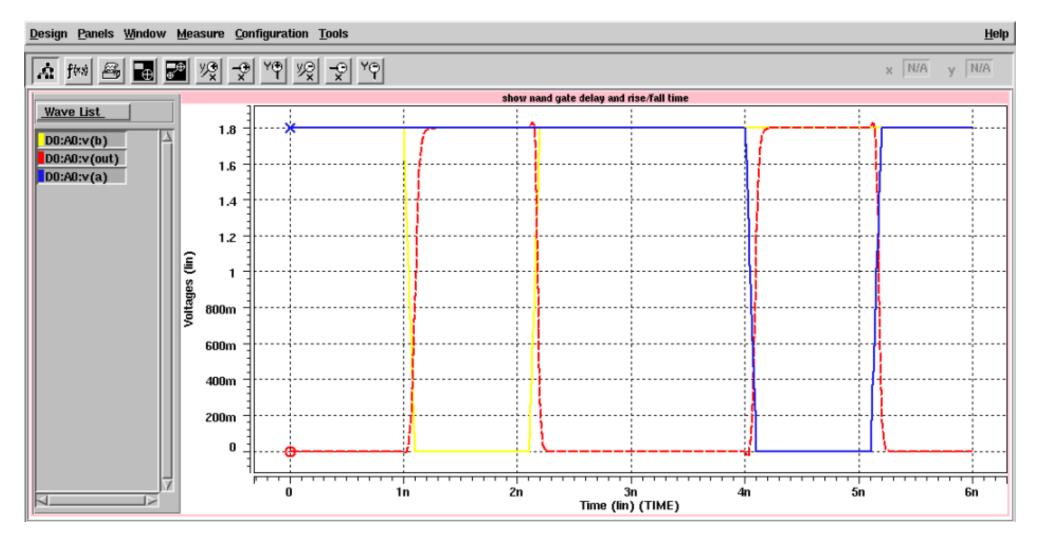

## **Spice Simulation: NAND Gate**

#### SPICE "deck" has "measure", print statements; parameters, netlist Model: 0.18 micron

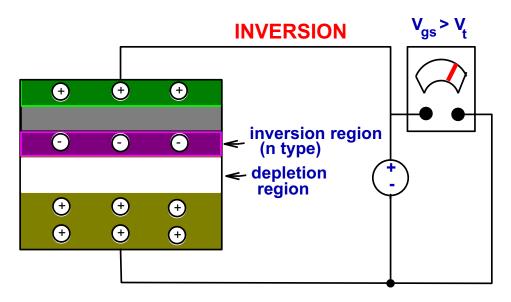

### **Modes in MOS Structures**

### **Greek alphabet**

#### **GREEK ALPHABET** By Ben Crowder • bencrowder.net • Last modified 2 May 2012 Zζ Λδ Eε Bβ Aα ALPHA [a] DELTA [d] ZETA [dz] BETA [b] GAMMA [g] EPSILON [e] δέλτα ἒ ψιλόν ἄλφα βῆτα γάμμα ζῆτα $M\mu$ Kκ Iι H $(\mathbf{H})$ THETA [th] **ΕΤΑ** [ε:] IOTA [i] KAPPA [k] LAMBDA [1] **MU** [m] λάμβδα ήτα θῆτα ίῶτα κάππα μũ Ξξ Nν Σσς Pρ Ππ **NU** [n] XI [ks] OMICRON [0] RHO [r] SIGMA [s] **PI** [p] Ĕεĩ vũ ὂ μικρόν πεĩ þῶ σĩγμα Tτ Ωω Yυ TAU [t] UPSILON [#] PHI [ph] CHI [k<sup>h</sup>] PSI [ps] OMEGA [5:] ταῦ ὖ ψιλόν φεĩ ψεĩ ὦ μέγα χεĩ