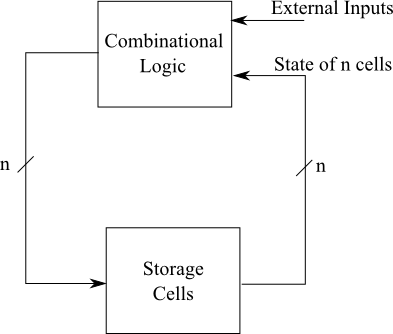

The clock partitions time into clock cycles:

At the START of each clock cycle, every storage cell on the chip is storing a 0 or a 1. During the clock cycle, those bits are input to the combinational logic gates that are processing information. Also input to that combinational logic are 0s and 1s that come from outside the chip. We call those *external inputs*. The logic gates compute results that are then stored in these cells at the END of that clock cycle, and are therefore available as input to the combinational logic in the next clock cycle.

As we said in class, each storage cell is made up of 2 gated latches, as shown below. I use the box labeled Gated Latch to represent each gated latch. Check your notes from Wednesday or look in the book for the details of a gated latch.

If we used a single gated latch as the storage cell in the above diagram, note what bad thing would happen. We want the combinational logic to perform a function based on the values stored in the storage cells at the beginning of the clock cycle and the external inputs. But the result of the combinational logic is stored in the gated latch, thereby changing its input to the combinational logic. So, it is no longer the case that the combinational logic processing will be based on what is stored in the cells at the start of the clock cycle. In fact, the combinational logic will receive new values from the gated latches, and in turn produce new results which will be sent to the gated latches, which will produce still new inputs to the combinational logic. In fact, this madness will continue to repeat until the WE signal (the clock) is 0, stopping the process. The end result is that the result produced by the combinational logic will depend on how many round trips are made between storage cells and combinational logic until the WE signal finally goes to 0. How can we fix this? Answer: We don't use gated latches, we use flip flops! The circuit now looks like this:

Note that information is stored in the gated latch M when CLOCK =1 and in gated latch S when CLOCK =0. When CLOCK =0, the value stored in M can not be changed. When CLOCK =1, the value stored in S can not be changed. Let's look at the two parts of the clock cycle, in turn. In the first part of the clock cycle, CLOCK = 1. =============================================== The value from gated latch S is input to the combinational logic. But, since CLOCK =1, the value stored there can not change, guaranteeing that the input to the combinational logic continues to be the value that has been in the storage cell since the start of the cycle. Since CLOCK =1, the result of the combinational logic is stored in the gated latch M. But (again) that result can not get to S because CLOCK =1. In the second part of the clock cycle, CLOCK = 0. ================================================ Since CLOCK =0, any new result of the combinational logic can not affect gated latch M. The result that was stored there remains unchanged for the rest of the clock cycle. However, since CLOCK = 0, what was stored in M during the first part of the cycle is now passed to S, so that it is ready for the start of the next cycle. In summary: ========== In the first part of the cycle, latch S maintains its value which is used by the combinational logic to produce a result which is stored in M. In the second part of the cycle, the value that was produced by the combinational logic in the first part of the cycle gets transferred to S so it will be ready at the start of the next cycle. Any changes in the output of the combinational logic due to the new value stored in S will have no effect since M can not change during the second part of the cycle. The result: The combinational logic produces results based on what is stored in the cell at the start of the cycle, and that result is available to the combinational logic at the start of the next cycle. I hope this now makes more sense. Have a great weekend. See you in class on Monday. Yale Patt