## Department of Electrical and Computer Engineering The University of Texas at Austin

EE 460N Fall 2016 Y. N. Patt, Instructor Siavash Zangeneh, Ali Fakhrzadehgan, Steven Flolid, Matthew Normyle TAs Exam 2 November 21, 2016

| Name:                                          | Solution                                                                                 |

|------------------------------------------------|------------------------------------------------------------------------------------------|

|                                                |                                                                                          |

|                                                | Problem 1 (25 points):                                                                   |

|                                                | Problem 2 (15 points):                                                                   |

|                                                | Problem 3 (15 points):                                                                   |

|                                                | Problem 4 (20 points):                                                                   |

|                                                | Problem 5 (25 points):                                                                   |

|                                                | Total (100 points):                                                                      |

|                                                |                                                                                          |

|                                                |                                                                                          |

| Note: Please be sure that your space provided. | answers to all questions (and all supporting work that is required) are contained in the |

| Note: Please be sure your name                 | e is recorded on each sheet of the exam.                                                 |

|                                                |                                                                                          |

| Please sign the following. I have              | re not given nor received any unauthorized help on this exam.                            |

|                                                |                                                                                          |

| Signature:                                     |                                                                                          |

| Name: |  |

|-------|--|

|       |  |

### Problem 1 (25 points)

**Part a (5 points):** A 2-way set-associative physically indexed, physically tagged write through cache implements LRU replacement. Memory space is  $2^{28}$ , memory is byte-addressable, and the physical address bits are assigned as follows:

| 15       | 7          | 6                  |

|----------|------------|--------------------|

| Tag bits | Index bits | Byte on block bits |

What are the total number of bits of storage required to implement a perfect LRU replacement policy for this cache.

Part b (5 points): If a cache is virtual, we avoid confusion as to what each address in the tag store means by one of two ways. Name one of them.

-flush cache on context switches - Keep process ID of each cache block in its tag store entry

**Part c (5 points):** Interrupt priority is determined by the urgency of handling the event. Is any event more urgent than "loss of power." Explain.

Machine check: a processor that does not work correctly is morse than a processor that does not work.

**Part d (5 points):** IEEE Floating Point uses radix 2 for dealing with exponents. The old IBM 360, currently called IBM Z-series, uses radix 16. Two advantages of radix 2 over radix 16 are:

Smaller wobble the most significant bit does not have to be stored

**Part e (5 points):** Seymour Cray, in many ways the "father" of the vector computer, did not like the notion of cache memory, so the Cray I did not have caches. What is it about cache memory that he did not like?

non - determinism

| Name: |

|-------|

|-------|

### Problem 2 (15 points)

Consider a floating point data type with all the IEEE characteristics except it contains 9 bits, rather than 32 or 64 bits. Your job: How many bits of exponent, how many bits of fraction? The bias is 4.

We can represent  $2\frac{1}{4}$  and  $\frac{1}{16}$  exactly.

If the rounding mode is round-toward-zero, computing (  $(2\frac{1}{4} + \frac{1}{16}) + \frac{1}{16}$  ) produces the result  $2\frac{1}{4}$ , and computing (  $(\frac{1}{16} + \frac{1}{16}) + 2\frac{1}{4}$  ) produces the result  $2\frac{3}{8}$ .

Part a (3 points): Given that computing ( $(2\frac{1}{4} + \frac{1}{16}) + \frac{1}{16}$ ) should produce the result  $2\frac{3}{8}$ , why was the result computed as  $2\frac{1}{4}$ ?

(24+16)=2516 cannot be represented exactly and is rounding to 214. Or, there are not enough fraction bits for intermediate results of ADDs, which results in rounding errors.

## Part b (7 points):

Number of bits of fraction

| 7 .      |

|----------|

| <u> </u> |

Number of bits of exponent

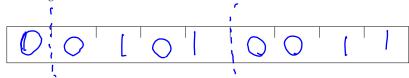

$\frac{1}{16} = (.000 \times 2^{-4})$   $= 0.00001 \times 2^{1}$

# Part c (5 points):

How would you represent  $2\frac{3}{8}$  in our 9 bit floating point format?

$2\frac{1}{4} + \frac{1}{18} = 2\frac{5}{18} = 1.00101 \times 2^{1}$ fraction bits

should be

fewer than 5

$2\frac{3}{8} = 1.0011 \times 2^{1}$ exponent = 4+1 = 5 = 0101

However,  $\frac{1}{8} + 2\frac{1}{4}$   $= 1.001 \times 2$   $+ 0.0001 \times 2$   $1.0011 \times 2$ is represented exactly

is represented exactly

50 there are exactly 4 fraction

bits

| Name: |

|-------|

|-------|

## Problem 3 (15 points)

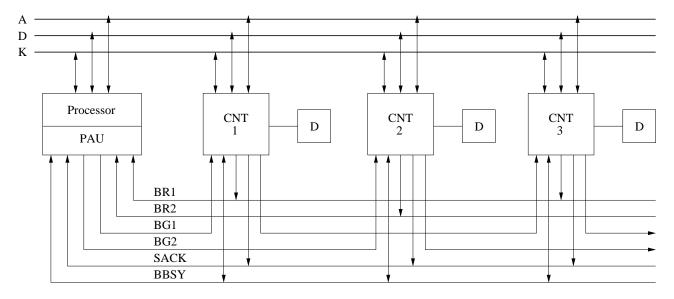

A processor/PAU and three device controllers are connected to an asynchronous bus as shown. Bus requests are of the form BR1 and BR2. BR2 is of higher priority.

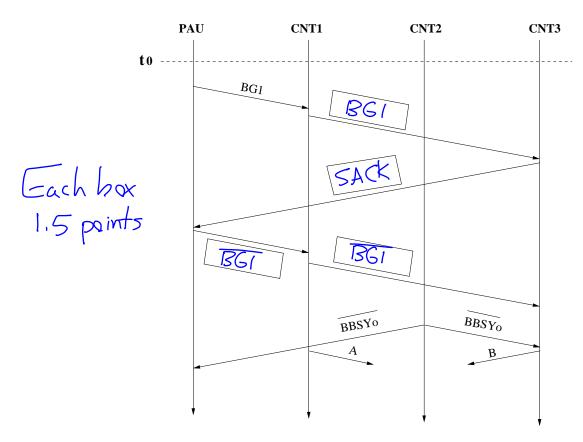

In class, we showed timing diagrams for **transactions** on the bus. In this problem, we will examine the timing diagram for **arbitration**, as shown on the next page.

Name:

At t0, a bus master asserts BBSYo, allowing arbitration for the next bus cycle to begin. If you examine the entire timing diagram, can you tell which controller acquires the bus at t0?

The PAU asserts BG1 as shown on the diagram. The next four signals are unlabeled. Your job: provide the labels.

At some point, the current bus master completes the bus cycle and releases the bus. This causes controller 1 to provide signals A or controller 3 to provide signals B.

Does controller 1 want the bus for the next bus cycle? Yes No (Gircle one). Explain.

2 points No, since it daisy chains 1861 to CNT3

Does controller 3 want the bus for the next bus cycle? Yes) No (Circle one). Explain.

2 points Yes, since if accepts 1861 by asserting 5ACK

1 point What signal(s), if any, are represented by A. Now

3 points What signal(s), if any, are represented by B. 1885%, MSXN, Addr

#### Problem 4. (20 points)

Suppose we have a byte-addressable machine with a virtually indexed, physically tagged cache. The cache is two way set associative and is initially empty. The cache uses perfect LRU replacement.

The machine has a 16 bit virtual address space, with a 128 byte page size. The physical address space is 11 bits. Assume the virtual address has the form:

| Leftover bits | Y Index bits | Z Byte on line bits |

|---------------|--------------|---------------------|

|               |              |                     |

Part a: How many cache lines are there in the 16 bit virtual address space? Solve in terms of Z.

Part b: Suppose you know one set of the cache is full, and nothing about the other sets. How many cache lines in

the virtual address space are **definitely not** in the cache? Solve in terms of Y and Z.

| The following are conse | cutiv | ve memory accesses.   |                  | 11:6           | (8 byte 3) can 7         |

|-------------------------|-------|-----------------------|------------------|----------------|--------------------------|

| it cerche line          | 51    | 'ze > 8 hyles         | - (5) WINZA R    | DONIT, A C     | y byte (5) con 1         |

|                         |       | Virtual Address       | Physical Address | Cache Hit/Miss | be hit                   |

|                         | 1     | 0000 000 1 1000 0000  | 0111 0000000     | Miss           | 10 11 21                 |

|                         |       |                       |                  |                | If more than 6 bis       |

|                         | 2     | 0000 000 1 1000 1000  | 0111 0001000     | Miss           | are used for indexin     |

|                         |       |                       |                  |                | WAS WERN FOR IMPRING     |

|                         | 3     | 0000 000 1 1000 1 100 | 0111 0001100     | Hit            | @should're been          |

|                         |       | •                     |                  |                | Sylvania C WEEN          |

|                         | 4     | 1111 000 1 1000 0000  | 0101 0000000     | Miss           | l in hit                 |

|                         |       |                       |                  |                |                          |

|                         | 5     | 0001 001 1 1000 0000  | 0001 0000000     | Miss           | If there are fewer than  |

|                         |       | 1                     |                  |                | It thought him being the |

|                         | 6     | 0000 000 1 1000 0100  | 0111 0000100     | Miss           | 6 bits used for indexi   |

|                         |       |                       |                  |                |                          |

|                         | 7     | 0000 000 0 1000 0001  | 1110 0000001     | Miss           | (8) cannot be a hit      |

|                         |       | 1                     |                  |                | Security 126 WWI         |

|                         | 8     | A                     | 0001 xxxxxxx     | Hit            | 51h Q 6 & 7 WOU          |

|                         |       |                       |                  |                |                          |

|                         | 9     | 0000 0001 1100 0100   | 0111 1000100     | В              | replace it               |

|                         | ,     | 3333 3331 1100 3100   | 0111 1000100     |                | 1 1/2 1000               |

|                         |       |                       |                  |                |                          |

If more than 6 bits are used for indexing @should've been

If there are fewer than 6 bits used for indexing 8) cannot be a hit

sing 6 & 0 would replace it

Part c: What range of virtual addresses can A be? Write your answer in binary.

000100111000 0xxx

Part d: Which bits of the virtual address are used for indexing? VA [8;37]

Dints Part e: Is B a hit or a miss? Wiss

### Problem 5 (25 points)

Consider an Out-of-Order exeuction/In-Order retirement processor. The ISA specifies 8 registers, R0 to R7. The microarchitecture contains one non-pipelined adder and one non-pipelined multiplier. Fetch and Decode take one cycle each. ADD execution takes 2 cycles, MUL execution takes 4 cycles, and in both cases one cycle is needed to write the result to a destination register. There is no data bypassing. The adder and multiplier each has a 3-entry reservation station. They are initially empty, and are filled from top to bottom. Each instruction remains in the reservation station until it retires.

A program consisting of five instructions takes 17 clock cycles to execute on this processor. The state of the register file is shown before execution starts (i.e., before cycle 1), at the end of cycle 7, and at the end of cycle 17.

|    | V  | Tag     | Value  |    | V  | Tag     | Value  |    | V  | Tag     | Value  |

|----|----|---------|--------|----|----|---------|--------|----|----|---------|--------|

| R0 | 1  | -       | 4      | R0 | 1  | -       | 4      | R0 | 1  | -       | 4      |

| R1 | 1  | -       | 5      | R1 | 0  | $\pi$   | -      | R1 | 1  | -       | 5      |

| R2 | 1  | -       | 0      | R2 | 1  | -       | 20     | R2 | 1  | -       | 31     |

| R3 | 1  | -       | 20     | R3 | 0  | au      | -      | R3 | 1  | -       | 26     |

| R4 | 1  | -       | 6      | R4 | 1  | -       | 6      | R4 | 1  | -       | 6      |

| R5 | 1  | -       | 3      | R5 | 1  | -       | 3      | R5 | 1  | -       | 3      |

| R6 | 1  | -       | 2      | R6 | 1  | -       | 2      | R6 | 1  | -       | 2      |

| R7 | 1  | -       | 7      | R7 | 1  | -       | 7      | R7 | 1  | -       | 7      |

|    | Вє | efore C | ycle 1 | I  | Er | nd of C | ycle 7 | I  | En | d of cy | cle 17 |

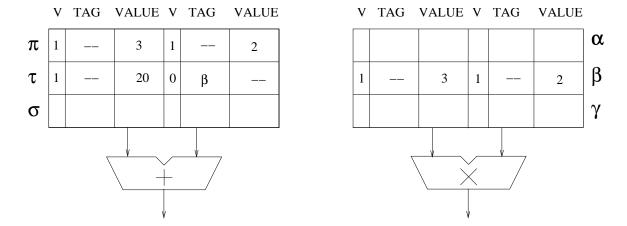

The state of the reservation stations at the end of cycle 7 are shown below.

Reservation Stations at the end of cycle 7

Name:

The following chart shows the cycles when the adder and multiplier are in use.

|            | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

|------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| Multiplier |   |   | Е | Е | Е | Е | Е | Е | Е | Е  |    |    |    |    |    |    |    |

| Adder      |   |   |   | Е | Е |   |   |   |   |    |    | Е  | Е  |    | Е  | Е  |    |

Part a (20 points): Specify the five-instruction program.

## instruction

| 1 | MUL RZ, RO, RI | R2 = 20 |

|---|----------------|---------|

| 2 | ADD RI, RS, R6 | RI C5   |

| 3 | MUL R3, R5, R6 | R3 C 6  |

| 4 | APP R3, RZ, R3 | R3 626  |

| 5 | APD RZ, RI, R3 |         |

**Part b (5 points):** How big is the Reorder Buffer? **Explain**. Hint: Instructions are allocated to the reorder at the same time they are placed in a reservation station.

4: Since the 5th instruction does not exist in the ADD reservation station in the end of cycle 7, that means 5th instruction could not have been decided due to Reorder Buffer being full

FDEEFER2)

FDEEFER2)

FDEEV (RI)

FDEEFER2)

FDD:D

ROBfull, decode is stalled