# Department of Electrical and Computer Engineering The University of Texas at Austin

EE 460N Fall 2014

Y. N. Patt, Instructor

Stephen Pruett, Emily Bragg, Siavash Zangeneh TAs

Final Exam

December 12, 2014

| Name:                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                         |

| Problem 1 (20 points):                                                                                                                  |

| Problem 2 (10 points):                                                                                                                  |

| Problem 3 (15 points):                                                                                                                  |

| Problem 4 (15 points):                                                                                                                  |

| Problem 5 (20 points):                                                                                                                  |

| Problem 6 (20 points):                                                                                                                  |

| Problem 7 (25 points):                                                                                                                  |

| Total (125 points):                                                                                                                     |

|                                                                                                                                         |

|                                                                                                                                         |

| Note: Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space provided. |

| Note: Please be sure your name is recorded on each sheet of the exam.                                                                   |

| Please sign the following. I have not given nor received any unauthorized help on this exam.                                            |

| Signature:                                                                                                                              |

| Name:     |  |

|-----------|--|

| 1 Tallic. |  |

# Problem 1 (25 points)

Part a (5 points): We showed in class that multiplication of two 16-bit binary fixed point numbers consists of a sequence of 16 shifts and adds. Andrew Booth's algorithm reduced that number from 16 to what?

8

Part b (5 points): Speed-up with p processors is defined as T1/Tp, where T1 is the time to solve the problem with one processor and Tp is the time to solve the problem if you have p processors. What important requirement is there on T1?

It is as small as possible

Part c (5 points): A four processor system, each processor having its own cache, uses the Directory scheme to maintain cache coherence. The directory stores a bit vector for each "line" (or, "block") of memory, indicating its status relative to the caches.

Assume no cache has line A. Then in sequence: processor 1 wishes to read a value in line A, processor 2 wishes to write a value in line A, processor 3 wishes to read a value in line A. At the end of this sequence, what are the contents of the bit vector for line A.

Part d (5 points): One Pseudo-LRU replacement scheme for 4-way set-associative caches uses 3 additional bits for each set in the cache. What does each of the three bits specify?

first bit: LRU between way 0 and way 1 second bit: LRU between way 2 and way 3 third bit: LRU between first 2 groups

| Name: |  |

|-------|--|

|       |  |

# Problem 2 (10 points)

Assume IEEE-like floating point, except a data element contains 7 bits, rather than 32 or 64. We can represent the values 14 and 1/32 as 7 bit numbers.

Furthermore, we can multiply 14 times 1/32 with a MUL instruction, which yields the result 7/16 (as we would expect), or we can execute the for loop:

which yields the result 1/4. Why do we get 1/4 instead of the correct value 7/16?

Rounding

Your job: Complete the specification of the IEEE-like 7-bit floating point number:

1210 = 1.11 x 23

Exponent: 4

Fraction: 2

Excess (also called bias): 7

· 00001 = 1.0 x 2 - 5

3

2

1

0

4

Exponents

needed

-3

-4

-5

| Name: |  |

|-------|--|

|       |  |

|       |  |

# Problem 3 (15 points)

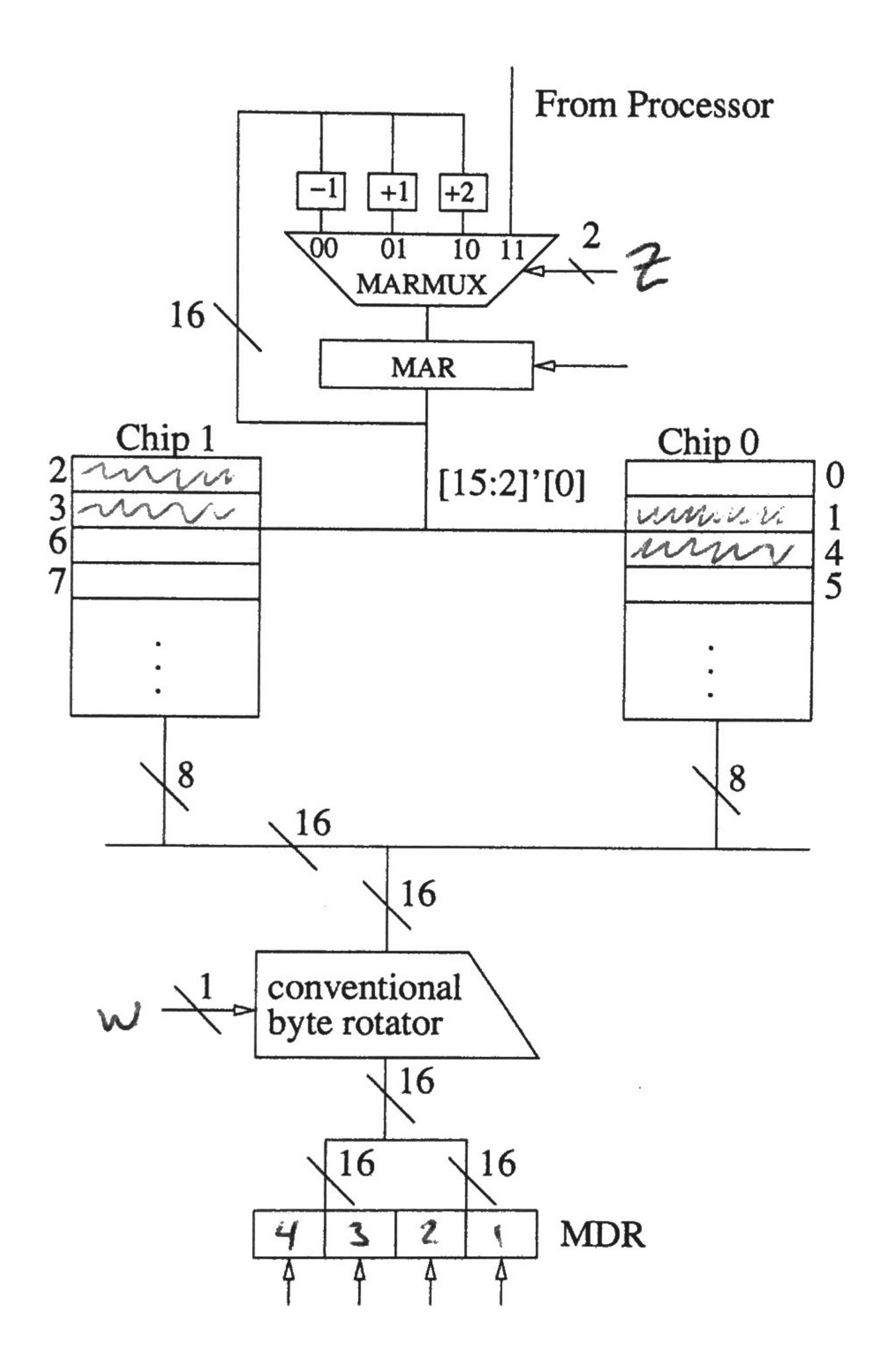

An Aggie messed up the wiring of an 8-bit addressable memory by leaving out bit 1 rather than bit 0, when he wired 15 bits of the MAR to the two memory chips. Instead of having chip 0 contain all even addresses and chip 1 contain all odd addresses, he ended up with what is shown below.

Your job is to implement the memory controller shown on the next page to support unaligned accesses of 32 bit loads.

Note: The conventional byte rotator simply takes a 16-bit vector and swaps the bytes.

Note: The MDR is a 32 bit register.

Note: The output of the byte rotator is simultaneous applied to both MDR[15:0] and MDR[31:16].

| Name:      |  |

|------------|--|

| I valific. |  |

#### Problem 3 continued

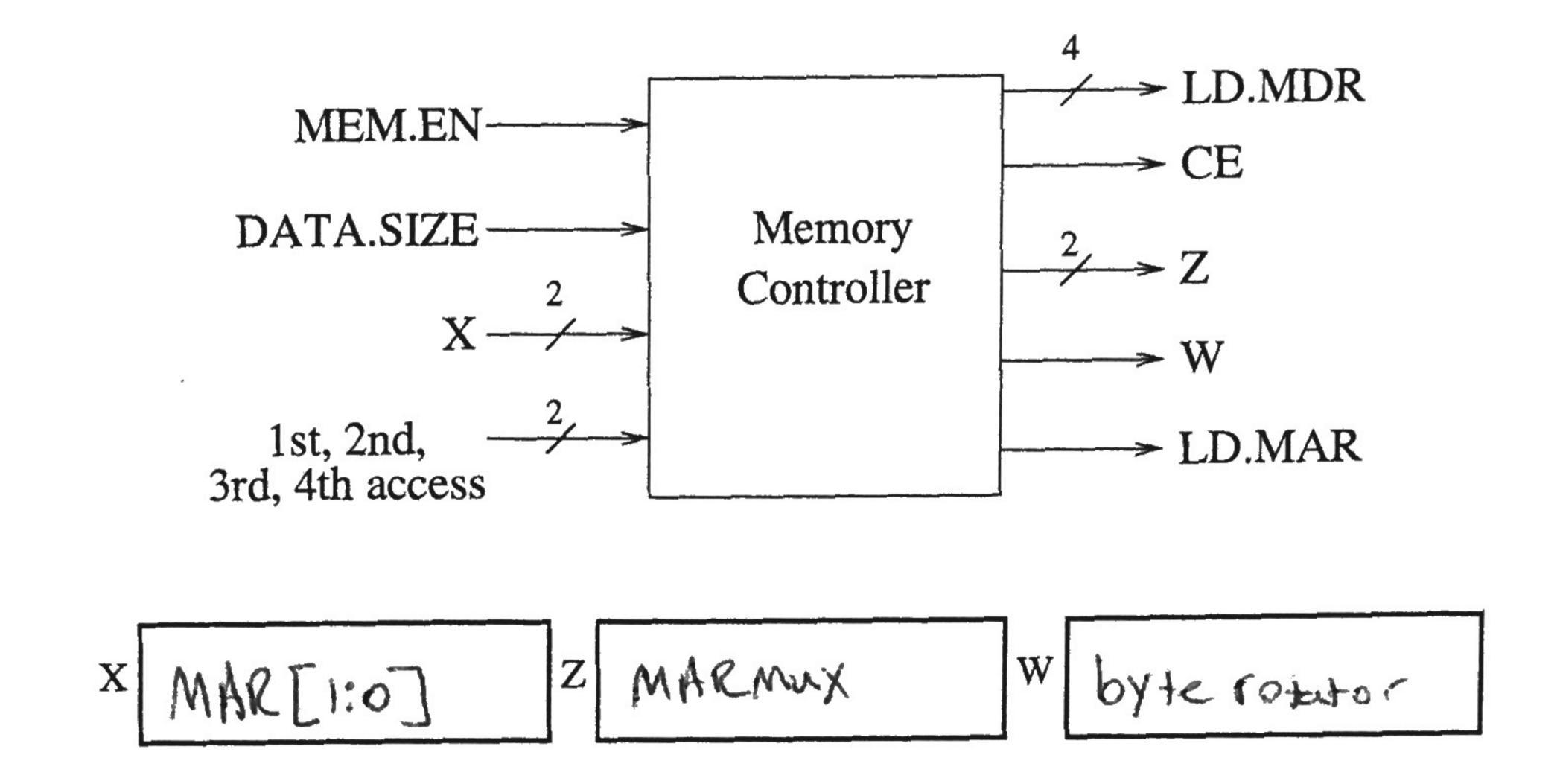

Part a: The memory controller shows a missing input (X) and two missing outputs (Z,W). Label them.

Part b: Given the byte rotator does a conventional byte rotate, what is the maximum number of bytes one can load into the MDR in each cycle.

Part c: For the case where data size is 32 bits, complete the truth table for the 4 input combinations labeled A, B, C, D:

|    | X  | 1st,2nd,3rd,4th access | LD.MDR3 | LD.MDR2 | LD.MDR1 | LD.MDR0    | Z1   | Z0   | W    |

|----|----|------------------------|---------|---------|---------|------------|------|------|------|

|    | 00 | 00                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 00 | 01                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 00 | 10                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 00 | 11                     | ****    | ****    | ****    | ****       | **** | **** | **** |

| A  | 01 | 00                     | 0       | (C)     |         |            | 0    | 0    | 0    |

| В  | 01 | 01                     | 0       | 0       |         | Ω          | 0    |      | 0    |

| СГ | 01 | 10                     | 0       |         | 0       | $\bigcirc$ | 0    |      | 1    |

| D  | 01 | 11                     |         | 0       | 0       | <b>Ç</b> > | 1    |      | 1    |

|    | 10 | . 00                   | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 10 | 01                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 10 | 10                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 10 | 11                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 11 | 00                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 11 | 01                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 11 | 10                     | ****    | ****    | ****    | ****       | **** | **** | **** |

|    | 11 | 11                     | ****    | ****    | ****    | ****       | **** | **** | **** |

| ame:               |      |

|--------------------|------|

| 4. P. 1917 P. 1917 |      |

|                    | ame: |

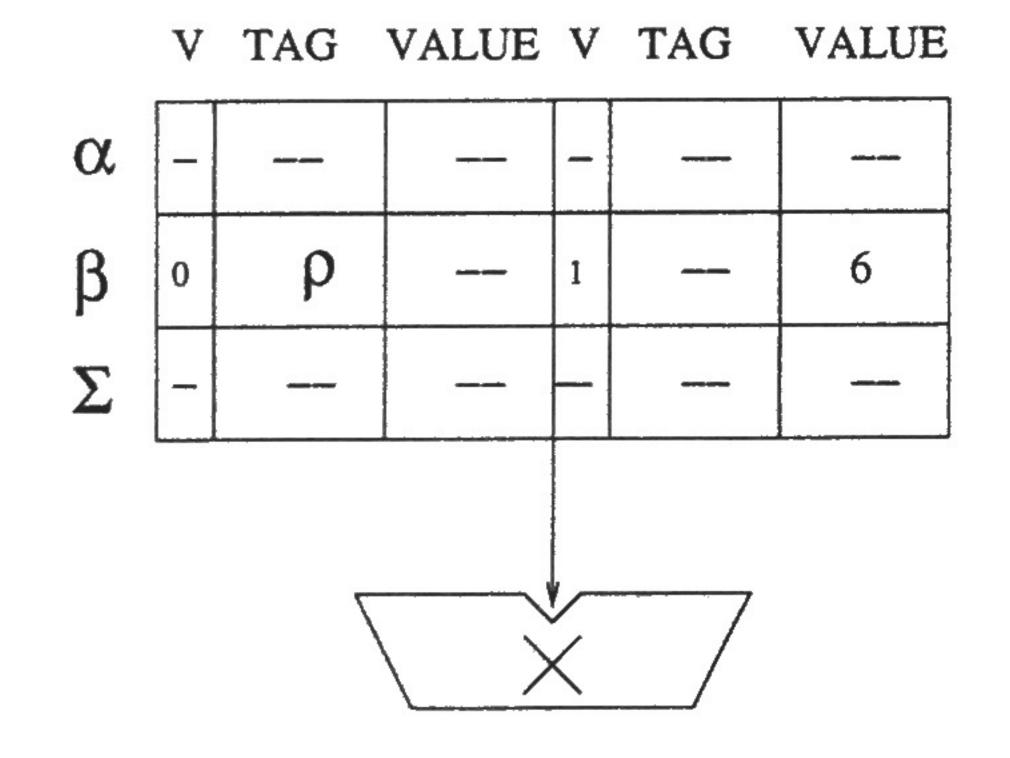

#### Problem 4 (20 points)

Assume a Tomasulo-style, out-of-order execution machine that handles ADD and MUL instructions. Instructions are of the form ADD Rx,Ry,Rz and MUL Rx,Ry,Rz, as discussed in class. Each instruction requires a fetch cycle, a decode cycle, some number of execution cycles, and a final cycle to store the result into a register and/or a reservation station entry waiting for that result. A result is available to subsequent instructions after it is stored in a register or reservation station entry.

Assume a program consists of four instructions. The first instruction is fetched in cycle 1.

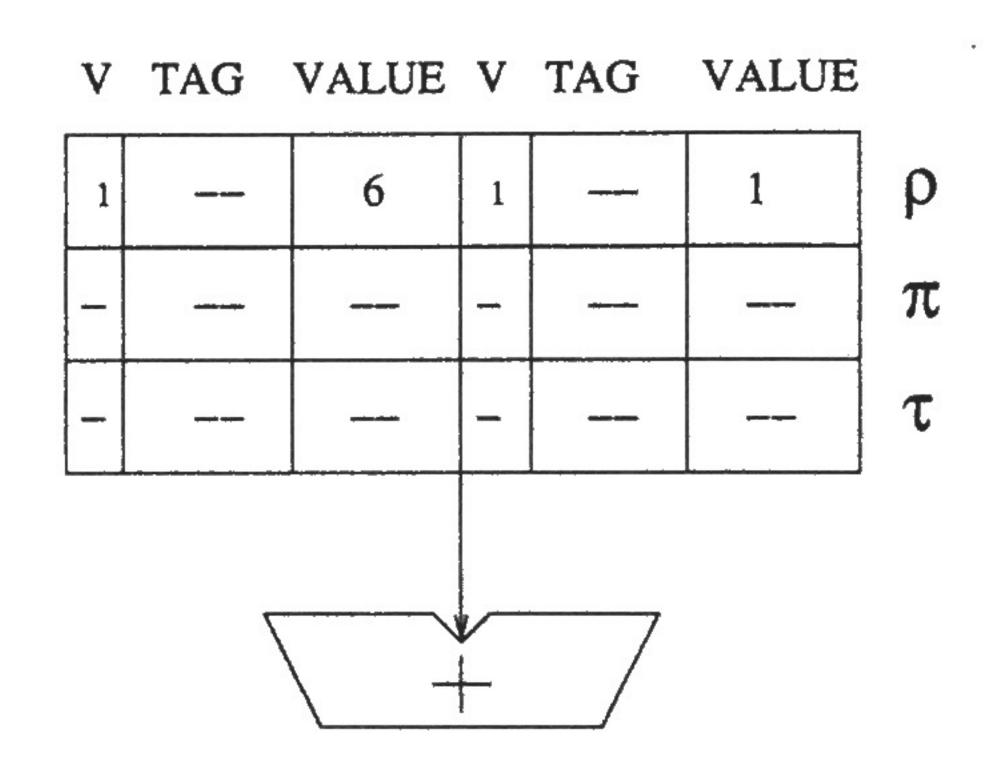

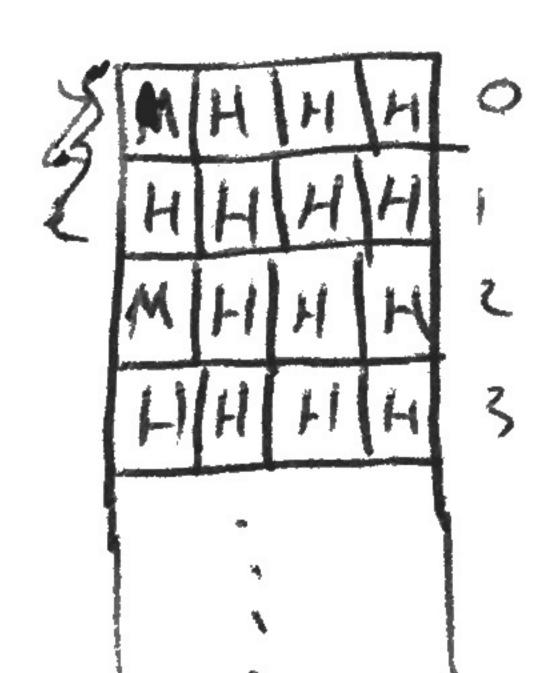

Shown below is a snapshot of the register file before cycle 1, the register file at the end of cycle x, and the reservation stations at the end of cycle x.

Reservation station entries are allocated in order, from top to bottom. That is, for example, the first MUL is allocated to the top reservation station entry associated with the mul functional unit, the second MUL with the second reservation station entry, etc. Each instruction remains in its reservation station until its result is stored in its destination register.

| R0 | 1 | - | 1 |

|----|---|---|---|

| R1 | 1 | _ | 2 |

| R2 | 1 | _ | 3 |

| R3 | 1 | _ | 4 |

Figure 1: Registers Before Cycle 1

| RO | 1 | - | 5 |

|----|---|---|---|

| R1 | 1 | _ | 2 |

| R2 | 1 |   | 3 |

| R3 | 0 | β | _ |

Figure 2: Registers After Cycle X

Figure 3: Reservation Stations after Cycle X

The machine has one add functional unit and one mul functional unit. Neither is pipelined. The timing diagram below indicates the cycles (with the letter E) that each functional unit is busy in the execution phase of an instruction.

|            | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| Adder      |   |   |   |   |   | E | E | E | E |    |    |    |    |    |    |    |

| Multiplier |   |   | E | Е | E | E |   |   |   |    | E  | E  | E  | E  |    |    |

| Name  |  |

|-------|--|

| Manne |  |

|       |  |

## **Problem 4 continued**

Part a (5 points): What is X (There are more than one correct answer. We are only asking for one of them)?

Part b (15 points): Complete the table by filling in the four instructions.

| Instruction | Opcode | DR    | SR1 | SR2 |

|-------------|--------|-------|-----|-----|

| I1          | Myl    | RO163 | 21  | 22  |

| I2          | ADD    | R9 7  | R36 | RO, |

| I3          | Mul    | 23    | RO  | R3  |

| I4          | ADD    | R0 5  | R1  | R2  |

|     |   | 2 1 | 3 1 | -1 | 5 | 6  |   | 2 |   | (0) |   | 12 | /3 | Ki | 15 |    |  |

|-----|---|-----|-----|----|---|----|---|---|---|-----|---|----|----|----|----|----|--|

| 0   | F | D   | E   | E  | E | E  | 5 |   |   |     |   |    |    |    | 13 | 16 |  |

| 3   |   | F   | D   |    |   |    |   | E | E | 5   |   |    |    |    |    |    |  |

| (3) |   |     | F   | 0  |   |    |   |   |   |     | E | E  | E  | E  | S  |    |  |

| (4) |   |     |     | F  | O | 1E | E | S |   |     |   |    |    |    |    |    |  |

|     | - | +   | +   | 1  |   |    |   |   | 1 |     |   |    |    |    |    | -  |  |

| Name: |

|-------|

|-------|

## Problem 5 (20 points)

Assume 16-bit physical address space, byte-addressible memory, and a 512 byte, 2-way set-associative, write-back cache with LRU replacement that allocates on a write-miss. Assume the cache is initially empty.

# Part a (10 points):

Suppose we execute the following code segment which copies an array A[256][4], whose starting address is x1000 into an array B[256][4], whose starting address is x2000. Each element in both arrays is one byte.

We note that the cache hit ratio for executing this code segment is 7/8.

Your job: Determine the cache parameters:

Block Size:

No. of Sets:

Tag Size:

Tag store size:

Part b (10 points)

Suppose instead, we execute the following code segment, starting with the same empty cache.

What is the cache hit ratio this time?

| Name: |

|-------|

|       |

## Problem 6 (20 points)

We wish to enhance the LC-3b by adding virtual memory and a new instruction, Load Indirect (LDI). Our virtual memory scheme will follow the VAX scheme which you have already studied. LDI will use the unused opcode 1011, and have the following format:

|     | 15  | 12  | 11 | 9 | 8  | 6 | , 5 |         |   | 0 |

|-----|-----|-----|----|---|----|---|-----|---------|---|---|

| LDI | 1 0 | 1 1 | D  | R | BR | ? | 1   | offset6 | 1 |   |

LDI operates as follows: A virtual address (call it A) is computed by adding the sign-extended offset to the contents of the register specified by BR. The contents of A is a virtual address B. The contents of B are loaded into the register specified by DR.

(If you took EE306, you studied the LDI instruction. Note, however, that the LDI instruction in EE306 computed the address A differently than is shown here.)

The virtual memory model is as follows: Virtual addresses are 16 bits. Physical addresses are 12 bits. Frame size is 64 bytes. Memory is partitioned into system space (x0000 to x7FFF) and user space (x8000 to xFFFF). Each PTE is 2 bytes and has the format

|     | 15 |     | 5  | 0  |

|-----|----|-----|----|----|

| PTE | V  | 000 | PI | FN |

### Problem 6 continued

Assume the state of the machine before this instruction is executed includes:

R0: x9500 R1: xA400 PC: x8200

1011,000 00100000

To process LDI R0,R1,#0, seven physical memory accesses are needed. The table below shows the VA, PA, Data, and whether or not there was a TLB hit for each of these seven physical memory accesses in the order they occurred.

Your job: Complete the table and fill in the additional two boxes. You can assume no page faults occur in the processing of the LDI instruction.

|                 | 1000,00000,0     | 901100 | e e     |

|-----------------|------------------|--------|---------|

| Virtual Address | Physical Address | Data   | TLB Hit |

| N/A             | x978             | 8012   | No      |

| x2F10           | x490             | 8018   | 20      |

| x8200           | x600             | x 8040 | てつ      |

| x A 4 00        | XZOO             | X COTE | Yes     |

| N/A             | 988              | x8006  | ての      |

| x3102           | x 182            | x801A  | でる      |

| xC07E           | 6BF              | xC07E  | 20      |

0110,10 11,1110 6BF

SBR: 1800 1000 00,10 0000 0000 008 +2 019 2 Foo 0010

| N | ame: |  |

|---|------|--|

|   |      |  |

|   |      |  |

## Problem 7 (25 points):

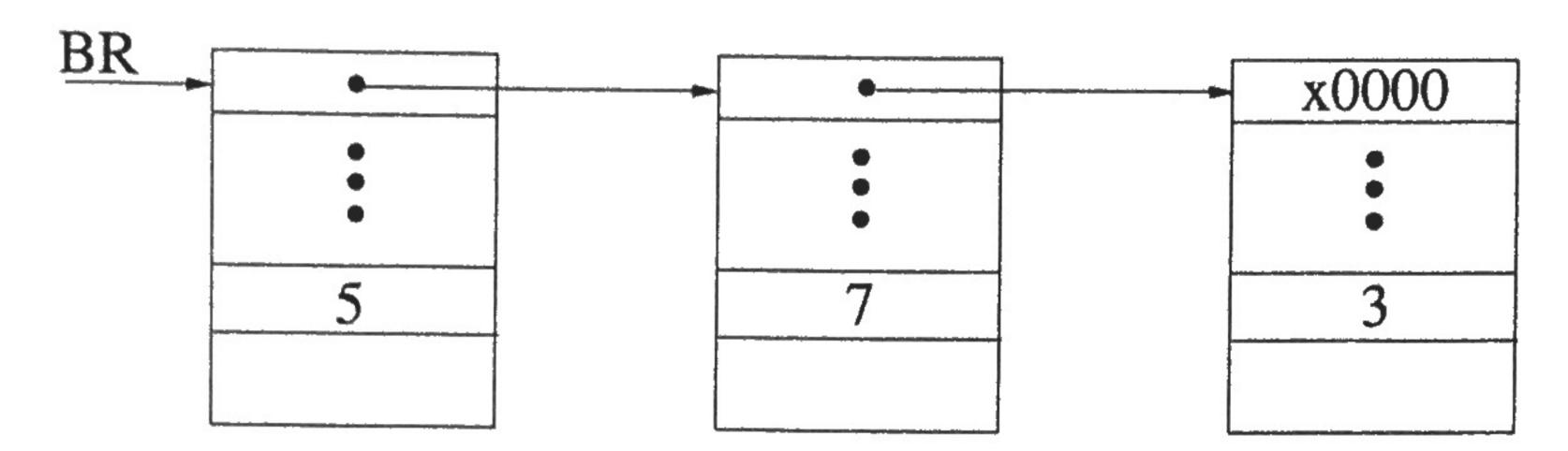

The linked list is a useful data structure that connects nodes, each of which is a record consisting of values for a number of parameters. Usually, the first word in a node is a pointer to the next node. The first word of the last node is usually x0000 (the null pointer).

It is common to traverse a linked list searching for a particular value for a particular parameter. A useful instruction to accomplish this could be added to the LC-3b ISA. Call it LinkedListSearch (LLS), which uses opcode 1010, and has the following format:

|     | 15  |  |     | 12 | 11 | 9 | , 8 | 6  | , 5     | 0 |  |

|-----|-----|--|-----|----|----|---|-----|----|---------|---|--|

| LLS | 1 0 |  | 1 0 |    | CR |   |     | BR | Offset6 |   |  |

CR contains the value one is searching for. BR contains a pointer to the first node in the linked list. offset is the offset from the starting address of a node where the value of the parameter being queried is contained. LLS operates as follows:

```

while (BR != 0) {

if (CR == M[BR + Offset6])

return

else

BR = M[BR]

}

```

After LLS executes, BR contains the address of the first node that contains the value we are looking for, or it will contain x0000, the null pointer signifying that no node contained that value.

Note that LLS modifies condition codes to an undefined state.

| Name |  |

|------|--|

|      |  |

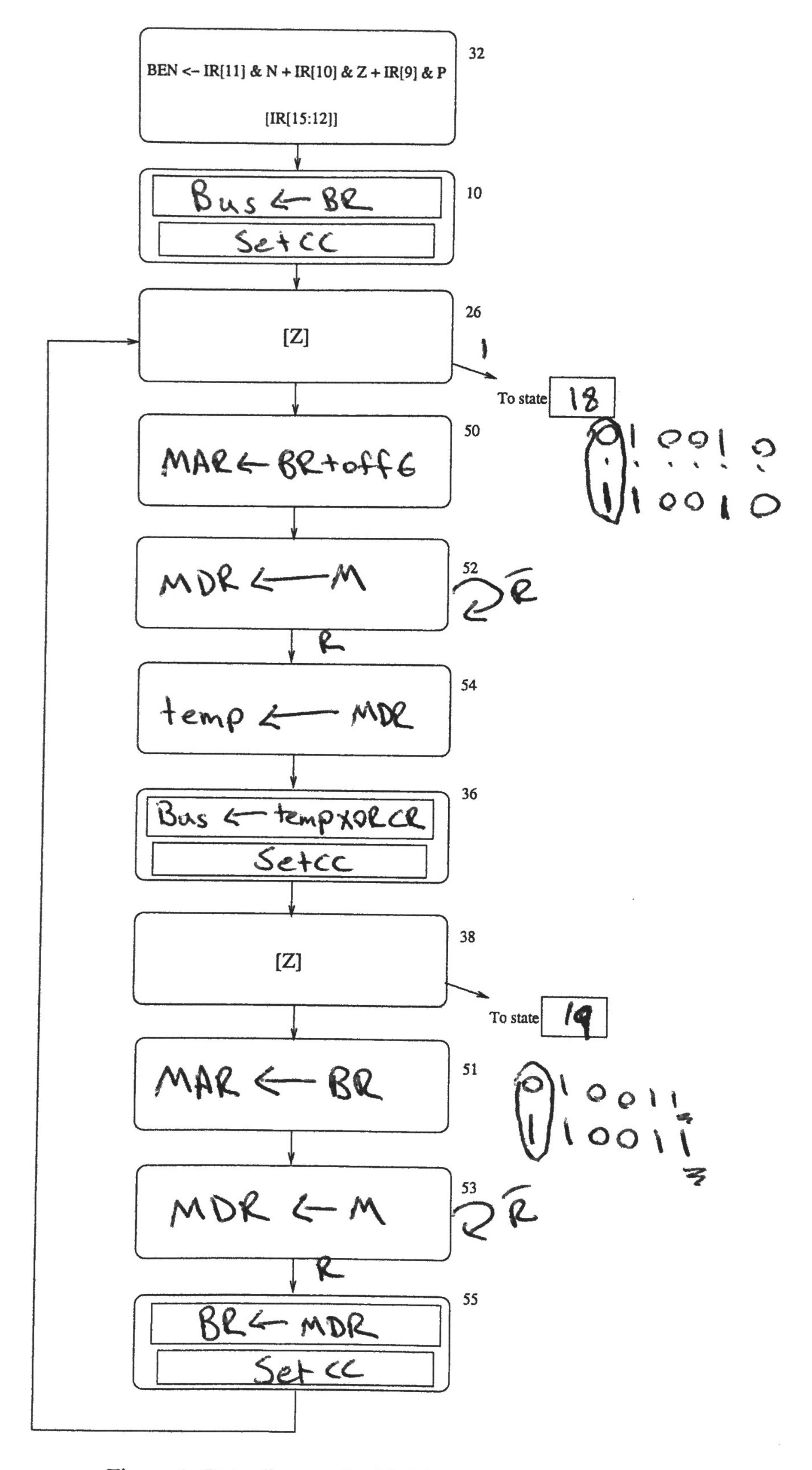

## Problem 7 continued:

Part a: Complete the state machine for this instruction.

Figure 4: State diagram for LLS instruction

#### Problem 7 continued:

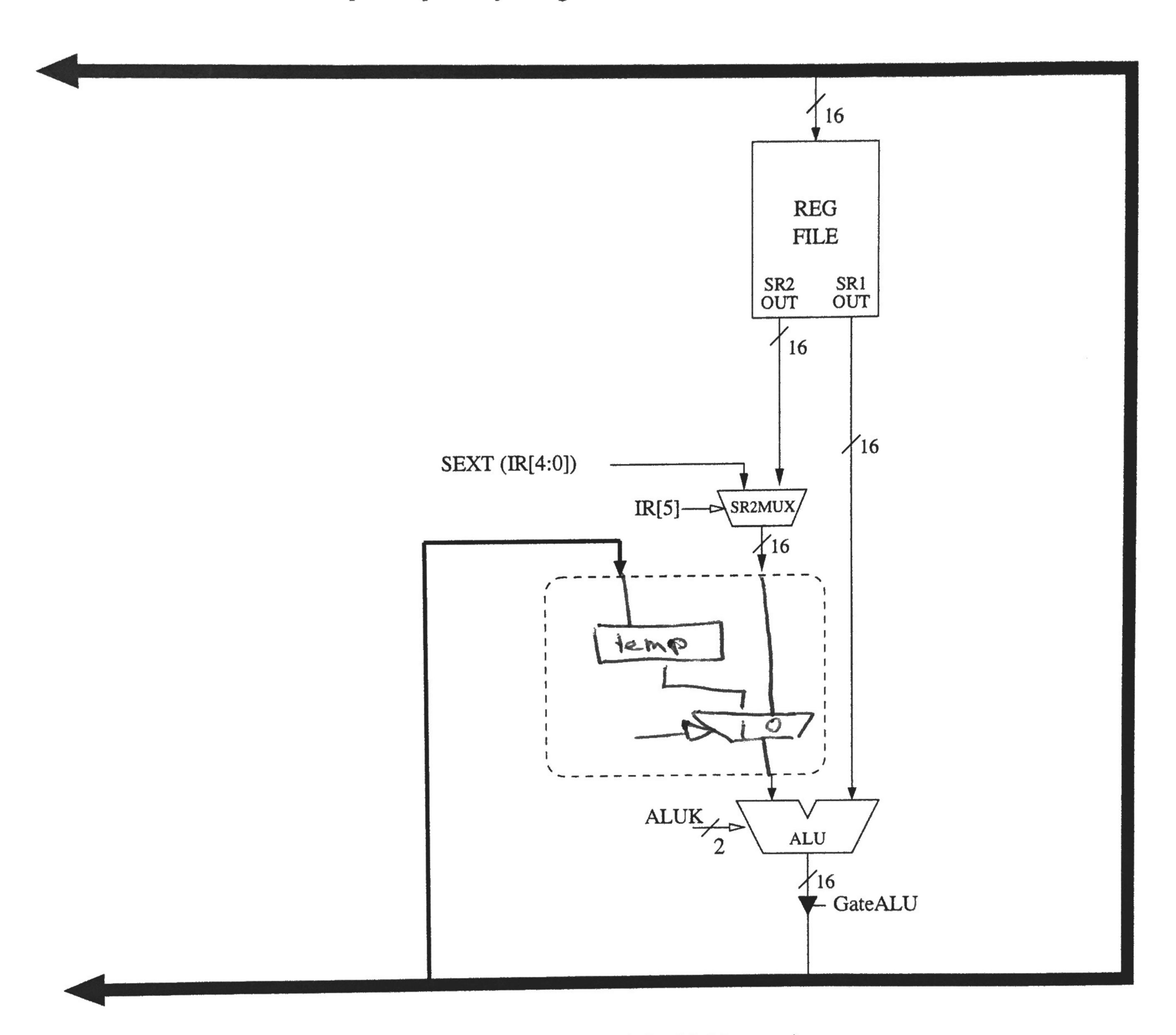

Part b: Add the additional data path required by filling in the dashed box.

Figure 5: Modified Datapath for LLS instruction

# Problem 7 continued:

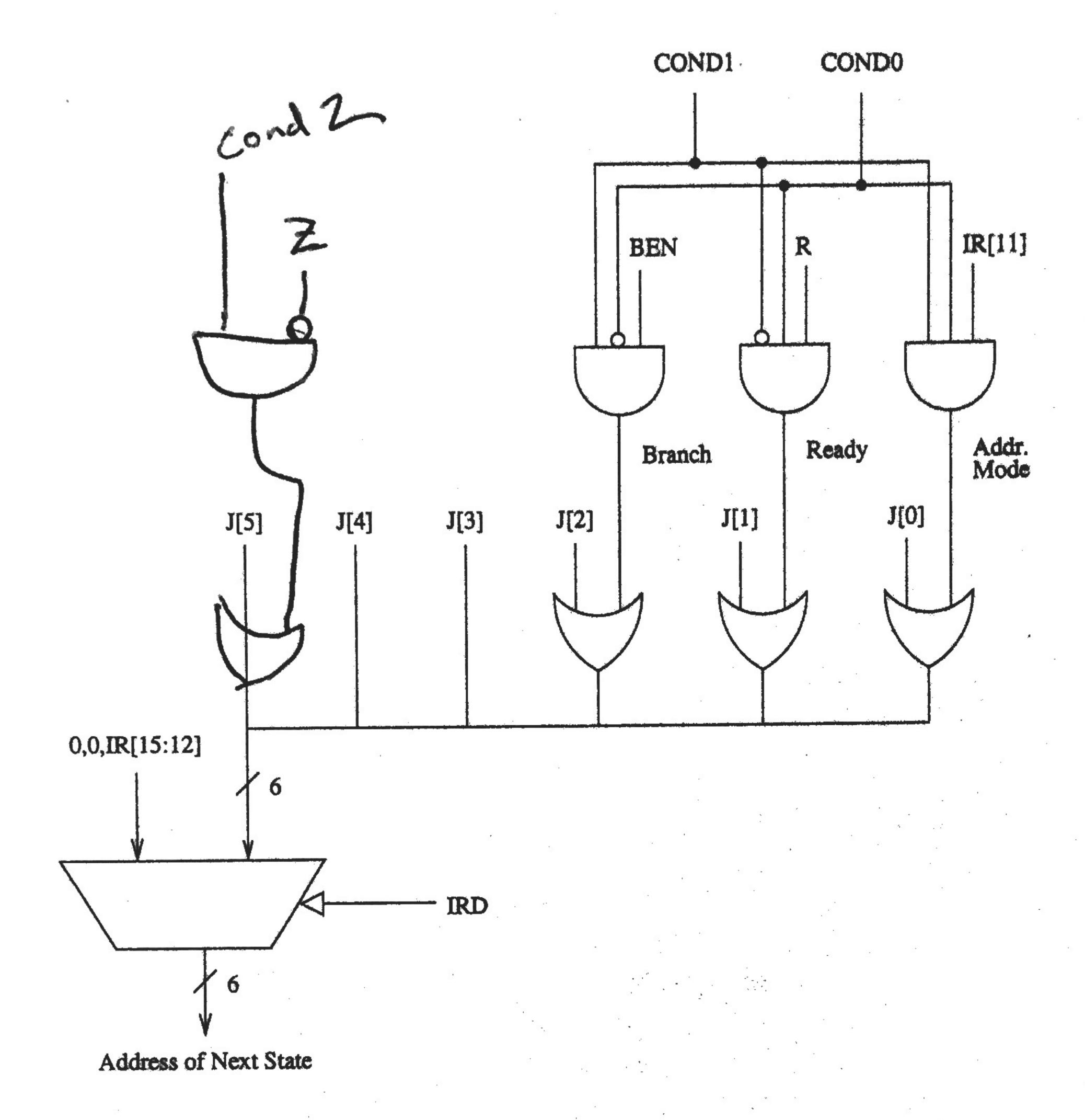

Part c: Modify the microsequencer as necessary.