Appendix

T. TM4C123 I/O Registers

Jonathan

Valvano and Mark McDermott

This chapter describes the TM4C123 I/O registers used in this book. It is not intended to replace the TM4C123 data sheet, but to serve as a quick reference for the specific registers used in this class.

Table of Contents:

- T.0. Nested Vectored Interrupt Controller (NVIC)

- T.1. GPIO and NVIC Programming

- T.2. ADC Programming

- T.3. Periodic Timer Interrupts

- T.4. UART

- T.5. Synchronous Transmission and Receiving using the SSI

- T.6. Inter-Integrated Circuit (I2C) Interface

- T.7. Edge-triggered Interrupts

- T.8. Pulse Width Modulation

- T.9. Input Capture

- T.10. Controller Area Network (CAN)

T.0. Nested Vectored Interrupt Controller (NVIC)

On the ARM Cortex-M microcontrollers, exceptions include resets, software interrupts and hardware interrupts. Interrupts on the Cortex-M are controlled by the Nested Vectored Interrupt Controller (NVIC). Each exception has an associated 32-bit vector that points to the interrupt service routine (ISR> that handles the exception. Vectors are stored in ROM at the beginning of memory. Program T.0.1 shows the first few vectors as defined in the Startup.s file. DCD is an assembler pseudo-op that defines a 32-bit constant. ROM location 0x00000000 has the initial stack pointer, and location 0x00000004 contains the initial program counter, which is called the reset vector. It points to a function called the reset handler, which is the first software executed following reset. There are up to 240 possible interrupt sources and their 32-bit vectors are listed in order starting with location 0x00000008. From a programming perspective, we can attach ISRs to interrupts by writing the ISRs as regular assembly subroutines or C functions with no input or output parameters and editing the Startup.s file to specify those functions for the appropriate interrupt. For example, if we wrote a Port F interrupt service routine named PortFISR, then we would replace GPIOPortF_Handler with PortFISR. In this book, we will define our ISRs using standard function names so that the Startup.s file need not be edited. I.e., we will simply name the ISR for edge-triggered interrupts on Port F as GPIOPortF_Handler. The ISR for this interrupt is a 32-bit pointer located at ROM address 0x000000B8. Because the vectors are in ROM, this linkage is defined at compile time and not at run time. For more details see the Startup.s files within the examples posted on the book web site.

: Where is the vector for SysTick? What is the standard name for this ISR?

EXPORT __Vectors

__Vectors ; address ISR

DCD StackMem + Stack ; 0x00000000 Top of Stack

DCD Reset_Handler ; 0x00000004 Reset Handler

DCD NMI_Handler ; 0x00000008 NMI Handler

DCD HardFault_Handler ; 0x0000000C Hard Fault Handler

DCD MemManage_Handler ; 0x00000010 MPU Fault Handler

DCD BusFault_Handler ; 0x00000014 Bus Fault Handler

DCD UsageFault_Handler ; 0x00000018 Usage Fault Handler

DCD 0 ; 0x0000001C Reserved

DCD 0 ; 0x00000020 Reserved

DCD 0 ; 0x00000024 Reserved

DCD 0 ; 0x00000028 Reserved

DCD SVC_Handler ; 0x0000002C SVCall Handler

DCD DebugMon_Handler ; 0x00000030 Debug Monitor Handler

DCD 0 ; 0x00000034 Reserved

DCD PendSV_Handler ; 0x00000038 PendSV Handler

DCD SysTick_Handler ; 0x0000003C SysTick Handler

DCD GPIOPortA_Handler ; 0x00000040 GPIO Port A

DCD GPIOPortB_Handler ; 0x00000044 GPIO Port B

DCD GPIOPortC_Handler ; 0x00000048 GPIO Port C

DCD GPIOPortD_Handler ; 0x0000004C GPIO Port D

DCD GPIOPortE_Handler ; 0x00000050 GPIO Port E

DCD UART0_Handler ; 0x00000054 UART0

DCD UART1_Handler ; 0x00000058 UART1

DCD SSI0_Handler ; 0x0000005C SSI

DCD I2C0_Handler ; 0x00000060 I2C

DCD PWM0Fault_Handler ; 0x00000064 PWM Fault

DCD PWM0Generator0_Handler ; 0x00000068 PWM 0 Generator 0

DCD PWM0Generator1_Handler ; 0x0000006C PWM 0 Generator 1

DCD PWM0Generator2_Handler ; 0x00000070 PWM 0 Generator 2

DCD Quadrature0_Handler ; 0x00000074 Quadrature Encoder 0

DCD ADC0Seq0_Handler ; 0x00000078 ADC0 Sequence 0

DCD ADC0Seq1_Handler ; 0x0000007C ADC0 Sequence 1

DCD ADC0Seq2_Handler ; 0x00000080 ADC0 Sequence 2

DCD ADC0Seq3_Handler ; 0x00000084 ADC0 Sequence 3

DCD WDT_Handler ; 0x00000088 Watchdog

DCD Timer0A_Handler ; 0x0000008C Timer 0 subtimer A

DCD Timer0B_Handler ; 0x00000090 Timer 0 subtimer B

DCD Timer1A_Handler ; 0x00000094 Timer 1 subtimer A

DCD Timer1B_Handler ; 0x00000098 Timer 1 subtimer B

DCD Timer2A_Handler ; 0x0000009C Timer 2 subtimer A

DCD Timer2B_Handler ; 0x000000A0 Timer 2 subtimer B

DCD Comp0_Handler ; 0x000000A4 Analog Comp 0

DCD Comp1_Handler ; 0x000000A8 Analog Comp 1

DCD Comp2_Handler ; 0x000000AC Analog Comp 2

DCD SysCtl_Handler ; 0x000000B0 System Control

DCD FlashCtl_Handler ; 0x000000B4 Flash Control

DCD GPIOPortF_Handler ; 0x000000B8 GPIO Port F

Program T.0.1. Software syntax to set the interrupt vectors for the TM4C (only some vectors are shown, see the startup.s file for a complete list).

Program T.0.2 shows that the syntax for an ISR looks like a function with no parameters. Notice that each ISR (except for SysTick) must acknowledge the interrupt in software by clearing the flag that caused the interrupt. In Program T.0.2, we assume the interrupt was caused by an edge on PF4, so writing to the ICR register will clear trigger flag 4.

void GPIOPortF_Handler(void){

GPIO_PORTF_ICR_R = 0x10; // ack, clear interrupt flag4

// stuff

}

Program T.0.2. Typical interrupt service routine.

|

Vector address |

Number |

IRQ |

ISR name in Startup.s |

NVIC |

Priority bits |

|

0x00000038 |

14 |

-2 |

PendSV_Handler |

NVIC_SYS_PRI3_R |

23 – 21 |

|

0x0000003C |

15 |

-1 |

SysTick_Handler |

NVIC_SYS_PRI3_R |

31 – 29 |

|

0x00000040 |

16 |

0 |

GPIOPortA_Handler |

NVIC_PRI0_R |

7 – 5 |

|

0x00000044 |

17 |

1 |

GPIOPortB_Handler |

NVIC_PRI0_R |

15 – 13 |

|

0x00000048 |

18 |

2 |

GPIOPortC_Handler |

NVIC_PRI0_R |

23 – 21 |

|

0x0000004C |

19 |

3 |

GPIOPortD_Handler |

NVIC_PRI0_R |

31 – 29 |

|

0x00000050 |

20 |

4 |

GPIOPortE_Handler |

NVIC_PRI1_R |

7 – 5 |

|

0x00000054 |

21 |

5 |

UART0_Handler |

NVIC_PRI1_R |

15 – 13 |

|

0x00000058 |

22 |

6 |

UART1_Handler |

NVIC_PRI1_R |

23 – 21 |

|

0x0000005C |

23 |

7 |

SSI0_Handler |

NVIC_PRI1_R |

31 – 29 |

|

0x00000060 |

24 |

8 |

I2C0_Handler |

NVIC_PRI2_R |

7 – 5 |

|

0x00000064 |

25 |

9 |

PWM0Fault_Handler |

NVIC_PRI2_R |

15 – 13 |

|

0x00000068 |

26 |

10 |

PWM0_Handler |

NVIC_PRI2_R |

23 – 21 |

|

0x0000006C |

27 |

11 |

PWM1_Handler |

NVIC_PRI2_R |

31 – 29 |

|

0x00000070 |

28 |

12 |

PWM2_Handler |

NVIC_PRI3_R |

7 – 5 |

|

0x00000074 |

29 |

13 |

Quadrature0_Handler |

NVIC_PRI3_R |

15 – 13 |

|

0x00000078 |

30 |

14 |

ADC0_Handler |

NVIC_PRI3_R |

23 – 21 |

|

0x0000007C |

31 |

15 |

ADC1_Handler |

NVIC_PRI3_R |

31 – 29 |

|

0x00000080 |

32 |

16 |

ADC2_Handler |

NVIC_PRI4_R |

7 – 5 |

|

0x00000084 |

33 |

17 |

ADC3_Handler |

NVIC_PRI4_R |

15 – 13 |

|

0x00000088 |

34 |

18 |

WDT_Handler |

NVIC_PRI4_R |

23 – 21 |

|

0x0000008C |

35 |

19 |

Timer0A_Handler |

NVIC_PRI4_R |

31 – 29 |

|

0x00000090 |

36 |

20 |

Timer0B_Handler |

NVIC_PRI5_R |

7 – 5 |

|

0x00000094 |

37 |

21 |

Timer1A_Handler |

NVIC_PRI5_R |

15 – 13 |

|

0x00000098 |

38 |

22 |

Timer1B_Handler |

NVIC_PRI5_R |

23 – 21 |

|

0x0000009C |

39 |

23 |

Timer2A_Handler |

NVIC_PRI5_R |

31 – 29 |

|

0x000000A0 |

40 |

24 |

Timer2B_Handler |

NVIC_PRI6_R |

7 – 5 |

|

0x000000A4 |

41 |

25 |

Comp0_Handler |

NVIC_PRI6_R |

15 – 13 |

|

0x000000A8 |

42 |

26 |

Comp1_Handler |

NVIC_PRI6_R |

23 – 21 |

|

0x000000AC |

43 |

27 |

Comp2_Handler |

NVIC_PRI6_R |

31 – 29 |

|

0x000000B0 |

44 |

28 |

SysCtl_Handler |

NVIC_PRI7_R |

7 – 5 |

|

0x000000B4 |

45 |

29 |

FlashCtl_Handler |

NVIC_PRI7_R |

15 – 13 |

|

0x000000B8 |

46 |

30 |

GPIOPortF_Handler |

NVIC_PRI7_R |

23 – 21 |

|

0x000000BC |

47 |

31 |

GPIOPortG_Handler |

NVIC_PRI7_R |

31 – 29 |

|

0x000000C0 |

48 |

32 |

GPIOPortH_Handler |

NVIC_PRI8_R |

7 – 5 |

|

0x000000C4 |

49 |

33 |

UART2_Handler |

NVIC_PRI8_R |

15 – 13 |

|

0x000000C8 |

50 |

34 |

SSI1_Handler |

NVIC_PRI8_R |

23 – 21 |

|

0x000000CC |

51 |

35 |

Timer3A_Handler |

NVIC_PRI8_R |

31 – 29 |

|

0x000000D0 |

52 |

36 |

Timer3B_Handler |

NVIC_PRI9_R |

7 – 5 |

|

0x000000D4 |

53 |

37 |

I2C1_Handler |

NVIC_PRI9_R |

15 – 13 |

|

0x000000D8 |

54 |

38 |

Quadrature1_Handler |

NVIC_PRI9_R |

23 – 21 |

|

0x000000DC |

55 |

39 |

CAN0_Handler |

NVIC_PRI9_R |

31 – 29 |

|

0x000000E0 |

56 |

40 |

CAN1_Handler |

NVIC_PRI10_R |

7 – 5 |

|

0x000000E4 |

57 |

41 |

CAN2_Handler |

NVIC_PRI10_R |

15 – 13 |

|

0x000000E8 |

58 |

42 |

Ethernet_Handler |

NVIC_PRI10_R |

23 – 21 |

|

0x000000EC |

59 |

43 |

Hibernate_Handler |

NVIC_PRI10_R |

31 – 29 |

|

0x000000F0 |

60 |

44 |

USB0_Handler |

NVIC_PRI11_R |

7 – 5 |

|

0x000000F4 |

61 |

45 |

PWM3_Handler |

NVIC_PRI11_R |

15 – 13 |

|

0x000000F8 |

62 |

46 |

uDMA_Handler |

NVIC_PRI11_R |

23 – 21 |

|

0x000000FC |

63 |

47 |

uDMA_Error |

NVIC_PRI11_R |

31 – 29 |

Table T.0.1. Some of the interrupt vectors for the TM4C. The TM4C123 has over 100 possible interrupt sources.

To activate an interrupt source we need to set its priority and enable that source in the NVIC. This activation is in addition to the arm and enable steps. Table T.0.1 lists some of the interrupt sources available on the TM4C family of microcontrollers. Interrupt numbers 0 to 15 contain the faults, software interrupt and SysTick; these interrupts will be handled differently from interrupts 16 and up.

Table T.0.2 shows some of the priority registers on the NVIC. Each register contains an 8-bit priority field for four devices. On the TM4C microcontrollers, only the top three bits of the 8-bit field are used. This allows us to specify the interrupt priority level for each device from 0 to 7, with 0 being the highest priority. The interrupt number (number column in Table T.0.1) is loaded into the IPSR register. The servicing of interrupts does not set the I bit in the PRIMASK, so a higher priority interrupt can suspend the execution of a lower priority ISR. If a request of equal or lower priority is generated while an ISR is being executed, that request is postponed until the ISR is completed. In particular, those devices that need prompt service should be given high priority.

|

Address |

31 – 29 |

23 – 21 |

15 – 13 |

7 – 5 |

Name |

|

0xE000E400 |

GPIO Port D |

GPIO Port C |

GPIO Port B |

GPIO Port A |

NVIC_PRI0_R |

|

0xE000E404 |

SSI0, Rx Tx |

UART1, Rx Tx |

UART0, Rx Tx |

GPIO Port E |

NVIC_PRI1_R |

|

0xE000E408 |

PWM Gen 1 |

PWM Gen 0 |

PWM Fault |

I2C0 |

NVIC_PRI2_R |

|

0xE000E40C |

ADC Seq 1 |

ADC Seq 0 |

Quad Encoder |

PWM Gen 2 |

NVIC_PRI3_R |

|

0xE000E410 |

Timer 0A |

Watchdog |

ADC Seq 3 |

ADC Seq 2 |

NVIC_PRI4_R |

|

0xE000E414 |

Timer 2A |

Timer 1B |

Timer 1A |

Timer 0B |

NVIC_PRI5_R |

|

0xE000E418 |

Comp 2 |

Comp 1 |

Comp 0 |

Timer 2B |

NVIC_PRI6_R |

|

0xE000E41C |

GPIO Port G |

GPIO Port F |

Flash Control |

System Control |

NVIC_PRI7_R |

|

0xE000E420 |

Timer 3A |

SSI1, Rx Tx |

UART2, Rx Tx |

GPIO Port H |

NVIC_PRI8_R |

|

0xE000E424 |

CAN0 |

Quad Encoder 1 |

I2C1 |

Timer 3B |

NVIC_PRI9_R |

|

0xE000E428 |

Hibernate |

Ethernet |

CAN2 |

CAN1 |

NVIC_PRI10_R |

|

0xE000E42C |

uDMA Error |

uDMA Soft Tfr |

PWM Gen 3 |

USB0 |

NVIC_PRI11_R |

|

0xE000ED20 |

SysTick |

PendSV |

-- |

Debug |

NVIC_SYS_PRI3_R |

Table T.0.2. The TM4C NVIC registers. Each register is 32 bits wide. Bits not shown are zero.

: Where are the priority bits for SysTick?

: Where are the priority bits for Timer 1A?

There are five enable registers NVIC_EN0_R through NVIC_EN4_R. The 32 bits in register NVIC_EN0_R control the IRQ numbers 0 to 31 (interrupt numbers 16 – 47). In Table T.0.1 we see UART0 is IRQ=5. To enable UART0 interrupts we set bit 5 in NVIC_EN0_R, see Table T.0.3. The 32 bits in NVIC_EN1_R control the IRQ numbers 32 to 63 (interrupt numbers 48 – 79). Not every interrupt source is available on every TM4C microcontroller, so you will need to refer to the data sheet for your microcontroller when designing I/O interfaces. Writing zeros to the NVIC_EN0_R through NVIC_EN4_R registers has no effect. To disable interrupts we write ones to the corresponding bit in the NVIC_DIS0_R through NVIC_DIS4_R register.

|

Address |

31 |

30 |

… |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

Name |

|

0xE000E100 |

G |

F |

… |

UART1 |

UART0 |

E |

D |

C |

B |

A |

NVIC_EN0_R |

|

0xE000E104 |

|

|

… |

Quad1 |

I2C1 |

Timer3B |

Timer3A |

SSI1 |

UART2 |

H |

NVIC_EN1_R |

|

0xE000E180 |

G |

F |

… |

UART1 |

UART0 |

E |

D |

C |

B |

A |

NVIC_DIS0_R |

|

0xE000E184 |

|

|

… |

Quad1 |

I2C1 |

Timer3B |

Timer3A |

SSI1 |

UART2 |

H |

NVIC_DIS1_R |

Table T.0.3. Some of the TM4C NVIC interrupt enable registers. There are five such registers defining 139 interrupt enable bits.

: Where is the enable bit for UART2?

We can locate the enable bit for any interrupt using formulas. There are 32 enable bits in each register, so first we divide the IRQ number by 32. The modulus gives us the bit number. Let n be the IRQ number, from Table T.0.1.

x = n/32

m = n%32

The enable bit for interrupt IRQ=n is bit m of register NVIC_ENx_R. For example, Timer3A is IRQ=35, x=1, m=3. So, the enable bit for Timer3A is bit 3 of NVIC_EN1_R.

: Where is the enable bit for Timer 5A, IRQ=92?

Similarly, we can locate the priority bits for any interrupt using formulas. There are 4 sets of priority bits in each register, so first we divide the IRQ number by 4. The modulus helps us identify which bits are priority. Let n be the IRQ number, from Table T.0.1.

y = n/4

p = n%4

The priority bits for interrupt IRQ=n are bits 8*p+7, 8*p+6, 8*p+5 of register NVIC_PRIy_R. For example, Timer3A is IRQ=35, y=8, m=3. So, the priority bits for Timer3A are bits 31-29 of NVIC_PRI8_R.

: Where are the priority bits for Timer 4A, IRQ=70?

Interactive tool T.0.1 shows the context switch from executing in the foreground to running a periodic SysTick ISR. Before the interrupt occurs, the I bit in the PRIMASK is 0 signifying interrupts are enabled, and the interrupt number (ISRNUM) in the IPSR register is 0, meaning we are running in Thread mode (i.e., the main program, and not an ISR). Handler mode is signified by a nonzero value in IPSR. When BASEPRI register is zero, all interrupts are allowed and the BASEPRI register is not active.

When the SysTick counter goes from 1 to 0, the Count flag in the NVIC_ST_CTRL_R register is set, triggering an interrupt. The current instruction is finished. (a) Eight registers are pushed on the stack with R0 on top. These registers are pushed onto the stack . (b) The vector address is loaded into the PC (“Vector address” column in Table T.0.1). (c) The IPSR register is set to 15 (“Number” column in Table 12.1) (d) The top 24 bits of LR are set to 0xFFFFFF, signifying the processor is executing an ISR. The bottom eight bits specify how to return from interrupt.

0xE1 Return to Handler mode MSP (using floating point state on TM4C)

0xE9 Return to Thread mode MSP (using floating point state on TM4C)

0xED Return to Thread mode PSP (using floating point state on TM4C)

0xF1 Return to Handler mode MSP

0xF9 Return to Thread mode MSP ← in this class we will always be using this one

0xFD Return to Thread mode PSP

After pushing the registers, the processor always uses the main stack pointer (MSP) during the execution of the ISR. Events 2, 3, and 4 can occur simultaneously

Use the following tool to see the steps involved in a context switch from the executing the foreground thread to switching to the background thread (ISR) when a GPIOPortC_Handler interrupt occurs.

Click Start to start the context switch by pushing the current registers into the stack.

To return

from an interrupt, the ISR

executes the typical function return BX LR.

However, since the top 24 bits of LR

are 0xFFFFFF, it knows to return from interrupt by popping the eight

registers off the stack. Since the bottom eight bits of LR

in this case are 0b11111001, it returns to thread mode using the MSP

as its stack pointer. Since the IPSR

is part of the PSR

that is popped, it is automatically reset its previous state.

A nested interrupt occurs when a higher priority interrupt suspends an ISR. The lower priority interrupt will finish after the higher priority ISR completes. When one interrupt preempts another, the LR is set to 0xFFFFFFF1, so it knows to return to handler mode. Tail chaining occurs when one ISR executes immediately after another. Optimization occurs because the eight registers need not be popped only to be pushed once again. If an interrupt is triggered and is in the process of stacking registers when a higher priority interrupt is requested, this late arrival interrupt will be executed first.

Priority determines the order of service when two or more requests are made simultaneously. Priority also allows a higher priority request to suspend a lower priority request currently being processed. Usually, if two requests have the same priority, we do not allow them to interrupt each other. NVIC assigns a priority level to each interrupt trigger. This mechanism allows a higher priority trigger to interrupt the ISR of a lower priority request. Conversely, if a lower priority request occurs while running an ISR of a higher priority trigger, it will be postponed until the higher priority service is complete.

Observation: There are many interrupt sources, but an effective system will use only a few.

Program T.0.3 gives the definitions in startup.s that allow the software to enable and disable interrupts. These functions are callable from either assembly or C code. The wait for interrupt can be used to place the processor in low-power sleep mode while it waits for an interrupt.

;*********** DisableInterrupts ***************

; disable interrupts

; inputs: none

; outputs: none

DisableInterrupts CPSID I ;set I=1

BX LR

;*********** EnableInterrupts ***************

; enable interrupts

; inputs: none

; outputs: none

EnableInterrupts CPSIE I ;set I=0

BX LR

;*********** WaitForInterrupt ************************

; go to low power mode while waiting for the next interrupt

; inputs: none

; outputs: none

WaitForInterrupt

WFI

BX LR

Program T.0.3. Assembly functions needed for interrupt enabling and disabling.

T.1. GPIO Programming

T.1.1. I/O Registers

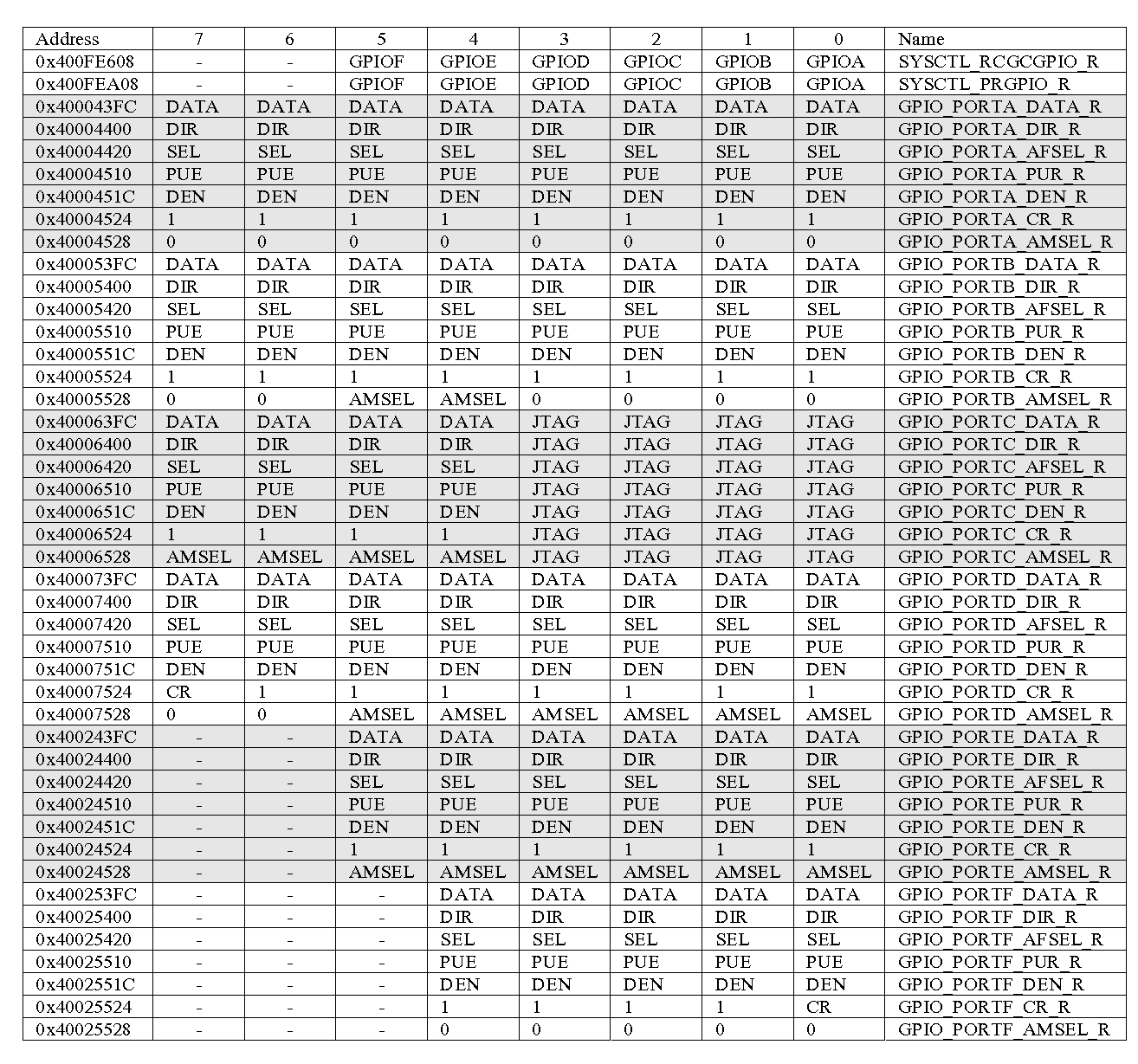

An I/O register is a location in memory with which software can interface with the I/O port. Initialization is executed once at the beginning. First, we turn on the clock in SYSCTL_RCGCGPIO_R by setting appropriate bits. Second, we wait about 25 ns, which is two bus cycles. Third, we write 1 into the corresponding DIR bit for each pin we wish to make output. Conversely we write a 0 into the corresponding DIR bit for each pin we wish to make input. To use the two switches on PF4 and PF0, we will also set bits 4 and 0 of the PUR register to activate an internal pull-up resistor. Lastly, we set the DEN bits to 1 to enable data pins. If we wish to input from a Port F GPIO pin we simply read from GPIO_PORTF_DATA_R. Reading from GPIO_PORTF_DATA_R obtains the current values for both input and output pins. If we wish to output to a Port F GPIO pin we write to GPIO_PORTF_DATA_R. Writing to GPIO_PORTF_DATA_R affects output pins but does not affect input pins. Table T.1.1 shows the addresses of some of the I/O registers.

Table T.1.1. GPIO I/O registers.

: How does the software input from Port F?

: How does the software output to Port F?

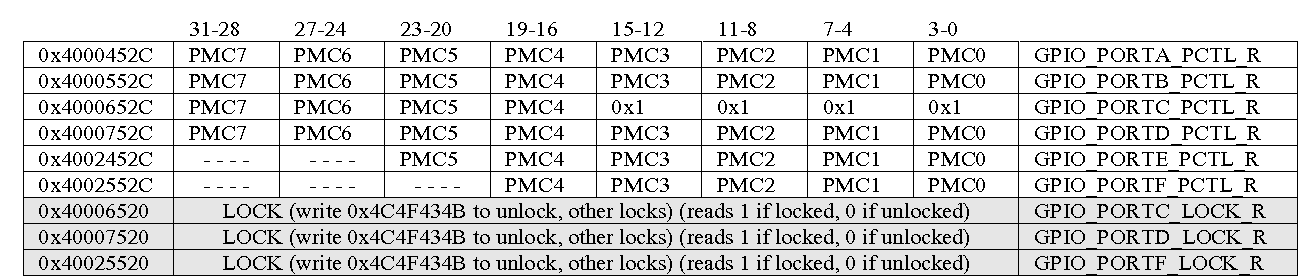

We write to the PCTL register to set the mode of the pin, see Table T.1.2. Each pin has a 4-bit mode, as listed in Table T.1.3. In this section we will set the mode to 0000 to specify GPIO.

Table T.1.2. PCTL registers.

Table T.1.3. PCTL constants.

Each of the output pins can be configured to drive 2, 4, or 8 mA. There is one configuration for each output pin. Writing ones to the DR8R register will clear the corresponding bits in the DR2R and DR4R registers. I.e., each output pin will be 2, 4, or 8 mA.

GPIO_PORTA_DR2R_R // 2mA drive

GPIO_PORTA_DR4R_R // 4mA drive

GPIO_PORTA_DR8R_R // 8mA drive

GPIO_PORTB_DR2R_R // 2mA drive

GPIO_PORTB_DR4R_R // 4mA drive

GPIO_PORTB_DR8R_R // 8mA drive

GPIO_PORTC_DR2R_R // 2mA drive

GPIO_PORTC_DR4R_R // 4mA drive

GPIO_PORTC_DR8R_R // 8mA drive

GPIO_PORTD_DR2R_R // 2mA drive

GPIO_PORTD_DR4R_R // 4mA drive

GPIO_PORTD_DR8R_R // 8mA drive

GPIO_PORTE_DR2R_R // 2mA drive

GPIO_PORTE_DR4R_R // 4mA drive

GPIO_PORTE_DR8R_R // 8mA drive

GPIO_PORTF_DR2R_R // 2mA drive

GPIO_PORTF_DR4R_R // 4mA drive

GPIO_PORTF_DR8R_R // 8mA drive

To initialize a TM4C I/O port for general use we perform these steps. Because a hardware reset will assume digital GPIO, steps 4, 5 and 7 could be skipped. Only PD7 and PF0 on the TM4C123 need to be unlocked. All the other bits on the two microcontrollers are always unlocked. The direction register specifies bit for bit whether the corresponding pins are input (0) or output (1). PC3-0 are used by the debugger, so be friendly when accessing Port C.

- We activate the clock for the port.

- We wait 2 bus cycles for the clocks to stabilize.

- We unlock the pin if needed.

- We disable the analog function.

- We select GPIO mode (0000) in PCTL.

- We set its direction register.

- If an output, we set its drive current.

- We disable the alternate function.

- We enable the digital port.

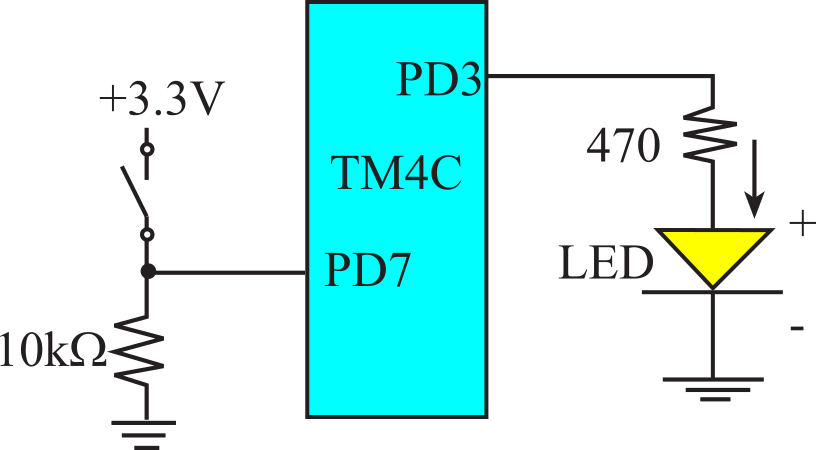

T.1.2. Examples

In this first example, we interface a switch and LED to the TM4C123, see Figure T.1.1. We will make PD7 input, and we will make PD3 output, as shown in Program T.1.1. Notice each operation is friendly, meaning it only changes the bits needed, leaving the other bits unchanged. When we read GPIO_PORTD_DATA_R the bottom 8 bits are returned with the current values on Port D. The top 24 bits are returned zero. We select bit 7 by anding with 0x80. The Port_Input function returns a 0 or 1 depending on the input on PD7. The friendly output requires these steps.- We read the existing values from the data register into a temporary.

- We clear the bits we wish to change in the temporary.

- We combine the new bits with the old bits into the temporary.

- We write the temporary back to the data register

Figure T.1.1. Switch and LED interfaced to the TM4C123.

#define GPIO_PORTD_DATA_R (*((volatile uint32_t *)0x400073FC))

#define GPIO_PORTD_DIR_R (*((volatile uint32_t *)0x40007400))

#define GPIO_PORTD_AFSEL_R (*((volatile uint32_t *)0x40007420))

#define GPIO_PORTD_DEN_R (*((volatile uint32_t *)0x4000751C))

#define GPIO_PORTD_LOCK_R (*((volatile uint32_t *)0x40007520))

#define GPIO_PORTD_DR8R_R (*((volatile uint32_t *)0x40007508))

#define GPIO_PORTD_LOCK_R (*((volatile uint32_t *)0x40007520))

#define GPIO_PORTD_PCTL_R (*((volatile uint32_t *)0x4000752C))

#define SYSCTL_RCGCGPIO_R (*((volatile uint32_t *)0x400FE608))

#define SYSCTL_PRGPIO_R (*((volatile uint32_t *)0x400FEA08))

void Port_Init(void){

SYSCTL_RCGCGPIO_R |= 0x08; // 1) activate clock for Port D

while((SYSCTL_PRGPIO_R&0x08) == 0){};// 2) ready?

GPIO_PORTD_LOCK_R = 0x4C4F434B; // 3) unlock GPIO Port D

GPIO_PORTD_CR_R = 0xFF; // allow changes to PD7

GPIO_PORTD_AMSEL_R &= ~0x88; // 4) disable analog on PD7,PD3

GPIO_PORTD_PCTL_R = (GPIO_PORTD_PCTL_R&0x0FFF0FFF); // 5) PCTL GPIO on PD7,PD3

GPIO_PORTD_DIR_R &= ~0x80; // 6) PD7 in

GPIO_PORTD_DIR_R |= 0x08; // 6) PD3 out

GPIO_PORTD_DR8R_R |= 0x08; // 7) PD3 out, 8mA

GPIO_PORTD_AFSEL_R &= ~0x88; // 8) disable alt funct on PD7,PD3

GPIO_PORTD_DEN_R |= 0x88; // 9) enable digital I/O on PD7,PD3

}

uint32_t Port_Input(void){ // returns 0 or 1

return ((GPIO_PORTD_DATA_R&0x80)>>7); // read PD7 input

}

void Port_Output(uint32_t data){ // data is 0 or 1

GPIO_PORTD_DATA_R = (GPIO_PORTD_DATA_R&~0x08)|(data<<3); // write PD3 output

}

Program T.1.1. A set of functions using PD7 as input and PD3 as output.

Observation: Remember to enable the high current drive functionality on the GPIO output pin when interfacing an LED by setting the corresponding bits in the DR8R register.

There is no conflict if two or more modules enable the clock for Port D. There are two ways on the TM4C123 to access individual port bits. The first method is to use read-modify-write software to change just pin 3. A read-or-write sequence can be used to set one or more bits.

GPIO_PORTD_DATA_R |= 0x08; // make PD3 high

A read-and-write sequence can be used to clear one or more bits.

GPIO_PORTD_DATA_R &= ~0x08; // make PD3 low

T.1.3. Bit-specific addressing

The second method uses the bit-specific addressing.

The TM4C family implements a more flexible way to access port pins

than the bit-banding described earlier.

This bit-specific addressing doesn't work for all the I/O registers,

just the parallel port data registers.

The TM4C mechanism allows collective access to 1 to 8 bits in a data port.

We define eight address offset constants in Table T.1.4.

Basically, if we are interested in bit b, the constant is 4*2b.

There are 256 possible bit combinations we might be interested in accessing,

from all of them to none of them.

Each possible bit combination has a separate address

for accessing that combination.

For each bit we are interested in, we add up the corresponding constants

from Table T.1.4 and then add that sum to the base address for the port.

The base addresses for the data ports are listed in Table T.1.5.

For example, assume we are interested in Port A bits 1, 2, and 3.

The base address for Port A is 0x40004000, and the constants are 0x0020, 0x0010 and 0x008.

The sum of 0x40004000+0x0020+0x0010+0x008 is the address 0x40004038.

If we read from 0x40004038 only bits 1, 2, and 3 will be returned.

If we write to this address only bits 1, 2, and 3 will be modified.

|

Bit |

Constant |

|

7 |

0x0200 |

|

6 |

0x0100 |

|

5 |

0x0080 |

|

4 |

0x0040 |

|

3 |

0x0020 |

|

2 |

0x0010 |

|

1 |

0x0008 |

|

0 |

0x0004 |

Table T.1.4. Address offsets used to specify individual data port bits.

|

Port |

Address |

|

Port A |

0x40004000 |

|

Port B |

0x40005000 |

|

Port C |

0x40006000 |

|

Port D |

0x40007000 |

|

Port E |

0x40024000 |

|

Port F |

0x40025000 |

Table T.1.5. Base addresses of GPIO ports.

The base address for Port D is 0x40007000. If we want to read and write all 8 bits of this port, the constants will add up to 0x03FC. Notice that the sum of the base address and the constants yields the 0x400073FC address used in Program T.2.1. In other words, read and write operations to GPIO_PORTD_DATA_R will access all 8 bits of Port D. If we are interested in just bit 3 of Port D, we add 0x0020 to 0x40007000, and we can define this in C as

#define PD3 (*((volatile uint32_t *)0x40007020))

Now, a simple write operation can be used to set PD3.

The following code is friendly because it does not modify the other 7 bits of Port D.

PD3 = 0x08; // make PD3 high

A simple write sequence will clear PD3.

The following code is also friendly.

PD3 = 0x00; // make PD3 low

A read from PD3 will return 0x03 or 0x00

depending on whether the pin is high or low, respectively.

The following code is also friendly.

PD3 = PD3^0x08; // toggle PD3

: What happens if we write to location 0x40007000?

: Specify a #define that allows us to access bits 7 and 2 of Port D. Use this #define to make both bits 7 and 2 of Port D high.

: What happens if we write to location 0x40007000? Specify a #define that allows us to access bits 6, 5, 0 of Port B. Use this #define to make bits 6, 5 and 0 of Port B high.

In this next example, we will create debugging heartbeats. We will use bit-specific addressing so the code will have no critical sections (thread safe).

#define PD0 (*((volatile uint32_t *)0x40007004))

#define PD1 (*((volatile uint32_t *)0x40007008))

void Debug_Init(void){

SYSCTL_RCGCGPIO_R |= 0x08; // 1) activate clock for Port D

while((SYSCTL_PRGPIO_R&0x08) == 0){};// 2) ready?

GPIO_PORTD_LOCK_R = 0x4C4F434B; // 3) unlock GPIO Port D

GPIO_PORTD_CR_R = 0xFF; // allow changes

GPIO_PORTD_AMSEL_R &= ~0x03; // 4) disable analog on PD1,PD0

GPIO_PORTD_PCTL_R = (GPIO_PORTD_PCTL_R&0xFFFFFF00); // 5) PCTL GPIO on PD1,PD0

GPIO_PORTD_DIR_R |= 0x03; // 6) PD1,PD0 out

GPIO_PORTD_DR8R_R |= 0x03; // 7) PD1,PD0 out, 8mA

GPIO_PORTD_AFSEL_R &= ~0x03; // 8) disable alt funct on PD1,PD0

GPIO_PORTD_DEN_R |= 0x03; // 9) enable digital I/O on PD1,PD0

}

#define Debug_HeartBeat0() (PD0 ^= 0x01)

#define Debug_HeartBeat1() (PD1 ^= 0x02)

Program T.1.2. An LED monitor.

Let's consider why using bit-specific addressing removes critical sections. Both GPIO_PORTD_DATA_R ^= 0x02; and PD2 ^= 0x02; will toggle bit 1 in the 32-bit Port D data register. They both perform a read modify write sequence to create the toggle. They both create similar assembly code when compiled, as shown in Program T.1.3.

|

; GPIO_PORTD_DATA_R ^= 0x02; |

; PD2 ^= 0x02; |

Program T.1.3. Assembly code to toggle PD1.

Using GPIO_PORTD_DATA_R creates a critical section between the second and fourth assembly instructions. Reading GPIO_PORTD_DATA_R gives all of port D, and writing GPIO_PORTD_DATA_R changes all of port D. Assume some other thread interrupts this thread between the second and third (or between the third and fourth) instructions, and that other thread changes bits 7-2 or bit 0 in port D. When the other thread returns from interrupt, the value in R0 of this thread is the previous contents of bits 7-2 and bit 0. Therefore, the change made by the other interrupt is undone.

Using PD1 does not create a critical section. Reading PD1 gives just port D bit 1 (0 or 2), and writing PD1 only changes bit 1 of port D. Since the write to PD1 does not change bits 7-2 and bit 0, any changes caused by other interrupts will not be undone.

T.1.4. Keyboard Scanning

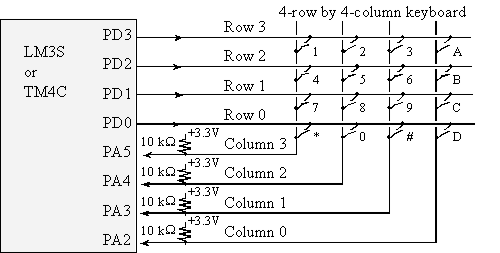

This matrix keyboard divides the sixteen keys into four rows and four columns, as shown in Figure T.1.2. Each key exists at a unique row/column location. It will take eight I/O pins to interface the rows and columns. Any output port on the TM4C could have been used to interface the rows. To scan the matrix, the software will drive the rows one at a time with open collector logic then read the columns. The open collector logic, with outputs HiZ and 0, will be created by toggling the direction register on the four rows. Actual 10 kΩ pull-up resistors will be placed on the column inputs (PA5-PA2) rather than configured internally, because the internal pull-ups are not fast enough to handle the scanning procedure.

Figure T.1.2. A matrix keyboard interfaced to the microcontroller.

Program T.1.4 shows the initialization software. The data structure will assist in the scanning algorithm, and it provides a visual mapping from the physical layout of the keys to the ASCII code produced when touching that key. The structure also makes it easy to adapt this solution to other keyboard interfaces. A periodic interrupt can be used to debounce the switches. The key to debouncing is to not observe the switches more frequently than once every 10 ms.

void MatrixKeypad_Init(void){

SYSCTL_RCGCGPIO_R |= 0x09; // 1) activate clock for Ports A and D

while((SYSCTL_PRGPIO_R&0x09) != 0x09){};// ready?

GPIO_PORTA_AFSEL_R &= ~0x3C; // GPIO function on PA5-2

GPIO_PORTA_AMSEL_R &= ~0x3C; // disable analog function on PA5-2

GPIO_PORTA_PCTL_R &= ~0x00FFFF00; // configure PA5-2 as GPIO

GPIO_PORTA_DEN_R |= 0x3C; // enable digital I/O on PA5-2

GPIO_PORTA_DIR_R &= ~0x3C; // make PA5-2 in (PA5-2 columns)

GPIO_PORTD_AFSEL_R &= ~0x0F; // GPIO function on PD3-0

GPIO_PORTD_AMSEL_R &= ~0x0F; // disable analog function on PD3-0

GPIO_PORTD_PCTL_R &= ~0x0000FFFF; // configure PD3-0 as GPIO

GPIO_PORTD_DATA_R &= ~0x0F; // DIRn=0, OUTn=HiZ; DIRn=1, OUTn=0

GPIO_PORTD_DEN_R |= 0x0F; // enable digital I/O on PD3-0

GPIO_PORTD_DIR_R &= ~0x0F; // make PD3-0 in (PD3-0 rows)

GPIO_PORTD_DR8R_R |= 0x0F;} // enable 8 mA drive

Program T.1.4. Initialization software for a matrix keyboard.

Program T.1.5 shows the

scanning software. The scanning sequence is listed in Table T.1.6. There are

two steps to scan a particular row:

- Select that row by driving it low, while the other rows are HiZ,

- Wait for the circuit to stabilize

- Read the columns to see if any keys are pressed in that row,

- 0 means the key is pressed

- 1 means the key is not pressed

It is important to observe column and row signals on a dual trace oscilloscope while running the software at full speed, because it takes time for correct signal to appear on the column after the row is changed. In most cases, a software delay should be inserted between setting the row and reading the column. The length of the delay you will need depends on the size of the pull-up resistor and any stray capacitance that may exist in your circuit.

|

direction |

PD0 |

PD1 |

PD2 |

PD3 |

PA2 |

PA3 |

PA4 |

PA5 |

|

0x01 |

0 |

HiZ |

HiZ |

HiZ |

1 |

2 |

3 |

A |

|

0x02 |

HiZ |

0 |

HiZ |

HiZ |

4 |

5 |

6 |

B |

|

0x04 |

HiZ |

HiZ |

0 |

HiZ |

7 |

8 |

9 |

C |

|

0x08 |

HiZ |

HiZ |

HiZ |

0 |

* |

0 |

# |

D |

Table T.1.6. Patterns for a 4 by 4 matrix keyboard.

struct Row{

uint8_t direction;

char keycode[4];

};

typedef const struct Row Row_t;

Row_t ScanTab[5]={

{ 0x01, "123A" }, // row 0

{ 0x02, "456B" }, // row 1

{ 0x04, "789C" }, // row 2

{ 0x08, "*0#D" }, // row 3

{ 0x00, " " }

};

// Returns ASCII code for key pressed,

// Num is the number of keys pressed

// both equal zero if no key pressed

char MatrixKeypad_Scan(int32_t *Num){

Row_t *pt;

uint32_t column; char key;

uint32_t j;

(*Num) = 0;

key = 0; // default values

pt = &ScanTab[0];

while(pt->direction){

GPIO_PORTD_DIR_R = pt->direction; // one output

GPIO_PORTD_DATA_R &= ~0x0F; // DIRn=0, OUTn=HiZ; DIRn=1, OUTn=0

for(j=1; j<=10; j++); // very short delay

column = ((GPIO_PORTA_DATA_R&0x3C)>>2);// read columns

for(j=0; j<=3; j++){

if((column&0x01)==0){

key = pt->keycode[j];

(*Num)++;

}

column>>=1; // shift into position

}

pt++;

}

return key;

}

// Waits for a key to be pressed, then released

// returns ASCII code for key pressed,

// n is the number of keys pressed

// both equal zero if no key pressed */

char MatrixKeypad_In(void){ int32_t n;

char letter;

do{

letter = MatrixKeypad_Scan(&n);

} while (n != 1); // repeat until exactly one

do{

letter = MatrixKeypad_Scan(&n);

} while (n != 0); // repeat until release

return letter;

}

Program T.1.5. Scanning software for a matrix keyboard

Two-key rollover occurs when the operator is typing quickly. For example, if the operator is typing the A, B, then C, he/she might type A, AB, B, BC, C, and then release. With rollover, the keyboard does not go through a no-key state in between typing. The hardware interface in Figure T.1.2 could handle two-key rollover, but the software solution in Program T.1.5 does not.

One of the problems with switches is called switch bounce. Many inexpensive switches will mechanically oscillate for up to a few milliseconds when touched or released. It behaves like an underdamped oscillator. These mechanical oscillations cause electrical oscillations such that a port pin will oscillate high/low during the bounce. In some cases, this bounce should be removed.

There are two good solutions to using interrupt synchronization for the keyboard. The approach implemented here uses periodic polling, because it affords a simple solution to both bouncing and two-key rollover. The time between interrupts is selected to be longer than the maximum bounce time, but shorter than the minimum time between key strikes. If you type ten characters per second, the minimum time between rising and falling edges is about 50 ms. Since switch bounce times are less than 10 ms, we will poll the keyboard every 25 ms. This means the average latency will be 12.5 ms, and the maximum latency will be 25 ms.

The initialization include GPIO, SysTick, and a FIFO. A key is recognized if the scanning returns one key found, and this key is different from what it scanned 25 ms ago.

AddIndexFifo(Matrix, 16, char, 1, 0) // create a FIFO

char static LastKey;

void Matrix_Init(void){

LastKey = 0; // no key typed

MatrixFifo_Init();

MatrixKeypad_Init();

SysTick_Init(1250000); // 25 ms polling

}

void SysTick_Handler(void){ char thisKey; int32_t n;

thisKey = MatrixKeypad_Scan(&n); // scan

if((thisKey != LastKey) && (n == 1)){

MatrixFifo_Put(thisKey);

LastKey = thisKey;

} else{

LastKey = 0; // invalid

}

}

char Matrix_InChar(void){ char letter;

while(MatrixFifo_Get(&letter) == FIFOFAIL){};

return(letter);

}

Program T.1.5. Periodic polling interface of a scanned keyboard.

One of the advantages of Program T.1.5 is two-key rollover. When people type very fast, they sometimes type the next key before the release the first key. For example, when the operator types the letters "BCD" slowly with one finger, the keyboard status goes in this sequence

<none>, <B>, <none>, <C>, <none>, <D>, <none>

Conversely, if the operator types quickly, there can be two-key rollover, which creates this sequence

<none>, <B>, <BC>, <C>, <CD>, <D>, <none>

where <BC> means both keys 'B' and 'C' are touched. Two-key rollover means the keyboard does not go through a state where no keys are touched between typing the 'B' and the 'C'. Since each of the keys goes through a state where exactly one key is pressed and is different than it was 25 ms ago, Program T.1.5 will handle two-key rollover.

A second approach is to arm the device for interrupts by driving all rows to zero. In this manner, we will receive a falling edge on one of the Port A inputs when any key is touched. During the ISR we could scan the keyboard and put the key into the FIFO. To solve the bounce problem this solution implements a time delay from key touch to when the software scans for keys. This approach uses a combination of edge-triggered inputs and timer interrupts to perform input in the background. When arming for interrupts, we set all four rows to output zero. In this way, a falling edge interrupt will occur on any key touched. When an edge-triggered interrupt occurs, we will disarm this input and arm an timer to trigger in 10 ms. It is during the timer ISR we scan the matrix. If there is exactly one key, we enter it into the FIFO. An interrupt may occur on release due to bounce. However, 10 ms after the release, when we scan during the Timer0A_Handler the MatrixKeypad_Scan function will return a Num of zero, and we will ignore it. This solution solves switch bounce, but not two-key rollover.

There are three solutions to debounce an individual switch

1) Blind synchronization: read switch, and then wait 10 ms

2) Periodic polling: use a periodic interrupt at 10 ms

3) Interrupt:

edge-triggered interrupt, then time delay interrupt

Table T.2.1 shows the ADC0 register bits required to perform sampling on a single channel. Any bits not specified will read 0. There are two ADCs; you will use ADC0 and TExaSdisplay uses ADC1. For more complex configurations refer to the specific data sheet. The value in the ADC0_PC_R specifies the maximum sampling rate, see Table T.2.2. This is not the actual sampling rate; it is the maximum possible. Setting ADC0_PC_R to 7, allows the TM4C123 to sample up to 1 million samples per second. The example code in this section will set ADC0_PC_R to 1, because we will be sampling much slower than 125 kHz. It will be more accurate and require less power to run at 125 kHz maximum mode, as compared to 1 MHz maximum mode. In this chapter we will use software trigger mode, so the actual sampling rate is determined by the SysTick periodic interrupt rate; the SysTick ISR will take one ADC sample. On the TM4C123, we will need to set bits in the AMSEL register to activate the analog interface. Furthermore, we will clear bits DEN register to deactivate the digital interface.

|

Address |

31-17 |

16 |

15-3 |

|

2 |

1 0 |

Name |

||

|

0x400F.E638 |

|

|

|

|

ADC1 ADC0 |

SYSCTL_RCGCADC_R |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

31-14 |

13-12 |

11-10 |

9-8 |

7-6 |

5-4 |

3-2 |

1-0 |

|

|

0x4003.8020 |

|

SS3 |

|

SS2 |

|

SS1 |

|

SS0 |

ADC0_SSPRI_R |

|

|

|

|

|

|

|

|

|

|

|

|

|

31-16 |

15-12 |

11-8 |

7-4 |

3-0 |

|

|||

|

0x4003.8014 |

|

EM3 |

EM2 |

EM1 |

EM0 |

ADC0_EMUX_R |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

31-4 |

3 |

2 |

1 |

0 |

|

|||

|

0x4003.8000 |

|

ASEN3 |

ASEN2 |

ASEN1 |

ASEN0 |

ADC0_ACTSS_R |

|||

|

0x4003.8030 |

|

AVE (3 bits) |

ADC0_SAC_R |

||||||

|

0x4003.80A0 |

|

MUX0 |

ADC0_SSMUX3_R |

||||||

|

0x4003.8FC4 |

|

Speed |

ADC0_PC_R |

||||||

|

0x4003.80A4 |

|

TS0 |

IE0 |

END0 |

D0 |

ADC0_SSCTL3_R |

|||

|

0x4003.8028 |

|

SS3 |

SS2 |

SS1 |

SS0 |

ADC0_PSSI_R |

|||

|

0x4003.8004 |

|

INR3 |

INR2 |

INR1 |

INR0 |

ADC0_RIS_R |

|||

|

0x4003.800C |

|

IN3 |

IN2 |

IN1 |

IN0 |

ADC0_ISC_R |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

31-12 |

11-0 |

|

||||||

|

0x4003.80A8 |

|

DATA |

ADC0_SSFIFO3 |

||||||

Table T.2.1. The TM4C ADC registers. Each register is 32 bits wide. You will use ADC0 and we will use ADC1 to implement the oscilloscope feature.

|

Value |

Description |

|

0x7 |

1M samples/second |

|

0x5 |

500K samples/second |

|

0x3 |

250K samples/second |

|

0x1 |

125K samples/second |

Table T.2.2. The maximum sampling rate specified in the ADC0_PC_R register.

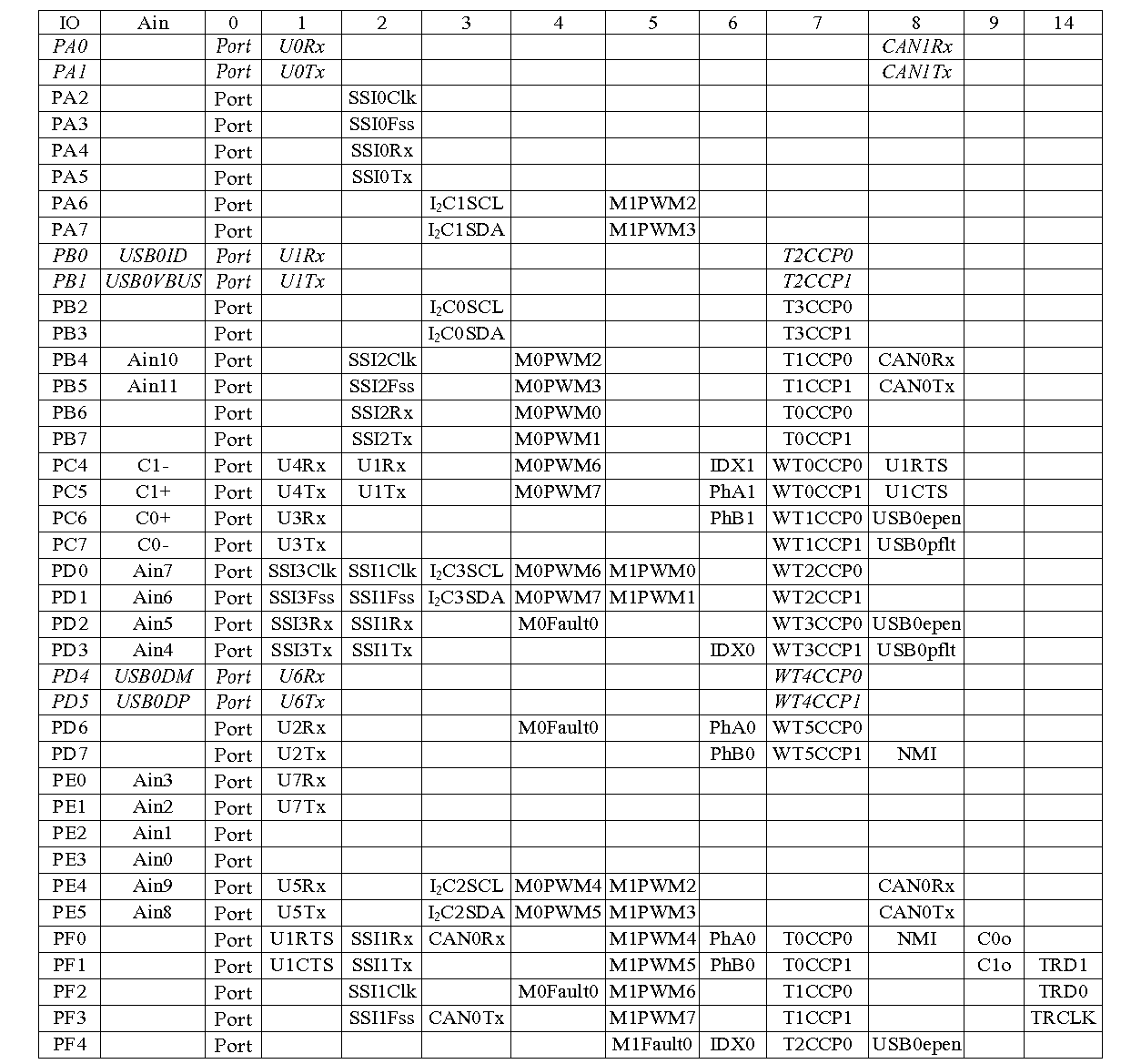

Table T.2.3 shows which I/O pins on the TM4C123 can be used for ADC analog input channels.

|

IO |

Ain |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

14 |

|

PB4 |

Ain10 |

Port |

|

SSI2Clk |

|

M0PWM2 |

|

|

T1CCP0 |

CAN0Rx |

|

|

|

PB5 |

Ain11 |

Port |

|

SSI2Fss |

|

M0PWM3 |

|

|

T1CCP1 |

CAN0Tx |

|

|

|

PD0 |

Ain7 |

Port |

SSI3Clk |

SSI1Clk |

I2C3SCL |

M0PWM6 |

M1PWM0 |

|

WT2CCP0 |

|

|

|

|

PD1 |

Ain6 |

Port |

SSI3Fss |

SSI1Fss |

I2C3SDA |

M0PWM7 |

M1PWM1 |

|

WT2CCP1 |

|

|

|

|

PD2 |

Ain5 |

Port |

SSI3Rx |

SSI1Rx |

|

M0Fault0 |

|

|

WT3CCP0 |

USB0epen |

|

|

|

PD3 |

Ain4 |

Port |

SSI3Tx |

SSI1Tx |

|

|

|

IDX0 |

WT3CCP1 |

USB0pflt |

|

|

|

PE0 |

Ain3 |

Port |

U7Rx |

|

|

|

|

|

|

|

|

|

|

PE1 |

Ain2 |

Port |

U7Tx |

|

|

|

|

|

|

|

|

|

|

PE2 |

Ain1 |

Port |

|

|

|

|

|

|

|

|

|

|

|

PE3 |

Ain0 |

Port |

|

|

|

|

|

|

|

|

|

|

|

PE4 |

Ain9 |

Port |

U5Rx |

|

I2C2SCL |

M0PWM4 |

M1PWM2 |

|

|

CAN0Rx |

|

|

|

PE5 |

Ain8 |

Port |

U5Tx |

|

I2C2SDA |

M0PWM5 |

M1PWM3 |

|

|

CAN0Tx |

|

|

Table T.2.3. Twelve different pins on the TM4C123 can be used to sample analog inputs. The example code will use ADC0 and PE4/Ch9 to sample analog input. TExaSdisplay uses ADC1 and PD3 to implement the oscilloscope feature.

The ADC has four sequencers. We set the ADC0_SSPRI_R register to 0x0123 to make sequencer 3 the highest priority. Because we are using just one sequencer, we just need to make sure each sequencer has a unique priority. We set bits 15-12 (EM3) in the ADC0_EMUX_R register to specify how the ADC will be triggered. Table T.2.4 shows the various ways to trigger an ADC conversion. Timer-triggered ADC sampling (EM3=0x5) has very low jitter. However, we will begin with software triggering (EM3=0x0). The software writes an 8 (SS3) to the ADC0_PSSI_R to initiate a conversion on sequencer 3. We can enable and disable the sequencers using the ADC0_ACTSS_R register. There are twelve ADC channels on the TM4C123. Which channel we sample is configured by writing to the ADC0_SSMUX3_R register. The mapping between channel number and the port pin is shown in Table T.2.3. For example channel 9 is connected to the pin PE4. The ADC0_SSCTL3_R register specifies the mode of the ADC sample. We set TS0 to measure temperature and clear it to measure the analog voltage on the ADC input pin. We set IE0 so that the INR3 bit is set when the ADC conversion is complete, and clear it when no flags are needed. When using sequencer 3, there is only one sample, so END0 will always be set, signifying this sample is the end of the sequence. In this class, the sequence will be just one ADC conversion. We set the D0 bit to activate differential sampling, such as measuring the analog difference between two ADC pins. In our example, we clear D0 to sample a single-ended analog input. Because we set the IE0 bit, the INR3 flag in the ADC0_RIS_R register will be set when the ADC conversion is complete, We clear the INR3 bit by writing an 8 to the ADC0_ISC_R register.

|

Value |

Event |

|

0x0 |

Software start |

|

0x1 |

Analog Comparator 0 |

|

0x2 |

Analog Comparator 1 |

|

0x3 |

Analog Comparator 2 |

|

0x4 |

External (GPIO PB4) |

|

0x5 |

Timer |

|

0x6 |

PWM0 |

|

0x7 |

PWM1 |

|

0x8 |

PWM2 |

|

0x9 |

PWM3 |

|

0xF |

Always (continuously sample) |

Table T.2.4. The ADC EM3, EM2, EM1, and EM0 bits in the ADC_EMUX_R register.

We perform the following steps to configure the ADC for software start on one channel. Program T.2.1 shows a specific details for sampling PE4, which is channel 9. The function ADC0_InSeq3 will sample PE4 using software start and use busy-wait synchronization to wait for completion.

Step 1. We enable the ADC clock bit 0 in SYSCTL_RCGCADC_R for ADC0.

Step 2. We enable the port clock for the pin that we will be using for the ADC input.

Step 3. We wait for the two clocks to stabilize (some people found extra delay prevented hard faults)

Step 4. Make that pin an input by writing zero to the DIR register.

Step 5. Enable the alternative function on that pin by writing one to the AFSEL register.

Step 6. Disable the digital function on that pin by writing zero to the DEN register.

Step 7. Enable the analog function on that pin by writing one to the AMSEL register.

Step 8. We set the ADC0_PC_R register specify the maximum sampling rate of the ADC. In this example, we will sample slower than 125 kHz, so the maximum sampling rate is set at 125 kHz. This will require less power and produce a longer sampling time, creating a more accurate conversion.

Step 9. We will set the priority of each of the four sequencers. In this case, we are using just one sequencer, so the priorities are irrelevant, except for the fact that no two sequencers should have the same priority.

Step 10. Before configuring the sequencer, we need to disable it. To disable sequencer 3, we write a 0 to bit 3 (ASEN3) in the ADC0_ACTSS_R register. Disabling the sequencer during programming prevents erroneous execution if a trigger event were to occur during the configuration process.

Step 11. We configure the trigger event for the sample sequencer in the ADC0_EMUX_R register. For this example, we write a 0000 to bits 15-12 (EM3) specifying software start mode for sequencer 3.

Step 12. Configure the corresponding input source in the ADC0_SSMUX3 register. In this example, we write the channel number to bits 3-0 in the ADC0_SSMUX3_R register. In this example, we sample channel 9, which is PE4.

Step 13. Configure the sample control bits in the corresponding nibble in the ADC0_SSCTL3 register. When programming the last nibble, ensure that the END bit is set. Failure to set the END bit causes unpredictable behavior. Sequencer 3 has only one sample, so we write a 0110 to the ADC0_SSCTL3_R register. Bit 3 is the TS0 bit, which we clear because we are not measuring temperature. Bit 2 is the IE0 bit, which we set because we want to the RIS bit to be set when the sample is complete. Bit 1 is the END0 bit, which is set because this is the last (and only) sample in the sequence. Bit 0 is the D0 bit, which we clear because we do not wish to use differential mode.

Step 14. Disable interrupts in ADC by clearing bits in the ADC0_IM_R register. Since we are using sequencer 3, we disable SS3 interrupts by clearing bit 3.

Step 15. We enable the sample sequencer logic by writing a 1 to the corresponding ASEN3. To enable sequencer 3, we write a 1 to bit 3 (ASEN3) in the ADC0_ACTSS_R register.

void ADC0_InitSWTriggerSeq3_Ch9(void){

SYSCTL_RCGCADC_R |= 0x0001; // 1)

activate ADC0

SYSCTL_RCGCGPIO_R |= 0x10; // 2)

activate clock for Port E

while((SYSCTL_PRGPIO_R&0x10) != 0x10){}; // 3

for stabilization

GPIO_PORTE_DIR_R &= ~0x10; //

4) make PE4 input

GPIO_PORTE_AFSEL_R |= 0x10; // 5)

enable alternate function on PE4

GPIO_PORTE_DEN_R &= ~0x10; //

6) disable digital I/O on PE4

GPIO_PORTE_AMSEL_R |= 0x10; // 7)

enable analog functionality on PE4

// while((SYSCTL_PRADC_R&0x0001) != 0x0001){}; // good code, but

not implemented in simulator

ADC0_PC_R &= ~0xF;

ADC0_PC_R |=

0x1; //

8) configure for 125K samples/sec

ADC0_SSPRI_R =

0x0123; // 9)

Sequencer 3 is highest priority

ADC0_ACTSS_R &=

~0x0008; // 10) disable sample

sequencer 3

ADC0_EMUX_R &=

~0xF000; // 11) seq3 is

software trigger

ADC0_SSMUX3_R &= ~0x000F;

ADC0_SSMUX3_R +=

9; //

12) set channel

ADC0_SSCTL3_R =

0x0006; // 13) no TS0 D0,

yes IE0 END0

ADC0_IM_R &=

~0x0008; // 14)

disable SS3 interrupts

ADC0_ACTSS_R |=

0x0008; // 15) enable

sample sequencer 3

}

Program T.2.1. Initialization of the ADC using software start and busy-wait (ADCSWTrigger).

Video T.2.1. ADC Initialization Ritual

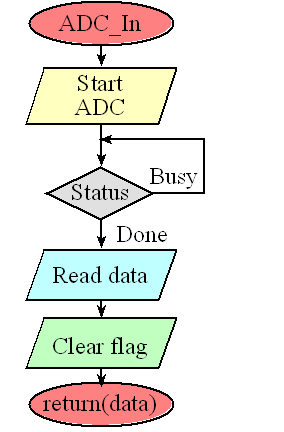

Program T.2.2 gives a function that performs an ADC conversion. There are four steps required to perform a software-start conversion. The range is 0 to 3.3V. If the analog input is 0, the digital output will be 0, and if the analog input is 3.3V, the digital output will be 4095.

Digital Sample = (Analog Input (volts) • 4095) / 3.3V(volts)

Step 1. The ADC is started using the software trigger. The channel to sample was specified earlier in the initialization.

Step 2. The function waits for the ADC to complete by polling the RIS register bit 3.

Step 3. The 12-bit digital sample is read out of sequencer 3.

Step 4. The RIS bit is cleared by writing to the ISC register.

Figure T.2.3. The four steps of analog to digital conversion: 1) initiate conversion, 2) wait for the ADC to finish, 3) read the digital result, and 4) clear the completion flag.

//------------ADC0_InSeq3------------

// Busy-wait analog to digital conversion

// Input: none

// Output: 12-bit result of ADC conversion

uint32_t ADC0_InSeq3(void){ uint32_t result;

ADC0_PSSI_R = 0x0008; // 1) initiate SS3

while((ADC0_RIS_R&0x08)==0){}; // 2) wait for conversion done

result = ADC0_SSFIFO3_R&0xFFF; // 3) read result

ADC0_ISC_R = 0x0008; // 4) acknowledge completion

return result;

}

Program T.2.2. ADC sampling using software start and busy-wait (ADCSWTrigger).

Video T.2.2. Capturing a Sample

: If the input voltage is 1.65V, what value will the TM4C 12-bit ADC return?

: If the input voltage is 1.0V, what value will the TM4C 12-bit ADC return?

It is important to sample the ADC at a regular rate. One simple way to deploy periodic sampling is to perform the ADC conversion in a periodic ISR. In Program T.2.3, the sampling rate is determined by the rate of the periodic interrupt. The global variable, Flag is called a semaphore, which is set when new information is stored into the variable Data. We can connect PD0 to a logic analyzer or oscilloscope to verify the sampling rate. Triple toggling allows us to measure the execution time of the ISR and the time between ISR invocations.

uint32_t Data; // 0 to 4095

uint32_t Flag; // 1 means new data

void SysTick_Handler(void){

Debug_HeartBeat0(); // toggle PD0

Debug_HeartBeat0(); // toggle PD0

Data =

ADC0_InSeq3(); // Sample ADC

Flag =

1; //

Synchronize with other threads

Debug_HeartBeat0(); // toggle PD0

}

Program T.2.3. Real-time sampling using SysTick Interrupts.

Observation: The triple toggle technique allows us to measure the execution time of the ISR (second to third toggle) and the time between interrupts (first toggle to the next first toggle).

Next, we will configure the ADC to sample a single channel at a periodic rate using a timer trigger. The most time-accurate sampling method is timer-triggered sampling (EM3=0x5). There is virtually no sampling jitter because the hardware timer starts the ADC conversion. When the software runs the ISR does not affect when the data was sampled.

: If the bus clock is 80 MHz and the SysTick LOAD register is 79999, what will be the ADC sampling rate?

: If the bus clock is 80 MHz and we wish to sample at 10 kHz, what value do we write into the SysTick LOAD register?

There are 13 steps to configure the ADC to sample a single channel at a periodic rate. The most accurate sampling method is timer-triggered sampling (EM3=0x5). On the TM4C123, the MUX fields are 4 bits wide, allowing us to specify channels 0 to 11. Timer-triggered sampling will have zero sampling jitter because the hardware starts each sample.

Step 1. We enable the ADC clock in the SYSCTL_RCGCADC_R register.

Step 2. Bits 3-0 of the ADC0_PC_R register specify the maximum sampling rate of the ADC. The actual sampling rate is determined by how fast the ADC is triggered. Running at 125 kHz will require less power and produce a longer sampling time compared to the faster modes, creating a more accurate conversion.

Step 3. We will set the priority of each of the four sequencers. In this case, we are using just one sequencer, so the priorities are irrelevant, except for the fact that no two sequencers should have the same priority.

Step 4. Next, we need to configure the timer to run at the desired sampling frequency. We enable the Timer0 clock by setting bit 0 of the SYSCTL_RCGCTIMER_R register. This initialization is similar to Program T.2.3 with two changes. First we set bit 5 of the TIMER0_CTL_R register to activate TAOTE, which is the Timer A output trigger enable. Secondly, we do not arm any Timer0 interrupts. The rate at which the timer rolls over determines the sampling frequency. Let prescale be the value loaded into TIMER0_TAPR_R, and let period be the value loaded into TIMER0_TAILR_R. If the period of the bus clock frequency is Δt, then the ADC sampling period will be Δt *(prescale + 1)*(period + 1)

The fastest sampling rate is determined by the speed of the processor handling the ADC interrupts and by the speed of the main program consuming the data from the FIFO. If the bus clock is 80 MHz, the slowest possible sampling rate for this example is 80MHz/232, which is about 0.018 Hz, which is every 53 seconds.

Step 5. Before configuring the sequencer, we need to disable it. To disable sequencer 3, we write a 0 to bit 3 (ASEN3) in the ADC0_ACTSS_R register. Disabling the sequencer during programming prevents erroneous execution if a trigger event were to occur during the configuration process.

Step 6. We configure the trigger event for the sample sequencer in the ADC0_EMUX_R register. For this example, we write a 0101 to bits 15-12 (EM3) specifying timer trigger mode for sequencer 3.

Step 7. For each sample in the sample sequence, configure the corresponding input source in the ADC0_SSMUXn register. In this example, we write the channel number (0, 1, 2, or 3) to bits 3-0 in the ADC0_SSMUX3_R register.

Step 8. For each sample in the sample sequence, we configure the sample control bits in the corresponding nibble in the ADC0_SSCTLn register. When programming the last nibble, ensure that the END bit is set. Failure to set the END bit causes unpredictable behavior. Sequencer 3 has only one sample, so we write a 0110 to the ADC0_SSCTL3_R register. Bit 3 is the TS0 bit, which we clear because we are not measuring temperature. Bit 2 is the IE0 bit, which we set because we want to request an interrupt when the sample is complete. Bit 1 is the END0 bit, which is set because this is the last (and only) sample in the sequence. Bit 0 is the D0 bit, which we clear because we do not wish to use differential mode.

Step 9. If interrupts are to be used, write a 1 to the corresponding mask bit in the ADC0_IM_R register. We want an interrupt to occur when the conversion is complete (set bit 3, MASK3).

Step 10. We enable the sample sequencer logic by writing a 1 to the corresponding ASENn. To enable sequencer 3, we write a 1 to bit 3 (ASEN3) in the ADC0_ACTSS_R register.

Step 11. The priority of the ADC0 sequencer 3 interrupts are in bits 13-15 of the NVIC_PRI4_R register.

Step 12. Since we are requesting interrupts, we need to enable interrupts in the NVIC. ADC sequencer 3 interrupts are enabled by setting bit 17 in the NVIC_EN0_R register.

Step 13. Lastly, we must enable interrupts in the PRIMASK register, which is typically done in the main program after all initializations are complete.

The timer starts the conversion at a regular rate. Bit 3 (INR3) in the ADC0_RIS_R register will be set when the conversion is done. This bit is armed and enabled for interrupting, so conversion complete will trigger an interrupt. The IN3 bit in the ADC0_ISC_R register triggers the interrupt. The ISR acknowledges the interrupt by writing a 1 to bit 3 (IN3). The 12-bit result is read from the ADC0_SSFIFO3_R register. The book web site for has example code. In order to reduce latency of other interrupt requests in the system, this ISR simply stores the 12-bit conversion in a FIFO, to be processed later in the main program. Programs T.2.4 and T.2.5 shows the initialization and interrupt service routine to affect the periodic sampling. For the port pin, we disable its DEN, clear its DIR, set its AFSEL and enable its AMSEL bit.

void (*ADCTask)(uint32_t); // user function to be called when new ADC data ready

void ADC0_InitTimer0ATriggerSeq3PD3(uint32_t period, void(*task)(uint32_t)){

volatile uint32_t delay;

SYSCTL_RCGCADC_R |= 0x01; // 1) activate ADC0

SYSCTL_RCGCGPIO_R |= 0x08; // Port D clock

delay = SYSCTL_RCGCGPIO_R; // allow time for clock to stabilize

GPIO_PORTD_DIR_R &= ~0x08; // make PD3 input

GPIO_PORTD_AFSEL_R |= 0x08; // enable alternate function on PD3

GPIO_PORTD_DEN_R &= ~0x08; // disable digital I/O on PD3

GPIO_PORTD_AMSEL_R |= 0x08; // enable analog functionality on PD3

ADC0_PC_R = 0x01; // 2) maximum speed is 125K samples/sec

ADC0_SSPRI_R = 0x3210; // 3) seq 0 is highest, seq 3 is lowest

SYSCTL_RCGCTIMER_R |= 0x01; // 4) activate timer0

delay = SYSCTL_RCGCGPIO_R;

TIMER0_CTL_R = 0x00000000; // disable timer0A during setup

TIMER0_CTL_R |= 0x00000020; // enable timer0A trigger to ADC

TIMER0_CFG_R = 0; // configure for 32-bit timer mode

TIMER0_TAMR_R = 0x00000002; // configure for periodic mode

TIMER0_TAPR_R = 0; // prescale value for trigger

TIMER0_TAILR_R = period-1; // start value for trigger

TIMER0_IMR_R = 0x00000000; // disable all interrupts

TIMER0_CTL_R |= 0x00000001; // enable timer0A 32-b, periodic

ADC0_ACTSS_R &= ~0x08; // 5) disable sample sequencer 3

ADC0_EMUX_R = (ADC0_EMUX_R&0xFFFF0FFF)+0x5000; // 6) timer trigger

ADC0_SSMUX3_R = 4; // 7) PD3 is analog channel 4

ADC0_SSCTL3_R = 0x06; // 8) set flag and end after first sample

ADC0_IM_R |= 0x08; // 9) enable SS3 interrupts

ADC0_ACTSS_R |= 0x08; // 10) enable sample sequencer 3

NVIC_PRI4_R = (NVIC_PRI4_R&0xFFFF00FF)|0x00004000; // 11)priority 2

NVIC_EN0_R = 1<<17; // 12) enable interrupt 17 in NVIC

}

void ADC0Seq0_Handler(void){ uint32_t data;

ADC0_ISC_R = 0x01; // acknowledge ADC sequence 0 completion

data = ADC0_SSFIFO3_R&0xFFF;

(*ADCTask)(data); // execute user task

}

Program T.2.4. Timer-triggered ADC sampling.

Program T.2.5 shows the high-level implementation of a real-time data acquisition system. Real-time sampling is implemented in the timer-triggered ADC sampling, and the processing occurs later in the main program. As long as the average time to process a sample is less than 100ms, the FIFO size can be chosen so it never fills. Abstraction is the separation of what it does (Program T.2.5) from how it works (Program T.2.4).

void RealTimeTask(uint32_t data){

Debug_HeartBeat0(); // toggle LED

Fifo_Put(data);

}

int main(void){

DisableInterrupts();

PLL_Init(Bus80MHz); // 80 MHz system clock

ADC0_InitTimer0ATriggerSeq3PD3(8000000,&); // ADC channel 4, 10 Hz sampling

Debug_Init();

EnableInterrupts(); // 13) I=0 in the PRIMASK register

while(1){uint32_t data;

while(Fifo_Get(&data)==0){}; // wait for data

Debug_HeartBeat1(); // toggle LED

// process data

}

}

}

Program T.2.5. High-level data acquisition.

: Assuming no noise what is the range, resolution and precision of the ADC?

Sequencer 3 can only sample one analog input. When we wish to sample multiple channels with one trigger, we need to use sequencers 0, 1, or 2. The TM4C123 has 12 analog input pins. The TM4C123 two ADC modules and each module has 4 sequencers. Program T.2.6 will sample ADC channels 4 and 5 at 1 kHz. Channel 4 on the TM4C123 is PD3 and channel 5 is PD2. This solution will use the periodic timer to establish the 1000 Hz sampling rate, similar to Program T.2.4. We specify the channels to sample in the ADC0_SSMUX2_R register. 0x0054 means first sample channel 4 then sample channel 5. The ADC0_SSCTL2_R bit END1 is set to specify two conversions, assuming END0=0. The IE1 bit is set to request an interrupt after the second conversion. We read the two 12-bit results from the ADC0_SSFIFO2 register. All other bits in the ADC0_SSCTL2_R register will be clear for this example (no temperature or differential measurements). Using the timer means no sampling jitter.

void ADC_Init(void){ // assumes a 80 MHz bus clock

SYSCTL_RCGCADC_R |= 0x01; // 1) activate ADC0

SYSCTL_RCGCGPIO_R |= 0x08; // Port D clock

SYSCTL_RCGCTIMER_R |= 0x01; // 4) activate timer0

Ch4Fifo_Init(); // initialize FIFOs

Ch5Fifo_Init(); // wait for clocks to stabilize

GPIO_PORTD_DIR_R &= ~0x0C; // make PD3-2 input

GPIO_PORTD_AFSEL_R |= 0x0C; // enable alternate function on PD3-2

GPIO_PORTD_DEN_R &= ~0x0C; // disable digital I/O on PD3-2

GPIO_PORTD_AMSEL_R |= 0x0C; // enable analog functionality on PD3-2

ADC0_PC_R = 0x01; // 2) configure for 125K samples/sec

ADC0_SSPRI_R = 0x3210; // 3) Priority of sequencers

TIMER0_CTL_R = 0x00000000; // disable timer0A during setup

TIMER0_CTL_R |= 0x00000020; // enable timer0A trigger to ADC

TIMER0_CFG_R = 0; // configure for 32-bit timer mode

TIMER0_TAMR_R = 0x00000002; // configure for periodic mode

TIMER0_TAPR_R = 0; // prescale value for trigger

TIMER0_TAILR_R = 79999; // 80000 cycles is 1ms

TIMER0_IMR_R = 0x00000000; // disable all interrupts

TIMER0_CTL_R |= 0x00000001; // enable timer0A 32-b, periodic

ADC0_ACTSS_R &= ~0x04; // 5) disable sample sequencer 2

ADC0_EMUX_R = (ADC0_EMUX_R&0xFFFFF0FF)+0x0500; // 6) timer trigger

ADC0_SSMUX2_R = 0x0054; // 7) PD3-2 are channel 4,5

ADC0_SSCTL2_R = 0x0060; // 8) set flag and end after second

ADC0_IM_R |= 0x04; // 9) enable SS2 interrupts

ADC0_ACTSS_R |= 0x04; // 10) enable sample sequencer 2

NVIC_PRI4_R = (NVIC_PRI4_R&0xFFFFFF00)|0x00000040; // ADC2 priority 2

NVIC_EN0_R = 1<<16; // 12)enable interrupt 16

// 13)enable all interrupts in main

}

void ADC0Seq2_Handler(void){

ADC0_ISC_R = 0x04; // acknowledge ADC sequence 2 completion

Ch4Fifo_Put(ADC0_SSFIFO2_R); // PD3, Channel 4 first

Ch5Fifo_Put(ADC0_SSFIFO2_R); // PD2, Channel 5 second

}

Program T.2.6. Software to sample channels 4 and 5 at 1 kHz.

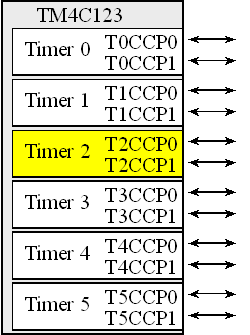

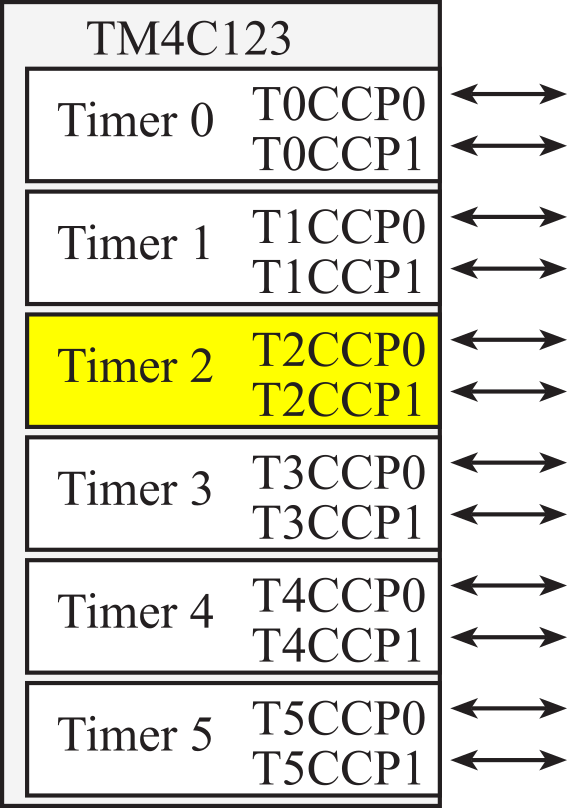

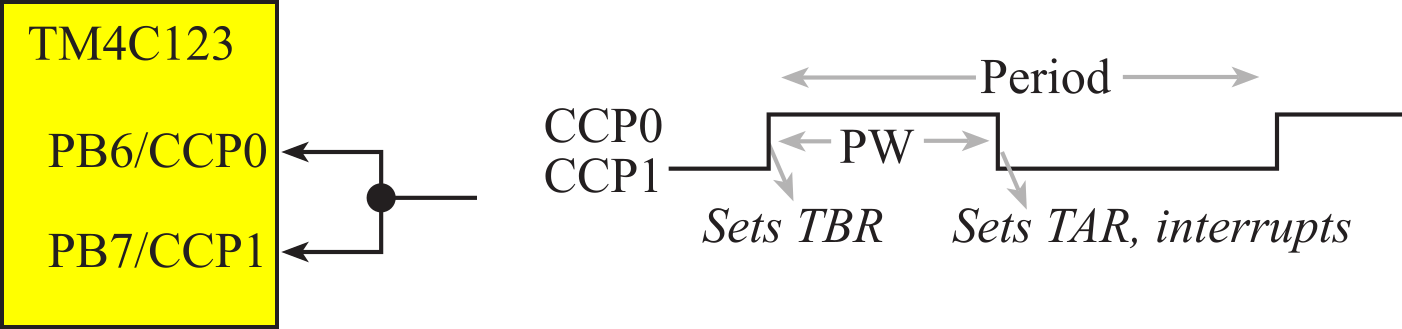

The TM4C123 has six timers and each timer has two modules, as shown in Figure T.3.1. We will use the timers to execute code on a periodic basis. In this section we will not use the associated I/O pins.

Figure T.3.1. Periodic timers on the TM4C123.

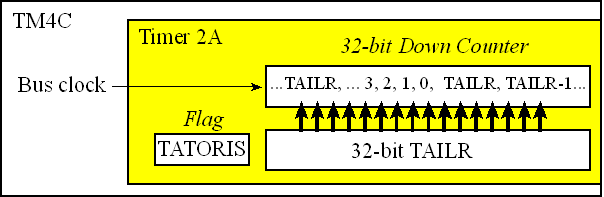

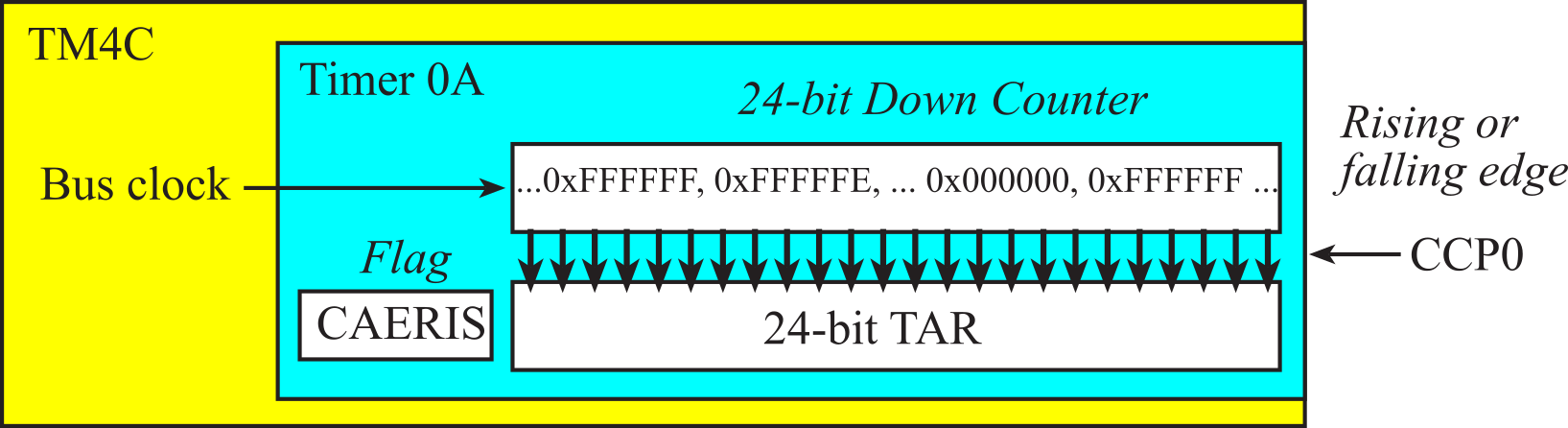

In periodic timer mode the timer is configured as a 32-bit down-counter, as shown in Figure T.3.2. When the timer counts from 1 to 0 it sets the trigger flag. On the next count, the timer is reloaded with the value in TIMER2_TAILR_R. We select periodic timer mode by setting the 2-bit TAMR field of the TIMER2_TAMR_R to 0x02. In periodic mode the timer runs continuously. The timers can be used to create pulse width modulated outputs and measure pulse width, period, or frequency.

Figure T.3.2. Operation of Periodic Timer.

In this section we will use Timer2A to trigger a periodic interrupt. We will implement an abstraction, such that the low-level implementation is defined in Program T.3.1, and the high-level application is shown in Program T.3.2. As with all abstractions, we separate what it does (Program T.3.2) from how it works (Program T.3.1). The precision is 32 bits and the resolution will be the bus cycle time of 12.5 ns. This means we could trigger an interrupt as slow as every 232*12.5ns, which is 53 seconds. The interrupt period will be

(TIMER2_TAILR_R +1)*12.5ns

: If the bus clock is 80 MHz, what TAILR value do you need to interrupt at 1 Hz?

Each periodic timer module has

A clock enable bit, bit 2 in SYSCTL_RCGCTIMER_R

A control register, TIMER2_CTL_R (set to 0 to disable, 1 to enable)

A configuration register, TIMER2_CFG_R (set to 0 for 32-bit mode)

A mode register, TIMER2_TAMR_R (set to 2 for periodic mode)

A 32-bit reload register, TIMER2_TAILR_R

A resolution register, TIMER2_TAPR_R (set to 0 for 12.5ns)

An interrupt clear register, TIMER2_ICR_R (bit 0)

An interrupt arm bit, TATOIM, TIMER2_IM_R (bit 0)

A flag bit, TATORIS, TIMER2_RIS_R (bit 0)

void (*PeriodicTask2)(void); // user function

void Timer_Init(void(*task)(void), uint32_t period, uint32_t priority){

SYSCTL_RCGCTIMER_R |= 0x04; // 0) activate timer2

PeriodicTask2 = task; // user function

TIMER2_CTL_R = 0x00000000; // 1) disable timer2A during setup

TIMER2_CFG_R = 0x00000000; // 2) configure for 32-bit mode

TIMER2_TAMR_R = 0x00000002; // 3) configure for periodic mode, default down-count settings

TIMER2_TAILR_R = period-1; // 4) reload value

TIMER2_TAPR_R = 0; // 5) bus clock resolution

TIMER2_ICR_R = 0x00000001; // 6) clear timer2A timeout flag

TIMER2_IMR_R = 0x00000001; // 7) arm timeout interrupt

NVIC_PRI5_R = (NVIC_PRI5_R&0x00FFFFFF)|(priority<<29); // priority

// interrupts enabled in the main program after all devices initialized

// vector number 39, interrupt number 23

NVIC_EN0_R = 1<<23; // 9) enable IRQ 23 in NVIC

TIMER2_CTL_R = 0x00000001; // 10) enable timer2A

}

void Timer2A_Handler(void){

TIMER2_ICR_R = TIMER_ICR_TATOCINT; // acknowledge TIMER2A timeout

(*PeriodicTask2)(); // execute user task

}

void Timer_Stop(void){

NVIC_DIS0_R = 1<<23; // 9) disable interrupt 23 in NVIC

TIMER2_CTL_R = 0x00000000; // 10) disable timer2A

}

Program T.3.1. Periodic interrupts using Timer2A.

Observation: It is good design practice to disable interrupts at the start of main, perform all initialization, and then enable interrupts.

uint32_t Time; // time in msec

void MyTask(void){ // task to run at 1kHz

Debug_HeartBeat0(); // Program T.1.2

Time++;

}

#define F1000HZ (80000000/1000)

int main(void){

DisableInterrupts();

PLL_Init(Bus80MHz); // bus clock at 80 MHz

Debug_Init(); // initialize heartbeat

Time = 0;

Timer_Init(&MyTask, F1000HZ,2); // 1000 Hz

EnableInterrupts();

while(1){

Debug_HeartBeat1();

}

}

Program T.3.2. Use of periodic interrupts to maintain time in msec.

: Assume there is a scope connected to the heartbeat in MyTask. At what frequency will the heartbeat oscillate?

Video T.3.1. Timer2A

As shown in Figure T.3.1, there are six 32-bit timers on the TM4C123. Table T.3.1 shows the changes one must make to use the other timers.

| Register | Timer0 | Timer1 | Timer2 | Timer3 | Timer4 | Timer5 |

| SYSCTL_RCGCTIMER_R | bit 0 | bit 1 | bit 2 | bit 3 | bit 4 | bit 5 |

| Priority register | NVIC_PRI4_R | NVIC_PRI5_R | NVIC_PRI5_R | NVIC_PRI8_R | NVIC_PRI17_R | NVIC_PRI23_R |

| Priority bits | 31-29 | 15-13 | 31-29 | 31-29 | 23-21 | 7-5 |

| Enable register | NVIC_EN0_R | NVIC_EN0_R | NVIC_EN0_R | NVIC_EN1_R | NVIC_EN2_R | NVIC_EN2_R |

| Enable bit | 19 | 21 | 23 | 3 | 6 | 28 |

Table T.3.1. Changes to Program T.3.1 needed to use the six timers.

T.4.1. Registers

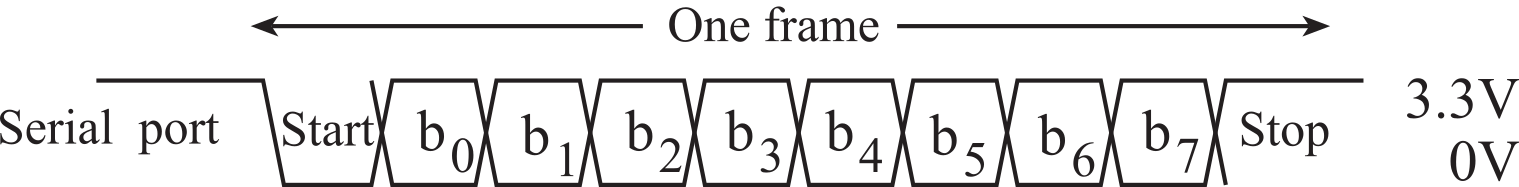

Next we will overview the specific UART functions on the TM4C microcontroller. Figure T.4.1 shows the UART protocol. The idle condition is high. The start bit is low. The data is transmitted one bit at a time b0 to b7. The frame ends in a stop bit, which is high. Because the idle and stop are high and the start is low, there is always a 1 to 0 transition at the start of a frame. The bit time is the width of each bit, the baud rate is 1/(bit time), and each frame is 10*(bit time). Since each frame contains one data byte, the bandwidth of the channel is 0.8*(baud rate).

Figure T.4.1. Full-duplex serial

communication channel.

TM4C microcontrollers have eight UARTs. The specific port pins used to implement the UARTs vary from one chip to the next. To find which pins your microcontroller uses, you will need to consult its datasheet. This section is intended to supplement rather than replace the Texas Instruments manuals. When designing systems with any I/O module, you must also refer to the reference manual of your specific microcontroller. It is also good design practice to review the errata for your microcontroller to see if any quirks (mistakes) exist in your microcontroller that might apply to the system you are designing. Table T.4.1 shows PCTL register for the TM4C123. Functionality U1Rx means UART1 reciever pin (input), and U1Tx means UART1 transmitter pin (output).

|

IO |

Ain |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

14 |

|

PA0 |

|

Port |

U0Rx |

|

|

|

|

|

|

CAN1Rx |

|

|

|

PA1 |

|

Port |

U0Tx |

|

|

|

|

|

|

CAN1Tx |

|

|

|

PA2 |

|

Port |

|

SSI0Clk |

|

|

|

|

|

|

|

|

|

PA3 |

|

Port |

|

SSI0Fss |

|

|

|

|

|

|

|

|

|

PA4 |

|

Port |

|

SSI0Rx |

|

|

|

|

|

|

|

|

|

PA5 |

|

Port |

|

SSI0Tx |

|

|

|

|

|

|

|

|

|

PA6 |

|

Port |

|

|

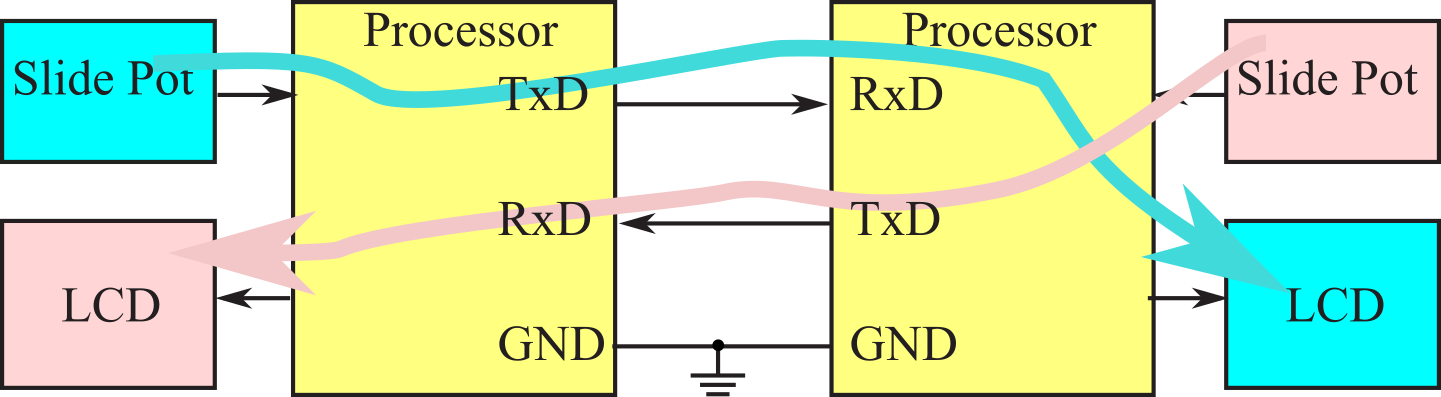

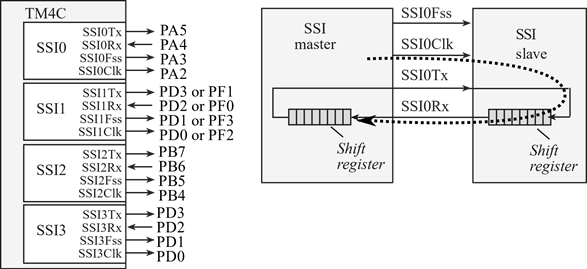

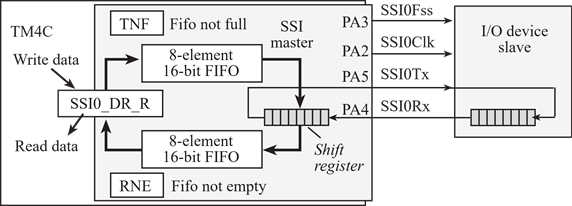

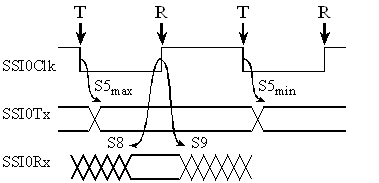

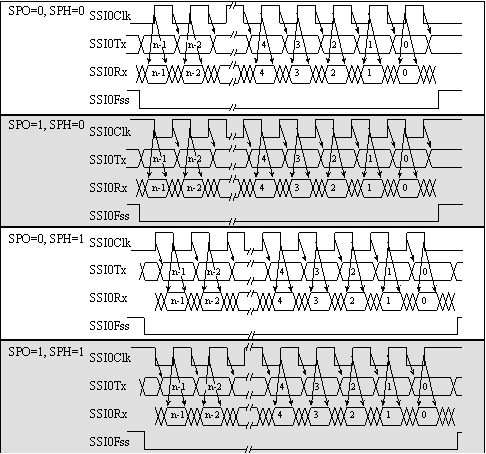

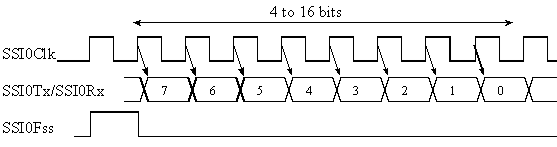

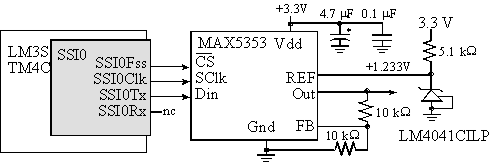

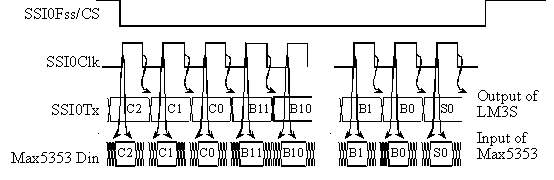

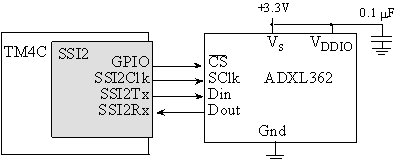

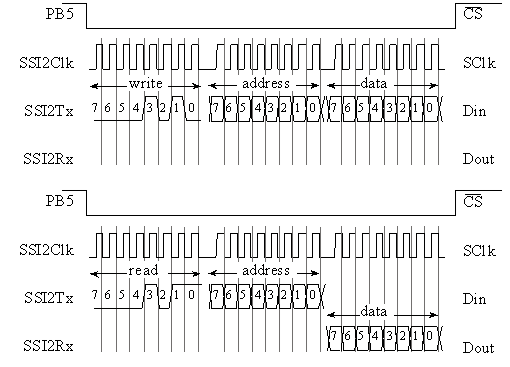

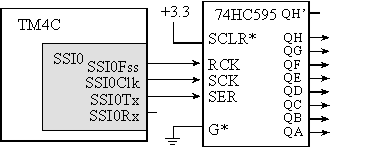

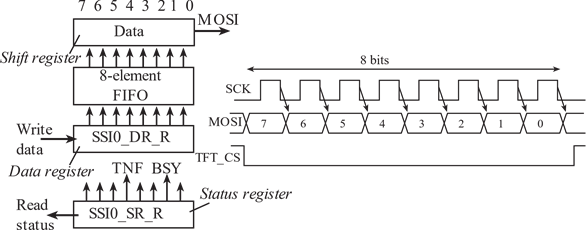

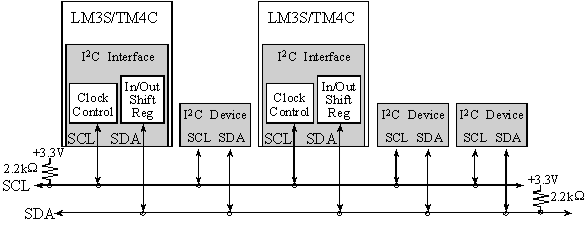

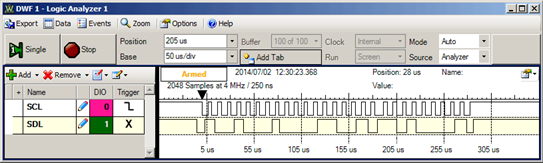

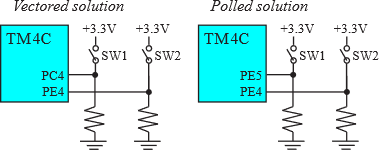

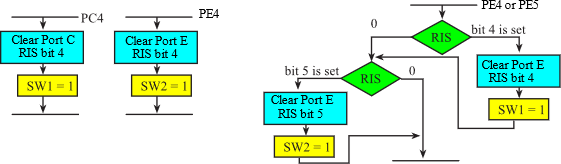

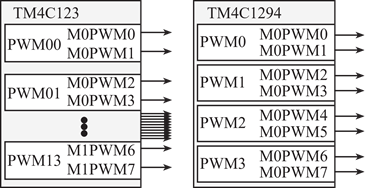

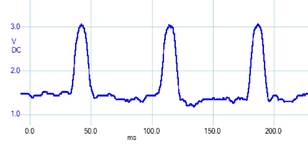

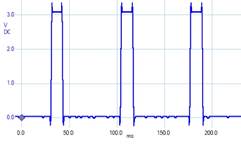

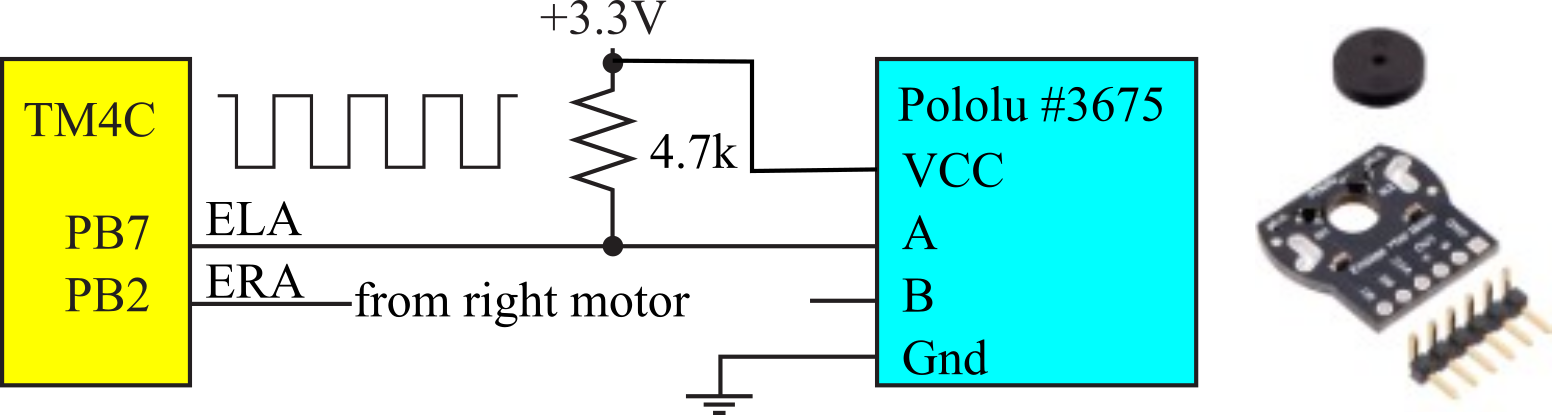

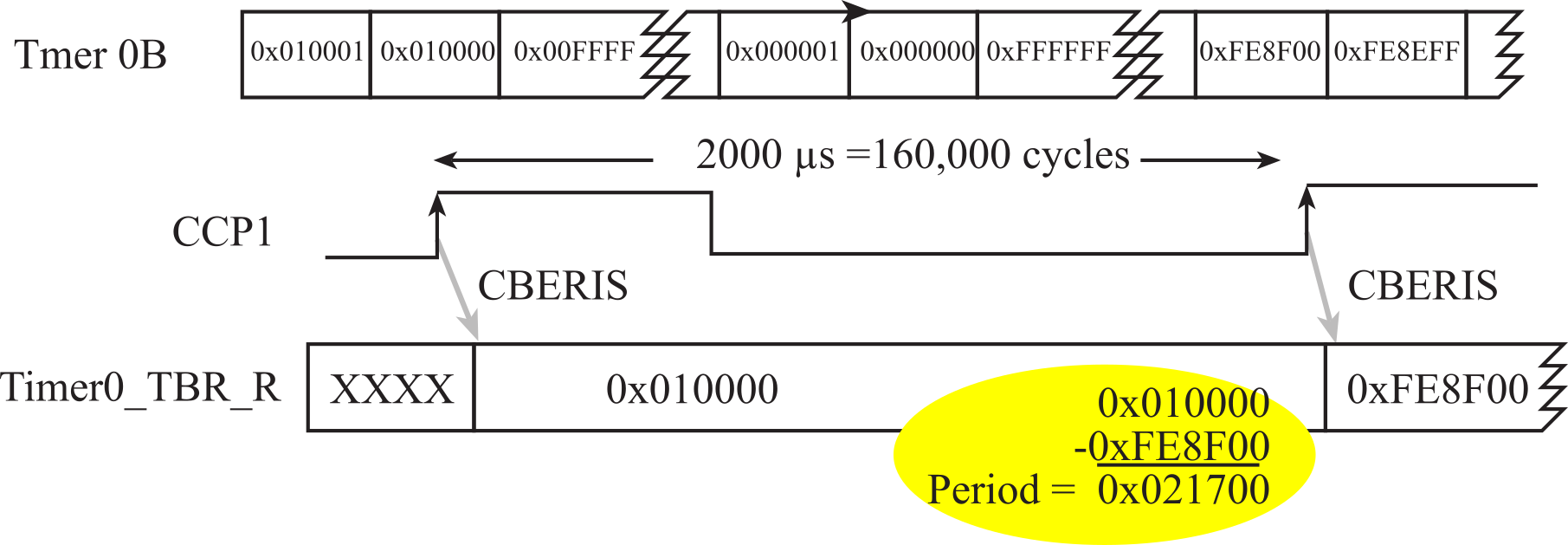

I2C1SCL |