|

Fall 2018 EE 460R: Intro to VLSI Design

Classroom: EER 1.518

Lab |

|

|

|

|

Course Goals:

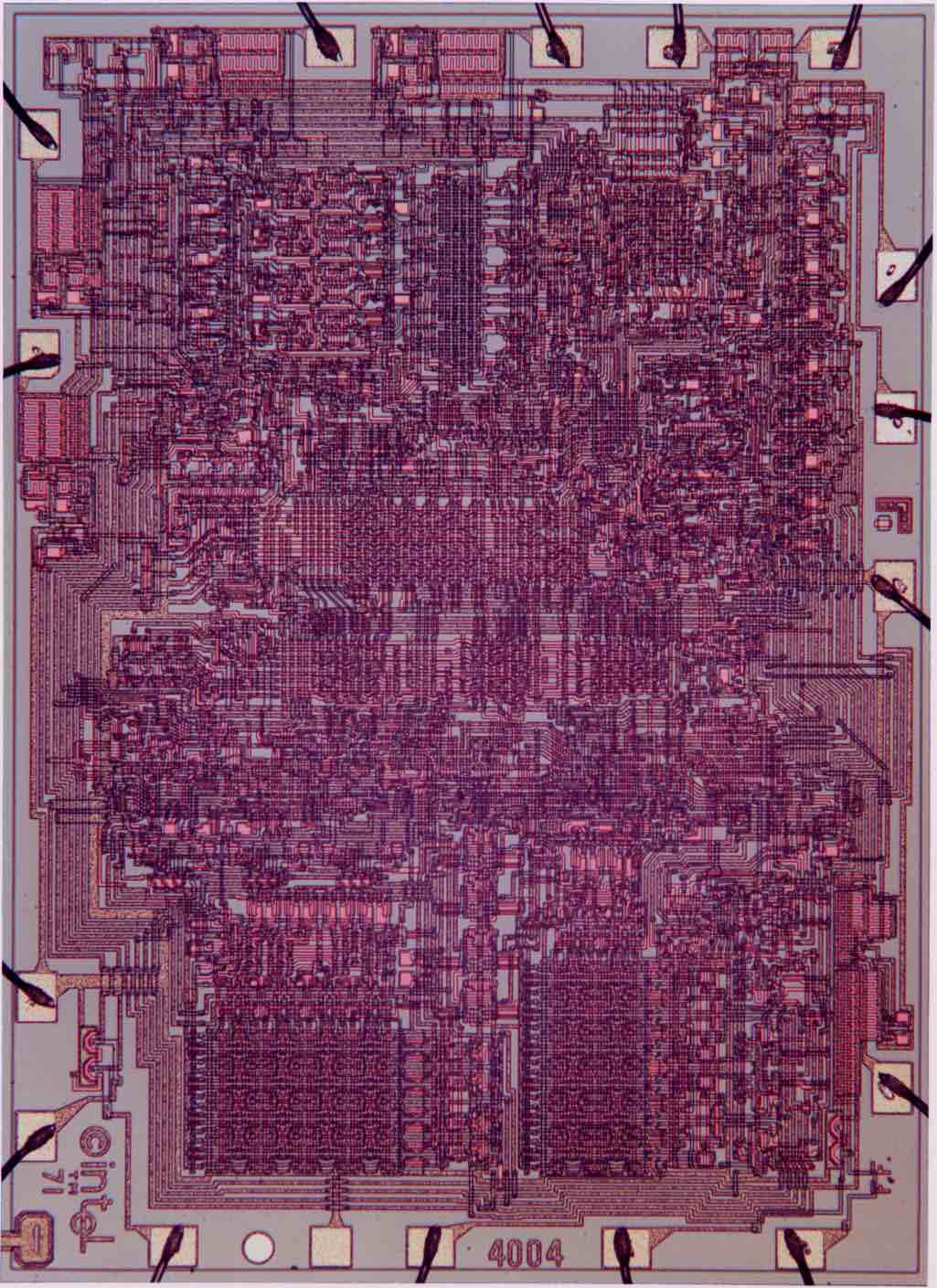

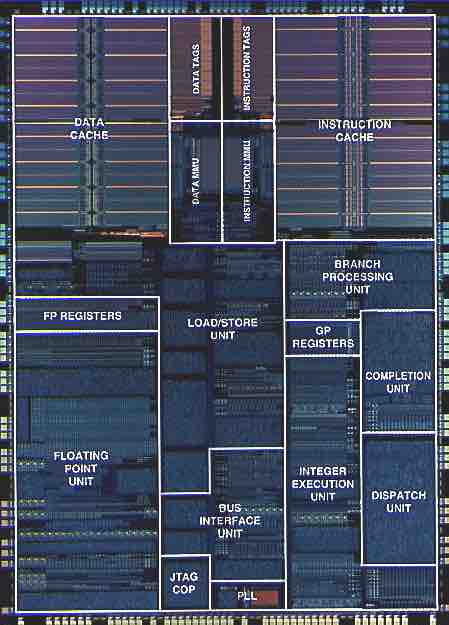

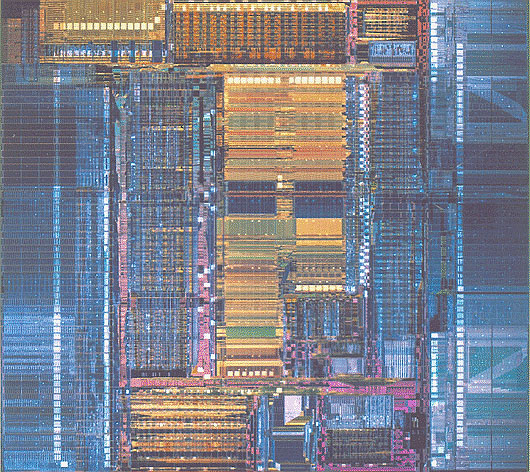

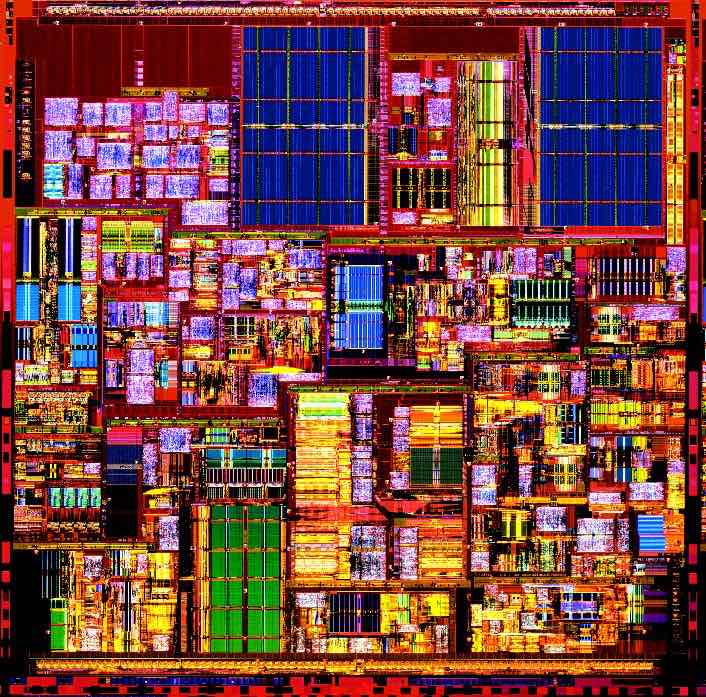

We will be learning the methodologies of implementing a digital system as a CMOS integrated circuit. The course will begin with a review of the basics of CMOS transistor operation and the manufacturing process for CMOS VLSI chips. We will then study in detail the problem of implementing logic gates in CMOS. Specifically, we will cover layout, design rules, and circuit families. Afterwards, we will examine techniques for analyzing and optimizing timing and power at the circuit level. We will study sequential elements (latches and flip-flops) and clocking. This will be followed by an overview of datapath design: detection logic, shifters, comparators, adders, and multipliers. We will also study memories, specifically the workhorse 6-T SRAM cell as well as peripheral decode logic. The course will conclude with a survey level treatment of various topics, including advanced circuit design techniques, synthesis, timing analysis, functional verification, design-for-test, and future trends.

Application of the concepts studied in class to larger designs will be done via the computer-aided design laboratory exercises which are based on common industry design practice. Commercial tools and an open-source standard cell library are used for the labs. Laboratory exercises will enable students to learn all aspects of digital design, including: layout of simple cells and the generation of larger blocks using these cells; designs at the schematic level, and the use of timing verification tools; the use of automatic place-and-route tools, and the concepts of post-layout timing closure; design at the register-transfer level using the Verilog hardware description language; and the use of synthesis tools to generate the design details with a standard cell library.

There will be two in-class exams. All exams are open book and open notes which means they will be hard. Several previous exams will be posted before the exam dates. There will be a final exam for EE460R. The team project replaces the final exam for EE382M-7.

Course prerequisites:

A working knowledge of digital logic design (EE316), fundamentals of electronic circuits (EE438) is required.

Textbook:

N. Weste and D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective (4th Edition), 2011. Addison-Wesley.

Instructor

Mark McDermott

Office: EER 5.826Phone: 471-3253

Office hours: T/Th 12:00 - 13:30 or by appointment

Teaching Assistant

Refer to TA web page for TA/grader office hours.

EE382M-7 Lab assignments are located here

EE460R Lab assignments are located here

Course outline and schedule: